Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs504t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(1)</sup>                                  | Pin<br>Type | Buffer<br>Type | PPS        | Description                                                                 |  |  |  |  |  |

|----------------------------------------------------------|-------------|----------------|------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| SCL1                                                     | I/O         | ST             | No         | Synchronous serial clock input/output for I2C1.                             |  |  |  |  |  |

| SDA1                                                     | I/O         | ST             | No         | Synchronous serial data input/output for I2C1.                              |  |  |  |  |  |

| ASCL1                                                    | I/O         | ST             | No         | Alternate synchronous serial clock input/output for I2C1.                   |  |  |  |  |  |

| ASDA1                                                    | I/O         | ST             | No         | Alternate synchronous serial data input/output for I2C1.                    |  |  |  |  |  |

| SCL2                                                     | I/O         | ST             | No         | Synchronous serial clock input/output for I2C2.                             |  |  |  |  |  |

| SDA2                                                     | I/O         | ST             | No         | Synchronous serial data input/output for I2C2.                              |  |  |  |  |  |

| ASCL2                                                    | I/O         | ST             | No         | Alternate synchronous serial clock input/output for I2C2.                   |  |  |  |  |  |

| ASDA2                                                    | I/O         | ST             | No         | Alternate synchronous serial data input/output for I2C2.                    |  |  |  |  |  |

| TMS                                                      | I           | ST             | No         | JTAG Test mode select pin.                                                  |  |  |  |  |  |

| TCK                                                      | I           | ST             | No         | JTAG test clock input pin.                                                  |  |  |  |  |  |

| TDI                                                      | I           | ST             | No         | JTAG test data input pin.                                                   |  |  |  |  |  |

| TDO                                                      | 0           |                | No         | JTAG test data output pin.                                                  |  |  |  |  |  |

| FLT1-FLT8                                                | Ι           | ST             | Yes        | PWM Fault Inputs 1 through 8.                                               |  |  |  |  |  |

| FLT9-FLT12                                               | I           | ST             | No         | PWM Fault Inputs 9 through 12.                                              |  |  |  |  |  |

| FLT31                                                    |             | ST             | No         | PWM Fault Input 31 (Class B Fault).                                         |  |  |  |  |  |

| PWM1L-PWM3L                                              | 0           | _              | No         | PWM Low Outputs 1 through 3.                                                |  |  |  |  |  |

| PWM1H-PWM3H                                              | 0           | _              | No         | PWM High Outputs 1 through 3.                                               |  |  |  |  |  |

| PWM4L-PWM5L <sup>(2)</sup><br>PWM4H-PWM5H <sup>(2)</sup> | 0           | _              | Yes        | PWM Low Outputs 4 and 5.                                                    |  |  |  |  |  |

| SYNCI1, SYNCI2                                           | 0           | —<br>ST        | Yes<br>Yes | PWM High Outputs 4 and 5.                                                   |  |  |  |  |  |

| SYNCO1, SYNCO2                                           | 0           | 51             | Yes        | PWM Synchronization Inputs 1 and 2.<br>PWM Synchronization Outputs 1 and 2. |  |  |  |  |  |

| CMP1A-CMP4A                                              |             | Analog         | No         | Comparator Channels 1 through 4 A input.                                    |  |  |  |  |  |

| CMP1B-CMP4B                                              |             | Analog         | No         | Comparator Channels 1 through 4 B input.                                    |  |  |  |  |  |

| CMP1C-CMP4C                                              | i           | Analog         | No         | Comparator Channels 1 through 4 C input.                                    |  |  |  |  |  |

| CMP1D-CMP4D                                              | i           | Analog         | No         | Comparator Channels 1 through 4 D input.                                    |  |  |  |  |  |

| DACOUT1, DACOUT2                                         | 0           |                | No         | DAC Output Voltages 1 and 2.                                                |  |  |  |  |  |

| EXTREF1, EXTREF2                                         | Ι           | Analog         | No         | External Voltage Reference Inputs 1 and 2 for the reference DACs.           |  |  |  |  |  |

| ISRC1-ISRC4                                              | 0           | Analog         | No         | Constant-Current Outputs 1 through 4.                                       |  |  |  |  |  |

| PGA1P1-PGA1P4                                            | Ι           | Analog         | No         | PGA1 Positive Inputs 1 through 4.                                           |  |  |  |  |  |

| PGA1N1-PGA1N3                                            | I           | Analog         | No         | PGA1 Negative Inputs 1 through 3.                                           |  |  |  |  |  |

| PGA2P1-PGA2P4                                            | I           | Analog         | No         | PGA2 Positive Inputs 1 through 4.                                           |  |  |  |  |  |

| PGA2N1-PGA2N3                                            | I           | Analog         | No         | PGA2 Negative Inputs 1 through 3.                                           |  |  |  |  |  |

| ADTRG31                                                  | Ι           | ST             | No         | External ADC trigger source.                                                |  |  |  |  |  |

| PGED1                                                    | I/O         | ST             | No         | Data I/O pin for Programming/Debugging Communication Channel 1.             |  |  |  |  |  |

| PGEC1                                                    | Ι           | ST             | No         | Clock input pin for Programming/Debugging Communication Channel 1.          |  |  |  |  |  |

| PGED2                                                    | I/O         | ST             | No         | Data I/O pin for Programming/Debugging Communication Channel 2.             |  |  |  |  |  |

| PGEC2                                                    | Ι           | ST             | No         | Clock input pin for Programming/Debugging Communication Channel 2.          |  |  |  |  |  |

| PGED3                                                    | I/O         | ST             | No         | Data I/O pin for Programming/Debugging Communication Channel 3.             |  |  |  |  |  |

| PGEC3                                                    | I           | ST             | No         | Clock input pin for Programming/Debugging Communication Channel 3.          |  |  |  |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------|

|------------|-------------------------------------|

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PowerO = OutputI = InputTTL = TTL input buffer

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

2: These pins are dedicated on 64-pin devices.

#### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXGS50X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXGS50X devices contain control registers for Modulo Addressing, Bit-Reversed Addressing and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 3-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |

| W0 through W14 <sup>(1)</sup>                     | Alternate 1 Working Register Array                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate 2 Working Register Array                        |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine STATUS Register                        |

| SPLIM                                             | Stack Pointer Limit Value Register                        |

| TBLPAG                                            | Table Memory Page Address Register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |

| RCOUNT                                            | REPEAT Loop Counter Register                              |

| DCOUNT                                            | DO Loop Counter Register                                  |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: Memory-mapped W0 through W14 represent the value of the register in the currently active CPU context.

**2:** The DOSTARTH and DOSTARTL registers are read-only.

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2   | SFA: Stack Frame Active Status bit                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG</li> <li>0 = Stack frame is not active; W14 and W15 address the base Data Space</li> </ul> |

| bit 1   | RND: Rounding Mode Select bit                                                                                                                                                             |

|         | <ul><li>1 = Biased (conventional) rounding is enabled</li><li>0 = Unbiased (convergent) rounding is enabled</li></ul>                                                                     |

| bit 0   | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                      |

|         | <ul> <li>1 = Integer mode is enabled for DSP multiply</li> <li>0 = Fractional mode is enabled for DSP multiply</li> </ul>                                                                 |

| Note 1: | This bit is always read as '0'.                                                                                                                                                           |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0             | U-0                                                               | U-0          | U-0 | U-0          | R-0              | R-0    | R-0    |  |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------|--------------|-----|--------------|------------------|--------|--------|--|--|--|--|--|--|--|

| —               | —                                                                 | —            | —   | —            | CCTXI2           | CCTXI1 | CCTXI0 |  |  |  |  |  |  |  |

| bit 15          |                                                                   | •            |     | bit 8        |                  |        |        |  |  |  |  |  |  |  |

|                 |                                                                   |              |     |              |                  |        |        |  |  |  |  |  |  |  |

| U-0             | U-0                                                               | U-0          | U-0 | U-0          | R-0              | R-0    | R-0    |  |  |  |  |  |  |  |

|                 | —                                                                 | —            | _   | —            | MCTXI2           | MCTXI1 | MCTXI0 |  |  |  |  |  |  |  |

| bit 7           |                                                                   |              |     |              |                  |        | bit 0  |  |  |  |  |  |  |  |

|                 |                                                                   |              |     |              |                  |        |        |  |  |  |  |  |  |  |

| Legend:         |                                                                   |              |     |              |                  |        |        |  |  |  |  |  |  |  |

| R = Readable I  | bit                                                               | W = Writable | bit | U = Unimpler | nented bit, read | as '0' |        |  |  |  |  |  |  |  |

| -n = Value at P | e at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |     |              |                  |        |        |  |  |  |  |  |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                 |

|-----------|----------------------------------------------------------------------------|

| bit 10-8  | CCTXI<2:0>: Current (W Register) Context Identifier bits                   |

|           | 111 = Reserved                                                             |

|           | •                                                                          |

|           | •                                                                          |

|           | •                                                                          |

|           | 011 = Reserved                                                             |

|           | 010 = Alternate Working Register Set 2 is currently in use                 |

|           | 001 = Alternate Working Register Set 1 is currently in use                 |

|           | 000 = Default register set is currently in use                             |

| bit 7-3   | Unimplemented: Read as '0'                                                 |

| bit 2-0   | MCTXI<2:0>: Manual (W Register) Context Identifier bits                    |

|           | 111 = Reserved                                                             |

|           | •                                                                          |

|           | •                                                                          |

|           | •                                                                          |

|           | 011 = Reserved                                                             |

|           | 010 = Alternate Working Register Set 2 was most recently manually selected |

|           | 001 = Alternate Working Register Set 1 was most recently manually selected |

|           | 000 = Default register set was most recently manually selected             |

#### TABLE 4-33: PORTA REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4         | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|---------------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  | _      | _      | _      |        | _      |        |       |       | _     | _     | _     |               |       | TRISA<4:0> | •         |       | 001F          |

| PORTA       | 0E02  | _      |        | —      |        | —      |        |       |       |       | —     | —     |               |       | RA<4:0>    |           |       | 0000          |

| LATA        | 0E04  | _      |        | —      |        | —      |        |       |       |       | —     | —     | LATA<4:0> 0   |       |            |           |       | 0000          |

| ODCA        | 0E06  | _      |        | —      |        | —      |        |       |       |       | —     | —     |               |       | ODCA<4:0>  | •         |       | 0000          |

| CNENA       | 0E08  | _      |        | —      |        | —      |        |       |       |       | —     | —     |               | (     | CNIEA<4:0  | >         |       | 0000          |

| CNPUA       | 0E0A  | _      |        | —      |        | —      |        |       |       |       | —     | —     |               | C     | CNPUA<4:0  | >         |       | 0000          |

| CNPDA       | 0E0C  | _      |        | —      |        | —      |        |       |       |       | —     | —     | CNPDA<4:0> 00 |       |            |           |       | 0000          |

| ANSELA      | 0E0E  | _      | _      | _      | -      | _      | -      | -     | -     | _     | —     | _     | _             | —     |            | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15          | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|-----------------|--------|--------|--------|--------|--------|--------|---------|-------|-----------|-------|-------|-------|-------|--------|-------|---------------|

| TRISB       | 0E10  |                 |        |        |        |        |        |        | TRISB<1 | 5:0>  |           |       |       |       |       |        |       | FFFF          |

| PORTB       | 0E12  |                 |        |        |        |        |        |        | RB<15   | :0>   |           |       |       |       |       |        |       | xxxx          |

| LATB        | 0E14  | LATB<15:0> xxxx |        |        |        |        |        |        |         | xxxx  |           |       |       |       |       |        |       |               |

| ODCB        | 0E16  |                 |        |        |        |        |        |        | ODCB<1  | 5:0>  |           |       |       |       |       |        |       | 0000          |

| CNENB       | 0E18  |                 |        |        |        |        |        |        | CNIEB<1 | 5:0>  |           |       |       |       |       |        |       | 0000          |

| CNPUB       | 0E1A  |                 |        |        |        |        |        |        | CNPUB<  | 15:0> |           |       |       |       |       |        |       | 0000          |

| CNPDB       | 0E1C  | CNPDB<15:0> 000 |        |        |        |        |        |        | 0000    |       |           |       |       |       |       |        |       |               |

| ANSELB      | 0E1E  |                 | _      | —      | —      | —      | ANSB<  | :10:9> | —       |       | ANSB<7:5> | •     | _     |       | ANSE  | 3<3:0> |       | 06EF          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PORTC REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15        | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|---------------|-----------------|--------|--------|--------|--------|-------|---------|-------|-------|-----------|-------|-------|-------|-----------|-------|---------------|

| TRISC       | 0E20  | 0 TRISC<15:0> |                 |        |        |        |        |       |         |       |       |           |       | FFFF  |       |           |       |               |

| PORTC       | 0E22  |               | RC<15:0> xxxx   |        |        |        |        |       |         |       |       |           | xxxx  |       |       |           |       |               |

| LATC        | 0E24  |               | LATC<15:0> xxxx |        |        |        |        |       |         |       |       | xxxx      |       |       |       |           |       |               |

| ODCC        | 0E26  |               |                 |        |        |        |        |       | ODCC<1  | 5:0>  |       |           |       |       |       |           |       | 0000          |

| CNENC       | 0E28  |               |                 |        |        |        |        |       | CNIEC<1 | 5:0>  |       |           |       |       |       |           |       | 0000          |

| CNPUC       | 0E2A  |               |                 |        |        |        |        |       | CNPUC<  | 15:0> |       |           |       |       |       |           |       | 0000          |

| CNPDC       | 0E2C  |               | CNPDC<15:0> 00  |        |        |        |        |       |         |       | 0000  |           |       |       |       |           |       |               |

| ANSELC      | 0E2E  | _             | _               | —      |        | ANSC<  | :12:9> |       | _       | —     |       | ANSC<6:4> |       | —     | /     | ANSC<2:0> |       | 1E77          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0           | R/W-0                                                                                                          | U-0                                 | U-0           | R/W-0                        | U-0               | R/W-0            | R/W-0         |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------|------------------------------|-------------------|------------------|---------------|--|--|--|--|--|--|

| TRAPR           | IOPUWR                                                                                                         |                                     | —             | VREGSF                       |                   | CM               | VREGS         |  |  |  |  |  |  |

| bit 15          |                                                                                                                |                                     | L             |                              |                   |                  | bit 8         |  |  |  |  |  |  |

|                 |                                                                                                                |                                     |               |                              |                   |                  |               |  |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                          | R/W-0                               | R/W-0         | R/W-0                        | R/W-0             | R/W-1            | R/W-1         |  |  |  |  |  |  |

| EXTR            | SWR                                                                                                            | SWDTEN <sup>(2)</sup>               | WDTO          | SLEEP                        | IDLE              | BOR              | POR           |  |  |  |  |  |  |

| bit 7           |                                                                                                                |                                     |               |                              |                   |                  | bit (         |  |  |  |  |  |  |

| Legend:         |                                                                                                                |                                     |               |                              |                   |                  |               |  |  |  |  |  |  |

| R = Readable    | bit                                                                                                            | W = Writable                        | bit           | U = Unimple                  | mented bit, read  | l as '0'         |               |  |  |  |  |  |  |

| -n = Value at l |                                                                                                                | '1' = Bit is set                    |               | '0' = Bit is cle             |                   | x = Bit is unki  | nown          |  |  |  |  |  |  |

|                 |                                                                                                                |                                     |               |                              |                   |                  |               |  |  |  |  |  |  |

| bit 15          | TRAPR: Trap                                                                                                    | Reset Flag bit                      |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 | -                                                                                                              | onflict Reset ha                    |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 | 0 = A Trap Co                                                                                                  | onflict Reset ha                    | s not occurre | ed                           |                   |                  |               |  |  |  |  |  |  |

| bit 14          | IOPUWR: Ille                                                                                                   | gal Opcode or                       | Uninitialized | W Register Ac                | cess Reset Flag   | bit              |               |  |  |  |  |  |  |

|                 | •                                                                                                              | •                                   |               | gal address m                | ode or Uninitial  | ized W registe   | er used as ar |  |  |  |  |  |  |

|                 |                                                                                                                | Pointer caused                      |               | ogistor Posot k              | nas not occurred  | 4                |               |  |  |  |  |  |  |

| bit 13-12       | -                                                                                                              | ited: Read as '                     |               | egister Reset i              | las not occurred  | 1                |               |  |  |  |  |  |  |

| bit 11          | •                                                                                                              |                                     |               |                              | n hit             |                  |               |  |  |  |  |  |  |

|                 | VREGSF: Flash Voltage Regulator Standby During Sleep bit<br>1 = Flash voltage regulator is active during Sleep |                                     |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                | Itage regulator                     |               | •                            | ing Sleep         |                  |               |  |  |  |  |  |  |

| bit 10          |                                                                                                                | ted: Read as '                      | -             | 5                            | 0                 |                  |               |  |  |  |  |  |  |

| bit 9           | -                                                                                                              | I: Configuration Mismatch Flag bit  |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                | uration Mismato<br>uration Mismato  |               |                              |                   |                  |               |  |  |  |  |  |  |

| bit 8           | VREGS: Volta                                                                                                   | age Regulator S                     | Standby Durir | ng Sleep bit                 |                   |                  |               |  |  |  |  |  |  |

|                 | VREGS: Voltage Regulator Standby During Sleep bit<br>1 = Voltage regulator is active during Sleep              |                                     |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 | 0 = Voltage r                                                                                                  | egulator goes i                     | nto Standby r | mode during SI               | еер               |                  |               |  |  |  |  |  |  |

| bit 7           |                                                                                                                | nal Reset (MCL                      |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                | Clear (pin) Res                     |               |                              |                   |                  |               |  |  |  |  |  |  |

| bit 6           |                                                                                                                | Clear (pin) Res                     |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                | instruction has                     | , .           |                              |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                | instruction has                     |               |                              |                   |                  |               |  |  |  |  |  |  |

| bit 5           | SWDTEN: So                                                                                                     | oftware Enable/                     | Disable of W  | DT bit <b><sup>(2)</sup></b> |                   |                  |               |  |  |  |  |  |  |

|                 | 1 = WDT is e                                                                                                   |                                     |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 | 0 = WDT is d                                                                                                   | isabled                             |               |                              |                   |                  |               |  |  |  |  |  |  |

| bit 4           |                                                                                                                | hdog Timer Tim                      | -             | it                           |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                | e-out has occur<br>e-out has not oc |               |                              |                   |                  |               |  |  |  |  |  |  |

|                 |                                                                                                                |                                     | set or cleare | d in software. S             | Setting one of th | ese bits in soft | ware does not |  |  |  |  |  |  |

|                 | use a device Re                                                                                                |                                     | hite are '11' | (upprogramm)                 |                   | alwaye anabla    | d rogardiaca  |  |  |  |  |  |  |

|                 | the SWDTEN< 1:0                                                                                                |                                     |               | unprogramme                  | ed), the WDT is   | aiways enable    | u, regardiess |  |  |  |  |  |  |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

© 2013-2017 Microchip Technology Inc.

of the SWDTEN bit setting.

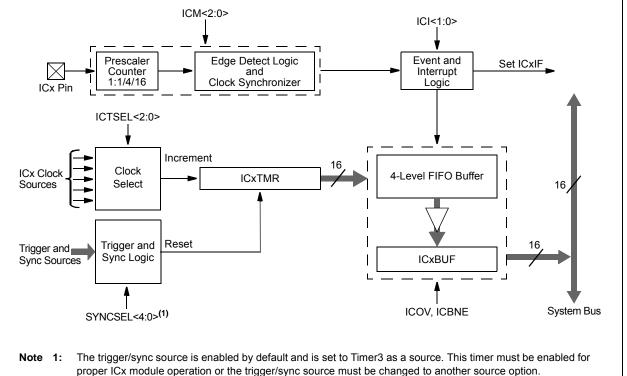

### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurements. The dsPIC33EPXXGS50X family devices support four input capture channels.

Key features of the input capture module include:

Hardware-Configurable for 32-Bit Operation in All modes by Cascading Two Adjacent Modules

- Synchronous and Trigger modes of Output Compare Operation, with up to 21 User-Selectable Trigger/Sync Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Six Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

### 13.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 13.1.1 KEY RESOURCES

- "Input Capture" (DS70000352) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## FIGURE 13-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

#### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = OCxRS compare event is used for synchronization

- 11110 = INT2 pin synchronizes or triggers OCx

- 11101 = INT1 pin synchronizes or triggers OCx

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers OCx

- 11010 = CMP3 module synchronizes or triggers OCx

- 11001 = CMP2 module synchronizes or triggers OCx

- 11000 = CMP1 module synchronizes or triggers OCx

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 input capture interrupt event synchronizes or triggers OCx

- 10010 = IC3 input capture interrupt event synchronizes or triggers OCx

- 10001 = IC2 input capture interrupt event synchronizes or triggers OCx

- 10000 = IC1 input capture interrupt event synchronizes or triggers OCx

- 01111 = Timer5 synchronizes or triggers OCx

- 01110 = Timer4 synchronizes or triggers OCx

- 01101 = Timer3 synchronizes or triggers OCx

- 01100 = Timer2 synchronizes or triggers OCx (default)

- 01011 = Timer1 synchronizes or triggers OCx

- 01010 = Reserved

- 01001 = Reserved

- 01000 = IC4 input capture event synchronizes or triggers OCx

- 00111 = IC3 input capture event synchronizes or triggers OCx

- 00110 = IC2 input capture event synchronizes or triggers OCx

- 00101 = IC1 input capture event synchronizes or triggers OCx

- 00100 = OC4 module synchronizes or triggers  $OCx^{(1,2)}$

- 00011 = OC3 module synchronizes or triggers  $OCx^{(1,2)}$

- 00010 = OC2 module synchronizes or triggers  $OCx^{(1,2)}$

- 00001 = OC1 module synchronizes or triggers  $OCx^{(1,2)}$

- 00000 = No sync or trigger source for OCx

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

#### **REGISTER 15-27: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER (x = 1 to 5)**

| R-0              | R-0 | R-0             | R-0  | R-0                          | R-0            | R-0      | R-0   |

|------------------|-----|-----------------|------|------------------------------|----------------|----------|-------|

|                  |     |                 |      | P<12:5> <sup>(1,2,3,4)</sup> |                |          |       |

| bit 15           |     |                 |      |                              |                |          | bit 8 |

|                  |     |                 |      |                              |                |          |       |

| R-0              | R-0 | R-0             | R-0  | R-0                          | U-0            | U-0      | U-0   |

|                  | PW  | MCAP<4:0>(1,2,3 | 8,4) |                              | _              |          |       |

| bit 7            |     |                 |      |                              |                |          | bit 0 |

|                  |     |                 |      |                              |                |          |       |

| Legend:          |     |                 |      |                              |                |          |       |

| R = Readable bit |     | W = Writable bi | t    | II = I Inimplem              | onted hit read | 1 26 '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-3 **PWMCAP<12:0>:** PWMx Primary Time Base Capture Value bits<sup>(1,2,3,4)</sup> The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

#### bit 2-0 Unimplemented: Read as '0'

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

- **3:** The minimum capture resolution is 8.32 ns.

- 4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

### 17.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70000195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family of devices contains two Inter-Integrated Circuit (I $^2$ C) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx/ASCLx pin is clock

- · The SDAx/ASDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting Both Master and Slave modes of Operation

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control)

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates accordingly

- System Management Bus (SMBus) Support

- Alternate I<sup>2</sup>C Pin Mapping (ASCLx/ASDAx)

### 17.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 17.1.1 KEY RESOURCES

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 18.1 UART Helpful Tips

- In multi-node, direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the UxRX pin.

- b) If URXINV = 1, use a pull-down resistor on the UxRX pin.

- 2. The first character received on a wake-up from Sleep mode, caused by activity on the UxRX pin of the UARTx module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 18.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 18.2.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                           |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                    |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                   |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                               |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                             |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                              |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                           |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                         |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                              |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                           |

Note 1: Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

NOTES:

#### REGISTER 20-1: CMPxCON: COMPARATOR x CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0 |

|--------|-----|---------|---------|---------|--------|---------|-------|

| CMPON  | —   | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE |

| bit 15 |     |         |         |         |        |         | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | HC-0, HS | R/W-0  | R/W-0  | R/W-0 |

|--------|--------|--------|--------|----------|--------|--------|-------|

| INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT  | ALTINP | CMPPOL | RANGE |

| bit 7  |        |        |        |          |        |        | bit 0 |

| Legend: HC = Hardware Clearable bit HS = Hardware |                  | HS = Hardware Settable bit  |                    |

|---------------------------------------------------|------------------|-----------------------------|--------------------|

| R = Readable bit                                  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR                                 | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | CMPON: Comparator Operating Mode bit                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------|

|           | 1 = Comparator module is enabled                                                                              |

|           | 0 = Comparator module is disabled (reduces power consumption)                                                 |

| bit 14    | Unimplemented: Read as '0'                                                                                    |

| bit 13    | CMPSIDL: Comparator Stop in Idle Mode bit                                                                     |

|           | 1 = Discontinues module operation when device enters Idle mode.                                               |

|           | 0 = Continues module operation in Idle mode                                                                   |

|           | If a device has multiple comparators, any CMPSIDL bit set to '1' disables all comparators while in Idle mode. |

| bit 12-11 | HYSSEL<1:0>: Comparator Hysteresis Select bits                                                                |

|           | 11 = 20 mV hysteresis                                                                                         |

|           | 10 = 10  mV hysteresis                                                                                        |

|           | 01 = 5 mV hysteresis<br>00 = No hysteresis is selected                                                        |

| bit 10    | FLTREN: Digital Filter Enable bit                                                                             |

|           | 1 = Digital filter is enabled                                                                                 |

|           | 0 = Digital filter is disabled                                                                                |

| bit 9     | FCLKSEL: Digital Filter and Pulse Stretcher Clock Select bit                                                  |

|           | 1 = Digital filter and pulse stretcher operate with the PWM clock                                             |

|           | 0 = Digital filter and pulse stretcher operate with the system clock                                          |

| bit 8     | DACOE: DACx Output Enable bit                                                                                 |

|           | 1 = DACx analog voltage is connected to the DACOUTx pin <sup>(1)</sup>                                        |

|           | 0 = DACx analog voltage is not connected to the DACOUTx pin                                                   |

| bit 7-6   | INSEL<1:0>: Input Source Select for Comparator bits                                                           |

|           | If ALTINP = 0, Select from Comparator Inputs:                                                                 |

|           | 11 = Selects CMPxD input pin<br>10 = Selects CMPxC input pin                                                  |

|           | 01 = Selects CMPxB input pin                                                                                  |

|           | 00 = Selects CMPxA input pin                                                                                  |

|           | If ALTINP = 1, Select from Alternate Inputs:                                                                  |

|           | 11 = Reserved                                                                                                 |

|           | 10 = Reserved<br>01 = Selects PGA2 output                                                                     |

|           | 01 = Selects PGA2 output<br>00 = Selects PGA1 output                                                          |

| •• · ·    |                                                                                                               |

**Note 1:** DACOUTx can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DACx output by setting their respective DACOE bit.

| Base<br>Instr<br># | nstr Assembly Assembly Syntax Descript |        |                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|----------------------------------------|--------|----------------|---------------------------------------------------|---------------|-------------------------------|--------------------------|

| 55                 | NEG                                    | NEG    | Acc            | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                                        | NEG    | f              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                                        | NEG    | f,WREG         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                                        | NEG    | Ws,Wd          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z              |

| 56                 | NOP                                    | NOP    |                | No Operation                                      | 1             | 1                             | None                     |

|                    |                                        | NOPR   |                | No Operation                                      | 1             | 1                             | None                     |

| 57                 | POP                                    | POP    | f              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                     |

|                    |                                        | POP    | Wdo            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                     |

|                    |                                        | POP.D  | Wnd            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                     |

|                    |                                        | POP.S  |                | Pop Shadow Registers                              | 1             | 1                             | All                      |

| 58                 | PUSH                                   | PUSH   | f              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                     |

|                    |                                        | PUSH   | Wso            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                     |

|                    |                                        | PUSH.D | Wns            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                     |

|                    |                                        | PUSH.S |                | Push Shadow Registers                             | 1             | 1                             | None                     |

| 59                 | PWRSAV                                 | PWRSAV | #lit1          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep               |

| 60                 | RCALL                                  | RCALL  | Expr           | Relative Call                                     | 1             | 4                             | SFA                      |

|                    |                                        | RCALL  | Wn             | Computed Call                                     | 1             | 4                             | SFA                      |

| 61                 | REPEAT                                 | REPEAT | #lit15         | Repeat Next Instruction lit15 + 1 time            | 1             | 1                             | None                     |

|                    |                                        | REPEAT | Wn             | Repeat Next Instruction (Wn) + 1 time             | 1             | 1                             | None                     |

| 62                 | RESET                                  | RESET  |                | Software device Reset                             | 1             | 1                             | None                     |

| 63                 | RETFIE                                 | RETFIE |                | Return from interrupt                             | 1             | 6 (5)                         | SFA                      |

| 64                 | RETLW                                  | RETLW  | #lit10,Wn      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                      |

| 65                 | RETURN                                 | RETURN |                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                      |

| 66                 | RLC                                    | RLC    | f              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                    |

|                    |                                        | RLC    | f,WREG         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                    |

|                    |                                        | RLC    | Ws,Wd          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                    |

| 67                 | RLNC                                   | RLNC   | f              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                      |

|                    |                                        | RLNC   | f,WREG         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                      |

|                    |                                        | RLNC   | Ws,Wd          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                      |

| 68                 | RRC                                    | RRC    | f              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                    |

|                    |                                        | RRC    | f,WREG         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                    |

|                    |                                        | RRC    | Ws,Wd          | Wd = Rotate Right through Carry Ws                | 1             | 1                             | C,N,Z                    |

| 69                 | RRNC                                   | RRNC   | f              | f = Rotate Right (No Carry) f                     | 1             | 1                             | N,Z                      |

|                    |                                        | RRNC   | f,WREG         | WREG = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                      |

|                    |                                        | RRNC   | Ws,Wd          | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                             | N,Z                      |

| 70                 | SAC                                    | SAC    | Acc,#Slit4,Wdo | Store Accumulator                                 | 1             | 1                             | None                     |

|                    |                                        | SAC.R  | Acc,#Slit4,Wdo | Store Rounded Accumulator                         | 1             | 1                             | None                     |

| 71                 | SE                                     | SE     | Ws,Wnd         | Wnd = sign-extended Ws                            | 1             | 1                             | C,N,Z                    |

| 72                 | SETM                                   | SETM   | f              | f = 0xFFFF                                        | 1             | 1                             | None                     |

|                    |                                        | SETM   | WREG           | WREG = 0xFFFF                                     | 1             | 1                             | None                     |

|                    |                                        | SETM   | Ws             | Ws = 0xFFFF                                       | 1             | 1                             | None                     |

| 73                 | SFTAC                                  | SFTAC  | Acc, Wn        | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                                        | SFTAC  | Acc,#Slit6     | Arithmetic Shift Accumulator by Slit6             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

### 25.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 25.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| DC CHARACT       | ERISTICS            |      |       | •          | <b>hs: 3.0V to 3.6V</b><br>≤ TA ≤ +85°C for Indu<br>≤ TA ≤ +125°C for Ex |           |  |  |

|------------------|---------------------|------|-------|------------|--------------------------------------------------------------------------|-----------|--|--|

| Parameter<br>No. | Тур.                | Max. | Units | Conditions |                                                                          |           |  |  |

| Idle Current (II | dle) <sup>(1)</sup> |      |       |            |                                                                          |           |  |  |

| DC40d            | 2                   | 4    | mA    | -40°C      |                                                                          |           |  |  |

| DC40a            | 2                   | 4    | mA    | +25°C      | - 3.3V                                                                   | 10 MIPS   |  |  |

| DC40b            | 2                   | 4    | mA    | +85°C      | 5.3V                                                                     | TO MIES   |  |  |

| DC40c            | 2                   | 4    | mA    | +125°C     |                                                                          |           |  |  |

| DC42d            | 3                   | 6    | mA    | -40°C      |                                                                          |           |  |  |

| DC42a            | 3                   | 6    | mA    | +25°C      | - 3.3V                                                                   | 20 MIPS   |  |  |

| DC42b            | 3                   | 6    | mA    | +85°C      | 5.3V                                                                     | 20 MIF 3  |  |  |

| DC42c            | 3                   | 6    | mA    | +125°C     |                                                                          |           |  |  |

| DC44d            | 6                   | 12   | mA    | -40°C      |                                                                          |           |  |  |

| DC44a            | 6                   | 12   | mA    | +25°C      | - 3.3V                                                                   | 40 MIPS   |  |  |

| DC44b            | 6                   | 12   | mA    | +85°C      | 5.3V                                                                     | 40 MIF 3  |  |  |

| DC44c            | 6                   | 12   | mA    | +125°C     |                                                                          |           |  |  |

| DC45d            | 8                   | 15   | mA    | -40°C      |                                                                          |           |  |  |

| DC45a            | 8                   | 15   | mA    | +25°C      | - 3.3V                                                                   | 60 MIPS   |  |  |

| DC45b            | 8                   | 15   | mA    | +85°C      | 3.3V                                                                     | OU IVIIPS |  |  |

| DC45c            | 8                   | 15   | mA    | +125°C     | ]                                                                        |           |  |  |

| DC46d            | 10                  | 20   | mA    | -40°C      |                                                                          |           |  |  |

| DC46a            | 10                  | 20   | mA    | +25°C      | 3.3V                                                                     | 70 MIPS   |  |  |

| DC46b            | 10                  | 20   | mA    | +85°C      | ]                                                                        |           |  |  |

#### TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

#### TABLE 26-20: INTERNAL FRC ACCURACY

| АС СНА       | RACTERISTICS           |           | d <b>Operatir</b><br>g tempera | ture -40    | $^{\circ}C \leq TA \leq \cdot$ | <b>/ to 3.6V (unless other</b><br>+85°C for Industrial<br>+125°C for Extended | wise stated)   |  |  |

|--------------|------------------------|-----------|--------------------------------|-------------|--------------------------------|-------------------------------------------------------------------------------|----------------|--|--|

| Param<br>No. | Characteristic         | Min.      | Тур.                           | Max.        | Units                          | Conditions                                                                    |                |  |  |

| Internal     | FRC Accuracy @ FRC Fre | equency = | 7.37 MHz                       | <b>(</b> 1) |                                |                                                                               |                |  |  |

| F20a         | FRC                    | -2        | 0.5                            | +2          | %                              | $-40^\circ C \le T A \le -10^\circ C$                                         | VDD = 3.0-3.6V |  |  |

|              |                        | -0.9      | 0.5                            | +0.9        | %                              | $-10^{\circ}C \le TA \le +85^{\circ}C$                                        | VDD = 3.0-3.6V |  |  |

| F20b         | FRC                    | -2        | 1                              | +2          | %                              | $+85^{\circ}C \leq TA \leq +125^{\circ}C$                                     | VDD = 3.0-3.6V |  |  |

**Note 1:** Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### TABLE 26-21: INTERNAL LPRC ACCURACY

| AC CH        | ARACTERISTICS               |      | <b>I Operatin</b><br>g temperati | ure -40° | $C \le TA \le +$ | to 3.6V (unless otherv<br>85°C for Industrial<br>125°C for Extended | vise stated)   |  |

|--------------|-----------------------------|------|----------------------------------|----------|------------------|---------------------------------------------------------------------|----------------|--|

| Param<br>No. | Characteristic              | Min. | Тур.                             | Max.     | Units            | Conditions                                                          |                |  |

| LPRC         | @ 32.768 kHz <sup>(1)</sup> |      |                                  |          |                  |                                                                     |                |  |