Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-TQFP Exposed Pad                                                             |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs505-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

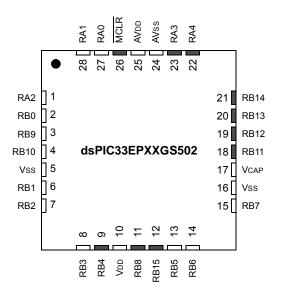

### **Pin Diagrams (Continued)**

### 28-Pin QFN-S, UQFN

| Pin | Pin Function                              | Pin | Pin Function                 |

|-----|-------------------------------------------|-----|------------------------------|

| 1   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         | 15  | PGEC1/AN21/SDA1/RP39/RB7     |

| 2   | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           |     | Vss                          |

| 3   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            | 17  | VCAP                         |

| 4   | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           | 18  | TMS/PWM3H/ <b>RP43</b> /RB11 |

| 5   | Vss                                       | 19  | TCK/PWM3L/RP44/RB12          |

| 6   | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  | 20  | PWM2H/ <b>RP45</b> /RB13     |

| 7   | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 | 21  | PWM2L/ <b>RP46</b> /RB14     |

| 8   | PGED2/AN18/DACOUT1/INT0/ <b>RP35</b> /RB3 | 22  | PWM1H/RA4                    |

| 9   | PGEC2/ADTRG31/EXTREF1/RP36/RB4            | 23  | PWM1L/RA3                    |

| 10  | Vdd                                       | 24  | AVss                         |

| 11  | PGED3/SDA2/FLT31/RP40/RB8                 | 25  | AVdd                         |

| 12  | PGEC3/SCL2/ <b>RP47</b> /RB15             | 26  | MCLR                         |

| 13  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         | 27  | AN0/PGA1P1/CMP1A/RA0         |

| 14  | PGED1/TDI/AN20/SCL1/ <b>RP38</b> /RB6     | 28  | AN1/PGA1P2/PGA2P1/CMP1B/RA1  |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "Multi-Tool Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

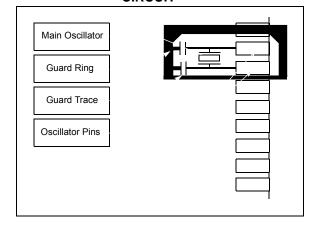

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

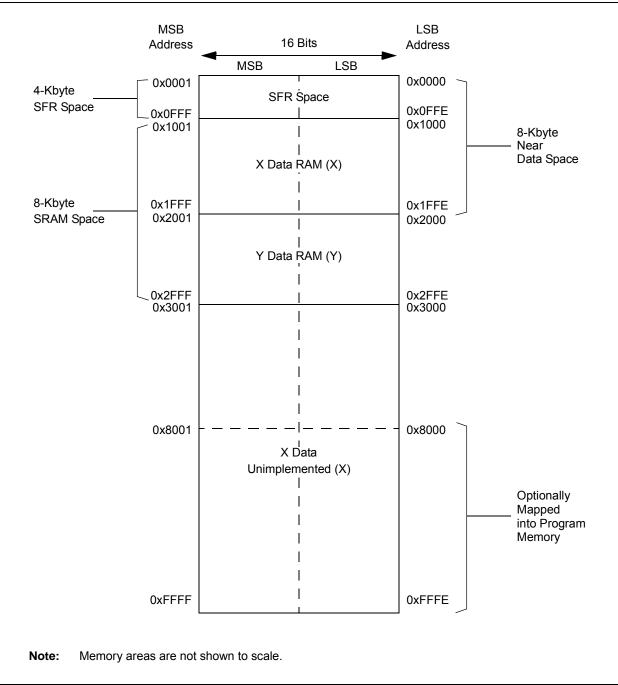

### 4.3 Data Address Space

The dsPIC33EPXXGS50X family CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps are shown in Figure 4-6 through Figure 4-8.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes or 32K words.

The lower half of the data memory space (i.e., when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV).

dsPIC33EPXXGS50X family devices implement up to 12 Kbytes of data memory. If an EA points to a location outside of this area, an all-zero word or byte is returned.

### 4.3.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

### 4.3.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXGS50X family instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through wordaligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.3.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXGS50X family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.3.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

#### FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

#### TABLE 4-9: **PWM GENERATOR 2 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15                                                                                        | Bit 14                                          | Bit 13  | Bit 12                                                                                             | Bit 11    | Bit 10         | Bit 9         | Bit 8          | Bit 7         | Bit 6        | Bit 5         | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|---------|----------------------------------------------------------------------------------------------------|-----------|----------------|---------------|----------------|---------------|--------------|---------------|----------|----------|----------|----------|----------|---------------|

| PWMCON2     | 0C40  | FLTSTAT                                                                                       | CLSTAT                                          | TRGSTAT | FLTIEN                                                                                             | CLIEN     | TRGIEN         | ITB           | MDCS           | DTC1          | DTC0         | —             | -        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON2      | 0C42  | PENH                                                                                          | PENL                                            | POLH    | POLL                                                                                               | PMOD1     | PMOD0          | OVRENH        | OVRENL         | OVRDAT1       | OVRDAT0      | FLTDAT1       | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON2     | 0C44  | IFLTMOD                                                                                       | CLSRC4                                          | CLSRC3  | C3 CLSRC2 CLSRC1 CLSRC0 CLPOL CLMOD FLTSRC4 FLTSRC3 FLTSRC2 FLTSRC1 FLTSRC0 FLTPOL FLTMOD1 FLTMOD0 |           |                |               |                |               |              | 00F8          |          |          |          |          |          |               |

| PDC2        | 0C46  |                                                                                               | PWM2 Generator Duty Cycle Register (PDC2<15:0>) |         |                                                                                                    |           |                |               |                |               |              | 0000          |          |          |          |          |          |               |

| PHASE2      | 0C48  |                                                                                               |                                                 |         |                                                                                                    | F         | WM2 Primary    | Phase-Shift c | or Independen  | t Time Base   | e Period Reg | gister (PHASE | 2<15:0>) |          |          |          |          | 0000          |

| DTR2        | 0C4A  | PWM2 Dead-Time Register (DTR2<13:0>)                                                          |                                                 |         |                                                                                                    |           |                |               |                | 0000          |              |               |          |          |          |          |          |               |

| ALTDTR2     | 0C4C  | —      PWM2 Alternate Dead-Time Register (ALTDTR2<13:0>)                                      |                                                 |         |                                                                                                    |           |                |               |                |               | 0000         |               |          |          |          |          |          |               |

| SDC2        | 0C4E  | PWM2 Secondary Duty Cycle Register (SDC2<15:0>)                                               |                                                 |         |                                                                                                    |           |                |               |                |               | 0000         |               |          |          |          |          |          |               |

| SPHASE2     | 0C50  |                                                                                               |                                                 |         |                                                                                                    |           |                | PWM2 Secon    | dary Phase-Sl  | hift Register | r (SPHASE2   | <15:0>)       |          |          |          |          |          | 0000          |

| TRIG2       | 0C52  |                                                                                               |                                                 |         |                                                                                                    | PWM2 Pri  | mary Trigger C | Compare Value | e Register (TR | GCMP<12:      | :0>)         |               |          |          | _        | _        | _        | 0000          |

| TRGCON2     | 0C54  | TRGDIV3                                                                                       | TRGDIV2                                         | TRGDIV1 | TRGDIV0                                                                                            | -         | _              | _             | _              | DTM           | _            | TRGSTRT5      | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG2      | 0C56  |                                                                                               |                                                 |         |                                                                                                    | PWM2 Seco | ndary Trigger  | Compare Valu  | e Register (S  | TRGCMP<1      | 12:0>)       |               |          |          | —        | —        | _        | 0000          |

| PWMCAP2     | 0C58  |                                                                                               |                                                 |         |                                                                                                    | PWM2 P    | rimary Time B  | ase Capture F | Register (PWN  | /ICAP<12:0    | >)           |               |          |          | _        | _        | _        | 0000          |

| LEBCON2     | 0C5A  | PHR                                                                                           | PHF                                             | PLR     | PLF                                                                                                | FLTLEBEN  | CLLEBEN        | _             | _              | _             | _            | BCH           | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2     | 0C5C  | —      —      PWM2 Leading-Edge Blanking Delay Register (LEB<8:0>)     —      —      —      — |                                                 |         |                                                                                                    |           |                |               |                |               | 0000         |               |          |          |          |          |          |               |

| AUXCON2     | 0C5E  |                                                                                               |                                                 |         |                                                                                                    |           |                |               | 0000           |               |              |               |          |          |          |          |          |               |

|             |       | _                                                                                             | -                                               |         |                                                                                                    | BLANKSEL3 | -              | BLAINKSELT    | BLANKSELU      | _             | _            | UNUPSELS      | UNUPSEL2 | CHUPSELT | CHOPSELU | CHUPHEN  | CHUPLEN  | 0             |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-10: PWM GENERATOR 3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                                          | Bit 14                                                         | Bit 13  | Bit 12  | Bit 11                                                                                          | Bit 10         | Bit 9         | Bit 8          | Bit 7          | Bit 6       | Bit 5        | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|-----------------------------------------------------------------|----------------------------------------------------------------|---------|---------|-------------------------------------------------------------------------------------------------|----------------|---------------|----------------|----------------|-------------|--------------|----------|----------|----------|----------|----------|---------------|

| PWMCON3     | 0C60  | FLTSTAT                                                         | CLSTAT                                                         | TRGSTAT | FLTIEN  | CLIEN                                                                                           | TRGIEN         | ITB           | MDCS           | DTC1           | DTC0        | _            | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON3      | 0C62  | PENH                                                            | PENL                                                           | POLH    | POLL    | PMOD1 PMOD0 OVRENH OVRENL OVRDAT1 OVRDAT0 FLTDAT1 FLTDAT0 CLDAT1 CLDAT0 SWAP OSYNC              |                |               |                |                |             | OSYNC        | C000     |          |          |          |          |               |

| FCLCON3     | 0C64  | IFLTMOD                                                         | CLSRC4                                                         | CLSRC3  | CLSRC2  | CLSRC2 CLSRC1 CLSRC0 CLPOL CLMOD FLTSRC4 FLTSRC3 FLTSRC2 FLTSRC1 FLTSRC0 FLTPOL FLTMOD1 FLTMOD0 |                |               |                |                |             |              | 00F8     |          |          |          |          |               |

| PDC3        | 0C66  |                                                                 | PWM3 Generator Duty Cycle Register (PDC3<15:0>)                |         |         |                                                                                                 |                |               |                |                |             | 0000         |          |          |          |          |          |               |

| PHASE3      | 0C68  |                                                                 |                                                                |         |         | Р                                                                                               | WM3 Primary    | Phase-Shift o | r Independent  | Time Base      | Period Regi | ster (PHASE3 | <15:0>)  |          |          |          |          | 0000          |

| DTR3        | 0C6A  | — — PWM3 Dead-Time Register (DTR3<13:0>)                        |                                                                |         |         |                                                                                                 |                |               |                | 0000           |             |              |          |          |          |          |          |               |

| ALTDTR3     | 0C6C  | —      —      PWM3 Alternate Dead-Time Register (ALTDTR3<13:0>) |                                                                |         |         |                                                                                                 |                |               |                | 0000           |             |              |          |          |          |          |          |               |

| SDC3        | 0C6E  | PWM3 Secondary Duty Cycle Register (SDC3<15:0>)                 |                                                                |         |         |                                                                                                 |                |               |                |                | 0000        |              |          |          |          |          |          |               |

| SPHASE3     | 0C70  |                                                                 |                                                                |         |         |                                                                                                 | I              | PWM3 Second   | lary Phase-Sh  | ift Register ( | (SPHASE3<   | <15:0>)      |          |          |          |          |          | 0000          |

| TRIG3       | 0C72  |                                                                 |                                                                |         |         | PWM3 Pri                                                                                        | mary Trigger C | Compare Value | e Register (TR | GCMP<12:0      | )>)         |              |          |          | _        | _        | _        | 0000          |

| TRGCON3     | 0C74  | TRGDIV3                                                         | TRGDIV2                                                        | TRGDIV1 | TRGDIV0 | _                                                                                               | _              | _             | _              | DTM            | _           | TRGSTRT5     | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG3      | 0C76  |                                                                 |                                                                |         |         | PWM3 Seco                                                                                       | ndary Trigger  | Compare Valu  | e Register (S  | RGCMP<1        | 2:0>)       |              |          |          | _        | _        | _        | 0000          |

| PWMCAP3     | 0C78  |                                                                 |                                                                |         |         | PWM3 P                                                                                          | rimary Time B  | ase Capture F | Register (PWN  | ICAP<12:0>     | ·)          |              |          |          | -        | _        | _        | 0000          |

| LEBCON3     | 0C7A  | PHR                                                             | PHR PHF PLR PLF FLTLEBEN CLLEBEN BCH BCL BPHH BPHL BPLH BPLL 0 |         |         |                                                                                                 |                |               |                |                |             | 0000         |          |          |          |          |          |               |

| LEBDLY3     | 0C7C  | PWM3 Leading-Edge Blanking Delay Register (LEB<8:0>)            |                                                                |         |         |                                                                                                 |                |               |                |                | 0000        |              |          |          |          |          |          |               |

| AUXCON3     | 0C7E  | HRPDIS                                                          | HRDDIS                                                         | _       | -       |                                                                                                 |                |               |                |                |             | 0000         |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1

OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

### REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

bit 4-0

**PLLPRE<4:0>:** PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler) 11111 = Input divided by 33

•

00001 = Input divided by 3

00000 = Input divided by 2 (default)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- **2:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0           | U-0              | U-0              | U-0               | U-0              | U-0                | R/W-0   |  |

|--------------|---------------|------------------|------------------|-------------------|------------------|--------------------|---------|--|

| _            | —             | _                | —                | —                 | —                | _                  | PLLDIV8 |  |

| bit 15       |               |                  |                  |                   |                  |                    | bit 8   |  |

|              |               |                  |                  |                   |                  |                    |         |  |

| R/W-0        | R/W-0         | R/W-1            | R/W-1            | R/W-0             | R/W-0            | R/W-0              | R/W-0   |  |

|              |               |                  | PLLDI            | V<7:0>            |                  |                    |         |  |

| bit 7        |               |                  |                  |                   |                  |                    | bit 0   |  |

|              |               |                  |                  |                   |                  |                    |         |  |

| Legend:      |               |                  |                  |                   |                  |                    |         |  |

| R = Reada    | ble bit       | W = Writable     | bit              | U = Unimplen      | nented bit, read | d as '0'           |         |  |

| -n = Value a | at POR        | '1' = Bit is set |                  | '0' = Bit is clea | ared             | x = Bit is unknown |         |  |

|              |               |                  |                  |                   |                  |                    |         |  |

| bit 15-9     | Unimplemen    | ted: Read as '   | )'               |                   |                  |                    |         |  |

| bit 8-0      | PLLDIV<8:0>   | -: PLL Feedbac   | k Divisor bits ( | also denoted a    | is 'M', PLL mul  | tiplier)           |         |  |

|              | 111111111     | = 513            |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | 000110000=    | = 50 (default)   |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | •             |                  |                  |                   |                  |                    |         |  |

|              | • 000000010 = | = 4              |                  |                   |                  |                    |         |  |

|              | 00000010-     | <b>– –</b>       |                  |                   |                  |                    |         |  |

### REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

000000001 = 3 000000000 = 2

### 9.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

### 9.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral (for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

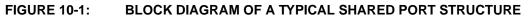

### 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS7000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 10.1 Parallel I/O (PIO) Ports

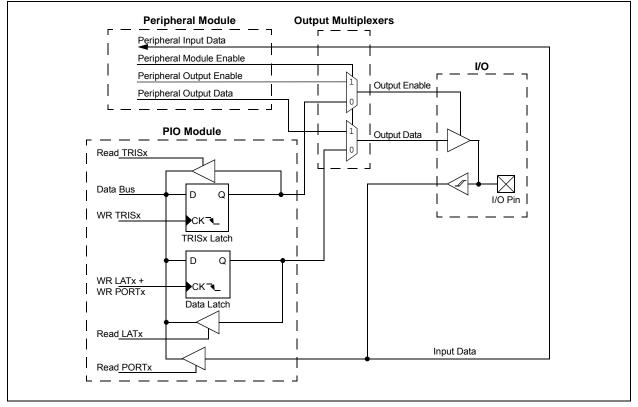

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 illus-trates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2013-2017 Microchip Technology Inc.

### REGISTER 10-17: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI2R7 | SYNCI2R6 | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 SYNCI2R<7:0>: Assign PWM Synchronization Input 2 to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 •

• 00000001 = Input tied to RP1 00000000 = Input tied to Vss

### 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1. T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 12-2.

### 12.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 13-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                 | R/W-0, HS               | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> |     | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable b | it                          |                    |

|-------------------|--------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared        | x = Bit is unknown |

bit 8 **IC32:** Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd ICx and even ICx form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

### bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- 0 = Input source is used to synchronize the input capture timer to a timer of another module (Synchronization mode)

### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

### REGISTER 15-22: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 5) (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator bits         11111 = Fault 31 (Default)         10001 = Reserved         10000 = Analog Comparator 4         01111 = Analog Comparator 3         01100 = Analog Comparator 2         01101 = Analog Comparator 1         01100 = Fault 12         01010 = Fault 11         01000 = Fault 12         01011 = Fault 11         01000 = Fault 12         01001 = Fault 10         01001 = Fault 5         00101 = Fault 4         00011 = Fault 3         00102 = Fault 4         00011 = Fault 1         00111 = Fault 1         00102 = Fault 1         00103 = Fault 4         00014 = Fault 5         0015         0015         0016         10000 = Fault 4         00011 = Fault 1         00012 = Fault 1         00014 = Fault 1         00015         0016         0017         10018         10019         119         119         119         1119         1119         1119         1119         1119 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

### REGISTER 15-23: STRIGX: PWMx SECONDARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 5)<sup>(1)</sup>

| R/W-0        | R/W-0       | R/W-0                                               | R/W-0           | R/W-0                              | R/W-0 | R/W-0           | R/W-0        |  |

|--------------|-------------|-----------------------------------------------------|-----------------|------------------------------------|-------|-----------------|--------------|--|

|              |             |                                                     | STRGC           | MP<12:5>                           |       |                 |              |  |

| bit 15       |             |                                                     |                 |                                    |       |                 | bit 8        |  |

| R/W-0        | R/W-0       | R/W-0                                               | R/W-0           | R/W-0                              | U-0   | U-0             | U-0          |  |

|              |             | STRGCMP<4:0                                         | >               |                                    |       | _               | _            |  |

| bit 7        |             |                                                     |                 |                                    |       |                 | bit (        |  |

| Legend:      |             |                                                     |                 |                                    |       |                 |              |  |

| R = Readab   | le bit      | W = Writable                                        | bit             | U = Unimplemented bit, read as '0' |       |                 |              |  |

| -n = Value a | t POR       | '1' = Bit is set                                    |                 | '0' = Bit is clea                  | ared  | x = Bit is unkr | iown         |  |

| bit 15-3     | When the se | <12:0>: Seconda<br>econdary PWMx<br>ger the ADC mod | functions in th | •                                  |       | contains the co | mpare values |  |

| bit 2-0      |             | nted: Read as '                                     |                 |                                    |       |                 |              |  |

**Note 1:** STRIGx cannot generate the PWM trigger interrupts.

### REGISTER 19-26: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

- 11111 = ADTRG31

- 11110 = Reserved

- 11101 = Reserved

- 11100 = PWM Generator 5 current-limit trigger

- 11011 = PWM Generator 4 current-limit trigger

- 11010 = PWM Generator 3 current-limit trigger

- 11001 = PWM Generator 2 current-limit trigger

- 11000 = PWM Generator 1 current-limit trigger

- 10111 = Output Compare 2 trigger

- 10110 = Output Compare 1 trigger 10101 = Reserved

- 10100 = Reserved

- 10011 = PWM Generator 5 secondary trigger

- 10010 = PWM Generator 4 secondary trigger

- 10001 = PWM Generator 3 secondary trigger

- 10000 = PWM Generator 2 secondary trigger

- 01111 = PWM Generator 1 secondary trigger

- 01110 = PWM secondary Special Event Trigger

- 01101 = Timer2 period match

- 01100 = Timer1 period match

- 01011 = Reserved

- 01010 = Reserved

- 01001 = PWM Generator 5 primary trigger

- 01000 = PWM Generator 4 primary trigger

- 00111 = PWM Generator 3 primary trigger

- 00110 = PWM Generator 2 primary trigger

- 00101 = PWM Generator 1 primary trigger

- 00100 = PWM Special Event Trigger

- 00011 = Reserved

- 00010 = Level software trigger

- 00001 = Common software trigger

- 00000 = No trigger is enabled

### REGISTER 19-29: ADCAL0H: ADC CALIBRATION REGISTER 0 HIGH

| R-0, HSC            | U-0                                                                                                                                                                        | U-0                                    | U-0              | r-0              | R/W-0            | R/W-0            | R/W-0            |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------------------|------------------|------------------|--|--|

| CAL3RDY             | —                                                                                                                                                                          | —                                      | —                | _                | CAL3DIFF         | CAL3EN           | CAL3RUN          |  |  |

| bit 15              |                                                                                                                                                                            |                                        |                  |                  |                  |                  | bit 8            |  |  |

|                     |                                                                                                                                                                            |                                        |                  |                  |                  |                  |                  |  |  |

| R-0, HSC            | U-0                                                                                                                                                                        | U-0                                    | U-0              | r-0              | R/W-0            | R/W-0            | R/W-0            |  |  |

| CAL2RDY             |                                                                                                                                                                            | —                                      |                  | _                | CAL2DIFF         | CAL2EN           | CAL2RUN          |  |  |

| bit 7               | ·                                                                                                                                                                          | ·                                      | •                |                  |                  |                  | bit 0            |  |  |

|                     |                                                                                                                                                                            |                                        |                  |                  |                  |                  |                  |  |  |

| Legend:             |                                                                                                                                                                            | r = Reserved                           | bit              | U = Unimpler     | nented bit, read | as '0'           |                  |  |  |

| R = Readabl         | e bit                                                                                                                                                                      | W = Writable                           | bit              | HSC = Hardw      | vare Settable/C  | earable bit      |                  |  |  |

| -n = Value at       | POR                                                                                                                                                                        | '1' = Bit is set                       |                  | '0' = Bit is cle | ared             | x = Bit is unkr  | nown             |  |  |

|                     |                                                                                                                                                                            |                                        |                  |                  |                  |                  |                  |  |  |

| bit 15              |                                                                                                                                                                            | Dedicated ADC                          |                  |                  | g bit            |                  |                  |  |  |

|                     |                                                                                                                                                                            | ed ADC Core 3 c                        |                  |                  |                  |                  |                  |  |  |

| hit 11 10           |                                                                                                                                                                            | ed ADC Core 3 c                        |                  | progress         |                  |                  |                  |  |  |

| bit 14-12<br>bit 11 | -                                                                                                                                                                          | nted: Read as '<br>/lust be written a  |                  |                  |                  |                  |                  |  |  |

| bit 10              |                                                                                                                                                                            | Dedicated ADC                          |                  | ntial Mada Cali  | ibration bit     |                  |                  |  |  |

|                     |                                                                                                                                                                            | ed ADC Core 3 v                        |                  |                  |                  |                  |                  |  |  |

|                     |                                                                                                                                                                            | d ADC Core 3 v                         |                  |                  | •                |                  |                  |  |  |

| bit 9               | CAL3EN: De                                                                                                                                                                 | edicated ADC C                         | ore 3 Calibratio | on Enable bit    | ·                |                  |                  |  |  |

|                     | 1 = Dedicate                                                                                                                                                               | ed ADC Core 3 o                        | calibration bits | (CALxRDY, CA     | LxDIFF and CA    | LxRUN) can b     | e accessed by    |  |  |

|                     | software                                                                                                                                                                   | e                                      |                  |                  |                  |                  |                  |  |  |

| 1.1.0               |                                                                                                                                                                            | ed ADC Core 3                          |                  |                  |                  |                  |                  |  |  |

| bit 8               |                                                                                                                                                                            | Dedicated ADC<br>it is set by soft     |                  |                  | ara 2 adibratia  | n avala ia atar  | tad: this hit is |  |  |

|                     |                                                                                                                                                                            | ically cleared by                      |                  |                  |                  | IT CYCLE IS SLAI | teu, this bit is |  |  |

|                     |                                                                                                                                                                            | e can start the n                      |                  | cycle            |                  |                  |                  |  |  |

| bit 7               | CAL2RDY:                                                                                                                                                                   | Dedicated ADC                          | Core 2 Calibra   | tion Status Flag | g bit            |                  |                  |  |  |

|                     |                                                                                                                                                                            | ed ADC Core 2 c                        |                  |                  |                  |                  |                  |  |  |

|                     |                                                                                                                                                                            | ed ADC Core 2 c                        |                  | progress         |                  |                  |                  |  |  |

| bit 6-4             | -                                                                                                                                                                          | nted: Read as '                        |                  |                  |                  |                  |                  |  |  |

| bit 3               |                                                                                                                                                                            | /lust be written a                     |                  |                  |                  |                  |                  |  |  |

| bit 2               |                                                                                                                                                                            | Dedicated ADC                          |                  |                  |                  |                  |                  |  |  |

|                     | <ul> <li>1 = Dedicated ADC Core 2 will be calibrated in Differential Input mode</li> <li>0 = Dedicated ADC Core 2 will be calibrated in Single-Ended Input mode</li> </ul> |                                        |                  |                  |                  |                  |                  |  |  |

| bit 1               |                                                                                                                                                                            | edicated ADC C                         |                  | -                |                  |                  |                  |  |  |

| bit i               |                                                                                                                                                                            | ed ADC Core 2 (                        |                  |                  | LxDIFF and CA    | LxRUN) can b     | e accessed by    |  |  |

|                     | software                                                                                                                                                                   |                                        |                  | (,,              |                  | ,,               |                  |  |  |

|                     | 0 = Dedicate                                                                                                                                                               | ed ADC Core 2                          | calibration bits | are disabled     |                  |                  |                  |  |  |

| bit 0               |                                                                                                                                                                            | Dedicated ADC                          |                  |                  |                  |                  |                  |  |  |

|                     |                                                                                                                                                                            | it is set by soft                      |                  | icated ADC Co    | ore 2 calibratio | n cycle is star  | ted; this bit is |  |  |

|                     |                                                                                                                                                                            | ically cleared by<br>e can start the n |                  | cycle            |                  |                  |                  |  |  |

|                     |                                                                                                                                                                            |                                        |                  | 0,000            |                  |                  |                  |  |  |

### REGISTER 19-32: ADCMPxENL: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER LOW (x = 0 or 1)

| R/W-0  | R/W-0          | R/W-0 | R/W-0         | R/W-0   | R/W-0 | R/W-0         | R/W-0          |

|--------|----------------|-------|---------------|---------|-------|---------------|----------------|

|        |                |       | CMPEN         | N<15:8> |       |               |                |

| bit 15 |                |       |               |         |       |               | bit 8          |

| DANIO  | <b>D</b> /// 0 | DAMO  | <b>D</b> 4440 | DAMO    |       | <b>D</b> 1110 | <b>D</b> /// 0 |

| R/W/0  | R/W-0          | R/W-0 | R/W-0         | R/W-0   | R/W-0 | R/W-0         | R/W-0          |

|        |                |       | CMPE          | N<7:0>  |       |               |                |

| bit 7  |                |       |               |         |       |               | bit 0          |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CMPEN<15:0>: Comparator Enable for Corresponding Input Channels bits

0 = Conversion result for corresponding channel is not used by the comparator

### REGISTER 19-33: ADCMPxENH: ADC DIGITAL COMPARATOR x CHANNEL ENABLE REGISTER HIGH (x = 0 or 1)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | CMPEN | <21:16> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0

CMPEN<21:16>: Comparator Enable for Corresponding Input Channels bits

0 = Conversion result for corresponding channel is not used by the comparator

<sup>1 =</sup> Conversion result for corresponding channel is used by the comparator

<sup>1 =</sup> Conversion result for corresponding channel is used by the comparator

### REGISTER 20-1: CMPxCON: COMPARATOR x CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0 |

|--------|-----|---------|---------|---------|--------|---------|-------|

| CMPON  | —   | CMPSIDL | HYSSEL1 | HYSSEL0 | FLTREN | FCLKSEL | DACOE |

| bit 15 |     |         |         |         |        |         | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | HC-0, HS | R/W-0  | R/W-0  | R/W-0 |

|--------|--------|--------|--------|----------|--------|--------|-------|

| INSEL1 | INSEL0 | EXTREF | HYSPOL | CMPSTAT  | ALTINP | CMPPOL | RANGE |

| bit 7  |        |        |        |          |        |        | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit  |                    |

|-------------------|-----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | CMPON: Comparator Operating Mode bit                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------|

|           | 1 = Comparator module is enabled                                                                              |

|           | 0 = Comparator module is disabled (reduces power consumption)                                                 |

| bit 14    | Unimplemented: Read as '0'                                                                                    |

| bit 13    | CMPSIDL: Comparator Stop in Idle Mode bit                                                                     |

|           | 1 = Discontinues module operation when device enters Idle mode.                                               |

|           | 0 = Continues module operation in Idle mode                                                                   |

|           | If a device has multiple comparators, any CMPSIDL bit set to '1' disables all comparators while in Idle mode. |

| bit 12-11 | HYSSEL<1:0>: Comparator Hysteresis Select bits                                                                |

|           | 11 = 20 mV hysteresis                                                                                         |

|           | 10 = 10  mV hysteresis                                                                                        |

|           | 01 = 5 mV hysteresis<br>00 = No hysteresis is selected                                                        |

| bit 10    | FLTREN: Digital Filter Enable bit                                                                             |

|           | 1 = Digital filter is enabled                                                                                 |

|           | 0 = Digital filter is disabled                                                                                |

| bit 9     | FCLKSEL: Digital Filter and Pulse Stretcher Clock Select bit                                                  |

|           | 1 = Digital filter and pulse stretcher operate with the PWM clock                                             |

|           | 0 = Digital filter and pulse stretcher operate with the system clock                                          |

| bit 8     | DACOE: DACx Output Enable bit                                                                                 |

|           | 1 = DACx analog voltage is connected to the DACOUTx pin <sup>(1)</sup>                                        |

|           | 0 = DACx analog voltage is not connected to the DACOUTx pin                                                   |

| bit 7-6   | INSEL<1:0>: Input Source Select for Comparator bits                                                           |

|           | If ALTINP = 0, Select from Comparator Inputs:                                                                 |

|           | 11 = Selects CMPxD input pin<br>10 = Selects CMPxC input pin                                                  |

|           | 01 = Selects CMPxB input pin                                                                                  |

|           | 00 = Selects CMPxA input pin                                                                                  |

|           | If ALTINP = 1, Select from Alternate Inputs:                                                                  |

|           | 11 = Reserved                                                                                                 |

|           | 10 = Reserved<br>01 = Selects PGA2 output                                                                     |

|           | 01 = Selects PGA2 output<br>00 = Selects PGA1 output                                                          |

| •• · ·    |                                                                                                               |

**Note 1:** DACOUTx can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DACx output by setting their respective DACOE bit.

### 25.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 25.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 25.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.