Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs506t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

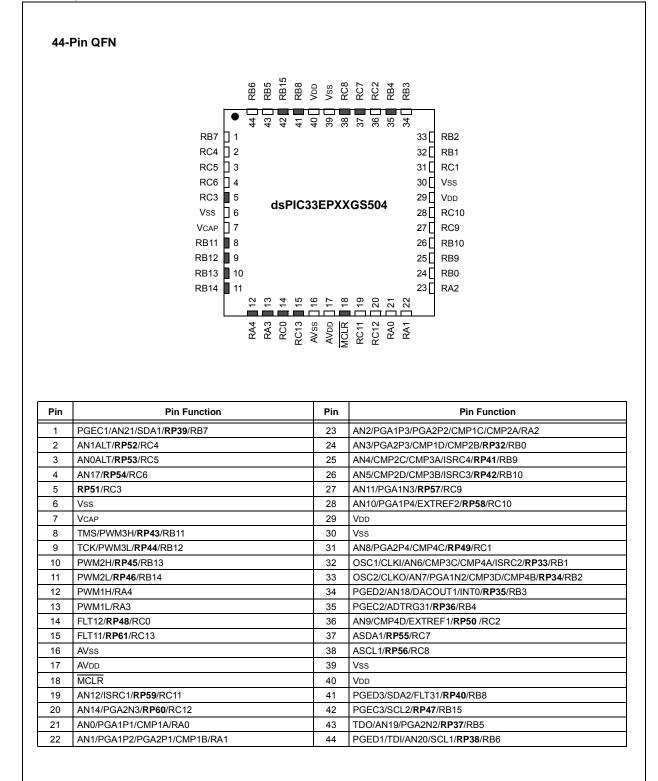

### **Pin Diagrams (Continued)**

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXGS50X Digital Signal Controller (DSC) devices.

dsPIC33EPXXGS50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

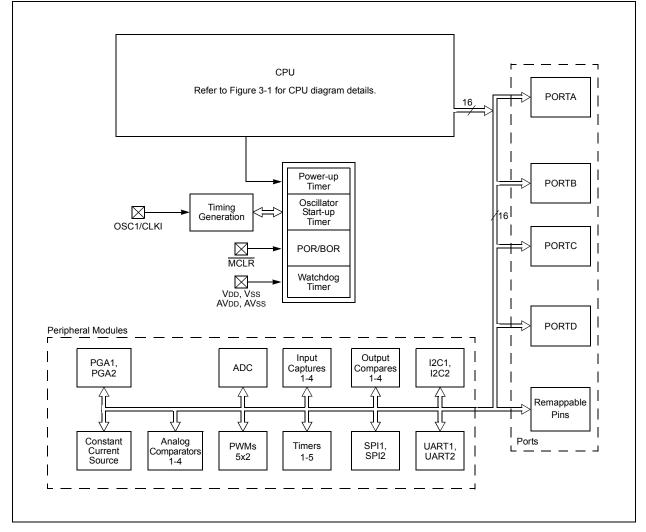

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EPXXGS50X FAMILY BLOCK DIAGRAM

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name <sup>(1)</sup>   | Pin<br>Type | Buffer<br>Type   | PPS        | Description                                                                                                                                                                                                    |

|---------------------------|-------------|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN21<br>AN0ALT-AN1ALT |             | Analog<br>Analog | No<br>No   | Analog input channels.<br>Alternate analog input channels.                                                                                                                                                     |

| CLKI                      | I           | ST/<br>CMOS      | No         | External clock source input. Always associated with OSC1 pin function Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |

| CLKO                      | 0           | —                | No         | Always associated with OSC2 pin function.                                                                                                                                                                      |

| OSC1                      | I           | ST/<br>CMOS      | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                |

| OSC2                      | I/O         | —                | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                       |

| REFCLKO                   | 0           | _                | Yes        | Reference clock output.                                                                                                                                                                                        |

| IC1-IC4                   | 1           | ST               | Yes        | Capture Inputs 1 through 4.                                                                                                                                                                                    |

| OCFA                      | 1           | ST               | Yes        | Compare Fault A input (for compare channels).                                                                                                                                                                  |

| OC1-OC4                   | Ó           | _                | Yes        | Compare Outputs 1 through 4.                                                                                                                                                                                   |

| INT0                      | 1           | ST               | No         | External Interrupt 0.                                                                                                                                                                                          |

| INT1                      | I           | ST               | Yes        | External Interrupt 1.                                                                                                                                                                                          |

| INT2                      | I           | ST               | Yes        | External Interrupt 2.                                                                                                                                                                                          |

| INT4                      | Ι           | ST               | No         | External Interrupt 4.                                                                                                                                                                                          |

| RA0-RA4                   | I/O         | ST               | No         | PORTA is a bidirectional I/O port.                                                                                                                                                                             |

| RB0-RB15                  | I/O         | ST               | No         | PORTB is a bidirectional I/O port.                                                                                                                                                                             |

| RC0-RC15                  | I/O         | ST               | No         | PORTC is a bidirectional I/O port.                                                                                                                                                                             |

| RD0-RD15                  | I/O         | ST               | No         | PORTD is a bidirectional I/O port.                                                                                                                                                                             |

| T1CK                      | 1           | ST               | Yes        | Timer1 external clock input.                                                                                                                                                                                   |

| T2CK                      |             | ST               | Yes        | Timer2 external clock input.                                                                                                                                                                                   |

| T3CK                      | İ           | ST               | Yes        | Timer3 external clock input.                                                                                                                                                                                   |

| T4CK                      | I           | ST               | No         | Timer4 external clock input.                                                                                                                                                                                   |

| T5CK                      | I.          | ST               | No         | Timer5 external clock input.                                                                                                                                                                                   |

| U1CTS                     | I           | ST               | Yes        | UART1 Clear-to-Send.                                                                                                                                                                                           |

| U1RTS                     | 0           | _                | Yes        | UART1 Request-to-Send.                                                                                                                                                                                         |

| U1RX                      | I           | ST               | Yes        | UART1 receive.                                                                                                                                                                                                 |

| U1TX                      | 0           | —                | Yes        | UART1 transmit.                                                                                                                                                                                                |

| BCLK1                     | 0           | ST               | Yes        | UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                                                                     |

| U2CTS                     | I           | ST               | Yes        |                                                                                                                                                                                                                |

| U2RTS                     | 0           | —                |            | UART2 Request-to-Send.                                                                                                                                                                                         |

| U2RX                      |             | ST               |            | UART2 receive.                                                                                                                                                                                                 |

| U2TX                      | 0           |                  | Yes        | UART2 transmit.                                                                                                                                                                                                |

| BCLK2                     | 0           | ST               | Yes        | UART2 IrDA baud clock output.                                                                                                                                                                                  |

| SCK1                      | 1/0         | ST               | Yes        | Synchronous serial clock input/output for SPI1.                                                                                                                                                                |

| SDI1                      |             | ST               | Yes        | SPI1 data in.                                                                                                                                                                                                  |

| SDO1<br>SS1               | 0<br>I/O    | ST               | Yes<br>Yes | SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                                                                                               |

| SCK2                      | I/O         | ST               | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                                                |

| SDI2                      | 1           | ST               | Yes        | SPI2 data in.                                                                                                                                                                                                  |

| SDO2                      | 0           |                  | Yes        | SPI2 data ini.<br>SPI2 data out.                                                                                                                                                                               |

| <u>SS2</u>                | 1/0         | ST               | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                 |

| Legend: CMOS = C          | _           |                  |            |                                                                                                                                                                                                                |

| ST = Schm<br>PPS = Peri   | itt Trigg   | er input v       | vith CN    |                                                                                                                                                                                                                |

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are dedicated on 64-pin devices.

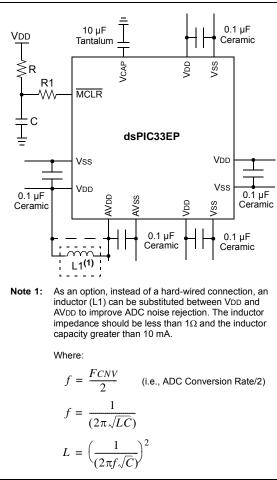

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (<0.5  $\Omega$ ) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu F$  (10  $\mu F$  is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 26.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 23.4 "On-Chip Voltage Regulator"** for details.

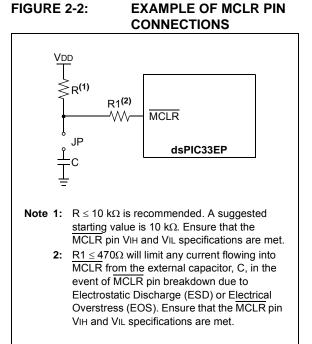

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

| 7                          | GOTO Instruction                                      | 0x000000                         |

|----------------------------|-------------------------------------------------------|----------------------------------|

|                            | Reset Address                                         | 0x000002                         |

| Ð                          | Interrupt Vector Table                                | 0x000004<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22,207 instructions) | 0x000200<br>0x00AF7E             |

| er Mem                     | Device Configuration                                  | 0x00AF80<br>0x00AFFE             |

| Use                        |                                                       | 0x00B000                         |

|                            | Unimplemented                                         |                                  |

|                            | (Read '0's)                                           |                                  |

|                            | Reserved                                              | 0x7FFFFE<br>0x800000<br>0x800E46 |

|                            | Calibration Data                                      | 0x800E48                         |

|                            | Reserved                                              | 0x800E78<br>0x800E7A<br>0x800EFE |

| Configuration Memory Space | UDID                                                  | 0x800F00<br>0x800F08<br>0x800F0A |

| nory S                     | Reserved                                              | 0x800F7E                         |

| n Mer                      | User OTP Memory                                       | 0x800F80<br>0x800FFC             |

| Iratio                     | Reserved                                              | 0x801000                         |

| onfigu                     | Write Latches                                         | 0xF9FFFE<br>0xFA0000             |

| ŏ                          |                                                       | 0xFA0002<br>0xFA0004             |

|                            | Reserved                                              |                                  |

|                            | DEVID                                                 | 0xFEFFFE<br>0xFF0000             |

|                            | Reserved                                              | 0xFF0002<br>0xFF0004             |

| _                          |                                                       | 0xFFFFFE                         |

Note: Memory areas are not shown to scale.

#### TABLE 4-16: ADC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                | Bit 14                | Bit 13                | Bit 12                | Bit 11                 | Bit 10                | Bit 9                 | Bit 8                 | Bit 7                 | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                  | Bit 0                  | All<br>Resets |

|-------------|-------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|---------------|

| ADCON1L     | 0300  | ADON                  | _                     | ADSIDL                | _                     | _                      | _                     | _                     | _                     | _                     | _                     | _                     | _                     | _                     | -                     | -                      | _                      | 0000          |

| ADCON1H     | 0302  | 1                     | -                     | -                     | -                     | _                      | -                     | -                     | -                     | FORM                  | SHRRES1               | SHRRES0               | -                     | -                     | -                     | -                      | -                      | 0060          |

| ADCON2L     | 0304  | REFCIE                | REFERCIE              | -                     | EIEN                  | _                      | SHREISEL2             | SHREISEL1             | SHREISEL0             | _                     | SHRADCS6              | SHRADCS5              | SHRADCS4              | SHRADCS3              | SHRADCS2              | SHRADCS1               | SHRADCS0               | 0000          |

| ADCON2H     | 0306  | REFRDY                | REFERR                |                       | _                     | _                      | -                     | SHRSAMC9              | SHRSAMC8              | SHRSAMC7              | SHRSAMC6              | SHRSAMC5              | SHRSAMC4              | SHRSAMC3              | SHRSAMC2              | SHRSAMC1               | SHRSAMC0               | 0000          |

| ADCON3L     | 0308  | REFSEL2               | REFSEL1               | REFSEL0               | SUSPEND               | SUSPCIE                | SUSPRDY               | SHRSAMP               | CNVRTCH               | SWLCTRG               | SWCTRG                | CNVCHSEL5             | CNVCHSEL4             | CNVCHSEL3             | CNVCHSEL2             | CNVCHSEL1              | CNVCHSEL0              | 0000          |

| ADCON3H     | 030A  | CLKSEL1               | CLKSEL0               | CLKDIV5               | CLKDIV4               | CLKDIV3                | CLKDIV2               | CLKDIV1               | CLKDIV0               | SHREN                 |                       | _                     |                       | C3EN                  | C2EN                  | C1EN                   | COEN                   | 0000          |

| ADCON4L     | 030C  | -                     | —                     |                       | -                     | SYNCTRG3               | SYNCTRG2              | SYNCTRG1              | SYNCTRG0              | -                     |                       | _                     |                       | SAMC3EN               | SAMC2EN               | SAMC1EN                | SAMC0EN                | 0000          |

| ADCON4H     | 030E  | -                     | _                     | -                     | —                     | _                      | -                     | -                     | —                     | C3CHS1                | C3CHS0                | C2CHS1                | C2CHS0                | C1CHS1                | C1CHS0                | C0CHS1                 | C0CHS0                 | 0000          |

| ADMOD0L     | 0310  | DIFF7                 | SIGN7                 | DIFF6                 | SIGN6                 | DIFF5                  | SIGN5                 | DIFF3                 | SIGN4                 | DIFF3                 | SIGN3                 | DIFF2                 | SIGN2                 | DIFF1                 | SIGN1                 | DIFF0                  | SIGN0                  | 0000          |

| ADMOD0H     | 0312  | DIFF15 <sup>(1)</sup> | SIGN15 <sup>(1)</sup> | DIFF14 <sup>(2)</sup> | SIGN14 <sup>(2)</sup> | DIFF13 <sup>(1)</sup>  | SIGN13 <sup>(1)</sup> | DIFF12 <sup>(2)</sup> | SIGN12 <sup>(2)</sup> | DIFF11 <sup>(2)</sup> | SIGN11 <sup>(2)</sup> | DIFF10 <sup>(2)</sup> | SIGN10 <sup>(2)</sup> | DIFF9 <sup>(2)</sup>  | SIGN9 <sup>(2)</sup>  | DIFF8 <sup>(2)</sup>   | SIGN8 <sup>(2)</sup>   | 0000          |

| ADMOD1L     | 0314  |                       | _                     | -                     | -                     | DIFF21                 | SIGN21                | DIFF20                | SIGN20                | DIFF19                | SIGN19                | DIFF18                | SIGN18                | DIFF17 <sup>(2)</sup> | SIGN17 <sup>(2)</sup> | DIFF16 <sup>(1)</sup>  | SIGN16 <sup>(1)</sup>  | 0000          |

| ADIEL       | 0320  | IE15 <sup>(1)</sup>   | IE14 <sup>(2)</sup>   | IE13 <sup>(1)</sup>   | IE12 <sup>(2)</sup>   | IE11 <sup>(2)</sup>    | IE10 <sup>(2)</sup>   | IE9 <sup>(2)</sup>    | IE8 <sup>(2)</sup>    | IE7                   | IE6                   | IE5                   | IE4                   | IE3                   | IE2                   | IE1                    | IE0                    | 0000          |

| ADIEH       | 0322  | -                     | _                     | -                     | -                     | -                      | -                     | -                     | -                     | -                     | -                     | IE21                  | IE20                  | IE19                  | IE18                  | IE17 <sup>(2)</sup>    | IE16 <sup>(1)</sup>    | 0000          |

| ADSTATL     | 0330  | AN15RDY(1)            | AN14RDY(2)            | AN13RDY(1)            | AN12RDY(2)            | AN11RDY <sup>(2)</sup> | AN10RDY(2)            | AN9RDY <sup>(2)</sup> | AN8RDY <sup>(2)</sup> | AN7RDY                | AN6RDY                | AN5RDY                | AN4RDY                | AN3RDY                | AN2RDY                | AN1RDY                 | ANORDY                 | 0000          |

| ADSTATH     | 0332  | _                     | —                     | _                     | _                     | _                      | _                     | -                     | -                     | _                     | _                     | AN21RDY               | AN20RDY               | AN19RDY               | AN18RDY               | AN17RDY <sup>(2)</sup> | AN16RDY <sup>(1)</sup> | 0000          |

| ADCMP0ENL   | 0338  | CMPEN15(1)            | CMPEN14(2)            | CMPEN13(1)            | CMPEN12(2)            | CMPEN11(2)             | CMPEN10(2)            | CMPEN9(2)             | CMPEN8(2)             | CMPEN7                | CMPEN6                | CMPEN5                | CMPEN4                | CMPEN3                | CMPEN2                | CMPEN1                 | CMPEN0                 | 0000          |

| ADCMP0ENH   | 033A  | _                     | —                     | _                     | _                     | _                      | _                     | -                     | -                     | _                     | _                     | CMPEN21               | CMPEN20               | CMPEN19               | CMPEN18               | CMPEN17(2)             | CMPEN16(1)             | 0000          |

| ADCMP0LO    | 033C  |                       |                       |                       |                       |                        |                       | AD                    | C Comparator          | ) Low Value Re        | egister               |                       |                       |                       |                       |                        |                        | 0000          |

| ADCMP0HI    | 033E  |                       |                       |                       |                       |                        |                       | AD                    | C Comparator (        | ) High Value R        | egister               |                       |                       |                       |                       |                        |                        | 0000          |

| ADCMP1ENL   | 0340  | CMPEN15(1)            | CMPEN14(2)            | CMPEN13(1)            | CMPEN12(2)            | CMPEN11(2)             | CMPEN10(2)            | CMPEN9(2)             | CMPEN8(2)             | CMPEN7                | CMPEN6                | CMPEN5                | CMPEN4                | CMPEN3                | CMPEN2                | CMPEN1                 | CMPEN0                 | 0000          |

| ADCMP1ENH   | 0342  | _                     | _                     | _                     | _                     | _                      | _                     | _                     | _                     | _                     | _                     | CMPEN21               | CMPEN20               | CMPEN19               | CMPEN18               | CMPEN17(2)             | CMPEN16(1)             | 0000          |

| ADCMP1LO    | 0344  |                       |                       |                       |                       |                        |                       | A                     | DC Comparator         | 1 Low Value Re        | gister                |                       |                       |                       |                       |                        |                        | 0000          |

| ADCMP1HI    | 0346  |                       |                       |                       |                       |                        |                       | A                     | DC Comparator         | 1 High Value Re       | egister               |                       |                       |                       |                       |                        |                        | 0000          |

| ADFLDAT     | 0368  |                       |                       |                       |                       |                        |                       |                       | ADC Filter 0 Re       | sults Data Regi       | ster                  |                       |                       |                       |                       |                        |                        | 0000          |

| ADFL1CON    | 036A  | FLEN                  | MODE1                 | MODE0                 | OVRSAM2               | OVRSAM1                | OVRSAM0               | IE                    | RDY                   | _                     | _                     | _                     | FLCHSEL4              | FLCHSEL3              | FLCHSEL2              | FLCHSEL1               | FLCHSEL0               | 0000          |

| ADFL1DAT    | 0368  |                       |                       |                       |                       |                        |                       |                       | ADC Filter 1 Re       | sults Data Reg        | ister                 |                       |                       |                       |                       |                        |                        | 0000          |

| ADFL0CON    | 036A  | FLEN                  | MODE1                 | MODE0                 | OVRSAM2               | OVRSAM1                | OVRSAM0               | IE                    | RDY                   | _                     | _                     | _                     | FLCHSEL4              | FLCHSEL3              | FLCHSEL2              | FLCHSEL1               | FLCHSEL0               | 0000          |

| ADTRIG0L    | 0380  | -                     | _                     | _                     |                       |                        | TRGSRC1<4:0           | )>                    |                       | _                     | _                     | _                     |                       |                       | TRGSRC0<4:0           | >                      |                        | 0000          |

| ADTRIG0H    | 0382  | _                     | _                     | -                     |                       |                        | TRGSRC3<4:0           | )>                    |                       | _                     | -                     | —                     |                       |                       | TRGSRC2<4:0           | >                      |                        | 0000          |

| ADTRIG1L    | 0384  | _                     | _                     | -                     |                       |                        | TRGSRC5<4:0           | )>                    |                       | _                     | _                     | _                     |                       |                       | TRGSRC4<4:0           | >                      |                        | 0000          |

| ADTRIG1H    | 0386  | _                     | _                     | _                     |                       |                        | TRGSRC7<4:0           | )>                    |                       | _                     | _                     | _                     |                       |                       | TRGSRC6<4:0           | >                      |                        | 0000          |

| ADTRIG2L    | 0388  | _                     | _                     | -                     |                       |                        | TRGSRC9<4:0           | )>                    |                       | _                     | _                     | _                     |                       |                       | TRGSRC8<4:0           | >                      |                        | 0000          |

| ADTRIG2H    | 038A  | _                     | _                     | _                     |                       |                        | TRGSRC11<4:           | 0>                    |                       | _                     | _                     | _                     |                       | T                     | RGSRC10<4:0           | >                      |                        | 0000          |

| ADTRIG3L    | 038C  | _                     | _                     | _                     |                       |                        | TRGSRC13<4:           | 0>                    |                       | _                     | _                     | _                     |                       | T                     | RGSRC12<4:0           | >                      |                        | 0000          |

| ADTRIG3H    | 038E  | _                     | _                     | _                     |                       |                        | TRGSRC15<4:           | 0>                    |                       | _                     | _                     | _                     |                       | T                     | RGSRC14<4:0           | >                      |                        | 0000          |

| ADTRIG4L    | 0390  | _                     | _                     | _                     |                       |                        | TRGSRC17<4:           | 0>                    |                       | _                     | _                     | _                     |                       | T                     | RGSRC16<4:0           | >                      |                        | 0000          |

| ADTRIG4H    | 0392  | _                     | _                     | _                     |                       |                        | TRGSRC19<4:           |                       |                       | _                     | _                     | _                     |                       |                       | RGSRC18<4:0           |                        |                        | 0000          |

| ADTRIG5L    | 0394  | _                     | _                     | _                     |                       |                        | TRGSRC21<4:           | -                     |                       | _                     | _                     | _                     |                       |                       | RGSRC20<4:0           |                        |                        | 0000          |

| ADCMP0CON   | 03A0  | _                     | _                     | _                     | CHNL4                 | CHNL3                  | CHNL2                 | CHNL1                 | CHNL0                 | CMPEN                 | IE                    | STAT                  | BTWN                  | HIHI                  | HILO                  | LOHI                   | LOLO                   | 0000          |

|             |       |                       |                       |                       | 1                     |                        | -                     |                       |                       |                       |                       | -                     |                       | 1                     | -                     |                        |                        | <u></u>       |

dsPIC33EPXXGS50X FAMILY

--- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

Implemented on dsPIC33EPXXGS506 devices only. Implemented on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices only. 2:

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD |       | —      | ADCMD | 0000          |

| PMD2        | 0762  |        | —      | —      | -      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | -      |       | —     | -      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3        | 0764  | Ι      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _      | _      | _     | I2C2MD | _     | 0000          |

| PMD4        | 0766  | Ι      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | _     | _      | _     | 0000          |

| PMD6        | 076A  | Ι      | _      | _      | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _     | _      | _     | 0000          |

| PMD7        | 076C  | Ι      | _      | _      | _      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | _     | _     | _      | _      | _     | PGA1MD | _     | 0000          |

| PMD8        | 076E  | _      | —      | _      | —      | _      | PGA2MD | ABGMD  | _      | _      | _     | —     | _      | _      | _     | CCSMD  |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: CONSTANT-CURRENT SOURCE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|-------|-------|----------|----------|----------|----------|----------|----------|---------------|

| ISRCCON     | 0500  | ISRCEN | _      |        | _      |        | OUTSEL2 | OUTSEL1 | OUTSEL0 | _     | _     | ISRCCAL5 | ISRCCAL4 | ISRCCAL3 | ISRCCAL2 | ISRCCAL1 | ISRCCAL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-25: PROGRAMMABLE GAIN AMPLIFIER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| PGA1CON     | 0504  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | _     | _     |       |       |       | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA1CAL     | 0506  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

| PGA2CON     | 0508  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | —     | —     | _     | —     | _     | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA2CAL     | 050A  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 8-7: LFSR: LINEAR FEEDBACK SHIFT REGISTER

| U-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               |       |                  |       | LFSR<14:8>       |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | LFS   | R<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set | t     | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15 Unimplemented: Read as '0'

bit 14-0 LFSR<14:0>: Pseudorandom Data bits

|                 | U-0                                                                                                                                              | U-0                                                                                                                                                               | R/W-0                                                                | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| _               | —                                                                                                                                                | —                                                                                                                                                                 | PWM5MD                                                               | PWM4MD            | PWM3MD           | PWM2MD          | PWM1MD |

| bit 15          |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 | bit 8  |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 |        |

| U-0             | U-0                                                                                                                                              | U-0                                                                                                                                                               | U-0                                                                  | U-0               | U-0              | U-0             | U-0    |

|                 |                                                                                                                                                  | _                                                                                                                                                                 | _                                                                    | <u> </u>          |                  |                 |        |

| bit 7           |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 | bit C  |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 |        |

| Legend:         |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 |        |

| R = Readabl     | le bit                                                                                                                                           | W = Writable I                                                                                                                                                    | oit                                                                  | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at   | t POR                                                                                                                                            | '1' = Bit is set                                                                                                                                                  |                                                                      | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 |        |

| bit 15-13       | Unimplement                                                                                                                                      | ted: Read as '0                                                                                                                                                   | )'                                                                   |                   |                  |                 |        |

| bit 12          | PWM5MD: P\                                                                                                                                       | WM5 Module D                                                                                                                                                      | isable bit                                                           |                   |                  |                 |        |

|                 |                                                                                                                                                  | odule is disable                                                                                                                                                  | -                                                                    |                   |                  |                 |        |

|                 |                                                                                                                                                  | odule is enable                                                                                                                                                   | -                                                                    |                   |                  |                 |        |

| bit 11          | PWM4MD: P\                                                                                                                                       | VM4 Module D                                                                                                                                                      | isable bit                                                           |                   |                  |                 |        |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                 |        |

|                 |                                                                                                                                                  | odule is disable                                                                                                                                                  |                                                                      |                   |                  |                 |        |

|                 | 0 = PWM4 mo                                                                                                                                      | odule is enable                                                                                                                                                   | d                                                                    |                   |                  |                 |        |

|                 | 0 = PWM4 mo<br><b>PWM3MD:</b> P\                                                                                                                 | odule is enable<br>VM3 Module D                                                                                                                                   | d<br>isable bit                                                      |                   |                  |                 |        |

|                 | 0 = PWM4 mo<br>PWM3MD: P\<br>1 = PWM3 mo                                                                                                         | odule is enable                                                                                                                                                   | d<br>isable bit<br>d                                                 |                   |                  |                 |        |

| bit 10<br>bit 9 | 0 = PWM4 mc<br>PWM3MD: P\<br>1 = PWM3 mc<br>0 = PWM3 mc                                                                                          | odule is enable<br>WM3 Module D<br>odule is disable                                                                                                               | d<br>isable bit<br>d                                                 |                   |                  |                 |        |

| bit 10          | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV                                                            | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable                                                                                            | d<br>isable bit<br>d<br>d<br>isable bit                              |                   |                  |                 |        |

| bit 10          | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV<br>1 = PWM2 mc                                             | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D                                                                            | d<br>isable bit<br>d<br>d<br>isable bit<br>d                         |                   |                  |                 |        |

| bit 10          | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV<br>1 = PWM2 mc<br>0 = PWM2 mc                              | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable                                                        | d<br>isable bit<br>d<br>d<br>isable bit<br>d<br>d                    |                   |                  |                 |        |

| bit 10<br>bit 9 | 0 = PWM4 mo<br>PWM3MD: PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br>PWM2MD: PV<br>1 = PWM2 mo<br>0 = PWM2 mo<br>0 = PWM2 mo<br>PWM1MD: PV<br>1 = PWM1 mo  | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable<br>odule is enable<br>WM1 Module D<br>odule is disable | d<br>isable bit<br>d<br>isable bit<br>d<br>d<br>isable bit<br>d      |                   |                  |                 |        |

| bit 10<br>bit 9 | 0 = PWM4 mo<br>PWM3MD: PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br>PWM2MD: PV<br>1 = PWM2 mo<br>0 = PWM2 mo<br>0 = PWM1 mo<br>0 = PWM1 mo<br>0 = PWM1 mo | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable<br>odule is enable<br>WM1 Module D                     | d<br>isable bit<br>d<br>isable bit<br>d<br>d<br>isable bit<br>d<br>d |                   |                  |                 |        |

| R/W-0           | R/W-0                                            | R/W-0                                                                                         | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|

| U1CTSR7         | U1CTSR6                                          | U1CTSR5                                                                                       | U1CTSR4          | U1CTSR3          | U1CTSR2          | U1CTSR1         | U1CTSR0 |

| bit 15          |                                                  |                                                                                               | ·                |                  |                  |                 | bit 8   |

|                 |                                                  |                                                                                               |                  |                  |                  |                 |         |

| R/W-0           | R/W-0                                            | R/W-0                                                                                         | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| U1RXR7          | U1RXR6                                           | U1RXR5                                                                                        | U1RXR4           | U1RXR3           | U1RXR2           | U1RXR1          | U1RXR0  |

| bit 7           |                                                  |                                                                                               |                  |                  |                  |                 | bit 0   |

| <u> </u>        |                                                  |                                                                                               |                  |                  |                  |                 |         |

| Legend:         |                                                  |                                                                                               |                  |                  |                  |                 |         |

| R = Readable    |                                                  | W = Writable                                                                                  |                  | •                | nented bit, read |                 |         |

| -n = Value at F | POR                                              | '1' = Bit is set                                                                              |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

| bit 7-0         | 10110100 =<br>•<br>•<br>00000001 =<br>00000000 = | Input tied to RF<br>Input tied to RF<br>Input tied to RF<br>Input tied to Vs<br>: Assign UART | 2180<br>21<br>35 | 1RX) to the Co   | rresponding RF   | n Pin bits      |         |

### REGISTER 10-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                          | R/W-0                              |                  | 5444.0           |                 |        |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|-----------------|--------|

|               |                                                                                                           |                                                                                                                | 10,00-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT6R7        | FLT6R6                                                                                                    | FLT6R5                                                                                                         | FLT6R4                             | FLT6R3           | FLT6R2           | FLT6R1          | FLT6R0 |

| bit 15        |                                                                                                           | ·                                                                                                              |                                    | ·                |                  |                 | bit 8  |

|               |                                                                                                           |                                                                                                                |                                    |                  |                  |                 |        |

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                          | R/W-0                              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT5R7        | FLT5R6                                                                                                    | FLT5R5                                                                                                         | FLT5R4                             | FLT5R3           | FLT5R2           | FLT5R1          | FLT5R0 |

| bit 7         |                                                                                                           |                                                                                                                |                                    |                  |                  |                 | bit C  |

| Legend:       |                                                                                                           |                                                                                                                |                                    |                  |                  |                 |        |

| R = Readable  | e bit                                                                                                     | W = Writable                                                                                                   | bit                                | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                                                                                               |                                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7-0       | 10110100 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>Assign PWM<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 5 (FLT5) | ) to the Corresp | oonding RPn Pi   | n bits          |        |

|               | •<br>•                                                                                                    | Input tied to RI                                                                                               |                                    |                  |                  |                 |        |

### REGISTER 10-18: RPINR42: PERIPHERAL PIN SELECT INPUT REGISTER 42

# 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1. T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 12-2.

## 12.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 12.1.1 KEY RESOURCES

- **"Timers"** (DS70362) in the *"dsPIC33/PIC24 Family Reference Manual"*

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 13.2 Input Capture Registers

### REGISTER 13-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER 13-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1 |                                                                                                                                                   |                                                                                                                                                       |                     |                                                          |                 |                |              |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------|-----------------|----------------|--------------|--|--|--|

| U-0                                                        | U-0                                                                                                                                               | R/W-0                                                                                                                                                 | R/W-0               | R/W-0                                                    | R/W-0           | U-0            | U-0          |  |  |  |

| —                                                          | —                                                                                                                                                 | ICSIDL                                                                                                                                                | ICTSEL2             | ICTSEL1                                                  | ICTSEL0         | _              | —            |  |  |  |

| bit 15                                                     |                                                                                                                                                   |                                                                                                                                                       |                     |                                                          |                 |                | bit 8        |  |  |  |

| U-0                                                        | R/W-0                                                                                                                                             | R/W-0                                                                                                                                                 | R-0, HC, HS         | R-0, HC, HS                                              | R/W-0           | R/W-0          | R/W-0        |  |  |  |

|                                                            | ICI1                                                                                                                                              | ICI0                                                                                                                                                  | ICOV                | ICBNE                                                    | ICM2            | ICM1           | ICM0         |  |  |  |

| bit 7                                                      |                                                                                                                                                   |                                                                                                                                                       |                     |                                                          |                 |                | bit          |  |  |  |

| Legend:                                                    |                                                                                                                                                   | HC = Hardward                                                                                                                                         | - Cloarable bit     | US - Hardwa                                              | re Settable bit |                |              |  |  |  |

| ∟ <b>egenu.</b><br>R = Readab                              | lo hit                                                                                                                                            |                                                                                                                                                       |                     |                                                          |                 | d as '0'       |              |  |  |  |

| -n = Value a                                               |                                                                                                                                                   | W = Writable bit<br>'1' = Bit is set                                                                                                                  |                     | U = Unimplemented bit, read as<br>'0' = Bit is cleared x |                 | x = Bit is unl | nown         |  |  |  |

|                                                            | IL FOR                                                                                                                                            | I - DILIS SEL                                                                                                                                         |                     |                                                          | areu            |                | (IIOWII      |  |  |  |

| bit 15-14                                                  | Unimplemer                                                                                                                                        | nted: Read as '0                                                                                                                                      | ,                   |                                                          |                 |                |              |  |  |  |

| bit 13                                                     | -                                                                                                                                                 |                                                                                                                                                       | in Idle Control bi  | t                                                        |                 |                |              |  |  |  |

|                                                            |                                                                                                                                                   | oture will halt in (                                                                                                                                  |                     | -                                                        |                 |                |              |  |  |  |

|                                                            |                                                                                                                                                   |                                                                                                                                                       | e to operate in C   | PU Idle mode                                             |                 |                |              |  |  |  |