Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs506t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

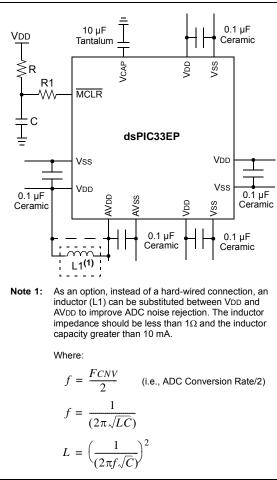

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (<0.5  $\Omega$ ) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu F$  (10  $\mu F$  is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 26.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 23.4 "On-Chip Voltage Regulator"** for details.

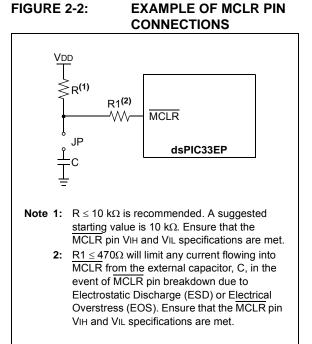

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

**CORCON: CORE CONTROL REGISTER**

REGISTER 3-2:

| R/W-0           | U-0                            | R/W-0                              | R/W-0                             | R/W-0                | R-0             | R-0             | R-0   |

|-----------------|--------------------------------|------------------------------------|-----------------------------------|----------------------|-----------------|-----------------|-------|

| VAR             |                                | US1                                | US0                               | EDT <sup>(1)</sup>   | DL2             | DL1             | DL0   |

| bit 15          |                                |                                    |                                   |                      |                 |                 | bit   |

| R/W-0           | R/W-0                          | R/W-1                              | R/W-0                             | R/C-0                | R-0             | R/W-0           | R/W-0 |

| SATA            | SATB                           | SATDW                              | ACCSAT                            | IPL3 <sup>(2)</sup>  | SFA             | RND             | IF    |

| bit 7           | OAID                           | OAIDW                              | ACCOAL                            | 11 2011              |                 | THE             | bit   |

| Legend:         |                                | C = Clearable                      | - hit                             |                      |                 |                 |       |

| R = Readable    | bit                            | W = Writable                       |                                   | U = Unimpler         | mented bit, rea | d as '0'        |       |

| -n = Value at F |                                | '1' = Bit is set                   |                                   | '0' = Bit is cle     |                 | x = Bit is unkn | iown  |

|                 |                                | 1 - Dit 13 301                     | •                                 |                      | arcu            |                 | lowin |

| bit 15          |                                | •                                  | ocessing Later                    |                      |                 |                 |       |

|                 |                                | • •                                | essing is enab<br>sing is enabled |                      |                 |                 |       |

| bit 14          | Unimplemen                     | ted: Read as '                     | 0'                                |                      |                 |                 |       |

| bit 13-12       | -                              |                                    | igned/Signed                      | Control bits         |                 |                 |       |

|                 | 11 = Reserve                   |                                    | 0 0                               |                      |                 |                 |       |

|                 |                                |                                    | are mixed-sigi                    | า                    |                 |                 |       |

|                 |                                | gine multiplies<br>gine multiplies |                                   |                      |                 |                 |       |

| bit 11          | EDT: Early DO                  | Loop Termina                       | ation Control b                   | it(1)                |                 |                 |       |

|                 | 1 = Terminate<br>0 = No effect | es executing Do                    | o loop at the e                   | nd of current lo     | oop iteration   |                 |       |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                       | Level Status bi                   | ts                   |                 |                 |       |

|                 | 111 <b>= 7</b> do <b>lo</b>    | ops are active                     |                                   |                      |                 |                 |       |

|                 | •                              |                                    |                                   |                      |                 |                 |       |

|                 | •                              |                                    |                                   |                      |                 |                 |       |

|                 | 001 = 1 DO lo                  | op is active<br>ops are active     |                                   |                      |                 |                 |       |

| bit 7           |                                | Saturation En                      |                                   |                      |                 |                 |       |

|                 |                                | Itor A saturatio                   |                                   |                      |                 |                 |       |

|                 |                                | itor A saturatio                   |                                   |                      |                 |                 |       |

| bit 6           | SATB: ACCB                     | Saturation En                      | able bit                          |                      |                 |                 |       |

|                 |                                | itor B saturatio                   |                                   |                      |                 |                 |       |

| bit 5           | SATDW: Data                    | a Space Write                      | from DSP Eng                      | ine Saturation       | Enable bit      |                 |       |

|                 | 1 = Data Spac                  | ce write satura                    | tion is enabled                   | l                    |                 |                 |       |

| bit 4           | -                              |                                    | ration Mode S                     |                      |                 |                 |       |

|                 |                                | ration (super s<br>ration (normal  |                                   |                      |                 |                 |       |

| L:1 0           |                                | •                                  | Level Status b                    | <sub>oit 3</sub> (2) |                 |                 |       |

| bit 3           |                                | contraped monity                   |                                   |                      |                 |                 |       |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

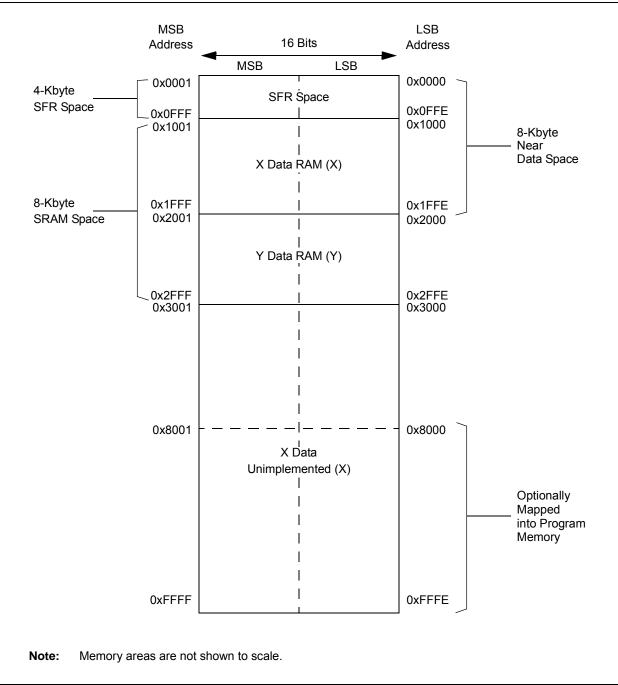

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXGS50X family architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXGS50X family devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.9 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to permit access to calibration data and Device ID sections of the configuration memory space.

The program memory maps for the dsPIC33EP16/ 32GS50X and dsPIC33EP64GS50X devices not operating in Dual Partition mode, are shown in Figure 4-1 through Figure 4-3.

The dsPIC33EP64GS50X devices can operate in a Dual Partition Flash Program Memory mode, where the user program Flash memory is arranged as two separate address spaces, one for each of the Flash partitions. The Active Partition always starts at address, 0x000000, and contains half of the available Flash memory (32K). The Inactive Partition always starts at address, 0x400000, and implements the remaining half of Flash memory. As shown in Figure 4-4, the Active and Inactive Partitions are identical and both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT if enabled) and the Flash Configuration Words.

### 4.2 Unique Device Identifier (UDID)

All (16-bit devices) family devices are individually encoded during final manufacturing with a Unique Device Identifier or UDID. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a requirement. It may also be used by the application manufacturer for any number of things that may require unique identification, such as:

- Tracking the device

- Unique serial number

- Unique security key

The UDID comprises five 24-bit program words. When taken together, these fields form a unique 120-bit identifier.

The UDID is stored in five read-only locations, located between 800F00h and 800F08h in the device configuration space. Table 4-1 lists the addresses of the identifier words and shows their contents.

| Name  | Address | Bits 23:16 Bits 15:8 Bits 7:0 |            |  |  |  |  |  |  |  |

|-------|---------|-------------------------------|------------|--|--|--|--|--|--|--|

| UDID1 | 800F00  | UDID Word 1                   |            |  |  |  |  |  |  |  |

| UDID2 | 800F02  | UDID Word 2                   |            |  |  |  |  |  |  |  |

| UDID3 | 800F04  | UDID Word 3                   |            |  |  |  |  |  |  |  |

| UDID4 | 800F06  | UDID Word 4                   |            |  |  |  |  |  |  |  |

| UDID5 | 800F08  | U                             | DID Word 5 |  |  |  |  |  |  |  |

TABLE 4-1: UDID ADDRESSES

#### FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

### TABLE 4-15: SPI1 AND SPI2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8       | Bit 7       | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|---------|----------|-------------|-------------|------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | _      | SPISIDL | —      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV     | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      | —      | —       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP        | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | —       | _        | _           | _           | _          | _      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |        |         |        |        |         | SPI1 Tra | nsmit and R | eceive Buff | er Registe | r      |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV     | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      | —      | —       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP        | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | —       | _        | _           | _           | _          | _      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  |        |        |         |        |        |         | SPI2 Tra | nsmit and R | eceive Buff | er Registe | r      |        |        |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.5.1 PAGED MEMORY SCHEME

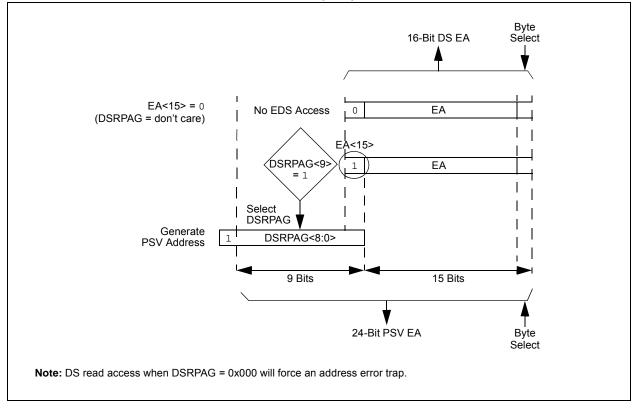

The dsPIC33EPXXGS50X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the base Data Space address is used in conjunction with the Data Space Page (DSRPAG) register to form the Program Space Visibility (PSV) address.

The Data Space Page (DSRPAG) register is located in the SFR space. Construction of the PSV address is shown in Figure 4-9. When DSRPAG<9> = 1 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit PSV read address. The paged memory scheme provides access to multiple 32-Kbyte windows in the PSV memory. The Data Space Page (DSRPAG) register, in combination with the upper half of the Data Space address, can provide up to 8 Mbytes of PSV address space. The paged data memory space is shown in Figure 4-10.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG.

### FIGURE 4-9: PROGRAM SPACE VISIBILITY (PSV) READ ADDRESS GENERATION

### 4.6.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

**Note:** For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- **Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.6.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.6.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| R/W-0           | R/W-0           | U-0                                  | U-0           | R/W-0                        | U-0               | R/W-0            | R/W-0         |

|-----------------|-----------------|--------------------------------------|---------------|------------------------------|-------------------|------------------|---------------|

| TRAPR           | IOPUWR          |                                      | —             | VREGSF                       | _                 | CM               | VREGS         |

| bit 15          |                 |                                      |               |                              |                   |                  | bit 8         |

|                 |                 |                                      |               |                              |                   |                  |               |

| R/W-0           | R/W-0           | R/W-0                                | R/W-0         | R/W-0                        | R/W-0             | R/W-1            | R/W-1         |

| EXTR            | SWR             | SWDTEN <sup>(2)</sup>                | WDTO          | SLEEP                        | IDLE              | BOR              | POR           |

| bit 7           |                 |                                      |               |                              |                   |                  | bit (         |

| Legend:         |                 |                                      |               |                              |                   |                  |               |

| R = Readable    | bit             | W = Writable                         | bit           | U = Unimple                  | mented bit, read  | l as '0'         |               |

| -n = Value at l |                 | '1' = Bit is set                     |               | '0' = Bit is cle             |                   | x = Bit is unki  | nown          |

|                 |                 |                                      |               |                              |                   |                  |               |

| bit 15          | TRAPR: Trap     | Reset Flag bit                       |               |                              |                   |                  |               |

|                 | -               | onflict Reset ha                     |               |                              |                   |                  |               |

|                 | 0 = A Trap Co   | onflict Reset ha                     | s not occurre | ed                           |                   |                  |               |

| bit 14          | IOPUWR: Ille    | gal Opcode or                        | Uninitialized | W Register Ac                | cess Reset Flag   | bit              |               |

|                 | •               | •                                    |               | gal address m                | ode or Uninitial  | ized W registe   | er used as ar |

|                 |                 | Pointer caused                       |               | ogistor Posot k              | nas not occurred  | 4                |               |

| bit 13-12       | -               | ited: Read as '                      |               | egister Reset i              | las not occurred  | 1                |               |

| bit 11          | •               |                                      |               | by During Sloo               | n hit             |                  |               |

|                 |                 | ash Voltage Reg<br>Itage regulator i | -             |                              | p bit             |                  |               |

|                 |                 | Itage regulator                      |               | •                            | ing Sleep         |                  |               |

| bit 10          |                 | ted: Read as '                       | -             | 5                            | 0                 |                  |               |

| bit 9           | -               | ation Mismatch                       |               |                              |                   |                  |               |

|                 |                 | uration Mismato<br>uration Mismato   |               |                              |                   |                  |               |

| bit 8           | VREGS: Volta    | age Regulator S                      | Standby Durir | ng Sleep bit                 |                   |                  |               |

|                 | 1 = Voltage r   | egulator is activ                    | ve during Sle | ep                           |                   |                  |               |

|                 | 0 = Voltage r   | egulator goes i                      | nto Standby r | mode during SI               | еер               |                  |               |

| bit 7           |                 | nal Reset (MCL                       |               |                              |                   |                  |               |

|                 |                 | Clear (pin) Res                      |               |                              |                   |                  |               |

| bit 6           |                 | Clear (pin) Res                      |               |                              |                   |                  |               |

|                 |                 | instruction has                      | , .           |                              |                   |                  |               |

|                 |                 | instruction has                      |               |                              |                   |                  |               |

| bit 5           | SWDTEN: So      | oftware Enable/                      | Disable of W  | DT bit <b><sup>(2)</sup></b> |                   |                  |               |

|                 | 1 = WDT is e    |                                      |               |                              |                   |                  |               |

|                 | 0 = WDT is d    | isabled                              |               |                              |                   |                  |               |

| bit 4           |                 | hdog Timer Tim                       | -             | it                           |                   |                  |               |

|                 |                 | e-out has occur<br>e-out has not oc  |               |                              |                   |                  |               |

|                 |                 |                                      | set or cleare | d in software. S             | Setting one of th | ese bits in soft | ware does not |

|                 | use a device Re |                                      | hite are '11' | (upprogramm)                 |                   | alwaye anabla    | d rogardiaca  |

|                 | the SWDTEN<1:0  |                                      |               | unprogramme                  | ed), the WDT is   | aiways enable    | u, regardiess |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

© 2013-2017 Microchip Technology Inc.

of the SWDTEN bit setting.

| R/W-0           | R/W-0       | R/W-0                   | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

|-----------------|-------------|-------------------------|--------------|------------------|------------------|-----------------|----------|

| SYNCI1R7        | SYNCI1R6    | SYNCI1R5                | SYNCI1R4     | SYNCI1R3         | SYNCI1R2         | SYNCI1R1        | SYNCI1R0 |

| bit 15          |             |                         |              |                  |                  | -               | bit 8    |

|                 |             |                         |              |                  |                  |                 |          |

| U-0             | U-0         | U-0                     | U-0          | U-0              | U-0              | U-0             | U-0      |

| —               | —           | —                       | —            | —                | —                | —               | —        |

| bit 7           |             |                         |              |                  |                  |                 | bit 0    |

|                 |             |                         |              |                  |                  |                 |          |

| Legend:         |             |                         |              |                  |                  |                 |          |

| R = Readable    | bit         | W = Writable            | bit          | U = Unimpler     | nented bit, read | l as '0'        |          |

| -n = Value at P | OR          | '1' = Bit is set        |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown     |

|                 |             |                         |              |                  |                  |                 |          |

| bit 15-8        | SYNCI1R<7:0 | <b>0&gt;:</b> Assign PW | M Synchroniz | ation Input 1 to | the Correspon    | ding RPn Pin b  | oits     |

|                 | 10110101 =  | Input tied to RI        | P181         |                  |                  |                 |          |

|                 | 10110100 =  | Input tied to RI        | P180         |                  |                  |                 |          |

|                 | •           |                         |              |                  |                  |                 |          |

|                 | •           |                         |              |                  |                  |                 |          |

|                 | •           |                         |              |                  |                  |                 |          |

|                 | 0000001 =   | Input tied to RI        | P1           |                  |                  |                 |          |

|                 |             | Input tied to Va        |              |                  |                  |                 |          |

| bit 7-0         | Unimplemen  | ted: Read as '          | 0'           |                  |                  |                 |          |

|                 |             |                         |              |                  |                  |                 |          |

### REGISTER 10-16: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                          | R/W-0                              |                  | 5444.0           |                 |        |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|-----------------|--------|

|               |                                                                                                           |                                                                                                                | 10,00-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT6R7        | FLT6R6                                                                                                    | FLT6R5                                                                                                         | FLT6R4                             | FLT6R3           | FLT6R2           | FLT6R1          | FLT6R0 |

| bit 15        |                                                                                                           | ·                                                                                                              |                                    | ·                |                  |                 | bit 8  |

|               |                                                                                                           |                                                                                                                |                                    |                  |                  |                 |        |

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                          | R/W-0                              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT5R7        | FLT5R6                                                                                                    | FLT5R5                                                                                                         | FLT5R4                             | FLT5R3           | FLT5R2           | FLT5R1          | FLT5R0 |

| bit 7         |                                                                                                           |                                                                                                                |                                    |                  |                  |                 | bit C  |

| Legend:       |                                                                                                           |                                                                                                                |                                    |                  |                  |                 |        |

| R = Readable  | e bit                                                                                                     | W = Writable                                                                                                   | bit                                | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                                                                                               |                                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7-0       | 10110100 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>Assign PWM<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 5 (FLT5) | ) to the Corresp | oonding RPn Pi   | n bits          |        |

|               | •<br>•                                                                                                    | Input tied to RI                                                                                               |                                    |                  |                  |                 |        |

### REGISTER 10-18: RPINR42: PERIPHERAL PIN SELECT INPUT REGISTER 42

NOTES:

### 13.2 Input Capture Registers

### REGISTER 13-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER              | 13-1: ICxC           | ON1: INPUT C                             | CAPTURE x CC        | NTROL REG            | ISTER 1          |                 |                   |

|-----------------------|----------------------|------------------------------------------|---------------------|----------------------|------------------|-----------------|-------------------|

| U-0                   | U-0                  | R/W-0                                    | R/W-0               | R/W-0                | R/W-0            | U-0             | U-0               |

| _                     | —                    | ICSIDL                                   | ICTSEL2             | ICTSEL1              | ICTSEL0          | _               | —                 |

| bit 15                |                      |                                          |                     |                      |                  |                 | bit 8             |

| U-0                   | R/W-0                | R/W-0                                    | R-0, HC, HS         | R-0, HC, HS          | R/W-0            | R/W-0           | R/W-0             |

|                       | ICI1 ICI0 ICOV ICBNE |                                          | 1 1                 | ICM2                 | ICM1             | ICM0            |                   |

| bit 7                 |                      |                                          |                     |                      |                  |                 | bit               |

| Legend:               |                      | HC = Hardward                            | Cloarable bit       | US - Hardwa          | re Settable bit  |                 |                   |

| ∟egena.<br>R = Readab | lo hit               | W = Writable b                           |                     |                      | nented bit, read | d as '0'        |                   |

| -n = Value a          |                      | '1' = Bit is set                         | it.                 | '0' = Bit is cle     |                  | x = Bit is unl  | nown              |

|                       |                      | I - Dit is set                           |                     |                      | areu             |                 |                   |

| bit 15-14             | Unimplemen           | nted: Read as '0                         | ,                   |                      |                  |                 |                   |

| bit 13                | -                    |                                          | in Idle Control bi  | t                    |                  |                 |                   |

| 511 10                | •                    | oture will halt in (                     |                     | t i                  |                  |                 |                   |

|                       |                      |                                          | e to operate in Cl  | PU Idle mode         |                  |                 |                   |

| bit 12-10             | ICTSEL<2:0           | >: Input Capture                         | x Timer Select bi   | ts                   |                  |                 |                   |

|                       |                      |                                          | s the clock source  |                      |                  |                 |                   |

|                       | 110 = Reser          | rved                                     |                     |                      |                  |                 |                   |

|                       | 101 = Reser          |                                          |                     |                      |                  |                 |                   |

|                       |                      |                                          | urce of the ICx (o  | nly the synchro      | nous clock is s  | supported)      |                   |

|                       |                      | K is the clock so<br>K is the clock so   |                     |                      |                  |                 |                   |

|                       |                      | K is the clock so                        |                     |                      |                  |                 |                   |

|                       |                      | K is the clock so                        |                     |                      |                  |                 |                   |

| bit 9-7               | Unimplemer           | ted: Read as '0                          | ,                   |                      |                  |                 |                   |

| oit 6-5               | ICI<1:0>: Nu         | mber of Capture                          | s per Interrupt Se  | elect bits (this fie | eld is not used  | if ICM<2:0> =   | 001 <b>or</b> 111 |

|                       |                      | t on every fourth                        |                     | Υ.                   |                  |                 |                   |

|                       | 10 = Interrup        | t on every third o                       | apture event        |                      |                  |                 |                   |

|                       |                      |                                          | nd capture event    |                      |                  |                 |                   |

|                       | 00 = Interrup        | t on every captu                         | re event            |                      |                  |                 |                   |

| bit 4                 | -                    | -                                        | ow Status Flag bit  |                      |                  |                 |                   |

|                       |                      |                                          | flow has occurred   |                      |                  |                 |                   |

|                       | -                    | -                                        | verflow has occu    |                      | <b>、</b>         |                 |                   |

| bit 3                 | -                    | -                                        | r Not Empty Stat    |                      | • •              |                 |                   |

|                       |                      | oture buffer is no<br>oture buffer is en | t empty, at least o | one more captu       | re value can b   | e read          |                   |

| bit 2-0               |                      | put Capture x M                          |                     |                      |                  |                 |                   |

| JIL 2-0               |                      | •                                        | ons as an interru   | unt nin only in (    | CDI I Sleen an   | d Idle modes    | (rising odg       |

|                       |                      |                                          | ontrol bits are not |                      |                  | u luie moues    | (IISING EUG       |

|                       |                      | ed (module is dis                        |                     |                      |                  |                 |                   |

|                       |                      | •                                        | 6th rising edge (l  | Prescaler Capti      | ure mode)        |                 |                   |

|                       | 100 <b>= Captu</b>   | re mode, every 4                         | th rising edge (P   | rescaler Captur      | re mode)         |                 |                   |

|                       |                      |                                          | ising edge (Simp    |                      |                  |                 |                   |

|                       |                      |                                          | alling edge (Simp   |                      |                  | is not used     | in this mode      |

|                       |                      | re mode, every ris                       | sing and falling ed | ye (⊏uye Delêc       |                  | r∕, is not used | III UIIS MODE     |

001 = Capture mode, every fising an000 = Input Capture x is turned off

### **REGISTER 15-10: MDC: PWMx MASTER DUTY CYCLE REGISTER**<sup>(1,2)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | MDC   | C<15:8>           |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | MD    | C<7:0>            |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

|                 |       |                  |       |                   |                |                 |       |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable    | bit   | W = Writable I   | oit   | U = Unimplem      | ented bit, rea | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

**Note 1:** The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

2: As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

#### REGISTER 15-11: PWMKEY: PWMx PROTECTION LOCK/UNLOCK KEY REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | PWMKE | Y<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PWMK  | EY<7:0> |       |       |       |

| bit 7  |       |       |       |         |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PWMKEY<15:0>:** PWMx Protection Lock/Unlock Key Value bits

### **REGISTER 19-31:** ADCMPxCON: ADC DIGITAL COMPARATOR x CONTROL REGISTER (x = 0 or 1)

| U-0                   | U-0                                                                                                      | U-0                                                   | R-0, HSC                       | R-0, HSC          | R-0, HSC         | R-0, HSC          | R-0, HSC       |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|-------------------|------------------|-------------------|----------------|

| —                     | —                                                                                                        | —                                                     | CHNL4                          | CHNL3             | CHNL2            | CHNL1             | CHNL0          |

| bit 15                |                                                                                                          |                                                       |                                |                   |                  |                   | bit 8          |

| R/W-0                 | R/W-0                                                                                                    | R-0, HC, HS                                           | R/W-0                          | R/W-0             | R/W-0            | R/W-0             | R/W-0          |

| CMPEN                 | IE                                                                                                       | STAT                                                  | BTWN                           | НІНІ              | HILO             | LOHI              | LOLO           |

| bit 7                 |                                                                                                          | • • • •                                               |                                |                   |                  |                   | bit 0          |

| Legend:               |                                                                                                          | HC = Hardwar                                          | e Clearable bit                | U = Unimplerr     | nented bit, read | as '0'            |                |

| R = Readable          | e bit                                                                                                    | W = Writable                                          |                                |                   | are Settable/Cle |                   |                |

| -n = Value at         | POR                                                                                                      | '1' = Bit is set                                      |                                | '0' = Bit is cle  | ared             | HS = Hardwar      | e Settable bit |

|                       |                                                                                                          | tada Daadaa (                                         |                                |                   |                  |                   |                |

| bit 15-13<br>bit 12-8 | -                                                                                                        | ted: Read as 'd<br>Input Channel                      |                                |                   |                  |                   |                |

|                       | If the compara<br>11111 = Res<br>10110 = Res<br>10101 = AN2<br>10100 = AN2<br>00001 = AN1<br>00000 = AN0 | erved<br>11<br>10                                     | ed an event for                | a channel, thi    | s channel numb   | ber is written to | these bits.    |

| bit 7                 |                                                                                                          | nparator Enable                                       | e bit                          |                   |                  |                   |                |

|                       | 1 = Comparat<br>0 = Comparat                                                                             | tor is enabled<br>tor is disabled a                   | and the STAT s                 | tatus bit is clea | ared             |                   |                |

| bit 6                 | IE: Comparat                                                                                             | or Common AE                                          | C Interrupt En                 | able bit          |                  |                   |                |

|                       |                                                                                                          | ADC interrupt                                         | U U                            |                   |                  | comparison ev     | vent           |

| bit 5                 | STAT: Compa                                                                                              | arator Event Sta                                      | itus bit                       |                   |                  |                   |                |

|                       | 1 = A compar                                                                                             | ared by hardwa<br>ison event has<br>ison event has    | been detected                  | since the last    | read of the CH   | NL<4:0> bits      |                |

| bit 4                 | BTWN: Betwe                                                                                              | een Low/High (                                        | Comparator Ev                  | ent bit           |                  |                   |                |

|                       |                                                                                                          | s a comparator<br>generate a digi                     |                                |                   |                  |                   | CMPxHI         |

| bit 3                 | HIHI: High/Hig                                                                                           | gh Comparator                                         | Event bit                      |                   |                  |                   |                |

|                       |                                                                                                          | s a digital comp<br>generate a digi                   |                                |                   |                  | CMPxHI            |                |

| bit 2                 | HILO: High/L                                                                                             | ow Comparator                                         | Event bit                      |                   |                  |                   |                |

|                       |                                                                                                          | s a digital comp<br>generate a digi                   |                                |                   |                  |                   |                |

| bit 1                 | 1 = Generate                                                                                             | igh Comparator<br>s a digital comp<br>generate a digi | parator event w                |                   |                  |                   |                |

| bit 0                 | LOLO: Low/L<br>1 = Generate                                                                              | ow Comparato<br>s a digital comp<br>generate a digi   | r Event bit<br>parator event w | hen ADCBUF        | < < ADCMPxLC     | )                 |                |

### 20.6 Hysteresis

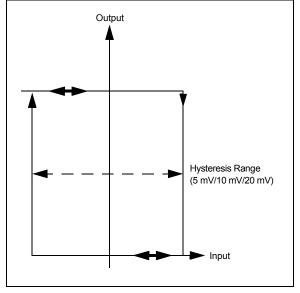

An additional feature of the module is hysteresis control. Hysteresis can be enabled or disabled and its amplitude can be controlled by the HYSSEL<1:0> bits in the CMPxCON register. Three different values are available: 5 mV, 10 mV and 20 mV. It is also possible to select the edge (rising or falling) to which hysteresis is to be applied.

Hysteresis control prevents the comparator output from continuously changing state because of small perturbations (noise) at the input (see Figure 20-2).

### 20.7 Analog Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 20.7.1 KEY RESOURCES

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

### REGISTER 21-1: PGAxCON: PGAx CONTROL REGISTER (CONTINUED)

- bit 2-0 GAIN<2:0>: PGAx Gain Selection bits

- 111 = Reserved

- 110 = Gain of 64x

- 101 = Gain of 32x

- 100 = Gain of 16x

- 011 = Gain of 8x

- 010 = Gain of 4x

- 001 = Reserved

- 000 = Reserved

### REGISTER 21-2: PGAxCAL: PGAx CALIBRATION REGISTER

| U-0             | U-0 | U-0              | U-0         | U-0                                     | U-0   | U-0   | U-0   |  |  |  |  |

|-----------------|-----|------------------|-------------|-----------------------------------------|-------|-------|-------|--|--|--|--|

| —               | —   | —                |             | —                                       | _     | —     | —     |  |  |  |  |

| bit 15          |     |                  |             |                                         |       |       | bit 8 |  |  |  |  |

|                 |     |                  |             |                                         |       |       |       |  |  |  |  |

| U-0             | U-0 | R/W-0            | R/W-0       | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

| —               | —   |                  | PGACAL<5:0> |                                         |       |       |       |  |  |  |  |

| bit 7           |     |                  |             |                                         |       |       | bit 0 |  |  |  |  |

|                 |     |                  |             |                                         |       |       |       |  |  |  |  |

| Legend:         |     |                  |             |                                         |       |       |       |  |  |  |  |

| R = Readable    | bit | W = Writable     | bit         | U = Unimplemented bit, read as '0'      |       |       |       |  |  |  |  |

| -n = Value at P | OR  | '1' = Bit is set |             | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **PGACAL<5:0>:** PGAx Offset Calibration bits

The calibration values for PGA1 and PGA2 must be copied from Flash addresses, 0x800E48 and 0x800E4C, respectively, into these bits before the module is enabled. Refer to the calibration data address table (Table 23-3) in **Section 23.0 "Special Features"** for more information.

### TABLE 23-1: CONFIGURATION REGISTER MAP<sup>(3)</sup>

| Name    | Address                    | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-16 | Bit 15                  | Bit 14 | Bit 13 | Bit 12   | Bit 11 | Bit 10 | Bit 9         | Bit 8    | Bit 7                   | Bit 6     | Bit 5        | Bit 4    | Bit 3       | Bit 2 | Bit 1   | Bit 0                   |

|---------|----------------------------|--------------------------------------|------------|-------------------------|--------|--------|----------|--------|--------|---------------|----------|-------------------------|-----------|--------------|----------|-------------|-------|---------|-------------------------|

|         | 002B80                     | 16                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

| FSEC    | 005780                     | 32                                   | 1          | _                       | _      | _      | CSS<2:0> |        | CWRP   | GSS<1:0> GWRP |          | GWRP                    | _         | BSEN         | BSS<1:0> |             | BWRP  |         |                         |

|         | 00AF80                     | 64                                   | -          |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002B90                     | 16                                   |            |                         |        |        |          |        |        |               |          | L                       |           | I            |          |             |       |         |                         |

| FBSLIM  | 005790                     | 32                                   | _          | _                       | _      | _      |          |        |        |               |          |                         | BSLI      | M<12:0>      |          |             |       |         |                         |

|         | 00AF90                     | 64                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002B94                     | 16                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

| FSIGN   | 005794                     | 32                                   | _          | Reserved <sup>(2)</sup> | _      | _      | _        | _      | _      | _             | _        | _                       | _         | _            | _        | _           | _     | _       | _                       |

|         | 00AF94                     | 64                                   | -          |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002B98                     | 16                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

| FOSCSEL | EL 005798 32               |                                      | _          |                         |        |        |          |        | — IESO | _             |          | _                       | _         | - FNOSC<2:0> |          | >           |       |         |                         |

|         | 00AF98                     | 64                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002B9C 16                  |                                      |            |                         |        | _      | _        | _      | _      | _             | PLLKEN   |                         |           |              |          |             |       |         |                         |

| FOSC    | DSC 00579C 32<br>00AF9C 64 |                                      | _          | _   _                   |        |        |          |        |        |               |          | FCKSM<1:0>              | IOL1WAY — | _            | OSCIOFNC | POSCMD<1:0> |       |         |                         |

|         |                            |                                      |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002BA0                     | 16                                   |            |                         |        |        |          |        |        |               | •        |                         |           |              |          |             |       |         |                         |

| FWDT    | 0057A0                     | 32                                   | —          | _                       | —      | _      | _        | _      | _      | WDTW          | /IN<1:0> | WINDIS                  | WDT       | EN<1:0>      | WDTPRE   |             | WDTPO | ST<3:0> |                         |

|         | 00AFA0                     | 64                                   | -          |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002BA4                     | 16                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

| FPOR    | 0057A4                     | 32                                   | —          | —                       | —      | —      | —        | —      | —      | —             | —        | —                       | —         | —            | —        | —           | —     | —       | Reserved <sup>(1)</sup> |

|         | 00AFA4                     | 64                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

|         | 002BA8                     | 16                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

| FICD    | 0057A8                     | 32                                   | —          | BTSWP                   | —      | —      | —        | —      | —      | —             | -        | Reserved <sup>(1)</sup> | —         | JTAGEN       | —        | -           | —     | ICS     | 6<1:0>                  |

|         | 00AFA8                     | 64                                   |            |                         |        |        |          |        |        |               |          |                         |           |              |          |             |       |         |                         |

Note 1: These bits are reserved and must be programmed as '1'.

2: This bit is reserved and must be programmed as '0'.

3: When operating in Dual Partition mode, each partition will have dedicated Configuration registers. On a device Reset, the configuration values of the Active Partition are read at start-up, but during a soft swap condition, the configuration settings of the newly Active Partition are ignored.

4: FBOOT resides in configuration memory space.

### 23.6 Watchdog Timer (WDT)

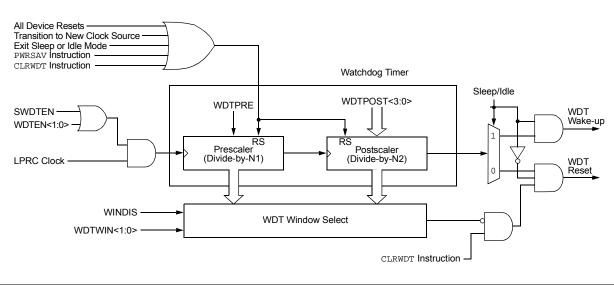

For dsPIC33EPXXGS50X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 23.6.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 26-23.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### FIGURE 23-2: WDT BLOCK DIAGRAM

### 23.6.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

### 23.6.3 ENABLING WDT

The WDT is enabled or disabled by the WDTEN<1:0> Configuration bits in the FWDT Configuration register. When the WDTEN<1:0> Configuration bits have been programmed to '0b11', the WDT is always enabled.

The WDT can be optionally controlled in software when the WDTEN<1:0> Configuration bits have been programmed to '0b10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disables the WDT during non-critical segments for maximum power savings.

The WDT Time-out flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 23.6.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

| DC CHARACTER                        | ISTICS | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |               |       |            |       |                 |  |  |  |

|-------------------------------------|--------|-------------------------------------------------------|---------------|-------|------------|-------|-----------------|--|--|--|

| Parameter No.                       | Тур.   | Max.                                                  | Doze<br>Ratio | Units | Conditions |       |                 |  |  |  |

| Doze Current (IDOZE) <sup>(1)</sup> |        |                                                       |               |       |            |       |                 |  |  |  |

| DC73a <sup>(2)</sup>                | 20     | 40                                                    | 1:2           | mA    | -40°C      | 3.3V  | Fosc = 140 MHz  |  |  |  |

| DC73g                               | 9      | 20                                                    | 1:128         | mA    | -40 C      |       | FUSC - 140 MINZ |  |  |  |

| DC70a <sup>(2)</sup>                | 20     | 40                                                    | 1:2           | mA    | +25°C      | 3.3V  | Fosc = 140 MHz  |  |  |  |

| DC70g                               | 9      | 20                                                    | 1:128         | mA    | +25 C      | 3.3V  | FUSC - 140 MITZ |  |  |  |

| DC71a <sup>(2)</sup>                | 20     | 40                                                    | 1:2           | mA    | +85°C      | 3.3V  |                 |  |  |  |

| DC71g                               | 9      | 20                                                    | 1:128         | mA    | +00 C      | 3.3V  | Fosc = 140 MHz  |  |  |  |

| DC72a <sup>(2)</sup>                | 20     | 40                                                    | 1:2           | mA    | +125°C     | 2 21/ | Ecco - 120 MH-  |  |  |  |

| DC72g                               | 9      | 20                                                    | 1:128         | mA    | +125°C     | 3.3V  | Fosc = 120 MHz  |  |  |  |

#### TABLE 26-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

• Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: These parameter are characterized but not tested in manufacturing.

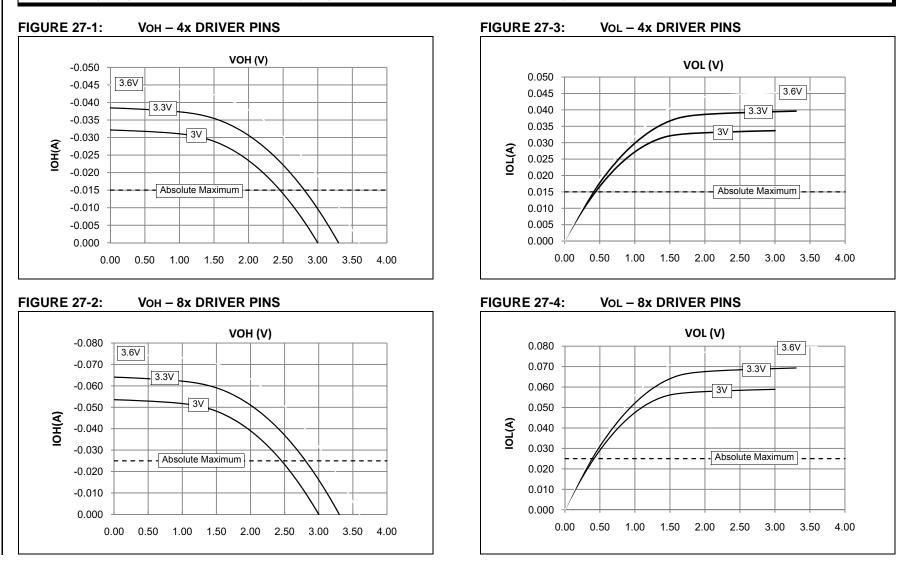

### 27.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.