Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502-e-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXGS50X family requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins regardless if ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

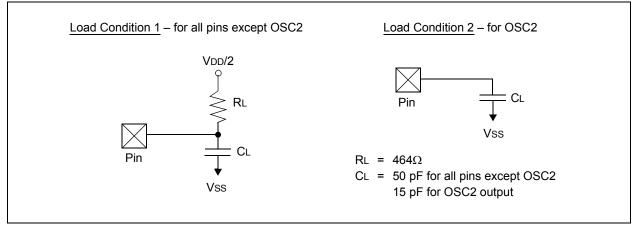

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| TABLE 4     | 4-4:  | TIME   | R1 THR            | OUGH . | TIMER5 | REGIST | FER MA | Р           |               |               |              |        |        |       |       |       |       |               |

|-------------|-------|--------|-------------------|--------|--------|--------|--------|-------------|---------------|---------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8         | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |                   |        |        |        |        |             | Timer1        | Register      |              |        |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |                   |        |        |        |        |             | Period R      | Register 1    |              |        |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _                 | TSIDL  | _      | _      | _      | _           | _             |               | TGATE        | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |        |                   |        |        |        |        |             | Timer2        | Register      |              |        |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |        |                   |        |        |        | Timer  | 3 Holding F | Register (for | 32-bit time   | r operations | only)  |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        |                   |        |        |        |        |             | Timer3        | Register      |              |        |        |       |       |       |       | xxxx          |

| PR2         | 010C  |        | Period Register 2 |        |        |        |        |             |               | FFFF          |              |        |        |       |       |       |       |               |

| PR3         | 010E  |        |                   |        |        |        |        |             | Period R      | Register 3    |              |        |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | _                 | TSIDL  | _      | _      | _      | _           | _             | _             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON    | _                 | TSIDL  | _      | _      | _      | _           | _             | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

| TMR4        | 0114  |        |                   |        |        |        |        |             | Timer4        | Register      |              |        |        |       |       |       |       | xxxx          |

| TMR5HLD     | 0116  |        |                   |        |        |        | Tir    | ner5 Holdin | g Register (  | (for 32-bit o | perations or | ıly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                   |        |        |        |        |             | Timer5        | Register      |              |        |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |                   |        |        |        |        |             | Period R      | Register 4    |              |        |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |                   |        |        |        |        |             | Period R      | Register 5    |              |        |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | _                 | TSIDL  | —      | _      | —      | _           | _             | —             | TGATE        | TCKPS1 | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _                 | TSIDL  | _      | _      | _      | _           | _             |               | TGATE        | TCKPS1 | TCKPS0 |       | _     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXGS50X FAMILY

#### TABLE 4-15: SPI1 AND SPI2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                    | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8       | Bit 7       | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|-------------------------------------------|---------|--------|--------|---------|----------|-------------|-------------|------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | _                                         | SPISIDL | —      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV     | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      | —                                         | —       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP        | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD                                    | FRMPOL  | _      | —      | —       | _        | _           | _           | _          | _      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |                                           |         |        |        |         | SPI1 Tra | nsmit and R | eceive Buff | er Registe | r      |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | _                                         | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0     | SRMPT       | SPIROV     | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      | —                                         | —       | DISSCK | DISSDO | MODE16  | SMP      | CKE         | SSEN        | CKP        | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD                                    | FRMPOL  | _      | —      | —       | _        | _           | _           | _          | _      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  |        | SPI2 Transmit and Receive Buffer Register |         |        |        |         |          |             |             |            | 0000   |        |        |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.6 Control Registers

Five SFRs are used to write and erase the program Flash memory: NVMCON, NVMKEY, NVMADR, NVMADRU and NVMSRCADR/H.

The NVMCON register (Register 5-1) selects the operation to be performed (page erase, word/row program, Inactive Partition erase), initiates the program or erase cycle and is used to determine the Active Partition in Dual Partition modes.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word/row for programming operations, or the selected page for erase operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

For row programming operation, data to be written to program Flash memory is written into data memory space (RAM) at an address defined by the NVMSRCADR register (location of first element in row programming data).

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/SO-0(    | <sup>1)</sup> R/W-0 <sup>(1)</sup>      | R/W-0 <sup>(1)</sup>                                                                                            | R/W-0                            | R/C-0                             | R-0                     | R/W-0                   | R/C-0                   |

|------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|-------------------------|-------------------------|-------------------------|

| WR         | WREN                                    | WRERR                                                                                                           | NVMSIDL <sup>(2)</sup>           | SFTSWP <sup>(6)</sup>             | P2ACTIV <sup>(6)</sup>  | RPDF                    | URERR                   |

| bit 15     |                                         |                                                                                                                 |                                  |                                   |                         |                         | bit 8                   |

|            |                                         |                                                                                                                 |                                  |                                   |                         |                         |                         |

| U-0        | U-0                                     | U-0                                                                                                             | U-0                              | R/W-0 <sup>(1)</sup>              | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    |

| _          | —                                       | —                                                                                                               | —                                | NVMOP3 <sup>(3,4)</sup>           | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4)</sup> |

| bit 7      |                                         |                                                                                                                 |                                  |                                   |                         |                         | bit 0                   |

|            |                                         |                                                                                                                 |                                  |                                   |                         |                         |                         |

| Legend:    |                                         | C = Clearab                                                                                                     | le bit                           | SO = Settable                     | Only bit                |                         |                         |

| R = Reada  | able bit                                | W = Writable                                                                                                    | e bit                            | U = Unimplem                      | ented bit, read a       | as '0'                  |                         |

| -n = Value | at POR                                  | '1' = Bit is se                                                                                                 | et                               | '0' = Bit is clea                 | red                     | x = Bit is unkn         | own                     |

|            |                                         |                                                                                                                 |                                  |                                   |                         |                         |                         |

| bit 15     | WR: Write Co                            |                                                                                                                 |                                  |                                   |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  |                                   | on; the operation       | on is self-timed        | and the bit is          |

|            |                                         |                                                                                                                 |                                  | tion is complete ete and inactive |                         |                         |                         |

| bit 14     | WREN: Write                             | -                                                                                                               | -                                |                                   | -                       |                         |                         |

|            |                                         |                                                                                                                 | m/erase operat                   | ions                              |                         |                         |                         |

|            |                                         |                                                                                                                 | /erase operation                 |                                   |                         |                         |                         |

| bit 13     |                                         |                                                                                                                 | Error Flag bit <sup>(1</sup>     |                                   |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  | ce attempt, or te                 | rmination has o         | ccurred (bit is se      | et automatically        |

|            | •                                       | et attempt of the second se |                                  | pleted normally                   | ,                       |                         |                         |

| bit 12     |                                         |                                                                                                                 | le Control bit <sup>(2)</sup>    |                                   |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  | ndby mode dur                     | ing Idle mode           |                         |                         |

|            |                                         | • •                                                                                                             | or is active duri                | •                                 | 0                       |                         |                         |

| bit 11     | SFTSWP: Pa                              | artition Soft Sv                                                                                                | vap Status bit <sup>(€</sup>     | 5)                                |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  |                                   | e BOOTSWP inst          |                         |                         |

|            |                                         |                                                                                                                 | artition swap us<br>sed on FBTSE |                                   | P instruction or        | a device Reset          | will determine          |

| bit 10     | P2ACTIV: Pa                             |                                                                                                                 |                                  | C .                               |                         |                         |                         |

|            |                                         |                                                                                                                 | apped into the a                 | active region                     |                         |                         |                         |

|            |                                         |                                                                                                                 | apped into the a                 | •                                 |                         |                         |                         |

| bit 9      | RPDF: Row F                             | Programming                                                                                                     | Data Format b                    | it                                |                         |                         |                         |

|            |                                         |                                                                                                                 |                                  | npressed forma                    |                         |                         |                         |

|            | 0 = Row data                            | a to be stored                                                                                                  | in RAM in und                    | ompressed forr                    | nat                     |                         |                         |

| Note 1:    | These bits can on                       | ly be reset or                                                                                                  | a POR.                           |                                   |                         |                         |                         |

| 2:         | If this bit is set, po                  |                                                                                                                 |                                  |                                   | DLE) and upon e         | exiting Idle mod        | e, there is a           |

| •          | delay (TVREG) bef                       |                                                                                                                 | -                                | -                                 |                         |                         |                         |

|            | All other combinat                      |                                                                                                                 |                                  | •                                 |                         | ana ara in prag         | ~~~~                    |

| 4:<br>5:   | Execution of the I<br>Two adjacent wor  |                                                                                                                 | -                                | -                                 | -                       |                         |                         |

| 5.<br>6:   | Only available on                       |                                                                                                                 | -                                |                                   | -                       | -                       |                         |

| 0.         | this bit is reserved                    |                                                                                                                 |                                  |                                   |                         |                         |                         |

| 7:         | The specific Boot                       |                                                                                                                 |                                  | of the program                    | med data:               |                         |                         |

|            | 11 = Single Partitio                    |                                                                                                                 |                                  |                                   |                         |                         |                         |

|            | 10 = Dual Partitio<br>01 = Protected Du |                                                                                                                 |                                  |                                   |                         |                         |                         |

|            | 00 = Reserved                           |                                                                                                                 |                                  |                                   |                         |                         |                         |

#### REGISTER 9-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

| U-0          | U-0        | U-0                                               | U-0            | U-0                                | R/W-0  | R/W-0            | U-0   |  |  |  |

|--------------|------------|---------------------------------------------------|----------------|------------------------------------|--------|------------------|-------|--|--|--|

| _            | _          | —                                                 | _              | _                                  | PGA2MD | ABGMD            | _     |  |  |  |

| bit 15       |            |                                                   |                |                                    |        |                  | bit 8 |  |  |  |

|              |            |                                                   |                |                                    |        |                  |       |  |  |  |

| U-0          | U-0        | U-0                                               | U-0            | U-0                                | U-0    | R/W-0            | U-0   |  |  |  |

| —            | —          | —                                                 | —              | _                                  | —      | CCSMD            | —     |  |  |  |

| bit 7        |            |                                                   |                |                                    |        |                  | bit 0 |  |  |  |

|              |            |                                                   |                |                                    |        |                  |       |  |  |  |

| Legend:      |            |                                                   |                |                                    |        |                  |       |  |  |  |

| R = Readab   | ole bit    | W = Writable b                                    | pit            | U = Unimplemented bit, read as '0' |        |                  |       |  |  |  |

| -n = Value a | it POR     | '1' = Bit is set                                  |                | '0' = Bit is clea                  | ared   | x = Bit is unkno | own   |  |  |  |

|              |            |                                                   |                |                                    |        |                  |       |  |  |  |

| bit 15-11    | Unimplemer | nted: Read as '0                                  | ,              |                                    |        |                  |       |  |  |  |

| bit 10       | PGA2MD: P  | GA2 Module Dis                                    | able bit       |                                    |        |                  |       |  |  |  |

|              |            | odule is disabled                                 | -              |                                    |        |                  |       |  |  |  |

|              | 0 = PGA2 m | odule is enabled                                  |                |                                    |        |                  |       |  |  |  |

| bit 9        | ABGMD: Ba  | nd Gap Referen                                    | ce Voltage Dis | able bit                           |        |                  |       |  |  |  |

|              |            | p reference volta                                 |                |                                    |        |                  |       |  |  |  |

|              |            | p reference volta                                 | -              |                                    |        |                  |       |  |  |  |

| bit 8-2      | Unimplemen | nted: Read as '0                                  | ,              |                                    |        |                  |       |  |  |  |

| bit 1        | CCSMD: Co  | CCSMD: Constant-Current Source Module Disable bit |                |                                    |        |                  |       |  |  |  |

|              |            | t-current source                                  |                |                                    |        |                  |       |  |  |  |

| bit 0        |            |                                                   |                |                                    |        |                  |       |  |  |  |

| DILU         | Unimpiemer | nted: Read as '0                                  |                |                                    |        |                  |       |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0                                                                                                                              | R/W-0                                      | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|-----------------|-----------------|--------|

| FLT2R7          | FLT2R6                                                               | FLT2R5                                                                                                                             | FLT2R4                                     | FLT2R3           | FLT2R2          | FLT2R1          | FLT2R0 |

| bit 15          |                                                                      |                                                                                                                                    |                                            |                  |                 |                 | bit 8  |

|                 |                                                                      |                                                                                                                                    |                                            |                  |                 |                 |        |

| R/W-0           | R/W-0                                                                | R/W-0                                                                                                                              | R/W-0                                      | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| FLT1R7          | FLT1R6                                                               | FLT1R5                                                                                                                             | FLT1R4                                     | FLT1R3           | FLT1R2          | FLT1R1          | FLT1R0 |

| bit 7           |                                                                      |                                                                                                                                    |                                            |                  |                 |                 | bit (  |

|                 |                                                                      |                                                                                                                                    |                                            |                  |                 |                 |        |

| Legend:         |                                                                      |                                                                                                                                    |                                            |                  |                 |                 |        |

| R = Readable    |                                                                      | W = Writable                                                                                                                       |                                            | •                | nented bit, rea |                 |        |

| -n = Value at I | POR                                                                  | '1' = Bit is set                                                                                                                   |                                            | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

| bit 7-0         | 10110100 =<br>000000001 =<br>00000000 =<br>FLT1R<7:0>:<br>10110101 = | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>Assign PWM<br>Input tied to RI<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 1 (FLT1)<br>⊃181 | to the Corresp   | oonding RPn Pi  | in bits         |        |

|                 |                                                                      | Input tied to RI<br>Input tied to Ve                                                                                               |                                            |                  |                 |                 |        |

#### REGISTER 10-8: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

#### REGISTER 10-17: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SYNCI2R7 | SYNCI2R6 | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 SYNCI2R<7:0>: Assign PWM Synchronization Input 2 to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180 •

• 00000001 = Input tied to RP1 00000000 = Input tied to Vss

#### REGISTER 10-36: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16

| U-0             | U-0    | R/W-0            | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------|------------------|---------|------------------|------------------|-----------------|---------|

| —               | _      | RP177R5          | RP177R4 | RP177R3          | RP177R2          | RP177R1         | RP177R0 |

| bit 15          | -<br>- |                  |         |                  |                  | •               | bit 8   |

| U-0             | U-0    | R/W-0            | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| _               | _      | RP176R5          | RP176R4 | RP176R3          | RP176R2          | RP176R1         | RP176R0 |

| bit 7           |        |                  |         |                  |                  |                 | bit C   |

| Legend:         |        |                  |         |                  |                  |                 |         |

| R = Readable    | bit    | W = Writable     | bit     | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at I | POR    | '1' = Bit is set |         | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 13-8 | RP177R<5:0>: Peripheral Output Function is Assigned to RP177 Output Pin bits |

|----------|------------------------------------------------------------------------------|

|          | (see Table 10-2 for peripheral function numbers)                             |

| bit 7-6  | Unimplemented: Read as '0'                                                   |

| bit 5-0  | RP176R<5:0>: Peripheral Output Function is Assigned to RP176 Output Pin bits |

### (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-37: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17

| U-0             | U-0 | R/W-0            | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|-----|------------------|---------|------------------|------------------|-----------------|---------|

| —               | —   | RP179R5          | RP179R4 | RP179R3          | RP179R2          | RP179R1         | RP179R0 |

| bit 15          |     |                  |         |                  |                  |                 | bit 8   |

| <b></b>         |     |                  |         |                  |                  |                 |         |

| U-0             | U-0 | R/W-0            | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| —               | —   | RP178R5          | RP178R4 | RP178R3          | RP178R2          | RP178R1         | RP178R0 |

| bit 7           |     |                  |         |                  |                  |                 | bit 0   |

|                 |     |                  |         |                  |                  |                 |         |

| Legend:         |     |                  |         |                  |                  |                 |         |

| R = Readable    | bit | W = Writable     | bit     | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at P | OR  | '1' = Bit is set |         | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

| -n = Value at P | OR  | '1' = Bit is set |         | '0' = Bit is cle | eared            | x = Bit is unkr | IOWN    |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP179R<5:0>:** Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 10-2 for peripheral function numbers)

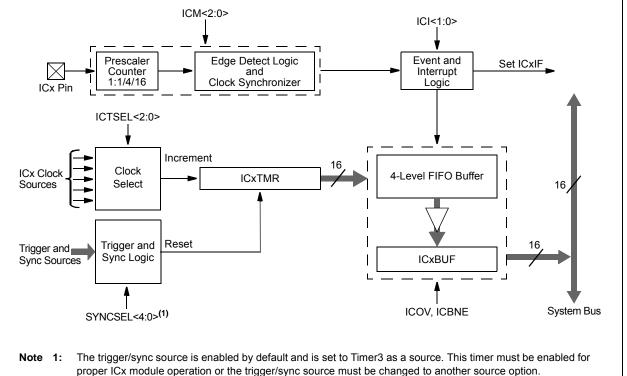

#### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurements. The dsPIC33EPXXGS50X family devices support four input capture channels.

Key features of the input capture module include:

Hardware-Configurable for 32-Bit Operation in All modes by Cascading Two Adjacent Modules

- Synchronous and Trigger modes of Output Compare Operation, with up to 21 User-Selectable Trigger/Sync Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Six Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

#### 13.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 13.1.1 KEY RESOURCES

- "Input Capture" (DS70000352) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### FIGURE 13-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

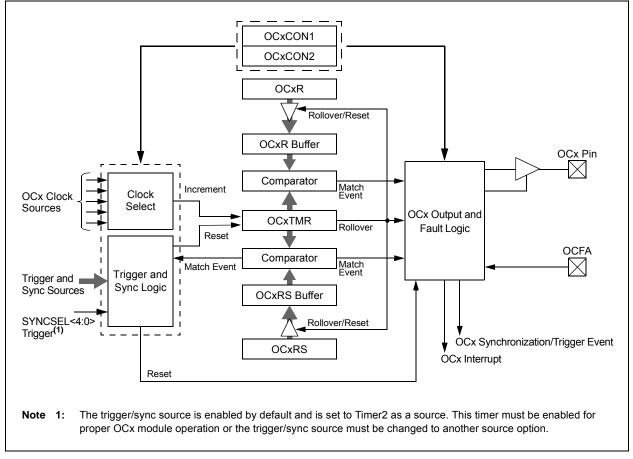

### 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare with Dedicated Timer" (DS70005159) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select one of six available clock sources for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

#### 14.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 14.1.1 KEY RESOURCES

- "Output Compare with Dedicated Timer" (DS70005159) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### FIGURE 14-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

x = Bit is unknown

#### **REGISTER 15-15:** PHASEX: PWMx PRIMARY PHASE-SHIFT REGISTER (x = 1 to 5)<sup>(1,2)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PHASE | Ex<15:8>     |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PHAS  | Ex<7:0>      |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit |       | U = Unimplen | nented bit. read | l as '0' |       |

bit 15-0 **PHASEx<15:0>:** PWMx Phase-Shift Value or Independent Time Base Period for the PWMx Generator bits

**Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

'1' = Bit is set

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Phase-shift value for PWMxH only

- When the PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period

'0' = Bit is cleared

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant, and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxH only

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000 through 0xFFF8

-n = Value at POR

| R/W-1            | R/W-1                        | R/W-0                                                                                | R/W-0                           | R/W-0                          | R/W-0                          | R/W-0                       | R/W-0  |

|------------------|------------------------------|--------------------------------------------------------------------------------------|---------------------------------|--------------------------------|--------------------------------|-----------------------------|--------|

| PENH             | PENL                         | POLH                                                                                 | POLL                            | PMOD1 <sup>(1)</sup>           | PMOD0 <sup>(1)</sup>           | OVRENH                      | OVRENL |

| pit 15           | •                            |                                                                                      |                                 | •                              |                                |                             | bit    |

|                  |                              | DAMO                                                                                 | DAMO                            |                                |                                | DAMO                        |        |

| R/W-0<br>OVRDAT1 | R/W-0                        | R/W-0<br>FLTDAT1 <sup>(2)</sup>                                                      | R/W-0<br>FLTDAT0 <sup>(2)</sup> | R/W-0<br>CLDAT1 <sup>(2)</sup> | R/W-0<br>CLDAT0 <sup>(2)</sup> | R/W-0                       | R/W-0  |

| • • • • • • •    | OVRDATU                      | FLIDAI                                                                               | FLIDAI0-                        | CLDATI                         | CLDATU-7                       | SWAP                        | OSYNC  |

| oit 7            |                              |                                                                                      |                                 |                                |                                |                             | bit    |

| _egend:          |                              |                                                                                      |                                 |                                |                                |                             |        |

| R = Readabl      | e bit                        | W = Writable b                                                                       | oit                             | U = Unimplem                   | nented bit, read               | l as '0'                    |        |

| n = Value at     | POR                          | '1' = Bit is set                                                                     |                                 | '0' = Bit is clea              | ared                           | x = Bit is unkno            | own    |

| ait 1 <i>5</i>   |                              |                                                                                      |                                 |                                |                                |                             |        |

| bit 15           | 1 = PWMx mo                  | KH Output Pin C<br>odule controls the<br>dule controls the                           | ne PWMxH pir                    | 1                              |                                |                             |        |

| oit 14           |                              | L Output Pin O                                                                       |                                 |                                |                                |                             |        |

|                  |                              | odule controls the                                                                   |                                 |                                |                                |                             |        |

| bit 13           |                              | kH Output Pin P                                                                      | olarity bit                     |                                |                                |                             |        |

|                  |                              | oin is active-low<br>oin is active-high                                              | ı                               |                                |                                |                             |        |

| bit 12 POLL: P   |                              | L Output Pin Po                                                                      | plarity bit                     |                                |                                |                             |        |

|                  | 0 = PWMxL p                  | in is active-low<br>in is active-high                                                |                                 |                                |                                |                             |        |

| oit 11-10        |                              | PWMx I/O Pin I                                                                       |                                 |                                |                                |                             |        |

|                  | 10 = PWMx I/<br>01 = PWMx I/ | O pin pair is in f<br>O pin pair is in f<br>O pin pair is in f<br>O pin pair is in f | the Push-Pull<br>the Redundan   | Output mode<br>t Output mode   |                                |                             |        |

| oit 9            | OVRENH: Ov                   | erride Enable fo                                                                     | or PWMxH Pin                    | bit                            |                                |                             |        |

|                  |                              | 1 provides data<br>nerator provides                                                  |                                 |                                | I                              |                             |        |

| oit 8            | OVRENL: Ov                   | erride Enable fo                                                                     | or PWMxL Pin                    | bit                            |                                |                             |        |

|                  |                              | ) provides data<br>nerator provides                                                  | •                               |                                |                                |                             |        |

| bit 7-6          | OVRDAT<1:0                   | >: Data for PW                                                                       | MxH, PWMxL                      | Pins if Override               | e is Enabled bi                | ts                          |        |

|                  |                              | = 1, OVRDAT1<br>= 1, OVRDAT0                                                         |                                 |                                |                                |                             |        |

| oit 5-4          | FLTDAT<1:0>                  | State for PWN                                                                        | MxH and PWN                     | IxL Pins if FLTN               | MOD<1:0> are                   | Enabled bits <sup>(2)</sup> |        |

|                  | If Fault is activ            | LCONx<15>) =<br>ve, then FLTDA<br>ve, then FLTDA                                     | T1 provides th                  | e state for the I              | •                              |                             |        |

|                  | IFLTMOD (FC                  | LCONx<15>) =                                                                         | 1: Independe                    | nt Fault Mode:                 | or the PWMxH                   | nin                         |        |

2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

#### REGISTER 19-21: ADMOD1L: ADC INPUT MODE CONTROL REGISTER 1 LOW

| U-0      | U-0     | U-0    | U-0    | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------|---------|--------|--------|--------|--------|--------|--------|

| —        | —       | —      | —      | DIFF21 | SIGN21 | DIFF20 | SIGN20 |

| bit 15   |         | •      | •      |        |        |        | bit 8  |

|          |         |        |        |        |        |        |        |

| R/W-0    | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| DIFF19   | SIGN19  | DIFF18 | SIGN18 | DIFF17 | SIGN17 | DIFF16 | SIGN16 |

| bit 7    |         |        | •      |        |        |        | bit 0  |

|          |         |        |        |        |        |        |        |

| Legend:  | Legend: |        |        |        |        |        |        |

| <u> </u> | ,       |        |        |        |        |        |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-1(odd) DIFF<21:16>: Differential-Mode for Corresponding Analog Inputs bits

1 = Channel is differential

0 = Channel is single-ended

bit 10-0 (even) SIGN<21:16>: Output Data Sign for Corresponding Analog Inputs bits

1 = Channel output data is signed

0 = Channel output data is unsigned

### REGISTER 19-26: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5)

|        | •   | ,   |       |       |                |       |       |

|--------|-----|-----|-------|-------|----------------|-------|-------|

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

| _      | —   |     |       | TF    | RGSRC(4x+1)<4: | 0>    |       |

| bit 15 |     |     |       |       |                |       | bit 8 |

|        |     |     |       |       |                |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

| _      | —   | —   |       | Т     | RGSRC(4x)<4:0  | >     |       |

| bit 7  |     |     |       |       |                |       | bit 0 |

|        |     |     |       |       |                |       |       |

#### Legend:

| •                 |                  |                               |                    |  |

|-------------------|------------------|-------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as 'O'             |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |  |

#### bit 15-13 Unimplemented: Read as '0'

bit 12-8 TRGSRC(4x+1)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

| 11111 = ADTRG31                               |

|-----------------------------------------------|

| 11110 = Reserved                              |

| 11101 = Reserved                              |

| 11100 = PWM Generator 5 current-limit trigger |

| 11011 = PWM Generator 4 current-limit trigger |

| 11010 = PWM Generator 3 current-limit trigger |

| 11001 = PWM Generator 2 current-limit trigger |

| 11000 = PWM Generator 1 current-limit trigger |

| 10111 = Output Compare 2 trigger              |

| 10110 = Output Compare 1 trigger              |

| 10101 = Reserved                              |

| 10100 = Reserved                              |

| 10011 = PWM Generator 5 secondary trigger     |

| 10010 = PWM Generator 4 secondary trigger     |

| 10001 = PWM Generator 3 secondary trigger     |

| 10000 = PWM Generator 2 secondary trigger     |

| 01111 = PWM Generator 1 secondary trigger     |

| 01110 = PWM secondary Special Event Trigger   |

| 01101 = Timer2 period match                   |

| 01100 = Timer1 period match                   |

| 01011 = Reserved                              |

| 01010 = Reserved                              |

| 01001 = PWM Generator 5 primary trigger       |

| 01000 = PWM Generator 4 primary trigger       |

| 00111 = PWM Generator 3 primary trigger       |

| 00110 = PWM Generator 2 primary trigger       |

| 00101 = PWM Generator 1 primary trigger       |

| 00100 = PWM Special Event Trigger             |

| 00011 = Reserved                              |

| 00010 = Level software trigger                |

| 00001 = Common software trigger               |

| 00000 = No trigger is enabled                 |

| Unimplemented: Read as '0'                    |

#### bit 7-5 Unimplemented: Read as '0'

#### **REGISTER 20-2: CMPxDAC: COMPARATOR x DAC CONTROL REGISTER**

| U-0             | U-0         | U-0              | U-0           | R/W-0                              | R/W-0           | R/W-0              | R/W-0 |

|-----------------|-------------|------------------|---------------|------------------------------------|-----------------|--------------------|-------|

| _               | —           | _                | —             |                                    | CMREF           | -<11:8>            |       |

| bit 15          |             |                  |               | •                                  |                 |                    | bit 8 |

|                 |             |                  |               |                                    |                 |                    |       |

| R/W-0           | R/W-0       | R/W-0            | R/W-0         | R/W-0                              | R/W-0           | R/W-0              | R/W-0 |

|                 |             |                  | CMRE          | F<7:0>                             |                 |                    |       |

| bit 7           |             |                  |               |                                    |                 |                    | bit 0 |

|                 |             |                  |               |                                    |                 |                    |       |

| Legend:         |             |                  |               |                                    |                 |                    |       |

| R = Readable    | bit         | W = Writable bit |               | U = Unimplemented bit, read as '0' |                 |                    |       |

| -n = Value at F | POR         | '1' = Bit is set |               | '0' = Bit is cleared               |                 | x = Bit is unknown |       |

|                 |             |                  |               |                                    |                 |                    |       |

| bit 15-12       | Unimplemen  | ted: Read as 'd  | )'            |                                    |                 |                    |       |

| bit 11-0        | CMREF<11:0  | >: Comparator    | Reference Vo  | oltage Select bi                   | ts              |                    |       |

|                 | 11111111111 | .11              |               |                                    |                 |                    |       |

|                 | •           |                  |               |                                    |                 |                    |       |

|                 | •           |                  |               |                                    |                 |                    |       |

|                 | •           | = ([CMREF        | <11:0>] * (AV | DD)/4096) volts                    | s (EXTREF = 0   | )                  |       |

|                 | •           | or ([CMRI        | EF<11:0>] * ( | EXTREF)/409                        | 6) volts (EXTRE | EF = 1)            |       |

|                 | •           |                  |               |                                    |                 |                    |       |

|                 | •           |                  |               |                                    |                 |                    |       |

|                 |             |                  |               |                                    |                 |                    |       |

#### TABLE 23-2: CONFIGURATION BITS DESCRIPTION

| Bit Field              | Description                                                                                                                                                                                                             |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSS<1:0>               | Boot Segment Code-Protect Level bits                                                                                                                                                                                    |

|                        | 11 = Boot Segment is not code-protected other than BWRP                                                                                                                                                                 |

|                        | 10 = Standard security                                                                                                                                                                                                  |

| BSEN                   | 0x = High security<br>Boot Segment Control bit                                                                                                                                                                          |

| DSEN                   | 1 = No Boot Segment is enabled                                                                                                                                                                                          |

|                        | 0 = Boot Segment size is determined by the BSLIM<12:0> bits                                                                                                                                                             |

| BWRP                   | Boot Segment Write-Protect bit                                                                                                                                                                                          |

|                        | 1 = Boot Segment can be written<br>0 = Boot Segment is write-protected                                                                                                                                                  |

| BSLIM<12:0>            | Boot Segment Flash Page Address Limit bits                                                                                                                                                                              |

|                        | Contains the last active Boot Segment page. The value to be programmed is the inverted page address, such that programming additional '0's can only increase the Boot Segment size (i.e., 0x1FFD = 2 Pages or 1024 IW). |

| GSS<1:0>               | General Segment Code-Protect Level bits                                                                                                                                                                                 |

|                        | 11 = User program memory is not code-protected                                                                                                                                                                          |

|                        | 10 = Standard security<br>0x = High security                                                                                                                                                                            |

| GWRP                   | General Segment Write-Protect bit                                                                                                                                                                                       |

| owna                   | 1 = User program memory is not write-protected                                                                                                                                                                          |

|                        | 0 = User program memory is write-protected                                                                                                                                                                              |

| CWRP                   | Configuration Segment Write-Protect bit                                                                                                                                                                                 |

|                        | <ul><li>1 = Configuration data is not write-protected</li><li>0 = Configuration data is write-protected</li></ul>                                                                                                       |

| CSS<2:0>               | Configuration Segment Code-Protect Level bits                                                                                                                                                                           |

|                        | 111 = Configuration data is not code-protected                                                                                                                                                                          |

|                        | 110 = Standard security<br>10x = Enhanced security                                                                                                                                                                      |

|                        | 0xx = High security                                                                                                                                                                                                     |

| BTSWP                  | BOOTSWP Instruction Enable/Disable bit                                                                                                                                                                                  |

|                        | 1 = BOOTSWP instruction is disabled                                                                                                                                                                                     |

|                        | 0 = BOOTSWP instruction is enabled                                                                                                                                                                                      |

| BSEQ<11:0>             | Boot Sequence Number bits (Dual Partition modes only)                                                                                                                                                                   |

|                        | Relative value defining which partition will be active after device Reset; the partition<br>containing a lower boot number will be active.                                                                              |

| IBSEQ<11:0>            | Inverse Boot Sequence Number bits (Dual Partition modes only)                                                                                                                                                           |

|                        | The one's complement of BSEQ<11:0>; must be calculated by the user and written for                                                                                                                                      |

|                        | device programming. If BSEQx and IBSEQx are not complements of each other, the Boot Sequence Number is considered to be invalid.                                                                                        |

| AIVTDIS <sup>(1)</sup> | Alternate Interrupt Vector Table bit                                                                                                                                                                                    |

|                        | 1 = Alternate Interrupt Vector Table is disabled                                                                                                                                                                        |

| IESO                   | 0 = Alternate Interrupt Vector Table is enabled if INTCON2<8> = 1                                                                                                                                                       |

| IESU                   | Two-Speed Oscillator Start-up Enable bit<br>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator                                                                                  |

|                        | source when ready                                                                                                                                                                                                       |

|                        | 0 = Starts up device with the user-selected oscillator source                                                                                                                                                           |

| PWMLOCK                | PWMx Lock Enable bit                                                                                                                                                                                                    |

|                        | 1 = Certain PWMx registers may only be written after a key sequence                                                                                                                                                     |

|                        | 0 = PWMx registers may be written without a key sequence                                                                                                                                                                |

Note 1: The Boot Segment must be present to use the Alternate Interrupt Vector Table.

| <b>TABLE 24-2:</b> | INSTRUCTION SET OVERVIEW | (CONTINUED) |

|--------------------|--------------------------|-------------|

|                    |                          |             |

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                                 | Assembly Syntax             | Description                                            | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected             |

|--------------------|----------------------|-------------------------------------------------|-----------------------------|--------------------------------------------------------|---------------|-------------------------------|--------------------------------------|

| 26                 | CTXTSWP              | CTXTSWP                                         | #lit3                       | Switch CPU register context to context defined by lit3 | 1             | 2                             | None                                 |