Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

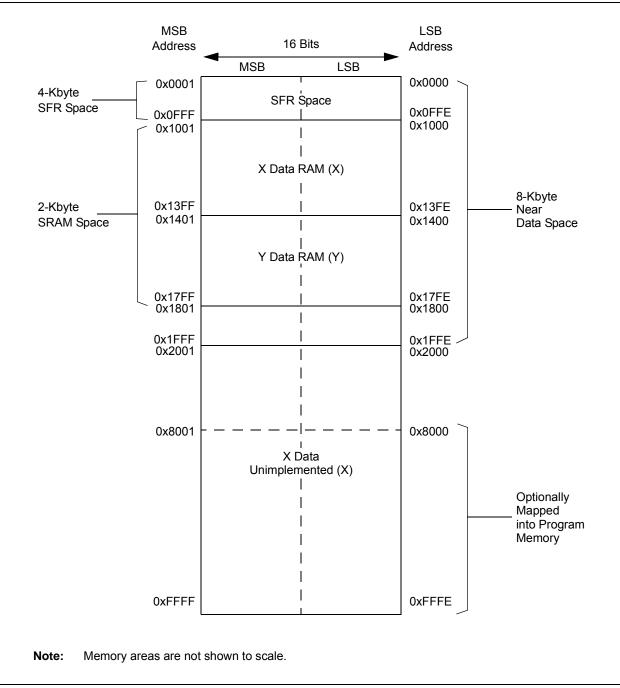

#### FIGURE 4-6: DATA MEMORY MAP FOR dsPIC33EP16GS50X DEVICES

### TABLE 4-16: ADC REGISTER MAP (CONTINUED)

| SFR<br>Name | Addr. | Bit 15                 | Bit 14                | Bit 13                 | Bit 12                 | Bit 11                  | Bit 10                 | Bit 9                  | Bit 8                  | Bit 7       | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1                  | Bit 0                   | All<br>Resets |

|-------------|-------|------------------------|-----------------------|------------------------|------------------------|-------------------------|------------------------|------------------------|------------------------|-------------|---------|----------|----------|----------|----------|------------------------|-------------------------|---------------|

| ADLVLTRGL   | 03D0  | LVLEN15 <sup>(1)</sup> | LVLEN14               | LVLEN13 <sup>(1)</sup> | LVLEN12 <sup>(2)</sup> | LVLEN11 <sup>(2)</sup>  | LVLEN10 <sup>(2)</sup> | LVLEN9 <sup>(2)</sup>  | LVLEN8 <sup>(2)</sup>  | LVLEN7      | LVLEN6  | LVLEN5   | LVLEN4   | LVLEN3   | LVLEN2   | LVLEN1                 | LVLEN0                  | 0000          |

| ADLVLTRGH   | 03D2  | _                      |                       | -                      | _                      | _                       |                        | _                      | _                      | -           |         | LVLEN21  | LVLEN20  | LVLEN19  | LVLEN18  | LVLEN17 <sup>(2)</sup> | LVLEN16 <sup>(1)</sup>  | 0000          |

| ADCORE0L    | 03D4  | —                      |                       | _                      | _                      | _                       |                        |                        |                        |             |         | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE0H    | 03D6  | -                      | -                     | -                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADCORE1L    | 03D8  | _                      |                       | -                      | _                      | _                       |                        |                        |                        |             |         |          |          |          | 0000     |                        |                         |               |

| ADCORE1H    | 03DA  | —                      |                       | _                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | _           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADCORE2L    | 03DC  | -                      | -                     | -                      | _                      | -                       | _                      |                        |                        |             | _       | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE2H    | 03DE  | _                      |                       | -                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADCORE3L    | 03E0  | —                      |                       | _                      | _                      | _                       |                        |                        |                        |             |         | SAMO     | C<9:0>   |          |          |                        |                         | 0000          |

| ADCORE3H    | 03E2  | -                      | -                     | -                      | EISEL2                 | EISEL1                  | EISEL0                 | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                  | ADCS0                   | 0000          |

| ADEIEL      | 03F0  | EIEN15 <sup>(1)</sup>  | EIEN14 <sup>(2)</sup> | EIEN13 <sup>(1)</sup>  | EIEN12 <sup>(2)</sup>  | EIEN11 <sup>(2)</sup>   | EIEN10 <sup>(2)</sup>  | EIEN9 <sup>(2)</sup>   | EIEN8 <sup>(2)</sup>   | EIEN7       | EIEN6   | EIEN5    | EIEN4    | EIEN3    | EIEN2    | EIEN1                  | EIEN0                   | 0000          |

| ADEIEH      | 03F2  | _                      | _                     | _                      | _                      | _                       | _                      | _                      | _                      | _           | _       | EIEN21   | EIEN20   | EIEN19   | EIEN18   | EIEN17 <sup>(2)</sup>  | EIEN16 <sup>(1)</sup>   | 0000          |

| ADEISTATL   | 03F8  | EISTAT15(1)            | EISTAT14(2)           | EISTAT13(1)            | EISTAT12(2)            | EISTAT11 <sup>(2)</sup> | EISTAT10(2)            | EISTAT9 <sup>(2)</sup> | EISTAT8 <sup>(2)</sup> | EISTAT7     | EISTAT6 | EISTAT5  | EISTAT4  | EISTAT3  | EISTAT2  | EISTAT1                | EISTAT0                 | 0000          |

| ADEISTATH   | 03FA  | _                      | _                     | _                      | _                      | _                       | _                      | _                      | _                      | _           | _       | EISTAT21 | EISTAT20 | EISTAT19 | EISTAT18 | EISTAT17(2)            | EISTAT16 <sup>(1)</sup> | 0000          |

| ADCON5L     | 0400  | SHRRDY                 | _                     | -                      | _                      | C3RDY                   | C2RDY                  | C1RDY                  | CORDY                  | SHRPWR      | _       | -        | -        | C3PWR    | C2PWR    | C1PWR                  | C0PWR                   | 0000          |

| ADCON5H     | 0402  | _                      | _                     | _                      | _                      | WARMTIME3               | WARMTIME2              | WARMTIME1              | WARMTIME0              | SHRCIE      | _       | _        | _        | C3CIE    | C2CIE    | C1CIE                  | C0CIE                   | 0000          |

| ADCALOL     | 0404  | CAL1RDY                | _                     | _                      | _                      | _                       | CAL1DIFF               | CAL1EN                 | CAL1RUN                | CALORDY     | _       | _        | _        | _        | CAL0DIFF | CAL0EN                 | CALORUN                 | 0000          |

| ADCAL0H     | 0406  | CAL3RDY                | _                     | _                      | _                      | _                       | CAL3DIFF               | CAL3EN                 | CAL3RUN                | CAL2RDY     | _       | _        | _        | _        | CAL2DIFF | CAL2EN                 | CAL2RUN                 | 0000          |

| ADCAL1H     | 040A  | CSHRRDY                | -                     | _                      | _                      | _                       | CSHRDIFF               | CSHREN                 | CSHRRUN                | —           | -       | _        | —        | _        | _        | _                      | —                       | 0000          |

| ADCBUF0     | 040C  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 0 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF1     | 040E  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 1 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF2     | 0410  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 2 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF3     | 0412  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 3 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF4     | 0414  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 4 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF5     | 0416  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 5 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF6     | 041B  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 6 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF7     | 041A  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 7 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF8     | 041C  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 8 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF9     | 041E  |                        |                       |                        |                        |                         |                        |                        | ADC Da                 | ta Buffer 9 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF10    | 0420  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 10 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF11    | 0422  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 11 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF12    | 0424  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 12 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF13    | 0426  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 13 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF14    | 0428  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 14 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF15    | 042A  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 15 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF16    | 042C  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 16 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF17    | 042E  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 17 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF18    | 0430  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 18 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF19    | 0432  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 19 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF20    | 0434  |                        |                       |                        |                        |                         |                        |                        | ADC Dat                | a Buffer 20 |         |          |          |          |          |                        |                         | 0000          |

| ADCBUF21    | 0436  |                        |                       |                        |                        |                         |                        |                        |                        | a Buffer 21 |         |          |          |          |          |                        |                         | 0000          |

dsPIC33EPXXGS50X FAMILY

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

Implemented on dsPIC33EPXXGS506 devices only.

Implemented on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices only.

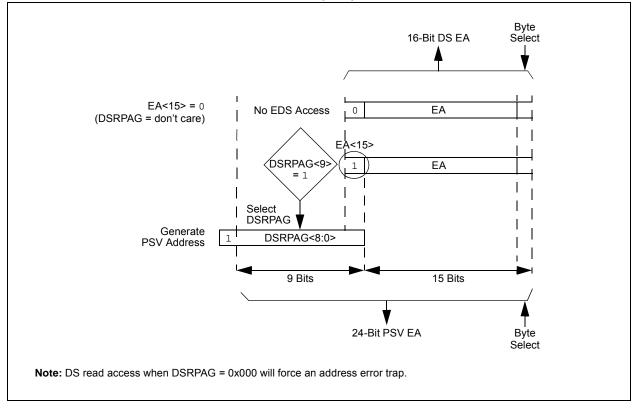

### 4.5.1 PAGED MEMORY SCHEME

The dsPIC33EPXXGS50X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the base Data Space address is used in conjunction with the Data Space Page (DSRPAG) register to form the Program Space Visibility (PSV) address.

The Data Space Page (DSRPAG) register is located in the SFR space. Construction of the PSV address is shown in Figure 4-9. When DSRPAG<9> = 1 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit PSV read address. The paged memory scheme provides access to multiple 32-Kbyte windows in the PSV memory. The Data Space Page (DSRPAG) register, in combination with the upper half of the Data Space address, can provide up to 8 Mbytes of PSV address space. The paged data memory space is shown in Figure 4-10.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG.

### FIGURE 4-9: PROGRAM SPACE VISIBILITY (PSV) READ ADDRESS GENERATION

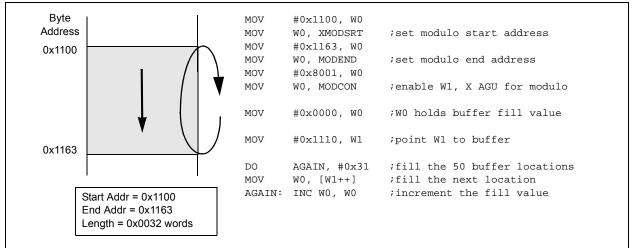

### 4.7 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.7.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-2).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.7.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags, as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W (XWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-2). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W (YWM) register, to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit (MODCON<14>) is set.

#### FIGURE 4-12: MODULO ADDRESSING OPERATION EXAMPLE

### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| —      | —   | —   | —   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

| R-0     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| VECNUM7 | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7   | •       |         |         |         |         | ·       | bit 0   |

| Legend:       |                                                                                 |                                |                       |                    |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------|--------------------------------|-----------------------|--------------------|--|--|--|--|--|--|

| R = Readabl   | e bit                                                                           | W = Writable bit               | U = Unimplemented bit | read as '0'        |  |  |  |  |  |  |

| -n = Value at | POR                                                                             | '1' = Bit is set               | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |  |

| bit 15-12     | Unimple                                                                         | mented: Read as '0'            |                       |                    |  |  |  |  |  |  |

| bit 11-8      | ILR<3:0>                                                                        | New CPU Interrupt Priority     | Level bits            |                    |  |  |  |  |  |  |

|               | 1111 = CPU Interrupt Priority Level is 15                                       |                                |                       |                    |  |  |  |  |  |  |

|               | •                                                                               |                                |                       |                    |  |  |  |  |  |  |

|               | •                                                                               |                                |                       |                    |  |  |  |  |  |  |

|               | •                                                                               |                                |                       |                    |  |  |  |  |  |  |

|               |                                                                                 | PU Interrupt Priority Level is |                       |                    |  |  |  |  |  |  |

|               | 0000 = CPU Interrupt Priority Level is 0                                        |                                |                       |                    |  |  |  |  |  |  |

| bit 7-0       | VECNUM<7:0>: Vector Number of Pending Interrupt bits                            |                                |                       |                    |  |  |  |  |  |  |

|               | 11111111 = 255, Reserved; do not use                                            |                                |                       |                    |  |  |  |  |  |  |

|               | •                                                                               |                                |                       |                    |  |  |  |  |  |  |

|               | •                                                                               |                                |                       |                    |  |  |  |  |  |  |

|               | •                                                                               |                                |                       |                    |  |  |  |  |  |  |

|               | 00001001 = 9, IC1 – Input Capture 1                                             |                                |                       |                    |  |  |  |  |  |  |

|               | 00001000 = 8, INT0 – External Interrupt 0<br>00000111 = 7, Reserved; do not use |                                |                       |                    |  |  |  |  |  |  |

|               | 00000111 = 7, Reserved, do not use<br>00000110 = 6. Generic soft error trap     |                                |                       |                    |  |  |  |  |  |  |

|               | 00000101 = 5, Reserved; do not use                                              |                                |                       |                    |  |  |  |  |  |  |

|               | 00000100 = 4, Math error trap                                                   |                                |                       |                    |  |  |  |  |  |  |

|               | 0000011 = 3, Stack error trap                                                   |                                |                       |                    |  |  |  |  |  |  |

|               | 0000001                                                                         | 0 = 2, Generic hard trap       |                       |                    |  |  |  |  |  |  |

|               |                                                                                 | 1 = 1, Address error trap      |                       |                    |  |  |  |  |  |  |

|               | 0000000                                                                         | 0 = 0, Oscillator fail trap    |                       |                    |  |  |  |  |  |  |

### 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXGS50X family devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

### 9.1 Clock Frequency and Clock Switching

The dsPIC33EPXXGS50X family devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

### 9.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXGS50X family devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

|  | REGISTER 9-2: | PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 |

|--|---------------|----------------------------------------------------|

|--|---------------|----------------------------------------------------|

| U-0          | U-0                                    | U-0                                        | U-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|----------------------------------------|--------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| —            |                                        |                                            | —              | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |  |

| pit 15       |                                        |                                            |                |                   | I               |                 | bit 8 |  |  |  |  |  |

| U-0          | U-0                                    | U-0                                        | U-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            | _                                      | _                                          | —              | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |  |

| bit 7        |                                        | ·                                          |                |                   |                 |                 | bit ( |  |  |  |  |  |

| Legend:      |                                        |                                            |                |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                 | W = Writable I                             | oit            | U = Unimplen      | nented bit, rea | ıd as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                  | '1' = Bit is set                           |                | '0' = Bit is clea |                 | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-12    | Unimplom                               | nted. Dood oo '                            | .,             |                   |                 |                 |       |  |  |  |  |  |

| bit 15-12    | -                                      | ented: Read as '0<br>out Capture 4 Moo     |                | i+                |                 |                 |       |  |  |  |  |  |

|              | •                                      | apture 4 module i                          |                | iit.              |                 |                 |       |  |  |  |  |  |

|              |                                        | apture 4 module i                          |                |                   |                 |                 |       |  |  |  |  |  |

| oit 10       | IC3MD: Inp                             | IC3MD: Input Capture 3 Module Disable bit  |                |                   |                 |                 |       |  |  |  |  |  |

|              | 1 = Input Capture 3 module is disabled |                                            |                |                   |                 |                 |       |  |  |  |  |  |

|              | 0 = Input Ca                           | apture 3 module i                          | s enabled      |                   |                 |                 |       |  |  |  |  |  |

| bit 9        | IC2MD: Inp                             | ut Capture 2 Moc                           | lule Disable b | it                |                 |                 |       |  |  |  |  |  |

|              |                                        | apture 2 module i                          |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                        | apture 2 module i                          |                |                   |                 |                 |       |  |  |  |  |  |

| bit 8        | -                                      | IC1MD: Input Capture 1 Module Disable bit  |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                        | apture 1 module i<br>apture 1 module i     |                |                   |                 |                 |       |  |  |  |  |  |

| bit 7-4      |                                        | ented: Read as '(                          |                |                   |                 |                 |       |  |  |  |  |  |

| bit 3        | •                                      | utput Compare 4                            |                | ole hit           |                 |                 |       |  |  |  |  |  |

|              |                                        | Compare 4 modu                             |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                        | Compare 4 modu                             |                |                   |                 |                 |       |  |  |  |  |  |

| bit 2        | OC3MD: O                               | OC3MD: Output Compare 3 Module Disable bit |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                        | Compare 3 modu<br>Compare 3 modu           |                |                   |                 |                 |       |  |  |  |  |  |

| bit 1        | •                                      | utput Compare 2                            |                | ole bit           |                 |                 |       |  |  |  |  |  |

|              |                                        | Compare 2 modu<br>Compare 2 modu           |                |                   |                 |                 |       |  |  |  |  |  |

| bit 0        |                                        | utput Compare 1                            |                | ole bit           |                 |                 |       |  |  |  |  |  |

|              | 1 = Output                             |                                            |                |                   |                 |                 |       |  |  |  |  |  |

| Function     | RPnR<5:0> | Output Name                                                 |

|--------------|-----------|-------------------------------------------------------------|

| Default PORT | 000000    | RPn tied to Default Pin                                     |

| U1TX         | 000001    | RPn tied to UART1 Transmit                                  |

| U1RTS        | 000010    | RPn tied to UART1 Request-to-Send                           |

| U2TX         | 000011    | RPn tied to UART2 Transmit                                  |

| U2RTS        | 000100    | RPn tied to UART2 Request-to-Send                           |

| SDO1         | 000101    | RPn tied to SPI1 Data Output                                |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output                               |

| SS1          | 000111    | RPn tied to SPI1 Slave Select                               |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                                |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                               |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                               |

| OC1          | 010000    | RPn tied to Output Compare 1 Output                         |

| OC2          | 010001    | RPn tied to Output Compare 2 Output                         |

| OC3          | 010010    | RPn tied to Output Compare 3 Output                         |

| OC4          | 010011    | RPn tied to Output Compare 4 Output                         |

| ACMP1        | 011000    | RPn tied to Analog Comparator 1 Output                      |

| ACMP2        | 011001    | RPn tied to Analog Comparator 2 Output                      |

| ACMP3        | 011010    | RPn tied to Analog Comparator 3 Output                      |

| SYNCO1       | 101101    | RPn tied to PWM Primary Master Time Base Sync Output        |

| SYNCO2       | 101110    | RPn tied to PWM Secondary Master Time Base Sync Output      |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output                          |

| ACMP4        | 110010    | RPn tied to Analog Comparator 4 Output                      |

| PWM4H        | 110011    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM4L        | 110100    | RPn tied to PWM Output Pins Associated with PWM Generator 4 |

| PWM5H        | 110101    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

| PWM5L        | 110110    | RPn tied to PWM Output Pins Associated with PWM Generator 5 |

### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| R/W-0           | R/W-0                                                                | R/W-0                                                                                                                              | R/W-0                                      | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|-----------------|-----------------|--------|

| FLT2R7          | FLT2R6                                                               | FLT2R5                                                                                                                             | FLT2R4                                     | FLT2R3           | FLT2R2          | FLT2R1          | FLT2R0 |

| bit 15          |                                                                      |                                                                                                                                    |                                            |                  |                 |                 | bit 8  |

|                 |                                                                      |                                                                                                                                    |                                            |                  |                 |                 |        |

| R/W-0           | R/W-0                                                                | R/W-0                                                                                                                              | R/W-0                                      | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| FLT1R7          | FLT1R6                                                               | FLT1R5                                                                                                                             | FLT1R4                                     | FLT1R3           | FLT1R2          | FLT1R1          | FLT1R0 |

| bit 7           |                                                                      |                                                                                                                                    |                                            |                  |                 |                 | bit (  |

|                 |                                                                      |                                                                                                                                    |                                            |                  |                 |                 |        |

| Legend:         |                                                                      |                                                                                                                                    |                                            |                  |                 |                 |        |

| R = Readable    |                                                                      | W = Writable                                                                                                                       |                                            | •                | nented bit, rea |                 |        |

| -n = Value at I | POR                                                                  | '1' = Bit is set                                                                                                                   |                                            | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

| bit 7-0         | 10110100 =<br>000000001 =<br>00000000 =<br>FLT1R<7:0>:<br>10110101 = | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>Assign PWM<br>Input tied to RI<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 1 (FLT1)<br>⊃181 | to the Corresp   | oonding RPn Pi  | in bits         |        |

|                 |                                                                      | Input tied to RI<br>Input tied to Ve                                                                                               |                                            |                  |                 |                 |        |

### REGISTER 10-8: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

| R/W-0         |        |                  |        |                  |                  |                 |        |

|---------------|--------|------------------|--------|------------------|------------------|-----------------|--------|

|               | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT8R7        | FLT8R6 | FLT8R5           | FLT8R4 | FLT8R3           | FLT8R2           | FLT8R1          | FLT8R0 |

| bit 15        |        |                  |        |                  |                  |                 | bit 8  |

|               |        |                  |        |                  |                  |                 |        |

| R/W-0         | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT7R7        | FLT7R6 | FLT7R5           | FLT7R4 | FLT7R3           | FLT7R2           | FLT7R1          | FLT7R0 |

| bit 7         |        |                  |        |                  |                  |                 | bit C  |

|               |        |                  |        |                  |                  |                 |        |

| Legend:       |        |                  |        |                  |                  |                 |        |

| R = Readable  | e bit  | W = Writable     | bit    | U = Unimpler     | nented bit, read | d as '0'        |        |

| -n = Value at | POR    | '1' = Bit is set | :      | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-8      |        | Assign PWM       | · · ·  | to the Corresp   | onding RPn Pi    | n bits          |        |

### REGISTER 10-19: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

# REGISTER 19-26: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5)

|        | •   | ,   |       |       |                |       |       |

|--------|-----|-----|-------|-------|----------------|-------|-------|

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

| _      | —   | -   |       | TF    | RGSRC(4x+1)<4: | 0>    |       |

| bit 15 |     |     |       |       |                |       | bit 8 |

|        |     |     |       |       |                |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0          | R/W-0 | R/W-0 |

| _      | —   | —   |       | Т     | RGSRC(4x)<4:0  | >     |       |

| bit 7  |     |     |       |       |                |       | bit 0 |

|        |     |     |       |       |                |       |       |

## Legend:

| •                 |                  |                               |                    |  |

|-------------------|------------------|-------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as 'O'             |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |  |

### bit 15-13 Unimplemented: Read as '0'

bit 12-8 TRGSRC(4x+1)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

| 11111 <b>=</b> A | ADTRG31                               |

|------------------|---------------------------------------|

| 11110 <b>= F</b> | Reserved                              |

| 11101 <b>= F</b> | Reserved                              |

| 11100 = F        | PWM Generator 5 current-limit trigger |

| 11011 <b>= F</b> | PWM Generator 4 current-limit trigger |

| 11010 = F        | PWM Generator 3 current-limit trigger |

| 11001 <b>=</b> F | PWM Generator 2 current-limit trigger |

|                  | PWM Generator 1 current-limit trigger |

| 10111 <b>= (</b> | Dutput Compare 2 trigger              |

|                  | Dutput Compare 1 trigger              |

| 10101 <b>= F</b> |                                       |

| 10100 <b>= F</b> |                                       |

|                  | PWM Generator 5 secondary trigger     |

|                  | PWM Generator 4 secondary trigger     |

|                  | PWM Generator 3 secondary trigger     |

|                  | PWM Generator 2 secondary trigger     |

|                  | PWM Generator 1 secondary trigger     |

|                  | PWM secondary Special Event Trigger   |

|                  | Timer2 period match                   |

|                  | Fimer1 period match                   |

| 01011 <b>= F</b> |                                       |

| 01010 = F        |                                       |

|                  | PWM Generator 5 primary trigger       |

|                  | PWM Generator 4 primary trigger       |

|                  | PWM Generator 3 primary trigger       |

|                  | PWM Generator 2 primary trigger       |

|                  | PWM Generator 1 primary trigger       |

|                  | PWM Special Event Trigger             |

| 00011 = F        |                                       |

|                  | Level software trigger                |

|                  | Common software trigger               |

|                  | No trigger is enabled                 |

| Unimplen         | nented: Read as '0'                   |

### bit 7-5 Unimplemented: Read as '0'

### 20.0 HIGH-SPEED ANALOG COMPARATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed Analog Comparator Module" (DS70005128) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The high-speed analog comparator module monitors current and/or voltage transients that may be too fast for the CPU and ADC to capture.

### 20.1 Features Overview

The SMPS comparator module offers the following major features:

- Four Rail-to-Rail Analog Comparators

- Dedicated 12-Bit DAC for each Analog Comparator

- Up to Six Selectable Input Sources per Comparator:

- Four external inputs

- Two internal inputs from the PGAx module

- Programmable Comparator Hysteresis

- Programmable Output Polarity

- Up to Two DAC Outputs to Device Pins

- Multiple Voltage References for the DAC:

External References (EXTREF1 or

- EXTREF2) - AVDD

- Interrupt Generation Capability

- Functional Support for PWMx:

- PWMx duty cycle control

- PWMx period control

- PWMx Fault detected

### TABLE 23-2: CONFIGURATION BITS DESCRIPTION

| Bit Field              | Description                                                                                                                                                                                                             |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSS<1:0>               | Boot Segment Code-Protect Level bits                                                                                                                                                                                    |

|                        | 11 = Boot Segment is not code-protected other than BWRP                                                                                                                                                                 |

|                        | 10 = Standard security                                                                                                                                                                                                  |

| BSEN                   | 0x = High security                                                                                                                                                                                                      |

| DSEN                   | Boot Segment Control bit<br>1 = No Boot Segment is enabled                                                                                                                                                              |

|                        | 0 = Boot Segment size is determined by the BSLIM<12:0> bits                                                                                                                                                             |

| BWRP                   | Boot Segment Write-Protect bit                                                                                                                                                                                          |

|                        | 1 = Boot Segment can be written<br>0 = Boot Segment is write-protected                                                                                                                                                  |

| BSLIM<12:0>            | Boot Segment Flash Page Address Limit bits                                                                                                                                                                              |

|                        | Contains the last active Boot Segment page. The value to be programmed is the inverted page address, such that programming additional '0's can only increase the Boot Segment size (i.e., 0x1FFD = 2 Pages or 1024 IW). |

| GSS<1:0>               | General Segment Code-Protect Level bits                                                                                                                                                                                 |

|                        | 11 = User program memory is not code-protected                                                                                                                                                                          |

|                        | 10 = Standard security<br>0x = High security                                                                                                                                                                            |

| GWRP                   | General Segment Write-Protect bit                                                                                                                                                                                       |

| owna                   | 1 = User program memory is not write-protected                                                                                                                                                                          |

|                        | 0 = User program memory is write-protected                                                                                                                                                                              |

| CWRP                   | Configuration Segment Write-Protect bit                                                                                                                                                                                 |

|                        | <ul><li>1 = Configuration data is not write-protected</li><li>0 = Configuration data is write-protected</li></ul>                                                                                                       |

| CSS<2:0>               | Configuration Segment Code-Protect Level bits                                                                                                                                                                           |

|                        | 111 = Configuration data is not code-protected                                                                                                                                                                          |

|                        | 110 = Standard security<br>10x = Enhanced security                                                                                                                                                                      |

|                        | 0xx = High security                                                                                                                                                                                                     |

| BTSWP                  | BOOTSWP Instruction Enable/Disable bit                                                                                                                                                                                  |

|                        | 1 = BOOTSWP instruction is disabled                                                                                                                                                                                     |

|                        | 0 = BOOTSWP instruction is enabled                                                                                                                                                                                      |

| BSEQ<11:0>             | Boot Sequence Number bits (Dual Partition modes only)                                                                                                                                                                   |

|                        | Relative value defining which partition will be active after device Reset; the partition<br>containing a lower boot number will be active.                                                                              |

| IBSEQ<11:0>            | Inverse Boot Sequence Number bits (Dual Partition modes only)                                                                                                                                                           |

|                        | The one's complement of BSEQ<11:0>; must be calculated by the user and written for                                                                                                                                      |

|                        | device programming. If BSEQx and IBSEQx are not complements of each other, the Boot Sequence Number is considered to be invalid.                                                                                        |

| AIVTDIS <sup>(1)</sup> | Alternate Interrupt Vector Table bit                                                                                                                                                                                    |

|                        | 1 = Alternate Interrupt Vector Table is disabled                                                                                                                                                                        |

| IESO                   | 0 = Alternate Interrupt Vector Table is enabled if INTCON2<8> = 1                                                                                                                                                       |

| IESU                   | Two-Speed Oscillator Start-up Enable bit<br>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator                                                                                  |

|                        | source when ready                                                                                                                                                                                                       |

|                        | 0 = Starts up device with the user-selected oscillator source                                                                                                                                                           |

| PWMLOCK                | PWMx Lock Enable bit                                                                                                                                                                                                    |

|                        | 1 = Certain PWMx registers may only be written after a key sequence                                                                                                                                                     |

|                        | 0 = PWMx registers may be written without a key sequence                                                                                                                                                                |

Note 1: The Boot Segment must be present to use the Alternate Interrupt Vector Table.

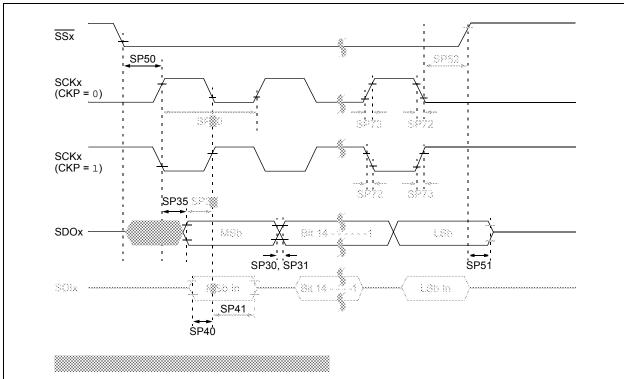

### FIGURE 26-17: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

### TABLE 26-44: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

| AC CHARACTERISTICS <sup>(2)</sup>   |                  |       | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |                                   |            |                                       |  |  |

|-------------------------------------|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------|------------|---------------------------------------|--|--|

| Param<br>No. Symbol Characteristics |                  | Min.  | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                      | Max. | Units                             | Conditions |                                       |  |  |

|                                     | Clock Parameters |       |                                                                                                                                                                                                                                                                          |      |                                   |            |                                       |  |  |

| AD50 TAD ADC Clock Period           |                  | 14.28 |                                                                                                                                                                                                                                                                          | _    | ns                                |            |                                       |  |  |

| Throughput Rate                     |                  |       |                                                                                                                                                                                                                                                                          |      |                                   |            |                                       |  |  |

| AD51                                | AD51 FTP SH0-SH3 |       | —                                                                                                                                                                                                                                                                        |      | 3.25                              |            | 70 MHz ADC clock, 12 bits, no pending |  |  |

|                                     |                  | SH4   | _                                                                                                                                                                                                                                                                        |      | 3.25 Msps conversion at time of t |            | conversion at time of trigger         |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is ensured, but not characterized.

#### TABLE 26-45: HIGH-SPEED ANALOG COMPARATOR MODULE SPECIFICATIONS

| AC/DC (                            | CHARAC | reristics <sup>(2)</sup>                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |          |                                                                                                                             |

|------------------------------------|--------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. Symbol Characteristic |        | Min.                                              | Тур.                                                                                                                                                                                                                                                                                    | Max. | Units | Comments |                                                                                                                             |

| CM10                               | VIOFF  | Input Offset Voltage                              | -35                                                                                                                                                                                                                                                                                     | ±5   | +35   | mV       |                                                                                                                             |

| CM11                               | VICM   | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                       | —    | AVDD  | V        |                                                                                                                             |

| CM13                               | CMRR   | Common-Mode<br>Rejection Ratio                    | 60                                                                                                                                                                                                                                                                                      | —    | _     | dB       |                                                                                                                             |

| CM14                               | TRESP  | Large Signal Response                             | _                                                                                                                                                                                                                                                                                       | 15   | _     | ns       | V+ input step of 100 mV while<br>V- input is held at AVDD/2. Delay<br>measured from analog input pin to<br>PWMx output pin. |

| CM15                               | VHYST  | Input Hysteresis                                  | 5                                                                                                                                                                                                                                                                                       | 10   | 20    | mV       | Depends on HYSSEL<1:0>                                                                                                      |

| CM16                               | TON    | Comparator Enabled to Valid Output                | _                                                                                                                                                                                                                                                                                       | —    | 1     | μs       |                                                                                                                             |

Note 1: These parameters are for design guidance only and are not tested in manufacturing.

2: The comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

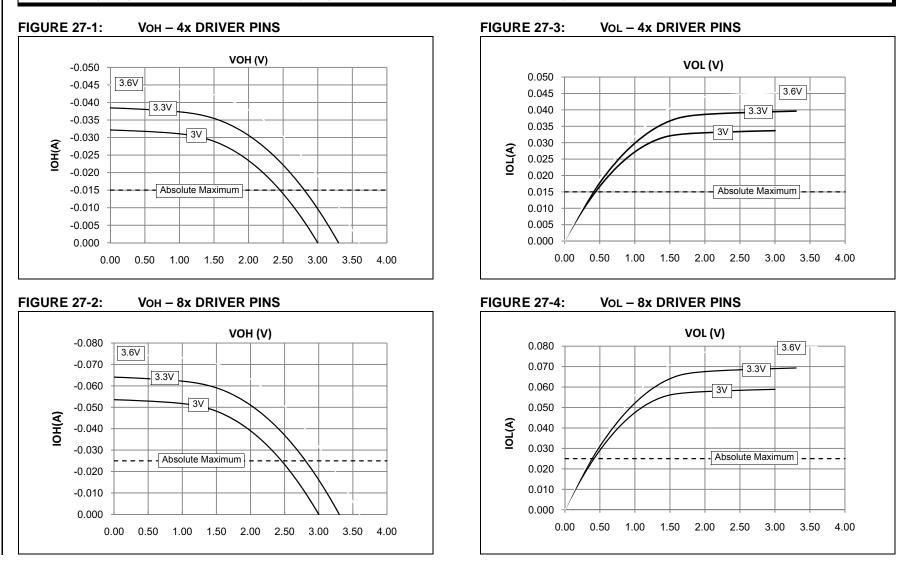

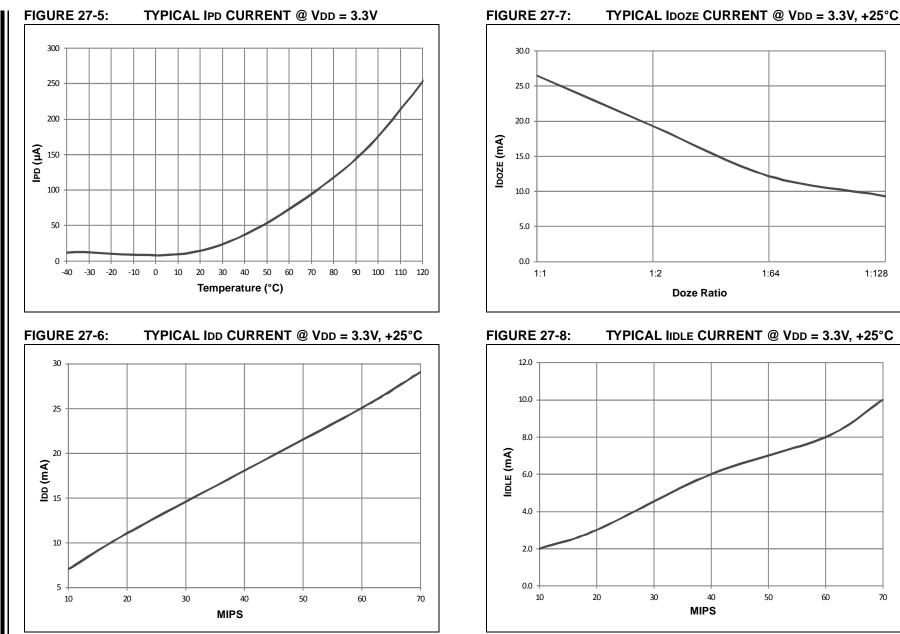

# 27.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

## 28.0 PACKAGING INFORMATION

### 28.1 Package Marking Information

28-Lead SOIC (.300")

Example

| 28-Lead UQFN | (6x6x0.55 mm) |

|--------------|---------------|

|--------------|---------------|

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN                                                                                                                                                                            | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note:  | : In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                        |  |  |  |

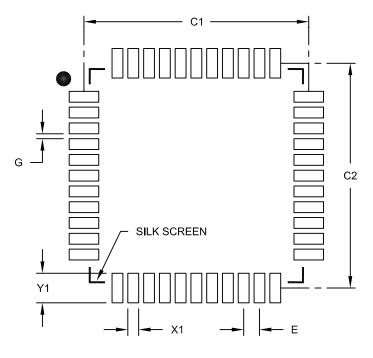

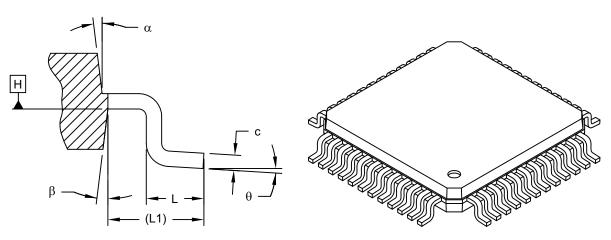

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### **RECOMMENDED LAND PATTERN**

|                          | Units            |      |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|------|----------|-------------|--|--|--|

| Dimension                | Dimension Limits |      | NOM      | MAX         |  |  |  |

| Contact Pitch            | E                |      | 0.80 BSC |             |  |  |  |

| Contact Pad Spacing      | C1               |      | 11.40    |             |  |  |  |

| Contact Pad Spacing      | C2               |      | 11.40    |             |  |  |  |

| Contact Pad Width (X44)  | X1               |      |          | 0.55        |  |  |  |

| Contact Pad Length (X44) | Y1               |      |          | 1.50        |  |  |  |

| Distance Between Pads    | G                | 0.25 |          |             |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

### 48-Lead Thin Quad Flatpack (Y8) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

SECTION A-A

|                          | MILLIMETERS |          |          |      |  |  |

|--------------------------|-------------|----------|----------|------|--|--|

| Dimension                | MIN         | NOM      | MAX      |      |  |  |

| Number of Leads          | Ν           |          | 48       |      |  |  |

| Lead Pitch               | е           | 0.50 BSC |          |      |  |  |

| Overall Height           | Α           | -        | -        | 1.20 |  |  |

| Standoff                 | A1          | 0.05     | -        | 0.15 |  |  |

| Molded Package Thickness | A2          | 0.95     | 1.00     | 1.05 |  |  |

| Foot Length              | L           | 0.45     | 0.60     | 0.75 |  |  |

| Footprint                | L1          | 1.00 REF |          |      |  |  |

| Foot Angle               | ¢           | 0°       | 3.5°     | 7°   |  |  |

| Overall Width            | E           |          | 9.00 BSC |      |  |  |

| Overall Length           | D           |          | 9.00 BSC |      |  |  |

| Molded Package Width     | E1          | 7.00 BSC |          |      |  |  |

| Molded Package Length    | D1          | 7.00 BSC |          |      |  |  |

| Lead Thickness           | С           | 0.09     | -        | 0.16 |  |  |

| Lead Width               | b           | 0.17     | 0.22     | 0.27 |  |  |

| Mold Draft Angle Top     | α           | 11°      | 12°      | 13°  |  |  |

| Mold Draft Angle Bottom  | β           | 11°      | 12°      | 13°  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A-B and D to be determined at center line between leads where leads exit plastic body at datum plane H

Microchip Technology Drawing C04-300-Y8 Rev A Sheet 2 of 2