Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

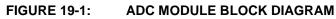

| Data Converters            | A/D 12x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

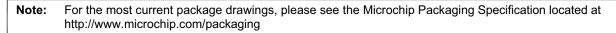

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502-i-2n |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI 7-5  | <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                           |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                      |

| bit 2   | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                       |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                         |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                        |

| Note 1: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                          |

- Note 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

### TABLE 4-13: I2C1 AND I2C2 REGISTER MAP

| SFR<br>Name | Addr.  | Bit 15    | Bit 14      | Bit 13    | Bit 12      | Bit 11     | Bit 10  | Bit 9                                    | Bit 8     | Bit 7       | Bit 6    | Bit 5      | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|--------|-----------|-------------|-----------|-------------|------------|---------|------------------------------------------|-----------|-------------|----------|------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1CONL    | 0200   | I2CEN     | _           | I2CSIDL   | SCLREL      | STRICT     | A10M    | DISSLW                                   | SMEN      | GCEN        | STREN    | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1CONH    | 0202   | —         | _           | —         | _           | _          | _       | —                                        | _         | _           | PCIE     | SCIE       | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C1STAT    | 0204   | ACKSTAT   | TRSTAT      | ACKTIM    | _           | _          | BCL     | GCSTAT                                   | ADD10     | IWCOL       | I2COV    | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 0206   | _         | —           | _         | _           | —          | _       |                                          |           |             |          | I2C1 Addr  | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 0208   | _         | —           | _         | _           | —          | _       |                                          |           |             | I2C1 SI  | ave Mode A | ddress Mask  | Register     |       |       |       | 0000          |

| I2C1BRG     | 020A   |           |             |           |             |            |         | E                                        | Baud Rate | Generator R | legister |            |              |              |       |       |       | 0000          |

| I2C1TRN     | 020C   | _         | —           | _         | _           | —          | _       | —                                        | _         |             |          |            | I2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1RCV     | 020E   | _         | —           | _         | _           | —          | _       | —                                        | _         |             |          |            | I2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2CON1    | 0210   | I2CEN     | —           | I2CSIDL   | SCLREL      | STRICT     | A10M    | DISSLW                                   | SMEN      | GCEN        | STREN    | ACKDT      | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2CON2    | 0212   | _         | _           | _         | _           | _          | _       | _                                        | _         | _           | PCIE     | SCIE       | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C2STAT    | 0214   | ACKSTAT   | TRSTAT      | ACKTIM    | _           | _          | BCL     | GCSTAT                                   | ADD10     | IWCOL       | I2COV    | D_A        | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 0216   | _         | _           | _         | _           | _          | _       |                                          |           |             |          | I2C2 Addr  | ess Register |              |       |       |       | 0000          |

| I2C2MSK     | 0218   | _         | —           | _         | _           | —          | _       | I2C2 Slave Mode Address Mask Register 00 |           |             |          |            |              |              | 0000  |       |       |               |

| I2C2BRG     | 021A   |           |             |           |             |            |         | E                                        | Baud Rate | Generator R | legister |            |              |              |       |       |       | 0000          |

| I2C2TRN     | 021C   | _         | —           | _         | _           | —          | _       | —                                        | _         |             |          |            | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2RCV     | 021E   | _         | _           | -         | —           | —          | _       | —                                        | —         |             |          |            | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| Legend:     | – unim | plemented | road as '0' | Peact val | ues are sho | we in hove | dooimal | •                                        | -         |             |          |            |              |              |       |       |       | •             |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                    | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                   | Bit 7    | Bit 6    | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|-------------------------------------------|--------|----------|--------|--------|--------|-------|-------------------------|----------|----------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN                                    | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                    | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1                                  | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                    | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                                         | _      | _        | _      | _      | _      | _     | UART1 Transmit Register |          |          |       |             |        |        |        |       | xxxx          |

| U1RXREG     | 0226  | _                                         | _      | _        | _      | _      | _      | _     | UART1 Receive Register  |          |          |       |             |        |        |        | 0000  |               |

| U1BRG       | 0228  | Baud Rate Generator Prescaler Register    |        |          |        |        |        |       |                         |          |          |       | 0000        |        |        |        |       |               |

| U2MODE      | 0230  | UARTEN                                    | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                    | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                                  | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                    | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                                         | _      | _        | _      | _      | —      | _     |                         |          |          | UART2 | Fransmit Re | gister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _                                         | _      | _        | _      | _      | _      | _     | UART2 Receive Register  |          |          |       |             |        |        |        |       | 0000          |

| U2BRG       | 0238  | 38 Baud Rate Generator Prescaler Register |        |          |        |        |        |       |                         |          | 0000     |       |             |        |        |        |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD |       | —      | ADCMD | 0000          |

| PMD2        | 0762  |        | —      | —      | -      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | -      |       | —     | -      | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3        | 0764  | Ι      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _      | _      | _     | I2C2MD | _     | 0000          |

| PMD4        | 0766  | Ι      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | _     | _      | _     | 0000          |

| PMD6        | 076A  | Ι      | _      | _      | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _     | _      | _     | 0000          |

| PMD7        | 076C  | Ι      | _      | _      | _      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | _     | _     | _      | _      | _     | PGA1MD | _     | 0000          |

| PMD8        | 076E  | _      | —      | _      | —      | _      | PGA2MD | ABGMD  | _      | _      | _     | —     | _      | _      | _     | CCSMD  |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: CONSTANT-CURRENT SOURCE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|-------|-------|----------|----------|----------|----------|----------|----------|---------------|

| ISRCCON     | 0500  | ISRCEN | _      |        | _      |        | OUTSEL2 | OUTSEL1 | OUTSEL0 | _     | _     | ISRCCAL5 | ISRCCAL4 | ISRCCAL3 | ISRCCAL2 | ISRCCAL1 | ISRCCAL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-25: PROGRAMMABLE GAIN AMPLIFIER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| PGA1CON     | 0504  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | _     | _     |       |       |       | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA1CAL     | 0506  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

| PGA2CON     | 0508  | PGAEN  | PGAOEN | SELPI2 | SELPI1 | SELPI0 | SELNI2 | SELNI1 | SELNI0 | —     | —     | _     | —     | _     | GAIN2  | GAIN1 | GAIN0 | 0000          |

| PGA2CAL     | 050A  | _      | —      | —      | —      | _      | —      | _      | _      | —     | —     |       |       | PGACA | L<5:0> |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PORTD REGISTER MAP FOR dsPIC33EPXXGS506 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------------|--------|--------|--------|--------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISD       | 0E30  |        |              |        |        |        |        |       | TRISD<15 | :0>   |       |       |       |       |       |       |       | FFFF          |

| PORTD       | 0E32  |        |              |        |        |        |        |       | RD<15:0  | >     |       |       |       |       |       |       |       | xxxx          |

| LATD        | 0E34  |        | LATD<15:0> 2 |        |        |        |        |       |          |       |       |       | xxxx  |       |       |       |       |               |

| ODCD        | 0E36  |        |              |        |        |        |        |       | ODCD<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| CNEND       | 0E38  |        |              |        |        |        |        |       | CNIED<15 | :0>   |       |       |       |       |       |       |       | 0000          |

| CNPUD       | 0E3A  |        |              |        |        |        |        |       | CNPUD<18 | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDD       | 0E3C  |        |              |        |        |        |        |       | CNPDD<15 | 5:0>  |       |       |       |       |       |       |       | 0000          |

| ANSELD      | 0E3E  |        | _            | ANSD13 | —      | _      | —      |       | -        | ANSD7 |       | _     | _     | -     | ANSD2 | _     |       | 6084          |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.6 Instruction Addressing Modes

The addressing modes shown in Table 4-38 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.6.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.6.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-38: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXGS50X family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior, contains the Global Interrupt Enable bit (GIE) and the Alternate Interrupt Vector Table Enable bit (AIVTEN).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

#### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt sources can be assigned to one of seven priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and Interrupt Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| R/W-0           | R/W-0                                                                            | R/W-0                                | R/W-0                                        | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|----------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|------------------|------------------|-----------------|---------|

| U2CTSR7         | U2CTSR6                                                                          | U2CTSR5                              | U2CTSR4                                      | U2CTSR3          | U2CTSR2          | U2CTSR1         | U2CTSR0 |

| bit 15          |                                                                                  |                                      | ·                                            | ·                |                  | ·               | bit 8   |

|                 |                                                                                  |                                      |                                              |                  |                  |                 |         |

| R/W-0           | R/W-0                                                                            | R/W-0                                | R/W-0                                        | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| U2RXR7          | U2RXR6                                                                           | U2RXR5                               | U2RXR4                                       | U2RXR3           | U2RXR2           | U2RXR1          | U2RXR0  |

| bit 7           |                                                                                  |                                      |                                              |                  |                  |                 | bit (   |

|                 |                                                                                  |                                      |                                              |                  |                  |                 |         |

| Legend:         | 1.11                                                                             |                                      | 1.11                                         |                  |                  |                 |         |

| R = Readable    |                                                                                  | W = Writable                         |                                              | •                | nented bit, read |                 |         |

| -n = Value at I | POR                                                                              | '1' = Bit is set                     |                                              | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7-0         | 10110100 =<br>00000001 =<br>00000000 =<br>U2RXR<7:0><br>10110101 =<br>10110100 = | Input tied to RI<br>Input tied to RI | 2180<br>21<br>22 Receive (U2<br>2181<br>2180 | 2RX) to the Co   | rresponding RF   | Pn Pin bits     |         |

|                 |                                                                                  | Input tied to RI<br>Input tied to Va |                                              |                  |                  |                 |         |

|                 |                                                                                  |                                      |                                              |                  |                  |                 |         |

#### REGISTER 10-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| R/W-0           | R/W-0       | R/W-0                   | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

|-----------------|-------------|-------------------------|--------------|------------------|------------------|-----------------|----------|

| SYNCI1R7        | SYNCI1R6    | SYNCI1R5                | SYNCI1R4     | SYNCI1R3         | SYNCI1R2         | SYNCI1R1        | SYNCI1R0 |

| bit 15          |             |                         |              |                  |                  | -<br>-          | bit 8    |

|                 |             |                         |              |                  |                  |                 |          |

| U-0             | U-0         | U-0                     | U-0          | U-0              | U-0              | U-0             | U-0      |

| —               | —           | —                       | —            | —                | —                | —               | —        |

| bit 7           |             |                         |              |                  |                  |                 | bit 0    |

|                 |             |                         |              |                  |                  |                 |          |

| Legend:         |             |                         |              |                  |                  |                 |          |

| R = Readable    | bit         | W = Writable            | bit          | U = Unimpler     | nented bit, read | l as '0'        |          |

| -n = Value at P | OR          | '1' = Bit is set        |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown     |

|                 |             |                         |              |                  |                  |                 |          |

| bit 15-8        | SYNCI1R<7:0 | <b>0&gt;:</b> Assign PW | M Synchroniz | ation Input 1 to | the Correspon    | ding RPn Pin b  | oits     |

|                 | 10110101 =  | Input tied to RI        | P181         |                  |                  |                 |          |

|                 | 10110100 =  | Input tied to RI        | P180         |                  |                  |                 |          |

|                 | •           |                         |              |                  |                  |                 |          |

|                 | •           |                         |              |                  |                  |                 |          |

|                 | •           |                         |              |                  |                  |                 |          |

|                 | 0000001 =   | Input tied to RI        | P1           |                  |                  |                 |          |

|                 |             | Input tied to Va        |              |                  |                  |                 |          |

| bit 7-0         | Unimplemen  | ted: Read as '          | 0'           |                  |                  |                 |          |

|                 |             |                         |              |                  |                  |                 |          |

#### REGISTER 10-16: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

#### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = OCxRS compare event is used for synchronization

- 11110 = INT2 pin synchronizes or triggers OCx

- 11101 = INT1 pin synchronizes or triggers OCx

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers OCx

- 11010 = CMP3 module synchronizes or triggers OCx

- 11001 = CMP2 module synchronizes or triggers OCx

- 11000 = CMP1 module synchronizes or triggers OCx

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 input capture interrupt event synchronizes or triggers OCx

- 10010 = IC3 input capture interrupt event synchronizes or triggers OCx

- 10001 = IC2 input capture interrupt event synchronizes or triggers OCx

- 10000 = IC1 input capture interrupt event synchronizes or triggers OCx

- 01111 = Timer5 synchronizes or triggers OCx

- 01110 = Timer4 synchronizes or triggers OCx

- 01101 = Timer3 synchronizes or triggers OCx

- 01100 = Timer2 synchronizes or triggers OCx (default)

- 01011 = Timer1 synchronizes or triggers OCx

- 01010 = Reserved

- 01001 = Reserved

- 01000 = IC4 input capture event synchronizes or triggers OCx

- 00111 = IC3 input capture event synchronizes or triggers OCx

- 00110 = IC2 input capture event synchronizes or triggers OCx

- 00101 = IC1 input capture event synchronizes or triggers OCx

- 00100 = OC4 module synchronizes or triggers  $OCx^{(1,2)}$

- 00011 = OC3 module synchronizes or triggers  $OCx^{(1,2)}$

- 00010 = OC2 module synchronizes or triggers  $OCx^{(1,2)}$

- 00001 = OC1 module synchronizes or triggers  $OCx^{(1,2)}$

- 00000 = No sync or trigger source for OCx

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

#### REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5) (CONTINUED)

bit 1

BPLH: Blanking in PWMxL High Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is high

bit 0

BPLL: Blanking in PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL output is low

**Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

#### **REGISTER 15-25: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER (x = 1 to 5)**

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| —      | —   | —   | —   |       | LEB•  | <8:5> |       |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|----------|-------|-------|-----|-----|-------|

|       |       | LEB<4:0> |       |       | —   | —   | —     |

| bit 7 |       |          |       |       |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-3 **LEB<8:0>:** Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits The value is in 8.32 ns increments.

bit 2-0 Unimplemented: Read as '0'

#### REGISTER 19-5: ADCON3L: ADC CONTROL REGISTER 3 LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HSC | R/W-0   | R-0, HSC |

|---------|---------|---------|---------|---------|----------|---------|----------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY  | SHRSAMP | CNVRTCH  |

| bit 15  |         |         |         |         |          |         | bit 8    |

| R/W-0   | R/W-0, HSC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|---------|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG | SWCTRG     | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7   |            |           |           |           |           |           | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

#### bit 15-13 **REFSEL<2:0>:** ADC Reference Voltage Selection bits

| Value | VREFH | VREFL |

|-------|-------|-------|

| 000   | AVdd  | AVss  |

001-111 = Unimplemented: Do not use bit 12 SUSPEND: All ADC Cores Triggers Disable bit 1 = All new trigger events for all ADC cores are disabled 0 = All ADC cores can be triggered bit 11 SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit 1 = Common interrupt will be generated when ADC core triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set) 0 = Common interrupt is not generated for suspend ADC cores event bit 10 SUSPRDY: All ADC Cores Suspended Flag bit 1 = All ADC cores are suspended (SUSPEND bit = 1) and have no conversions in progress 0 = ADC cores have previous conversions in progress bit 9 SHRSAMP: Shared ADC Core Sampling Direct Control bit This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit. It connects an analog input, specified by the CNVCHSEL<5:0> bits, to the shared ADC core and allows extending the sampling time. This bit is not controlled by hardware and must be cleared before the conversion starts (setting CNVRTCH to '1'). 1 = Shared ADC core samples an analog input specified by the CNVCHSEL<5:0> bits 0 = Sampling is controlled by the shared ADC core hardware bit 8 **CNVRTCH:** Software Individual Channel Conversion Trigger bit 1 = Single trigger is generated for an analog input specified by the CNVCHSEL<5:0> bits; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Next individual channel conversion trigger can be generated bit 7 SWLCTRG: Software Level-Sensitive Common Trigger bit 1 = Triggers are continuously generated for all channels with the software, level-sensitive common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers 0 = No software, level-sensitive common triggers are generated SWCTRG: Software Common Trigger bit bit 6 1 = Single trigger is generated for all channels with the software, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Ready to generate the next software, common trigger CNVCHSEL <5:0>: Channel Number Selection for Software Individual Channel Conversion Trigger bits bit 5-0

These bits define a channel to be converted when the CNVRTCH bit is set.

### REGISTER 19-28: ADCAL0L: ADC CALIBRATION REGISTER 0 LOW

| R-0, HSC       | U-0                                                                                                                                                                                                                  | U-0                                                                                                  | U-0                                                                                                             | r-0                                                                                 | R/W-0            | R/W-0           | R/W-0            |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|-----------------|------------------|--|

| CAL1RDY        |                                                                                                                                                                                                                      | _                                                                                                    | _                                                                                                               | _                                                                                   | CAL1DIFF         | CAL1EN          | CAL1RUN          |  |

| bit 15         |                                                                                                                                                                                                                      |                                                                                                      |                                                                                                                 |                                                                                     | ·                |                 | bit 8            |  |

|                |                                                                                                                                                                                                                      |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

| R-0, HSC       | U-0                                                                                                                                                                                                                  | U-0                                                                                                  | U-0                                                                                                             | r-0                                                                                 | R/W-0            | R/W-0           | R/W-0            |  |

| CALORDY        | —                                                                                                                                                                                                                    |                                                                                                      | —                                                                                                               |                                                                                     | CAL0DIFF         | CAL0EN          | CALORUN          |  |

| bit 7          |                                                                                                                                                                                                                      |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 | bit C            |  |

| Legend:        |                                                                                                                                                                                                                      | r = Reserved                                                                                         | hit                                                                                                             |                                                                                     | nented bit, read | ac '0'          |                  |  |

| R = Readable   | o hit                                                                                                                                                                                                                | W = Writable                                                                                         |                                                                                                                 |                                                                                     | vare Settable/Cl |                 |                  |  |

| -n = Value at  |                                                                                                                                                                                                                      | '1' = Bit is set                                                                                     | on                                                                                                              | '0' = Bit is cle                                                                    |                  | x = Bit is unkr | nown             |  |

|                |                                                                                                                                                                                                                      |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

| bit 15         | CAL1RDY:                                                                                                                                                                                                             | Dedicated ADC                                                                                        | Core 1 Calibra                                                                                                  | tion Status Flag                                                                    | g bit            |                 |                  |  |

|                |                                                                                                                                                                                                                      | ed ADC Core 1 d                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

|                | 0 = Dedicate                                                                                                                                                                                                         | ed ADC Core 1 c                                                                                      | alibration is in                                                                                                | progress                                                                            |                  |                 |                  |  |

| bit 14-12      | Unimpleme                                                                                                                                                                                                            | nted: Read as 'o                                                                                     | )'                                                                                                              |                                                                                     |                  |                 |                  |  |

| bit 11         | Reserved:                                                                                                                                                                                                            | Must be written a                                                                                    | <b>is</b> '0'                                                                                                   |                                                                                     |                  |                 |                  |  |

| bit 10         | CAL1DIFF: Dedicated ADC Core 1 Differential-Mode Calibration bit                                                                                                                                                     |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

|                | 1 = Dedicated ADC Core 1 will be calibrated in Differential Input mode                                                                                                                                               |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

| <b>h</b> # 0   | <ul> <li>0 = Dedicated ADC Core 1 will be calibrated in Single-Ended Input mode</li> <li>CAL1EN: Dedicated ADC Core 1 Calibration Enable bit</li> </ul>                                                              |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

| bit 9          |                                                                                                                                                                                                                      | edicated ADC Core 1 c                                                                                |                                                                                                                 |                                                                                     |                  | l vPLINI) can b | a accessed by    |  |

|                | software                                                                                                                                                                                                             |                                                                                                      |                                                                                                                 | (CALXEDT, CA                                                                        |                  |                 | e accessed by    |  |

|                | 0 = Dedicat                                                                                                                                                                                                          | ed ADC Core 1                                                                                        | calibration bits                                                                                                | are disabled                                                                        |                  |                 |                  |  |

| bit 8          | CAL1RUN:                                                                                                                                                                                                             | Dedicated ADC                                                                                        | Core 1 Calibra                                                                                                  | ation Start bit                                                                     |                  |                 |                  |  |

|                |                                                                                                                                                                                                                      | oit is set by soft                                                                                   |                                                                                                                 | icated ADC Co                                                                       | ore 1 calibratio | n cycle is star | ted; this bit is |  |

|                |                                                                                                                                                                                                                      | tically cleared by<br>e can start the n                                                              |                                                                                                                 | avela                                                                               |                  |                 |                  |  |

| bit 7          |                                                                                                                                                                                                                      | Dedicated ADC (                                                                                      |                                                                                                                 | •                                                                                   | a hit            |                 |                  |  |

|                |                                                                                                                                                                                                                      | ed ADC Core 0 c                                                                                      |                                                                                                                 |                                                                                     | y bit            |                 |                  |  |

|                |                                                                                                                                                                                                                      | ed ADC Core 0 c                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

| bit 6-4        | Unimpleme                                                                                                                                                                                                            | nted: Read as 'o                                                                                     | )'                                                                                                              |                                                                                     |                  |                 |                  |  |

| bit 3          | Reserved:                                                                                                                                                                                                            | Must be written a                                                                                    | <b>s</b> '0'                                                                                                    |                                                                                     |                  |                 |                  |  |

| bit 2          | CAL0DIFF:                                                                                                                                                                                                            | Dedicated ADC                                                                                        | Core 0 Differe                                                                                                  | ntial-Mode Cal                                                                      | ibration bit     |                 |                  |  |

|                | CALODIFF: Dedicated ADC Core 0 Differential-Mode Calibration bit<br>1 = Dedicated ADC Core 0 will be calibrated in Differential Input mode<br>0 = Dedicated ADC Core 0 will be calibrated in Single-Ended Input mode |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

|                | 0 = Dedicate                                                                                                                                                                                                         |                                                                                                      |                                                                                                                 |                                                                                     |                  |                 |                  |  |

| bit 1          |                                                                                                                                                                                                                      |                                                                                                      | vill be calibrate                                                                                               | ed in Single-En                                                                     |                  |                 |                  |  |

| bit 1          | <b>CAL0EN:</b> D<br>1 = Dedicat                                                                                                                                                                                      | ed ADC Core 0 v<br>edicated ADC Core 0 c<br>red ADC Core 0 c                                         | vill be calibrate<br>ore 0 Calibrati                                                                            | ed in Single-En<br>on Enable bit                                                    | ded Input mode   |                 | e accessed by    |  |

| bit 1          | CALOEN: D<br>1 = Dedicat<br>software                                                                                                                                                                                 | ed ADC Core 0 v<br>edicated ADC Co<br>red ADC Core 0 c<br>e                                          | vill be calibrate<br>ore 0 Calibrati<br>calibration bits                                                        | ed in Single-En<br>on Enable bit<br>(CALxRDY, CA                                    | ded Input mode   |                 | e accessed b     |  |

|                | CALOEN: D<br>1 = Dedicat<br>software<br>0 = Dedicat                                                                                                                                                                  | ed ADC Core 0 w<br>edicated ADC Core 0 c<br>ed ADC Core 0 c<br>e<br>ed ADC Core 0 c                  | vill be calibrate<br>ore 0 Calibrati<br>calibration bits<br>calibration bits                                    | ed in Single-En<br>on Enable bit<br>(CALxRDY, CA<br>are disabled                    | ded Input mode   |                 | e accessed by    |  |

| bit 1<br>bit 0 | CALOEN: D<br>1 = Dedicat<br>software<br>0 = Dedicat<br>CALORUN:                                                                                                                                                      | ed ADC Core 0 v<br>edicated ADC Core 0 c<br>ed ADC Core 0 c<br>e<br>ed ADC Core 0 c<br>Dedicated ADC | vill be calibrate<br>ore 0 Calibrati<br>calibration bits<br>calibration bits<br>Core 0 Calibra                  | ed in Single-En<br>on Enable bit<br>(CALxRDY, CA<br>are disabled<br>ation Start bit | ded Input mode   | LxRUN) can b    |                  |  |

|                | CALOEN: D<br>1 = Dedicat<br>software<br>0 = Dedicat<br>CALORUN:<br>1 = If this b                                                                                                                                     | ed ADC Core 0 w<br>edicated ADC Core 0 c<br>ed ADC Core 0 c<br>e<br>ed ADC Core 0 c                  | vill be calibrate<br>ore 0 Calibrati<br>calibration bits<br>calibration bits<br>Core 0 Calibra<br>ware, the ded | ed in Single-En<br>on Enable bit<br>(CALxRDY, CA<br>are disabled<br>ation Start bit | ded Input mode   | LxRUN) can b    |                  |  |

## 23.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXGS50X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

## 23.1 Configuration Bits

In dsPIC33EPXXGS50X family devices, the Configuration Words are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the end of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 23-1 with detailed descriptions in Table 23-2. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration Shadow registers during device Resets.

For devices operating in Dual Partition modes, the BSEQx bits (FBTSEQ<11:0>) determine which panel is the Active Partition at start-up and the Configuration Words from that panel are loaded into the Configuration Shadow registers.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Words for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled. Program code executing out of configuration space will cause a device Reset.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words.

#### TABLE 26-25: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CH        | AC CHARACTERISTICS |                                       |                           |                                        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |               |       |                                                                            |  |  |

|--------------|--------------------|---------------------------------------|---------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|----------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic <sup>(1)</sup>         |                           | Min.                                   | Тур.                                                                                                                                                                                                 | Max.          | Units | Conditions                                                                 |  |  |

| TB10         | TtxH               | TxCK High<br>Time                     | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N   | _                                                                                                                                                                                                    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescale Value<br>(1, 8, 64, 256) |  |  |

| TB11         | TtxL               | TxCK Low<br>Time                      | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N   |                                                                                                                                                                                                      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescale Value<br>(1, 8, 64, 256) |  |  |

| TB15         | TtxP               | TxCK<br>Input<br>Period               | Synchronous<br>mode       | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _                                                                                                                                                                                                    | _             | ns    | N = Prescale Value<br>(1, 8, 64, 256)                                      |  |  |

| TB20         | TCKEXTMRL          | Delay from<br>Clock Edge<br>Increment | External TxCK<br>to Timer | 0.75 Tcy + 40                          |                                                                                                                                                                                                      | 1.75 Tcy + 40 | ns    |                                                                            |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

### TABLE 26-26: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                              |                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |               |       |                                       |

|--------------------|-----------|--------------------------------------------------------------|----------------------------|------------------------------------------------------|------|---------------|-------|---------------------------------------|

| Param<br>No.       | Symbol    | Charac                                                       | teristic <sup>(1)</sup>    | Min.                                                 | Тур. | Max.          | Units | Conditions                            |

| TC10               | TtxH      | TxCK High<br>Time                                            | Synchronous                | Tcy + 20                                             |      |               | ns    | Must also meet<br>Parameter TC15      |

| TC11               | TtxL      | TxCK Low<br>Time                                             | Synchronous                | Tcy + 20                                             | _    | —             | ns    | Must also meet<br>Parameter TC15      |

| TC15               | TtxP      | TxCK Input<br>Period                                         | Synchronous with Prescaler | 2 Tcy + 40                                           | _    | —             | ns    | N = Prescale Value<br>(1, 8, 64, 256) |

| TC20               | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                            | 0.75 Tcy + 40                                        |      | 1.75 Tcy + 40 | ns    |                                       |

Note 1: These parameters are characterized but not tested in manufacturing.

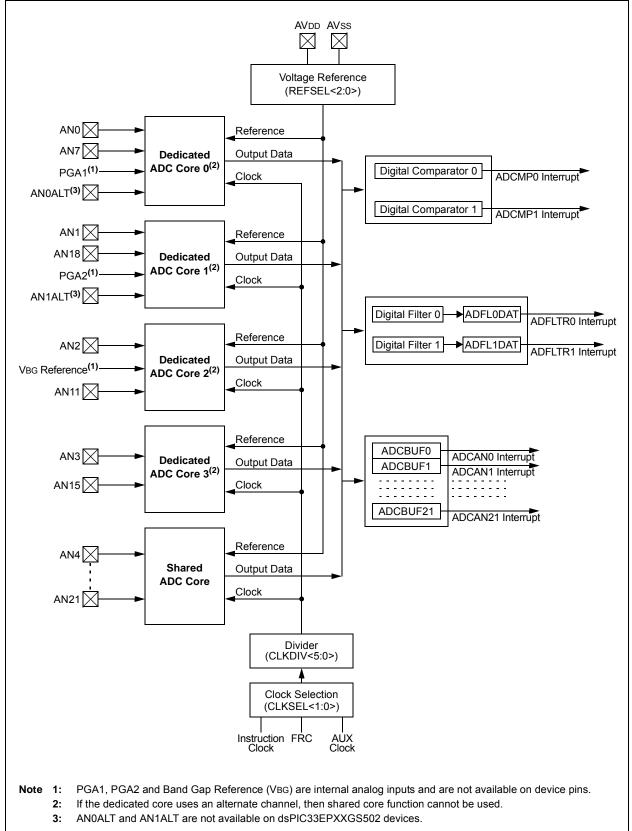

#### FIGURE 26-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

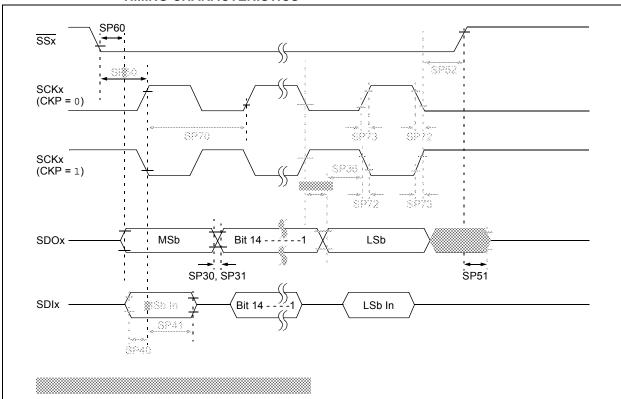

### FIGURE 26-23: UARTX MODULE I/O TIMING CHARACTERISTICS

### TABLE 26-41: UARTX MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                     |      |       |            |

|--------------------|---------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol  | Characteristic <sup>(1)</sup>                     | Min.                                                                                                                                   | Тур. <sup>(2)</sup> | Max. | Units | Conditions |

| UA10               | TUABAUD | UARTx Baud Time                                   | 66.67                                                                                                                                  | _                   | _    | ns    |            |

| UA11               | FBAUD   | UARTx Baud Frequency                              | _                                                                                                                                      | —                   | 15   | Mbps  |            |

| UA20               | TCWF    | Start Bit Pulse Width to Trigger<br>UARTx Wake-up | 500                                                                                                                                    | —                   |      | ns    |            |

Note 1: These parameters are characterized but not tested in manufacturing.