Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

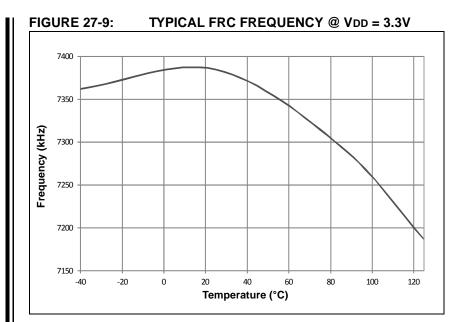

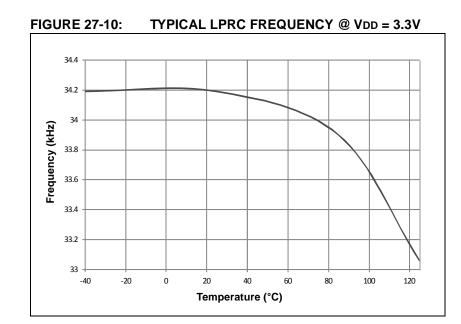

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

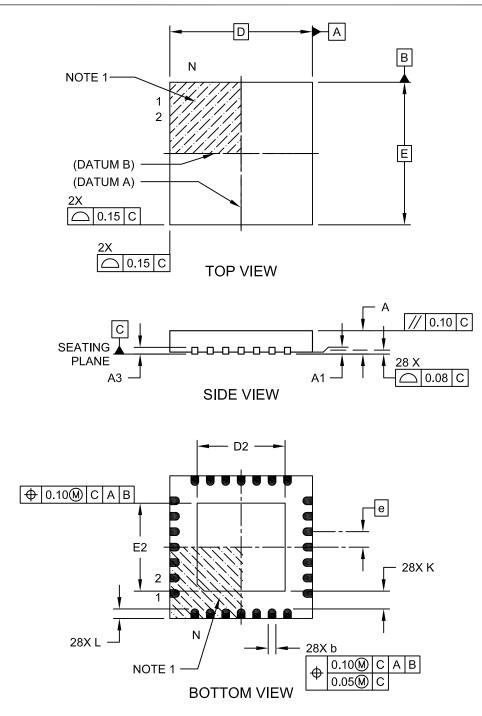

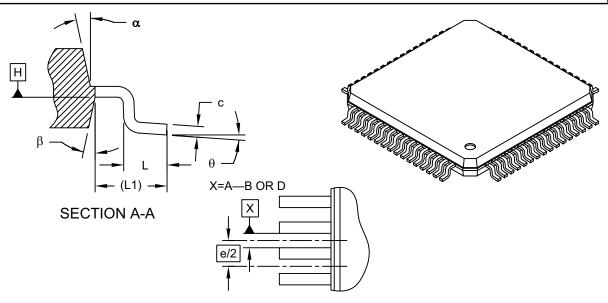

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502t-e-2n |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name <sup>(1)</sup>   | Pin<br>Type | Buffer<br>Type   | PPS        | Description                                                                                                                                                                                                    |

|---------------------------|-------------|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN21<br>AN0ALT-AN1ALT |             | Analog<br>Analog | No<br>No   | Analog input channels.<br>Alternate analog input channels.                                                                                                                                                     |

| CLKI                      | I           | ST/<br>CMOS      | No         | External clock source input. Always associated with OSC1 pin function Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |

| CLKO                      | 0           | —                | No         | Always associated with OSC2 pin function.                                                                                                                                                                      |

| OSC1                      | I           | ST/<br>CMOS      | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                |

| OSC2                      | I/O         | —                | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                       |

| REFCLKO                   | 0           | _                | Yes        | Reference clock output.                                                                                                                                                                                        |

| IC1-IC4                   | 1           | ST               | Yes        | Capture Inputs 1 through 4.                                                                                                                                                                                    |

| OCFA                      | 1           | ST               | Yes        | Compare Fault A input (for compare channels).                                                                                                                                                                  |

| OC1-OC4                   | Ó           | _                | Yes        | Compare Outputs 1 through 4.                                                                                                                                                                                   |

| INT0                      | 1           | ST               | No         | External Interrupt 0.                                                                                                                                                                                          |

| INT1                      | I           | ST               | Yes        | External Interrupt 1.                                                                                                                                                                                          |

| INT2                      | I           | ST               | Yes        | External Interrupt 2.                                                                                                                                                                                          |

| INT4                      | Ι           | ST               | No         | External Interrupt 4.                                                                                                                                                                                          |

| RA0-RA4                   | I/O         | ST               | No         | PORTA is a bidirectional I/O port.                                                                                                                                                                             |

| RB0-RB15                  | I/O         | ST               | No         | PORTB is a bidirectional I/O port.                                                                                                                                                                             |

| RC0-RC15                  | I/O         | ST               | No         | PORTC is a bidirectional I/O port.                                                                                                                                                                             |

| RD0-RD15                  | I/O         | ST               | No         | PORTD is a bidirectional I/O port.                                                                                                                                                                             |

| T1CK                      | 1           | ST               | Yes        | Timer1 external clock input.                                                                                                                                                                                   |

| T2CK                      |             | ST               | Yes        | Timer2 external clock input.                                                                                                                                                                                   |

| T3CK                      | İ           | ST               | Yes        | Timer3 external clock input.                                                                                                                                                                                   |

| T4CK                      | I           | ST               | No         | Timer4 external clock input.                                                                                                                                                                                   |

| T5CK                      | I.          | ST               | No         | Timer5 external clock input.                                                                                                                                                                                   |

| U1CTS                     | I           | ST               | Yes        | UART1 Clear-to-Send.                                                                                                                                                                                           |

| U1RTS                     | 0           | _                | Yes        | UART1 Request-to-Send.                                                                                                                                                                                         |

| U1RX                      | I           | ST               | Yes        | UART1 receive.                                                                                                                                                                                                 |

| U1TX                      | 0           | —                | Yes        | UART1 transmit.                                                                                                                                                                                                |

| BCLK1                     | 0           | ST               | Yes        | UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                                                                     |

| U2CTS                     | I           | ST               | Yes        |                                                                                                                                                                                                                |

| U2RTS                     | 0           | —                |            | UART2 Request-to-Send.                                                                                                                                                                                         |

| U2RX                      |             | ST               |            | UART2 receive.                                                                                                                                                                                                 |

| U2TX                      | 0           |                  | Yes        | UART2 transmit.                                                                                                                                                                                                |

| BCLK2                     | 0           | ST               | Yes        | UART2 IrDA baud clock output.                                                                                                                                                                                  |

| SCK1                      | 1/0         | ST               | Yes        | Synchronous serial clock input/output for SPI1.                                                                                                                                                                |

| SDI1                      |             | ST               | Yes        | SPI1 data in.                                                                                                                                                                                                  |

| SDO1<br>SS1               | 0<br>I/O    | ST               | Yes<br>Yes | SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                                                                                               |

| SCK2                      | I/O         | ST               | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                                                |

| SDI2                      | 1           | ST               | Yes        | SPI2 data in.                                                                                                                                                                                                  |

| SDO2                      | 0           |                  | Yes        | SPI2 data ini.<br>SPI2 data out.                                                                                                                                                                               |

| <u>SS2</u>                | 1/0         | ST               | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                 |

| Legend: CMOS = C          | _           |                  |            |                                                                                                                                                                                                                |

| ST = Schm<br>PPS = Peri   | itt Trigg   | er input v       | vith CN    |                                                                                                                                                                                                                |

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are dedicated on 64-pin devices.

#### 3.7 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R/W-0                | R/W-0                | R/W-0                                                      | R/W-0             | R/C-0            | R/C-0            | R-0             | R/W-0 |

|----------------------|----------------------|------------------------------------------------------------|-------------------|------------------|------------------|-----------------|-------|

| OA                   | OB                   | SA <sup>(3)</sup>                                          | SB <sup>(3)</sup> | OAB              | SAB              | DA              | DC    |

| bit 15               |                      |                                                            |                   |                  |                  |                 | bit 8 |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup>                                       | R-0               | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| IPL2 <sup>(1)</sup>  | IPL1 <sup>(1)</sup>  | IPL0 <sup>(1)</sup>                                        | RA                | N                | OV               | Z               | C     |

| bit 7                |                      |                                                            |                   |                  |                  | _               | bit 0 |

|                      |                      |                                                            |                   |                  |                  |                 |       |

| Legend:              |                      | C = Clearable                                              | bit               |                  |                  |                 |       |

| R = Readable         | e bit                | W = Writable                                               | bit               | U = Unimplen     | nented bit, read | d as '0'        |       |

| -n = Value at        | POR                  | '1'= Bit is set                                            |                   | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 15               | 1 = Accumula         | ator A Overflow<br>ator A has overf<br>ator A has not o    | lowed             |                  |                  |                 |       |

| bit 14               | 1 = Accumula         | ator B Overflow<br>ator B has overf<br>ator B has not o    | lowed             |                  |                  |                 |       |

| bit 13               | 1 = Accumula         | ator A Saturatio<br>ator A is saturat<br>ator A is not sat | ed or has bee     |                  | some time        |                 |       |

- 1 = Accumulator B is saturated or has been saturated at some time

- 0 = Accumulator B is not saturated

- bit 11 OAB: OA || OB Combined Accumulator Overflow Status bit

- 1 = Accumulators A or B have overflowed

- 0 = Neither Accumulators A or B have overflowed

- bit 10 SAB: SA || SB Combined Accumulator 'Sticky' Status bit

- 1 = Accumulators A or B are saturated or have been saturated at some time

- 0 = Neither Accumulator A or B are saturated

- bit 9 DA: DO Loop Active bit

- 1 = DO loop in progress

- 0 = DO loop not in progress

- bit 8 DC: MCU ALU Half Carry/Borrow bit

- 1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- 0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **2:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

#### TABLE 4-28: PORTA REGISTER MAP FOR dsPIC33EPXXGS502 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|------------|-------|------------|-----------|-------|---------------|

| TRISA       | 0E00  |        | _      | _      | _      |        |        | _     | _     |       |       |       |            |       | RISA<4:0>  | •         |       | 001F          |

| PORTA       | 0E02  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     |            |       | RA<4:0>    |           |       | 0000          |

| LATA        | 0E04  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     | LATA<4:0>  |       |            | 0000      |       |               |

| ODCA        | 0E06  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     |            | (     | DDCA<4:0>  |           |       | 0000          |

| CNENA       | 0E08  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     |            | (     | CNIEA<4:0> | •         |       | 0000          |

| CNPUA       | 0E0A  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     | CNPUA<4:0> |       |            | 0000      |       |               |

| CNPDA       | 0E0C  | —      | —      | —      |        | _      |        | _     | —     |       |       | _     | CNPDA<4:0> |       |            | 0000      |       |               |

| ANSELA      | 0E0E  | _      | _      | —      | -      | _      | _      | _     | -     | _     | _     |       | _          | _     | /          | ANSA<2:0> |       | 0007          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-29: PORTB REGISTER MAP FOR dsPIC33EPXXGS502 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14                  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|-------------------------|--------|--------|--------|--------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E10  |        |                         |        |        |        |        |       | TRISB<15 | 5:0>  |       |       |       |       |       |       |       | FFFF          |

| PORTB       | 0E12  |        | RB<15:0>                |        |        |        |        |       |          |       |       |       | xxxx  |       |       |       |       |               |

| LATB        | 0E14  |        | LATB<15:0>              |        |        |        |        |       |          |       |       |       | xxxx  |       |       |       |       |               |

| ODCB        | 0E16  |        | ODCB<15:0>              |        |        |        |        |       |          |       |       | 0000  |       |       |       |       |       |               |

| CNENB       | 0E18  |        |                         |        |        |        |        |       | CNIEB<18 | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1A  |        |                         |        |        |        |        |       | CNPUB<1  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDB       | 0E1C  |        | CNPDB<15:0>             |        |        |        |        |       |          |       |       | 0000  |       |       |       |       |       |               |

| ANSELB      | 0E1E  | _      | ANSB<10:9>ANSB<7:0> (0) |        |        |        |        |       |          |       | 06FF  |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 10-14: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0         | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

|---------------|------------------------------------|------------------------------------------------------------------------------|--------------|------------------|------------------|-----------------|----------|

| SCK2INR7      | SCK2INR6                           | SCK2INR5                                                                     | SCK2INR4     | SCK2INR3         | SCK2INR2         | SCK2INR1        | SCK2INR0 |

| bit 15        |                                    |                                                                              |              |                  |                  |                 | bit 8    |

| R/W-0         | R/W-0                              | R/W-0                                                                        | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0    |

| SDI2R7        | SDI2R6                             | SDI2R5                                                                       | SDI2R4       | SDI2R3           | SDI2R2           | SDI2R1          | SDI2R0   |

| bit 7         |                                    |                                                                              |              |                  |                  |                 | bit (    |

| Legend:       |                                    |                                                                              |              |                  |                  |                 |          |

| R = Readable  | bit                                | W = Writable                                                                 | bit          | U = Unimpler     | nented bit, read | l as '0'        |          |

| -n = Value at | POR                                | '1' = Bit is set                                                             |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown     |

|               | 10110100 =<br>•<br>•<br>00000001 = | Input tied to Rf<br>Input tied to Rf<br>Input tied to Rf<br>Input tied to Vs | 2180<br>21   |                  |                  |                 |          |

| bit 7-0       | 10110101 =                         | Input tied to RF<br>Input tied to RF                                         | 2181<br>2180 | 12) to the Corre | esponding RPn    | Pin bits        |          |

#### REGISTER 10-28: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| —         —         RP49R5         RP49R4         RP49R3         RP49R2         RP49R1         RP49R1           bit 15         U-0         U-0         R/W-0         R/W-0 <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |            |                  |        |                  |                  |                 |        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|------------------|--------|------------------|------------------|-----------------|--------|--|

| bit 15U-0U-0R/W-0R/W-0R/W-0R/W-0R/W-0———RP48R5RP48R4RP48R3RP48R2RP48R1RP4bit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15-14Unimplemented: Read as '0'<br>bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits<br>(see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0             | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

| U-0U-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —               | —          | RP49R5           | RP49R4 | RP49R3           | RP49R2           | RP49R1          | RP49R0 |  |

| —       —       RP48R5       RP48R4       RP48R3       RP48R2       RP48R1       RP4         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15          |            |                  |        |                  |                  |                 | bit 8  |  |

| —       —       RP48R5       RP48R4       RP48R3       RP48R2       RP48R1       RP4         bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |            |                  |        |                  |                  |                 |        |  |

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0             | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'         bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —               | —          | RP48R5           | RP48R4 | RP48R3           | RP48R2           | RP48R1          | RP48R0 |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'         bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 7           |            | •                | -      |                  |                  |                 | bit 0  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'         bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |            |                  |        |                  |                  |                 |        |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       Image: Second se | Legend:         |            |                  |        |                  |                  |                 |        |  |

| bit 15-14Unimplemented: Read as '0'bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits<br>(see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R = Readable    | bit        | W = Writable     | bit    | U = Unimpler     | nented bit, read | l as '0'        |        |  |

| bit 13-8 <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n = Value at F | POR        | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |

| bit 13-8 <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |            |                  |        |                  |                  |                 |        |  |

| (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15-14       | Unimplemen | ted: Read as '   | 0'     |                  |                  |                 |        |  |

| bit 7-6 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |            |                  |        |                  |                  |                 |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7-6         | Unimplemen | ted: Read as '   | 0'     |                  |                  |                 |        |  |

bit 5-0 **RP48R<5:0>:** Peripheral Output Function is Assigned to RP48 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-29: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0             | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|------------|------------------|--------|------------------|------------------|-----------------|--------|

| —               | —          | RP51R5           | RP51R4 | RP51R3           | RP51R2           | RP51R1          | RP51R0 |

| bit 15          |            |                  |        |                  |                  | -<br>-          | bit 8  |

|                 |            |                  |        |                  |                  |                 |        |

| U-0             | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —               | —          | RP50R5           | RP50R4 | RP50R3           | RP50R2           | RP50R1          | RP50R0 |

| bit 7           | •          |                  |        | ·                |                  |                 | bit 0  |

|                 |            |                  |        |                  |                  |                 |        |

| Legend:         |            |                  |        |                  |                  |                 |        |

| R = Readable    | bit        | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at P | OR         | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|                 |            |                  |        |                  |                  |                 |        |

| bit 15-14       | Unimplemen | ted: Read as '   | )'     |                  |                  |                 |        |

bit 13-8 **RP51R<5:0>:** Peripheral Output Function is Assigned to RP51 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP50R<5:0>:** Peripheral Output Function is Assigned to RP50 Output Pin bits (see Table 10-2 for peripheral function numbers)

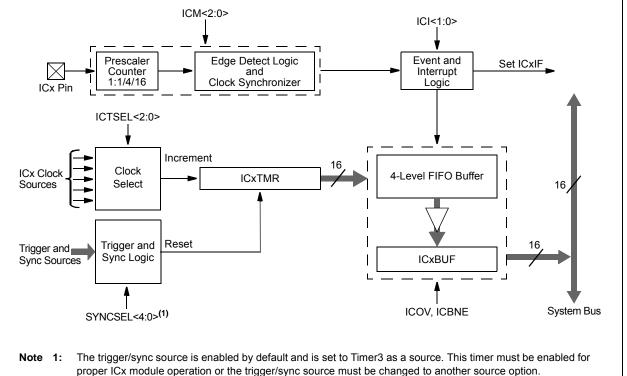

### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurements. The dsPIC33EPXXGS50X family devices support four input capture channels.

Key features of the input capture module include:

Hardware-Configurable for 32-Bit Operation in All modes by Cascading Two Adjacent Modules

- Synchronous and Trigger modes of Output Compare Operation, with up to 21 User-Selectable Trigger/Sync Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Six Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

### 13.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 13.1.1 KEY RESOURCES

- "Input Capture" (DS70000352) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### FIGURE 13-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

#### REGISTER 13-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

bit 4-0 S

- **SYNCSEL<4:0>:** Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup> 11111 = No sync or trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- 11001 = CMP2 module synchronizes or triggers  $ICx^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module interrupt synchronizes or triggers ICx

- 10010 = IC3 module interrupt synchronizes or triggers ICx

- 10001 = IC2 module interrupt synchronizes or triggers ICx

- 10000 = IC1 module interrupt synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = Reserved

- 01001 = Reserved

- 01000 = IC4 module synchronizes or triggers ICx

- 00111 = IC3 module synchronizes or triggers ICx

- 00110 = IC2 module synchronizes or triggers ICx

- 00101 = IC1 module synchronizes or triggers ICx

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No sync or trigger source for ICx

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

#### REGISTER 15-12: PWMCONx: PWMx CONTROL REGISTER (x = 1 to 5) (CONTINUED)

- bit 7-6 DTC<1:0>: Dead-Time Control bits 11 = Reserved 10 = Dead-time function is disabled 01 = Negative dead time is actively applied for Complementary Output mode 00 = Positive dead time is actively applied for all Output modes bit 5-4 Unimplemented: Read as '0' bit 3 MTBS: Master Time Base Select bit 1 = PWMx generator uses the secondary master time base for synchronization and the clock source for the PWMx generation logic (if secondary time base is available) 0 = PWMx generator uses the primary master time base for synchronization and the clock source for the PWMx generation logic CAM: Center-Aligned Mode Enable bit<sup>(2,3,4)</sup> bit 2 1 = Center-Aligned mode is enabled 0 = Edge-Aligned mode is enabled XPRES: External PWMx Reset Control bit<sup>(5)</sup> bit 1 1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base mode 0 = External pins do not affect the PWMx time base bit 0 **IUE:** Immediate Update Enable bit 1 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are immediate 0 = Updates to the active Duty Cycle, Phase Offset, Dead-Time and local Time Base Period registers are synchronized to the local PWMx time base Note 1: Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller. 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored. 3: These bits should not be changed after the PWMx is enabled by setting PTEN = 1 (PTCON<15>). 4: Center-Aligned mode ignores the Least Significant 3 bits of the Duty Cycle, Phase and Dead-Time registers. The highest Center-Aligned mode resolution available is 8.32 ns with the clock prescaler set to

- 5: Configure CLMOD = 0 (FCLCONx<8>) and ITB = 1 (PWMCONx<9>) to operate in External Period Reset mode.

the fastest clock.

#### REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5) (CONTINUED)

bit 1

BPLH: Blanking in PWMxL High Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is high

bit 0

BPLL: Blanking in PWMxL Low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL low Enable bit

1 = State blanking (of current-limit and/or Fault input signals) when the PWMxL output is low

0 = No blanking when the PWMxL output is low

**Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

#### **REGISTER 15-25: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER (x = 1 to 5)**

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| —      | —   | —   | —   |       | LEB•  | <8:5> |       |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|----------|-------|-------|-----|-----|-------|

|       |       | LEB<4:0> |       |       | —   | —   | —     |

| bit 7 |       |          |       |       |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-3 **LEB<8:0>:** Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits The value is in 8.32 ns increments.

bit 2-0 Unimplemented: Read as '0'

#### R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 **HRPDIS HRDDIS** \_\_\_\_ BLANKSEL3 BLANKSEL2 BLANKSEL1 **BLANKSEL0** \_ bit 15 bit 8 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CHOPSEL3 CHOPSEL2 CHOPSEL1 CHOPSEL0 CHOPHEN CHOPLEN bit 7 bit 0 Leaend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 HRPDIS: High-Resolution PWMx Period Disable bit 1 = High-resolution PWMx period is disabled to reduce power consumption 0 = High-resolution PWMx period is enabled bit 14 HRDDIS: High-Resolution PWMx Duty Cycle Disable bit 1 = High-resolution PWMx duty cycle is disabled to reduce power consumption 0 = High-resolution PWMx duty cycle is enabled bit 13-12 Unimplemented: Read as '0' bit 11-8 BLANKSEL<3:0>: PWMx State Blank Source Select bits The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register). 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM5H is selected as the state blank source 0100 = PWM4H is selected as the state blank source 0011 = PWM3H is selected as the state blank source 0010 = PWM2H is selected as the state blank source 0001 = PWM1H is selected as the state blank source 0000 = No state blanking bit 7-6 Unimplemented: Read as '0' bit 5-2 CHOPSEL<3:0>: PWMx Chop Clock Source Select bits The selected signal will enable and disable (chop) the selected PWMx outputs. 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM5H is selected as the chop clock source 0100 = PWM4H is selected as the chop clock source 0011 = PWM3H is selected as the chop clock source 0010 = PWM2H is selected as the chop clock source 0001 = PWM1H is selected as the chop clock source 0000 = Chop clock generator is selected as the chop clock source bit 1 **CHOPHEN:** PWMxH Output Chopping Enable bit 1 = PWMxH chopping function is enabled 0 = PWMxH chopping function is disabled bit 0 CHOPLEN: PWMxL Output Chopping Enable bit 1 = PWMxL chopping function is enabled 0 = PWMxL chopping function is disabled

**REGISTER 15-26:** AUXCONx: PWMx AUXILIARY CONTROL REGISTER (x = 1 to 5)

#### REGISTER 19-5: ADCON3L: ADC CONTROL REGISTER 3 LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HSC | R/W-0   | R-0, HSC |

|---------|---------|---------|---------|---------|----------|---------|----------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY  | SHRSAMP | CNVRTCH  |

| bit 15  |         |         |         |         |          |         | bit 8    |

| R/W-0       | R/W-0, HSC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|-------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG     | SWCTRG     | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7 bit 0 |            |           |           |           |           |           |           |

| Legend:           | U = Unimplemented bit, read as '0'                     |                      |                    |  |  |

|-------------------|--------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit HSC = Hardware Settable/Clearable bit |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared | x = Bit is unknown |  |  |

#### bit 15-13 **REFSEL<2:0>:** ADC Reference Voltage Selection bits

| Value | VREFH | VREFL |

|-------|-------|-------|

| 000   | AVdd  | AVss  |

001-111 = Unimplemented: Do not use bit 12 SUSPEND: All ADC Cores Triggers Disable bit 1 = All new trigger events for all ADC cores are disabled 0 = All ADC cores can be triggered bit 11 SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit 1 = Common interrupt will be generated when ADC core triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set) 0 = Common interrupt is not generated for suspend ADC cores event bit 10 SUSPRDY: All ADC Cores Suspended Flag bit 1 = All ADC cores are suspended (SUSPEND bit = 1) and have no conversions in progress 0 = ADC cores have previous conversions in progress bit 9 SHRSAMP: Shared ADC Core Sampling Direct Control bit This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit. It connects an analog input, specified by the CNVCHSEL<5:0> bits, to the shared ADC core and allows extending the sampling time. This bit is not controlled by hardware and must be cleared before the conversion starts (setting CNVRTCH to '1'). 1 = Shared ADC core samples an analog input specified by the CNVCHSEL<5:0> bits 0 = Sampling is controlled by the shared ADC core hardware bit 8 **CNVRTCH:** Software Individual Channel Conversion Trigger bit 1 = Single trigger is generated for an analog input specified by the CNVCHSEL<5:0> bits; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Next individual channel conversion trigger can be generated bit 7 SWLCTRG: Software Level-Sensitive Common Trigger bit 1 = Triggers are continuously generated for all channels with the software, level-sensitive common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers 0 = No software, level-sensitive common triggers are generated SWCTRG: Software Common Trigger bit bit 6 1 = Single trigger is generated for all channels with the software, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers; when the bit is set, it is automatically cleared by hardware on the next instruction cycle 0 = Ready to generate the next software, common trigger CNVCHSEL <5:0>: Channel Number Selection for Software Individual Channel Conversion Trigger bits bit 5-0

These bits define a channel to be converted when the CNVRTCH bit is set.

#### REGISTER 19-15: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EIEN<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15     |       |       |       |       |       |       | bit 8 |  |  |

|            |       |       |       |       |       |       |       |  |  |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|            |       |       | EIEN  | <7:0> |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |  |

|            |       |       |       |       |       |       |       |  |  |

| Legend:    |       |       |       |       |       |       |       |  |  |

| Logona.           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 15-0 EIEN<15:0>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

#### REGISTER 19-16: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| —     | —   | EIEN<21:16> |       |       |       |       |       |

| bit 7 |     |             |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 EIEN<21:16>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

### REGISTER 19-26: ADTRIGXL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

- 11111 = ADTRG31

- 11110 = Reserved

- 11101 = Reserved

- 11100 = PWM Generator 5 current-limit trigger

- 11011 = PWM Generator 4 current-limit trigger