Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502t-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

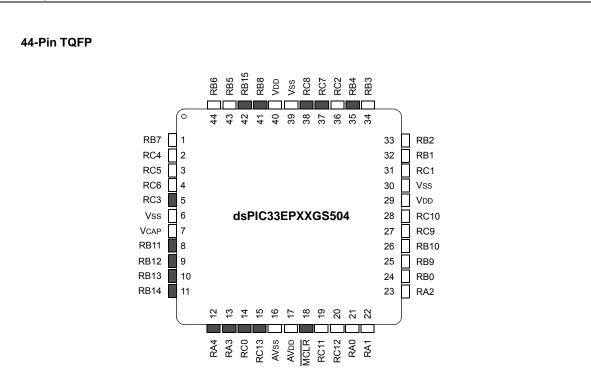

#### **Pin Diagrams (Continued)**

| Pin | Pin Function                      | Pin | Pin Function                              |

|-----|-----------------------------------|-----|-------------------------------------------|

| 1   | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7 | 23  | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         |

| 2   | AN1ALT/ <b>RP52</b> /RC4          | 24  | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           |

| 3   | AN0ALT/RP53/RC5                   | 25  | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            |

| 4   | AN17/ <b>RP54</b> /RC6            | 26  | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           |

| 5   | RP51/RC3                          | 27  | AN11/PGA1N3/ <b>RP57</b> /RC9             |

| 6   | Vss                               | 28  | AN10/PGA1P4/EXTREF2/RP58/RC10             |

| 7   | VCAP                              | 29  | VDD                                       |

| 8   | TMS/PWM3H/RP43/RB11               | 30  | Vss                                       |

| 9   | TCK/PWM3L/ <b>RP44</b> /RB12      | 31  | AN8/PGA2P4/CMP4C/RP49/RC1                 |

| 10  | PWM2H/ <b>RP45</b> /RB13          | 32  | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  |

| 11  | PWM2L/ <b>RP46</b> /RB14          | 33  | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 |

| 12  | PWM1H/RA4                         | 34  | PGED2/AN18/DACOUT1/INT0/RP35/RB3          |

| 13  | PWM1L/RA3                         | 35  | PGEC2/ADTRG31/ <b>RP36</b> /RB4           |

| 14  | FLT12/ <b>RP48</b> /RC0           | 36  | AN9/CMP4D/EXTREF1/RP50 /RC2               |

| 15  | FLT11/ <b>RP61</b> /RC13          | 37  | ASDA1/ <b>RP55</b> /RC7                   |

| 16  | AVss                              | 38  | ASCL1/RP56/RC8                            |

| 17  | AVDD                              | 39  | Vss                                       |

| 18  | MCLR                              | 40  | VDD                                       |

| 19  | AN12/ISRC1/ <b>RP59</b> /RC11     | 41  | PGED3/SDA2/FLT31/RP40/RB8                 |

| 20  | AN14/PGA2N3/ <b>RP60</b> /RC12    | 42  | PGEC3/SCL2/RP47/RB15                      |

| 21  | AN0/PGA1P1/CMP1A/RA0              | 43  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         |

| 22  | AN1/PGA1P2/PGA2P1/CMP1B/RA1       | 44  | PGED1/TDI/AN20/SCL1/RP38/RB6              |

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin I   | Name <sup>(1)</sup>      | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                   |  |  |  |  |  |

|---------|--------------------------|-------------|----------------|-----|-------------------------------------------------------------------------------|--|--|--|--|--|

| MCLR    |                          | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.    |  |  |  |  |  |

| AVDD    |                          | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all imes.   |  |  |  |  |  |

| AVss    |                          | Р           | Р              | No  | Ground reference for analog modules. This pin must be connected at all times. |  |  |  |  |  |

| Vdd     |                          | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                            |  |  |  |  |  |

| VCAP    |                          | Р           | _              | No  | CPU logic filter capacitor connection.                                        |  |  |  |  |  |

| Vss     |                          | Р           |                | No  | Ground reference for logic and I/O pins.                                      |  |  |  |  |  |

| Legend: | CMOS = CM<br>ST = Schmit |             |                |     |                                                                               |  |  |  |  |  |

PPS = Peripheral Pin Select

TTL = TTL input buffer

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are dedicated on 64-pin devices.

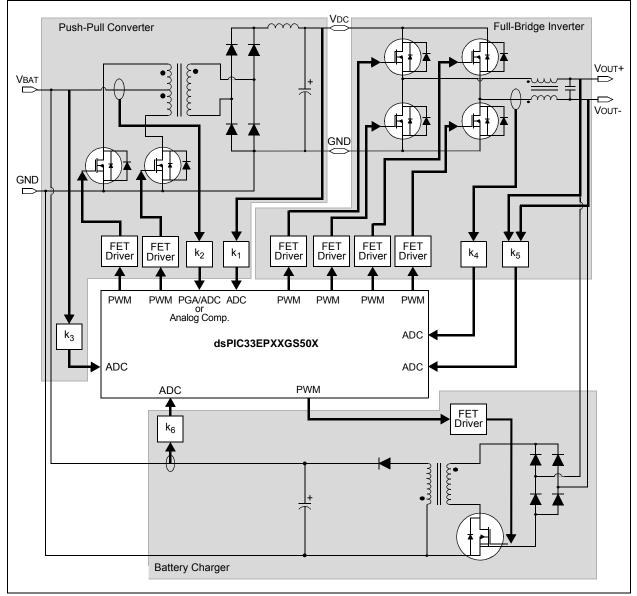

#### FIGURE 2-6: OFF-LINE UPS

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES (DUAL PARTITION) 0x000000 GOTO Instruction 0x000002 Reset Address 0x000004 Interrupt Vector Table 0x0001FE 0x000200 Active Program Flash Memory (10,944 instructions) **Active Partition** 0x00577E 0x005780 **Device Configuration** 0x0057FE 0x005800 User Memory Space Unimplemented (Read '0's) 0x3FFFFE 0x400000 GOTO Instruction 0x400002 Reset Address 0x400004 Interrupt Vector Table 0x4001FE 0x400200 **Inactive Partition** Inactive Program Flash Memory (10,944 instructions) 0x40577E 0x405780 **Device Configuration** 0x4057FE 0x405800 Unimplemented (Read '0's) 0x7FFFFE 0x800000 Reserved 0x800E46 0x800E48 Calibration Data 0x800E78 0x800E7A Reserved 0x800EFE Configuration Memory Space 0x800F00 UDID 0x800F08 0x800F0A Reserved 0x800F7E 0x800F80 User OTP Memory 0x800FFC 0x801000 Reserved 0xF9FFFE 0xFA0000 Write Latches 0xFA0002 0xFA0004 Reserved **0xFEFFFE** 0xFF0000 DEVID 0xFF0002 0xFF0004 Reserved 0xFFFFFE Note: Memory areas are not shown to scale.

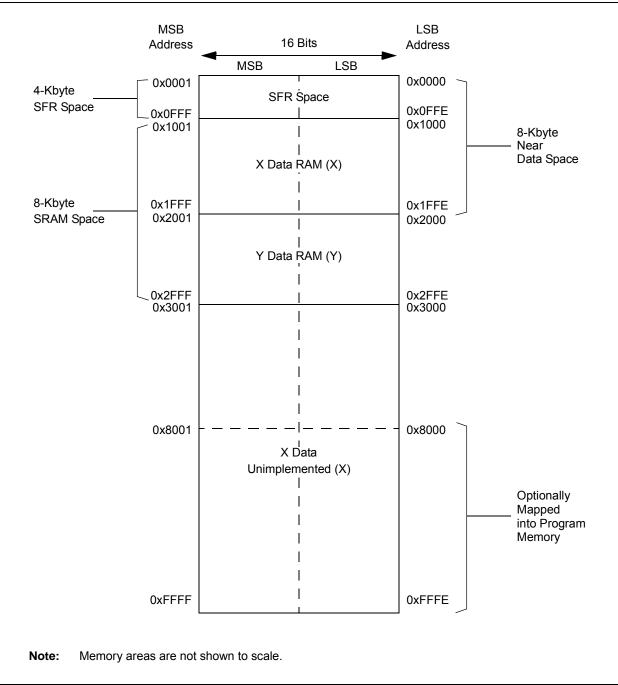

#### FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

#### TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                   | Bit 14                   | Bit 13                   | Bit 12                   | Bit 11                   | Bit 10                   | Bit 9                    | Bit 8                   | Bit 7                   | Bit 6    | Bit 5    | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0                    | All<br>Resets |

|-------------|-------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------------------------|-------------------------|----------|----------|-----------|-----------|-----------|-----------|--------------------------|---------------|

| IFS0        | 0800  | NVMIF                    | -                        | ADCIF                    | U1TXIF                   | U1RXIF                   | SPI1IF                   | SPI1EIF                  | T3IF                    | T2IF                    | OC2IF    | IC2IF    | -         | T1IF      | OC1IF     | IC1IF     | INTOIF                   | 0000          |

| IFS1        | 0802  | U2TXIF                   | U2RXIF                   | INT2IF                   | T5IF                     | T4IF                     | OC4IF                    | OC3IF                    | -                       | _                       | -        | -        | INT1IF    | CNIF      | AC1IF     | MI2C1IF   | SI2C1IF                  | 0000          |

| IFS2        | 0804  | _                        | -                        | _                        | _                        | _                        | _                        | —                        | -                       | _                       | IC4IF    | IC3IF    | -         | _         | _         | SPI2IF    | SPI2EIF                  | 0000          |

| IFS3        | 0806  | _                        | _                        | _                        | _                        | _                        | _                        | PSEMIF                   | _                       | _                       | INT4IF   | _        | _         | _         | MI2C2IF   | SI2C2IF   | _                        | 0000          |

| IFS4        | 0808  | -                        | -                        | -                        | -                        | -                        | -                        | PSESIF                   | -                       | -                       | -        | -        | -         | -         | U2EIF     | U1EIF     | -                        | 0000          |

| IFS5        | 080A  | PWM2IF                   | PWM1IF                   | _                        | _                        | _                        | _                        | _                        | _                       |                         | _        | _        | _         | _         | -         | -         | -                        | 0000          |

| IFS6        | 080C  | ADCAN1IF                 | ADCAN0IF                 | —                        | _                        | _                        | _                        | AC4IF                    | AC3IF                   | AC2IF                   |          | _        | _         | _         | PWM5IF    | PWM4IF    | PWM3IF                   | 0000          |

| IFS7        | 080E  | -                        | -                        | -                        | -                        | -                        | -                        | -                        | -                       | -                       | -        | ADCAN7IF | ADCAN6IF  | ADCAN5IF  | ADCAN4IF  | ADCAN3IF  | ADCAN2IF                 | 0000          |

| IFS8        | 0810  | JTAGIF                   | ICDIF                    | -                        | -                        | -                        | -                        | -                        | -                       | -                       | -        | -        | -         | -         | -         | -         | -                        | 0000          |

| IFS9        | 0812  | ADCAN16IF <sup>(1)</sup> | ADCAN15IF <sup>(1)</sup> | ADCAN14IF <sup>(2)</sup> | ADCAN13IF(1)             | ADCAN12IF <sup>(2)</sup> | ADCAN11IF <sup>(2)</sup> | ADCAN10IF <sup>(2)</sup> | ADCAN9IF <sup>(2)</sup> | ADCAN8IF <sup>(2)</sup> | _        | _        | _         | _         | -         | -         | -                        | 0000          |

| IFS10       | 0814  | -                        | I2C2BCIF                 | I2C1BCIF                 | -                        | -                        | _                        | -                        | -                       | _                       | -        | -        | ADCAN21IF | ADCAN20IF | ADCAN19IF | ADCAN18IF | ADCAN17IF <sup>(2)</sup> | 0000          |

| IFS11       | 0816  | _                        | -                        | _                        | _                        | _                        | _                        | _                        | -                       | _                       | _        | _        | ADFLTR1IF | ADFLTR0IF | ADCMP1IF  | ADCMP0IF  | -                        | 0000          |

| IEC0        | 0820  | NVMIE                    | -                        | ADCIE                    | U1TXIE                   | U1RXIE                   | SPI1IE                   | SPI1EIE                  | T3IE                    | T2IE                    | OC2IE    | IC2IE    | -         | T1IE      | OC1IE     | IC1IE     | INTOIE                   | 0000          |

| IEC1        | 0822  | U2TXIE                   | U2RXIE                   | INT2IE                   | T5IE                     | T4IE                     | OC4IE                    | OC3IE                    | -                       | _                       | _        | -        | INT1IE    | CNIE      | AC1IF     | MI2C1IE   | SI2C1IE                  | 0000          |

| IEC2        | 0824  | _                        | _                        | _                        | _                        | _                        | _                        | _                        | _                       | _                       | IC4IE    | IC3IE    | -         | _         | _         | SPI2IE    | SPI2EIE                  | 0000          |

| IEC3        | 0826  | _                        | _                        | _                        | _                        | _                        | _                        | PSEMIE                   | _                       | _                       | INT4IE   | _        | -         | _         | MI2C2IE   | SI2C2IE   | -                        | 0000          |

| IEC4        | 0828  | _                        | -                        | _                        | -                        | _                        | _                        | PSESIE                   | -                       | _                       | _        | _        | -         | -         | U2EIE     | U1EIE     | -                        | 0000          |

| IEC5        | 082A  | PWM2IE                   | PWM1IE                   | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC6        | 082C  | ADCAN1IE                 | ADCAN0IE                 | _                        | _                        | _                        | _                        | AC4IE                    | AC3IE                   | AC2IE                   | _        | _        | -         | _         | PWM5IE    | PWM4IE    | PWM3IE                   | 0000          |

| IEC7        | 082E  | _                        | _                        | _                        | -                        | _                        | _                        | _                        | -                       | _                       | _        | ADCAN7IE | ADCAN6IE  | ADCAN5IE  | ADCAN4IE  | ADCAN3IE  | ADCAN2IE                 | 0000          |

| IEC8        | 0830  | JTAGIE                   | ICDIE                    | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC9        | 0832  | ADCAN16IE <sup>(1)</sup> | ADCAN15IE <sup>(1)</sup> | ADCAN14IE <sup>(2)</sup> | ADCAN13IE <sup>(1)</sup> | ADCAN12IE <sup>(2)</sup> | ADCAN11IE <sup>(2)</sup> | ADCAN10IE <sup>(2)</sup> | ADCAN9IE <sup>(2)</sup> | ADCAN8IE <sup>(2)</sup> | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC10       | 0834  | _                        | I2C2BCIE                 | I2C1BCIE                 | -                        | _                        | _                        | _                        | -                       | _                       | _        | _        | ADCAN21IE | ADCAN20IE | ADCAN19IE | ADCAN18IE | ADCAN17IE <sup>(2)</sup> | 0000          |

| IEC11       | 0836  | _                        | _                        | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | ADFLTR1IE | ADFLTR0IE | ADCMP1IE  | ADCMP0IE  | -                        | 0000          |

| IPC0        | 0840  | _                        | T1IP2                    | T1IP1                    | T1IP0                    | _                        | OC1IP2                   | OC1IP1                   | OC1IP0                  | _                       | IC1IP2   | IC1IP1   | IC1IP0    | -         | INT0IP2   | INT0IP1   | INT0IP0                  | 4444          |

| IPC1        | 0842  | -                        | T2IP2                    | T2IP1                    | T2IP0                    | -                        | OC2IP2                   | OC2IP1                   | OC2IP0                  | _                       | IC2IP2   | IC2IP1   | IC2IP0    | -         | -         | -         | -                        | 4440          |

| IPC2        | 0844  | _                        | U1RXIP2                  | U1RXIP1                  | U1RXIP0                  | _                        | SPI1IP2                  | SPI1IP1                  | SPI1IP0                 | _                       | SPI1EIP2 | SPI1EIP1 | SPI1EIP0  | -         | T3IP2     | T3IP1     | T3IP0                    | 4444          |

| IPC3        | 0846  | _                        | NVMIP2                   | NVMIP1                   | NVMIP0                   | _                        | _                        | _                        | _                       | _                       | ADCIP2   | ADCIP1   | ADCIP0    | -         | U1TXIP2   | U1TXIP1   | U1TXIP0                  | 4044          |

| IPC4        | 0848  | _                        | CNIP2                    | CNIP1                    | CNIP0                    | _                        | AC1IP2                   | AC1IP1                   | AC1IP0                  | _                       | MI2C1IP2 | MI2C1IP1 | MI2C1IP0  | -         | SI2C1IP2  | SI2C1IP1  | SI2C1IP0                 | 4444          |

| IPC5        | 084A  | _                        | -                        | _                        | -                        | _                        | -                        | -                        | —                       | _                       | —        | -        | -         | -         | INT1IP2   | INT1IP1   | INT1IP0                  | 0004          |

| IPC6        | 084C  | _                        | T4IP2                    | T4IP1                    | T4IP0                    | _                        | OC4IP2                   | OC4IP1                   | OC4IP0                  | _                       | OC3IP2   | OC3IP1   | OC3IP0    | -         | -         | -         | -                        | 4440          |

| IPC7        | 084E  | _                        | U2TXIP2                  | U2TXIP1                  | U2TXIP0                  | _                        | U2RXIP2                  | U2RXIP1                  | U2RXIP0                 | _                       | INT2IP2  | INT2IP1  | INT2IP0   | _         | T5IP2     | T5IP1     | T5IP0                    | 4444          |

| IPC8        | 0850  | _                        | -                        | _                        | -                        | _                        | _                        | -                        | -                       | _                       | SPI2IP2  | SPI2IP1  | SPI2IP0   | -         | SPI2EIP2  | SPI2EIP1  | SPI2EIP0                 | 0044          |

| IPC9        | 0852  | _                        | _                        | _                        | _                        | _                        | IC4IP2                   | IC4IP1                   | IC4IP0                  | _                       | IC3IP2   | IC3IP1   | IC3IP0    | _         | _         | _         | _                        | 0440          |

Legend:

Note 1:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal. Only available on dsPIC33EPXXGS506 devices. Only available on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices.

2:

| U-0          | U-0          | U-0              | U-0            | U-0                                     | R/W-0            | U-0      | U-0   |

|--------------|--------------|------------------|----------------|-----------------------------------------|------------------|----------|-------|

| _            | —            | —                | —              | —                                       | CMPMD            | —        | _     |

| bit 15       |              |                  |                |                                         |                  |          | bit 8 |

|              |              |                  |                |                                         |                  |          |       |

| U-0          | U-0          | U-0              | U-0            | U-0                                     | U-0              | R/W-0    | U-0   |

| _            | _            | —                | —              | _                                       | —                | I2C2MD   | —     |

| bit 7        |              |                  |                |                                         |                  |          | bit 0 |

|              |              |                  |                |                                         |                  |          |       |

| Legend:      |              |                  |                |                                         |                  |          |       |

| R = Readab   | ole bit      | W = Writable     | bit            | U = Unimplem                            | nented bit, read | d as '0' |       |

| -n = Value a | at POR       | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                  |          |       |

|              |              |                  |                |                                         |                  |          |       |

| bit 15-11    | Unimplement  | ted: Read as '   | כ'             |                                         |                  |          |       |

| bit 10       | CMPMD: Con   | nparator Modul   | le Disable bit |                                         |                  |          |       |

|              | 1 = Comparat | or module is di  | sabled         |                                         |                  |          |       |

|              | 0 = Comparat | or module is ei  | nabled         |                                         |                  |          |       |

| bit 9-2      | Unimplement  | ted: Read as '   | כי             |                                         |                  |          |       |

| bit 1        | 12C2MD: 12C2 | 2 Module Disat   | ole bit        |                                         |                  |          |       |

|              |              | ule is disabled  |                |                                         |                  |          |       |

|              | 0 = I2C2 mod | ule is enabled   |                |                                         |                  |          |       |

#### REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 0 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       |                            |

#### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0  | U-0  | U-0 | U-0  | U-0  | U-0   |

|--------|-----|------|------|-----|------|------|-------|

| —      | —   | —    | —    | —   | —    | —    | —     |

| bit 15 |     |      |      |     |      |      | bit 8 |

|        |     |      |      |     |      |      |       |

| 11.0   |     | 11.0 | 11.0 |     | 11.0 | 11.0 | 11.0  |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                        |

|----------|---------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit |

|          | 1 = Reference clock module is disabled            |

|          | 0 = Reference clock module is enabled             |

| bit 2-0  | Unimplemented: Read as '0'                        |

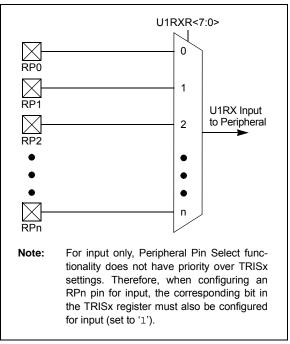

#### 10.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-19). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 10-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 10-2: REMAPPABLE INPUT FOR U1RX

#### 10.4.4.1 Virtual Connections

The dsPIC33EPXXGS50X devices support six virtual RPn pins (RP176-RP181), which are identical in functionality to all other RPn pins, with the exception of pinouts. These six pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP176 and the PWM Fault input can be configured for RP176 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

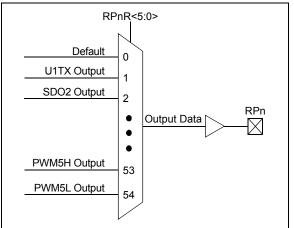

#### 10.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 10-20 through Register 10-38). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 10-3: MULTIPLEXING REMAPPABLE OUTPUTS FOR RPn

#### 10.4.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings, across any or all of the RPn pins, is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs, and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

| <b>REGISTER 12-2:</b> | TyCON: ( | (TIMER3 AND TIMER | 5) CONTROL REGISTER |

|-----------------------|----------|-------------------|---------------------|

|-----------------------|----------|-------------------|---------------------|

| TON <sup>(1)</sup> |                               | R/W-0                        | U-0                     | U-0                          | U-0             | U-0                  | U-0            |

|--------------------|-------------------------------|------------------------------|-------------------------|------------------------------|-----------------|----------------------|----------------|

| TON                |                               | TSIDL <sup>(2)</sup>         | —                       | _                            | _               | _                    | _              |

| bit 15             |                               |                              |                         |                              |                 |                      | bit            |

| U-0                | R/W-0                         | R/W-0                        | R/W-0                   | U-0                          | U-0             | R/W-0                | U-0            |

| _                  | TGATE <sup>(1)</sup>          | TCKPS1 <sup>(1)</sup>        | TCKPS0 <sup>(1)</sup>   | _                            | _               | TCS <sup>(1,3)</sup> | _              |

| bit 7              |                               |                              |                         |                              |                 |                      | bit            |

| Legend:            |                               |                              |                         |                              |                 |                      |                |

| R = Readable       | bit                           | W = Writable                 | hit                     | =   Inimpler                 | mented bit, rea | ad as 'O'            |                |

| -n = Value at I    |                               | '1' = Bit is set             |                         | '0' = Bit is cle             |                 | x = Bit is unkno     | מעאר           |

|                    | FOR                           | I - DILISSEL                 |                         |                              | aleu            |                      | 50011          |

| bit 15             | TON: Timery                   | On bit <sup>(1)</sup>        |                         |                              |                 |                      |                |

|                    | 1 = Starts 16-                | •                            |                         |                              |                 |                      |                |

|                    | 0 = Stops 16-                 | bit Timery                   |                         |                              |                 |                      |                |

| bit 14             | •                             | ted: Read as '               |                         |                              |                 |                      |                |

| bit 13             | TSIDL: Timer                  | y Stop in Idle M             | lode bit <sup>(2)</sup> |                              |                 |                      |                |

|                    |                               | ues module op                |                         |                              | dle mode        |                      |                |

|                    |                               | s module opera               |                         | ode                          |                 |                      |                |

| bit 12-7           | -                             | ted: Read as '               |                         | (4)                          |                 |                      |                |

| bit 6              |                               | ery Gated Time               | Accumulation            | Enable bit <sup>(1)</sup>    |                 |                      |                |

|                    | When TCS =<br>This bit is ign |                              |                         |                              |                 |                      |                |

|                    | When TCS =                    |                              |                         |                              |                 |                      |                |

|                    |                               | <u>o.</u><br>le accumulatior | n is enabled            |                              |                 |                      |                |

|                    |                               | e accumulation               |                         |                              |                 |                      |                |

| bit 5-4            | TCKPS<1:0>                    | : Timery Input               | Clock Prescal           | e Select bits <sup>(1)</sup> | 1               |                      |                |

|                    | 11 <b>= 1:256</b>             |                              |                         |                              |                 |                      |                |

|                    | 10 <b>= 1:64</b>              |                              |                         |                              |                 |                      |                |

|                    | 01 = 1:8<br>00 = 1:1          |                              |                         |                              |                 |                      |                |

| bit 3-2            |                               | ted: Read as '               | ı'                      |                              |                 |                      |                |

| bit 1              | -                             | Clock Source S               |                         |                              |                 |                      |                |

|                    |                               | clock is from pir            |                         | e risina edae)               |                 |                      |                |

|                    | 0 = Internal c                |                              |                         | c rising cage)               |                 |                      |                |

| bit 0              |                               | ted: Read as '               | )'                      |                              |                 |                      |                |

|                    |                               |                              |                         | 1), these bits               | have no effec   | t on Timery operat   | tion; all time |

|                    | ictions are set th            | •                            |                         | 1) in the Time-              | v Control rogi  | ster (TxCON<3>),     |                |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all devices. See the "Pin Diagrams" section for the available pins.

| R-0, HSC             |                                           | R-0, HSC                                 | R/W-0                   | R/W-0              | R/W-0                  | R/W-0                | R/W-0               |

|----------------------|-------------------------------------------|------------------------------------------|-------------------------|--------------------|------------------------|----------------------|---------------------|

| FLTSTAT <sup>(</sup> | <sup>1)</sup> CLSTAT <sup>(1)</sup>       | TRGSTAT                                  | FLTIEN                  | CLIEN              | TRGIEN                 | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |

| bit 15               |                                           |                                          |                         | •                  | •                      | •                    | bit 8               |

| R/W-0                | R/W-0                                     | U-0                                      | U-0                     | R/W-0              | R/W-0                  | R/W-0                | R/W-0               |

|                      |                                           | 0-0                                      | 0-0                     | 1                  | CAM <sup>(2,3,4)</sup> | XPRES <sup>(5)</sup> |                     |

| DTC1<br>bit 7        | DTC0                                      | _                                        |                         | MTBS               | CAM <sup>2,0,1</sup>   | XPRES <sup>(0)</sup> | IUE<br>bit (        |

|                      |                                           |                                          |                         |                    |                        |                      | Dit (               |

| Legend:              |                                           | HSC = Hardw                              | are Settable/C          | learable bit       |                        |                      |                     |

| R = Reada            | ble bit                                   | W = Writable I                           | oit                     | U = Unimplei       | mented bit, read       | l as '0'             |                     |

| -n = Value           | at POR                                    | '1' = Bit is set                         |                         | '0' = Bit is cle   | ared                   | x = Bit is unkr      | nown                |

|                      |                                           |                                          | (4)                     |                    |                        |                      |                     |

| bit 15               |                                           | ult Interrupt Sta                        |                         |                    |                        |                      |                     |

|                      |                                           | rupt is pending                          |                         |                    |                        |                      |                     |

|                      |                                           | nterrupt is pend<br>ared by setting      |                         |                    |                        |                      |                     |

| bit 14               |                                           | ent-Limit Interr                         |                         | )                  |                        |                      |                     |

|                      |                                           | nit interrupt is p                       | •                       |                    |                        |                      |                     |

|                      |                                           | t-limit interrupt                        |                         |                    |                        |                      |                     |

|                      | This bit is clea                          | ared by setting                          | CLIEN = 0.              |                    |                        |                      |                     |

| bit 13               | TRGSTAT: Tri                              | igger Interrupt S                        | Status bit              |                    |                        |                      |                     |

|                      |                                           | errupt is pendi                          |                         |                    |                        |                      |                     |

|                      |                                           | interrupt is per<br>ared by setting      |                         |                    |                        |                      |                     |

| bit 12               | FLTIEN: Fault                             | t Interrupt Enab                         | ole bit                 |                    |                        |                      |                     |

|                      |                                           | rupt is enabled<br>rupt is disabled      |                         | STAT bit is clea   | ired                   |                      |                     |

| bit 11               | CLIEN: Curre                              | nt-Limit Interru                         | pt Enable bit           |                    |                        |                      |                     |

|                      |                                           | nit interrupt is e<br>nit interrupt is o |                         | ne CLSTAT bit      | is cleared             |                      |                     |

| bit 10               | TRGIEN: Trig                              | ger Interrupt Er                         | nable bit               |                    |                        |                      |                     |

|                      |                                           | event generates                          |                         |                    | AT bit is cleared      |                      |                     |

| bit 9                | ITB: Independ                             | lent Time Base                           | Mode bit <sup>(3)</sup> |                    |                        |                      |                     |

|                      |                                           |                                          |                         | ne time base p     | eriod for this PV      | VMx generator        |                     |

|                      | 0 = PTPER re                              | gister provides                          | timing for this         | PWMx genera        | ator                   | ·                    |                     |

| bit 8                | MDCS: Maste                               | er Duty Cycle R                          | egister Select          | bit <sup>(3)</sup> |                        |                      |                     |

|                      | 1 = MDC regis                             | ster provides du                         | uty cycle inforr        | nation for this    | PWMx generate          | or                   |                     |

|                      | 0 = PDCx and                              | I SDCx register                          | s provide duty          | cycle informa      | tion for this PW       | Mx generator         |                     |

| Note 1:              | Software must cle                         | ar the interrupt                         | status here a           | nd in the corre    | sponding IFSx I        | pit in the interru   | pt controller.      |

|                      | The Independent<br>CAM bit is ignored     |                                          | de (ITB = 1) m          | ust be enabled     | I to use Center-       | Aligned mode.        | If ITB = 0, the     |

| 3:                   | These bits should                         | not be change                            | d after the PW          | /Mx is enabled     | by setting PTE         | N = 1 (PTCON         | <15>).              |

|                      | Center-Aligned m                          | -                                        |                         |                    |                        | -                    | -                   |

|                      | registers. The higl<br>the fastest clock. |                                          |                         |                    |                        |                      |                     |

|                      | The fastest clock.                        |                                          |                         |                    |                        |                      |                     |

#### **REGISTER 15-12: PWMCONX: PWMx CONTROL REGISTER (x = 1 to 5)**

#### **REGISTER 15-22:** FCLCONX: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (x = 1 to 5)

|                 | (x = 1                                  | to 5)                                                                                                                                                        |                                                 |                                                                                      |                                                                             |                                                  |                  |

|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|------------------|

| R/W-0           | R/W-0                                   | R/W-0                                                                                                                                                        | R/W-0                                           | R/W-0                                                                                | R/W-0                                                                       | R/W-0                                            | R/W-0            |

| IFLTMOD         | CLSRC4                                  | CLSRC3                                                                                                                                                       | CLSRC2                                          | CLSRC1                                                                               | CLSRC0                                                                      | CLPOL <sup>(1)</sup>                             | CLMOD            |

| bit 15          | •                                       |                                                                                                                                                              |                                                 | •<br>                                                                                |                                                                             |                                                  | bit 8            |

| R/W-1           | R/W-1                                   | R/W-1                                                                                                                                                        | R/W-1                                           | R/W-1                                                                                | R/W-0                                                                       | R/W-0                                            | R/W-0            |

| FLTSRC4         | FLTSRC3                                 | FLTSRC2                                                                                                                                                      | FLTSRC1                                         | FLTSRC0                                                                              | FLTPOL <sup>(1)</sup>                                                       | FLTMOD1                                          | FLTMOD0          |

| bit 7           |                                         |                                                                                                                                                              |                                                 |                                                                                      |                                                                             |                                                  | bit C            |

| Legend:         |                                         |                                                                                                                                                              |                                                 |                                                                                      |                                                                             |                                                  |                  |

| R = Readable    | bit                                     | W = Writable                                                                                                                                                 | oit                                             | U = Unimplem                                                                         | nented bit, read                                                            | l as '0'                                         |                  |

| -n = Value at I | POR                                     | '1' = Bit is set                                                                                                                                             |                                                 | '0' = Bit is clea                                                                    | ared                                                                        | x = Bit is unkr                                  | iown             |

| bit 14-10       | input map<br>0 = Normal F<br>outputs; t | es FLTDAT0 to f<br>Fault_mode:_Cu<br>he PWM Fault                                                                                                            | he PWMxL out<br>urrent-Limit mo<br>mode maps Fl | input maps FL<br>tput; the CLDAT<br>ode maps CLD<br>LTDAT<1:0> to<br>I Source Select | <pre>&lt;1:0&gt; bits are r<br/>AT&lt;1:0&gt; bits 1<br/>the PWMxH ar</pre> | not used for ove<br>to the PWMxH<br>nd PWMxL out | erride functions |

|                 | 01111 = Anal<br>01110 = Anal            | erved<br>og Comparato<br>og Comparato<br>og Comparato<br>og Comparato<br>t 12<br>t 11<br>t 10<br>t 9<br>t 8<br>t 7<br>t 6<br>t 5<br>t 4<br>t 3<br>t 2<br>t 1 | r 3<br>r 2                                      |                                                                                      |                                                                             |                                                  |                  |

| bit 9           | 1 = The selec<br>0 = The selec          | ent-Limit Polari<br>ted current-limi<br>ted current-limi                                                                                                     | t source is act<br>t source is act              | ive-low<br>ive-high                                                                  | bit                                                                         |                                                  |                  |

| bit 8           | 1 = Current-Li                          | mit mode is en<br>mit mode is dis                                                                                                                            | abled                                           | WMx Generator                                                                        | Dit                                                                         |                                                  |                  |

|                 |                                         | 1 1                                                                                                                                                          |                                                 |                                                                                      |                                                                             |                                                  |                  |

Note 1: These bits should be changed only when PTEN = 0 (PTCON<15>).

### REGISTER 17-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul>                                                                                                                           |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                                                                                                                                                                     |

| bit 3 | S: Start bit                                                                                                                                                                                                                                   |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                                     |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                                                                                                                                                                     |

| bit 2 | <b>R_W:</b> Read/Write Information bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                      |

|       | <ul> <li>1 = Read – Indicates data transfer is output from the slave</li> <li>0 = Write – Indicates data transfer is input to the slave</li> <li>Hardware is set or clear after reception of an I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                            |

|       | <ol> <li>Receive is complete, I2CxRCV is full</li> <li>Receive is not complete, I2CxRCV is empty</li> <li>Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads</li> <li>I2CxRCV.</li> </ol>     |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                           |

|       | 1 = Transmit is in progress, I2CxTRN is full                                                                                                                                                                                                   |

|       | <ul> <li>0 = Transmit is complete, I2CxTRN is empty</li> <li>Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission.</li> </ul>                                                               |

|       |                                                                                                                                                                                                                                                |

#### REGISTER 19-15: ADEIEL: ADC EARLY INTERRUPT ENABLE REGISTER LOW

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-------|-------|--------|-------|-------|-------|

|          |       |       | EIEN  | <15:8> |       |       |       |

| bit 15   |       |       |       |        |       |       | bit 8 |

|          |       |       |       |        |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | EIEN  | <7:0>  |       |       |       |

| bit 7    |       |       |       |        |       |       | bit 0 |

| <u> </u> |       |       |       |        |       |       |       |

| Legend:  |       |       |       |        |       |       |       |

| Logona.           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 15-0 EIEN<15:0>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

#### REGISTER 19-16: ADEIEH: ADC EARLY INTERRUPT ENABLE REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|

| —     | —   |       | EIEN<21:16> |       |       |       |       |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 EIEN<21:16>: Early Interrupt Enable for Corresponding Analog Inputs bits

1 = Early interrupt is enabled for the channel

0 = Early interrupt is disabled for the channel

#### TABLE 23-2: CONFIGURATION BITS DESCRIPTION

| Bit Field              | Description                                                                                                                                                                                                             |  |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BSS<1:0>               | Boot Segment Code-Protect Level bits                                                                                                                                                                                    |  |  |  |  |  |

|                        | 11 = Boot Segment is not code-protected other than BWRP                                                                                                                                                                 |  |  |  |  |  |

|                        | 10 = Standard security                                                                                                                                                                                                  |  |  |  |  |  |

| BSEN                   | 0x = High security<br>Boot Segment Control bit                                                                                                                                                                          |  |  |  |  |  |

| DSEN                   | 1 = No Boot Segment is enabled                                                                                                                                                                                          |  |  |  |  |  |

|                        | 0 = Boot Segment size is determined by the BSLIM<12:0> bits                                                                                                                                                             |  |  |  |  |  |

| BWRP                   | Boot Segment Write-Protect bit                                                                                                                                                                                          |  |  |  |  |  |

|                        | 1 = Boot Segment can be written<br>0 = Boot Segment is write-protected                                                                                                                                                  |  |  |  |  |  |

| BSLIM<12:0>            | Boot Segment Flash Page Address Limit bits                                                                                                                                                                              |  |  |  |  |  |

|                        | Contains the last active Boot Segment page. The value to be programmed is the inverted page address, such that programming additional '0's can only increase the Boot Segment size (i.e., 0x1FFD = 2 Pages or 1024 IW). |  |  |  |  |  |

| GSS<1:0>               | General Segment Code-Protect Level bits                                                                                                                                                                                 |  |  |  |  |  |

|                        | 11 = User program memory is not code-protected                                                                                                                                                                          |  |  |  |  |  |

|                        | 10 = Standard security<br>0x = High security                                                                                                                                                                            |  |  |  |  |  |

| GWRP                   | General Segment Write-Protect bit                                                                                                                                                                                       |  |  |  |  |  |

| owna                   | 1 = User program memory is not write-protected                                                                                                                                                                          |  |  |  |  |  |

|                        | 0 = User program memory is write-protected                                                                                                                                                                              |  |  |  |  |  |

| CWRP                   | Configuration Segment Write-Protect bit                                                                                                                                                                                 |  |  |  |  |  |

|                        | <ul><li>1 = Configuration data is not write-protected</li><li>0 = Configuration data is write-protected</li></ul>                                                                                                       |  |  |  |  |  |

| CSS<2:0>               | Configuration Segment Code-Protect Level bits                                                                                                                                                                           |  |  |  |  |  |

|                        | 111 = Configuration data is not code-protected                                                                                                                                                                          |  |  |  |  |  |

|                        | 110 = Standard security<br>10x = Enhanced security                                                                                                                                                                      |  |  |  |  |  |

|                        | 0xx = High security                                                                                                                                                                                                     |  |  |  |  |  |

| BTSWP                  | BOOTSWP Instruction Enable/Disable bit                                                                                                                                                                                  |  |  |  |  |  |

|                        | 1 = BOOTSWP instruction is disabled                                                                                                                                                                                     |  |  |  |  |  |

|                        | 0 = BOOTSWP instruction is enabled                                                                                                                                                                                      |  |  |  |  |  |

| BSEQ<11:0>             | Boot Sequence Number bits (Dual Partition modes only)                                                                                                                                                                   |  |  |  |  |  |

|                        | Relative value defining which partition will be active after device Reset; the partition<br>containing a lower boot number will be active.                                                                              |  |  |  |  |  |

| IBSEQ<11:0>            | Inverse Boot Sequence Number bits (Dual Partition modes only)                                                                                                                                                           |  |  |  |  |  |

|                        | The one's complement of BSEQ<11:0>; must be calculated by the user and written for                                                                                                                                      |  |  |  |  |  |

|                        | device programming. If BSEQx and IBSEQx are not complements of each other, the Boot Sequence Number is considered to be invalid.                                                                                        |  |  |  |  |  |

| AIVTDIS <sup>(1)</sup> | Alternate Interrupt Vector Table bit                                                                                                                                                                                    |  |  |  |  |  |

|                        | 1 = Alternate Interrupt Vector Table is disabled                                                                                                                                                                        |  |  |  |  |  |

| IESO                   | 0 = Alternate Interrupt Vector Table is enabled if INTCON2<8> = 1                                                                                                                                                       |  |  |  |  |  |

| IESU                   | Two-Speed Oscillator Start-up Enable bit<br>1 = Starts up device with FRC, then automatically switches to the user-selected oscillator                                                                                  |  |  |  |  |  |

|                        | source when ready                                                                                                                                                                                                       |  |  |  |  |  |

|                        | 0 = Starts up device with the user-selected oscillator source                                                                                                                                                           |  |  |  |  |  |

| PWMLOCK                | PWMx Lock Enable bit                                                                                                                                                                                                    |  |  |  |  |  |

|                        | 1 = Certain PWMx registers may only be written after a key sequence                                                                                                                                                     |  |  |  |  |  |

|                        | 0 = PWMx registers may be written without a key sequence                                                                                                                                                                |  |  |  |  |  |

Note 1: The Boot Segment must be present to use the Alternate Interrupt Vector Table.

#### TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn | Multiplicand and Multiplier Working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                       |

| Wn    | One of 16 Working registers $\in$ {W0W15}                                                                                                                                                                                                                            |

| Wnd   | One of 16 Destination Working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns   | One of 16 Source Working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG  | W0 (Working register used in file register instructions)                                                                                                                                                                                                             |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| DC CHARACTERISTICS |        |                                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |                     |       |                                                                                                                                      |

|--------------------|--------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|