Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502t-i-2n |

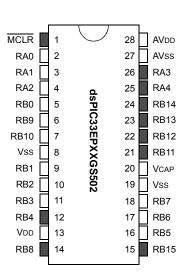

### **Pin Diagrams**

| Pin | Pin Function                                       | Pin | Pin Function                      |

|-----|----------------------------------------------------|-----|-----------------------------------|

| 1   | MCLR                                               | 15  | PGEC3/SCL2/RP47/RB15              |

| 2   | AN0/PGA1P1/CMP1A/RA0                               | 16  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5 |

| 3   | AN1/PGA1P2/PGA2P1/CMP1B/RA1                        | 17  | PGED1/TDI/AN20/SCL1/RP38/RB6      |

| 4   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2                  | 18  | PGEC1/AN21/SDA1/RP39/RB7          |

| 5   | AN3/PGA2P3/CMP1D/CMP2B/ <b>RP32</b> /RB0           | 19  | Vss                               |

| 6   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9                     | 20  | VCAP                              |

| 7   | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10                    | 21  | TMS/PWM3H/ <b>RP43</b> /RB11      |

| 8   | Vss                                                | 22  | TCK/PWM3L/RP44/RB12               |

| 9   | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           | 23  | PWM2H/ <b>RP45</b> /RB13          |

| 10  | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/ <b>RP34</b> /RB2 | 24  | PWM2L/ <b>RP46</b> /RB14          |

| 11  | PGED2/AN18/DACOUT1/INT0/RP35/RB3                   | 25  | PWM1H/RA4                         |

| 12  | PGEC2/ADTRG31/EXTREF1/RP36/RB4                     | 26  | PWM1L/RA3                         |

| 13  | VDD                                                | 27  | AVss                              |

| 14  | PGED3/SDA2/FLT31/RP40/RB8                          | 28  | AVDD                              |

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

### 3.0 CPU

# Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for Digital Signal Processing (DSP). The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 3.1 Registers

The dsPIC33EPXXGS50X devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EPXXGS50X devices include two Alternate Working register sets which consist of W0 through W14. The Alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The Alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register. The Alternate Working registers can also be accessed manually by using the CTXTSWP instruction. The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current and most recent, manually selected Working register sets.

### 3.2 Instruction Set

The instruction set for dsPIC33EPXXGS50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

### 3.3 Data Space Addressing

The base Data Space can be addressed as up to 4K words or 8 Kbytes, and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Refer to "Data Memory" (DS70595) in the "dsPIC33/PIC24 Family Reference Manual" for more details on PSV and table accesses.

On dsPIC33EPXXGS50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms.

### 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- · Register Direct

- · Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

DS70005127D-page 55

TABLE 4-16: ADC REGISTER MAP (CONTINUED)

|             |       |                         |                                                                              | 1                       | ., ., (55               |                         |                         |                        |                        |             | 1       | 1        |          |          | 1        |                         |                         | г п           |

|-------------|-------|-------------------------|------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|-------------|---------|----------|----------|----------|----------|-------------------------|-------------------------|---------------|

| SFR<br>Name | Addr. | Bit 15                  | Bit 14                                                                       | Bit 13                  | Bit 12                  | Bit 11                  | Bit 10                  | Bit 9                  | Bit 8                  | Bit 7       | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1                   | Bit 0                   | All<br>Resets |

| ADLVLTRGL   | 03D0  | LVLEN15 <sup>(1)</sup>  | LVLEN14                                                                      | LVLEN13 <sup>(1)</sup>  | LVLEN12 <sup>(2)</sup>  | LVLEN11 <sup>(2)</sup>  | LVLEN10 <sup>(2)</sup>  | LVLEN9 <sup>(2)</sup>  | LVLEN8 <sup>(2)</sup>  | LVLEN7      | LVLEN6  | LVLEN5   | LVLEN4   | LVLEN3   | LVLEN2   | LVLEN1                  | LVLEN0                  | 0000          |

| ADLVLTRGH   | 03D2  | _                       | _                                                                            | _                       | _                       | _                       | 1                       | _                      | -                      | -           | _       | LVLEN21  | LVLEN20  | LVLEN19  | LVLEN18  | LVLEN17 <sup>(2)</sup>  | LVLEN16 <sup>(1)</sup>  | 0000          |

| ADCORE0L    | 03D4  | _                       | _                                                                            | _                       | _                       | 1                       | -                       |                        |                        |             |         | SAMO     | >9:0>    |          |          |                         |                         | 0000          |

| ADCORE0H    | 03D6  | _                       | _                                                                            | _                       | EISEL2                  | EISEL1                  | EISEL0                  | RES1                   | RES0                   | _           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                   | ADCS0                   | 0000          |

| ADCORE1L    | 03D8  | _                       | -                                                                            | _                       | _                       | -                       | -                       |                        |                        |             |         | SAMO     | >9:0>    |          |          |                         |                         | 0000          |

| ADCORE1H    | 03DA  | _                       | -                                                                            | _                       | EISEL2                  | EISEL1                  | EISEL0                  | RES1                   | RES0                   | -           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                   | ADCS0                   | 0000          |

| ADCORE2L    | 03DC  | -                       | ı                                                                            | _                       | _                       | -                       | ı                       |                        |                        |             |         | SAMO     | <9:0>    |          |          |                         |                         | 0000          |

| ADCORE2H    | 03DE  | -                       | EISEL2 EISEL1 EISEL0 RES1 RES0 - ADCS6 ADCS5 ADCS4 ADCS3 ADCS2 ADCS1 ADCS0 0 |                         |                         |                         |                         |                        |                        |             |         |          |          | 0000     |          |                         |                         |               |

| ADCORE3L    | 03E0  | -                       | ı                                                                            | _                       | _                       | -                       | ı                       |                        |                        |             |         | SAMO     | >9:0>    |          |          |                         |                         | 0000          |

| ADCORE3H    | 03E2  | _                       | _                                                                            | _                       | EISEL2                  | EISEL1                  | EISEL0                  | RES1                   | RES0                   | _           | ADCS6   | ADCS5    | ADCS4    | ADCS3    | ADCS2    | ADCS1                   | ADCS0                   | 0000          |

| ADEIEL      | 03F0  | EIEN15 <sup>(1)</sup>   | EIEN14 <sup>(2)</sup>                                                        | EIEN13 <sup>(1)</sup>   | EIEN12 <sup>(2)</sup>   | EIEN11 <sup>(2)</sup>   | EIEN10 <sup>(2)</sup>   | EIEN9 <sup>(2)</sup>   | EIEN8 <sup>(2)</sup>   | EIEN7       | EIEN6   | EIEN5    | EIEN4    | EIEN3    | EIEN2    | EIEN1                   | EIEN0                   | 0000          |

| ADEIEH      | 03F2  | _                       | _                                                                            | _                       | _                       | 1                       | -                       | _                      | _                      | _           | _       | EIEN21   | EIEN20   | EIEN19   | EIEN18   | EIEN17 <sup>(2)</sup>   | EIEN16 <sup>(1)</sup>   | 0000          |

| ADEISTATL   | 03F8  | EISTAT15 <sup>(1)</sup> | EISTAT14 <sup>(2)</sup>                                                      | EISTAT13 <sup>(1)</sup> | EISTAT12 <sup>(2)</sup> | EISTAT11 <sup>(2)</sup> | EISTAT10 <sup>(2)</sup> | EISTAT9 <sup>(2)</sup> | EISTAT8 <sup>(2)</sup> | EISTAT7     | EISTAT6 | EISTAT5  | EISTAT4  | EISTAT3  | EISTAT2  | EISTAT1                 | EISTAT0                 | 0000          |

| ADEISTATH   | 03FA  | _                       | _                                                                            | _                       | _                       | _                       | _                       | _                      | _                      | _           | _       | EISTAT21 | EISTAT20 | EISTAT19 | EISTAT18 | EISTAT17 <sup>(2)</sup> | EISTAT16 <sup>(1)</sup> | 0000          |

| ADCON5L     | 0400  | SHRRDY                  | _                                                                            | _                       | _                       | C3RDY                   | C2RDY                   | C1RDY                  | C0RDY                  | SHRPWR      | _       | _        | _        | C3PWR    | C2PWR    | C1PWR                   | C0PWR                   | 0000          |

| ADCON5H     | 0402  | _                       | _                                                                            | _                       | _                       | WARMTIME3               | WARMTIME2               | WARMTIME1              | WARMTIME0              | SHRCIE      | _       | _        | _        | C3CIE    | C2CIE    | C1CIE                   | C0CIE                   | 0000          |

| ADCAL0L     | 0404  | CAL1RDY                 | _                                                                            | _                       | _                       | 1                       | CAL1DIFF                | CAL1EN                 | CAL1RUN                | CAL0RDY     | _       | _        | _        | _        | CAL0DIFF | CAL0EN                  | CAL0RUN                 | 0000          |

| ADCAL0H     | 0406  | CAL3RDY                 | _                                                                            | _                       | _                       | 1                       | CAL3DIFF                | CAL3EN                 | CAL3RUN                | CAL2RDY     | _       | _        | _        | _        | CAL2DIFF | CAL2EN                  | CAL2RUN                 | 0000          |

| ADCAL1H     | 040A  | CSHRRDY                 | _                                                                            | _                       | _                       | 1                       | CSHRDIFF                | CSHREN                 | CSHRRUN                | _           | _       | _        | _        | _        | _        | _                       | _                       | 0000          |

| ADCBUF0     | 040C  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 0 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF1     | 040E  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 1 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF2     | 0410  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 2 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF3     | 0412  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 3 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF4     | 0414  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 4 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF5     | 0416  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 5 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF6     | 041B  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 6 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF7     | 041A  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 7 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF8     | 041C  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 8 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF9     | 041E  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Da                 | ta Buffer 9 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF10    | 0420  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 10 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF11    | 0422  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 11 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF12    | 0424  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 12 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF13    | 0426  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 13 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF14    | 0428  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 14 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF15    | 042A  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 15 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF16    | 042C  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 16 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF17    | 042E  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 17 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF18    | 0430  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 18 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF19    | 0432  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 19 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF20    | 0434  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 20 |         |          |          |          |          |                         |                         | 0000          |

| ADCBUF21    | 0436  |                         |                                                                              |                         |                         |                         |                         |                        | ADC Dat                | a Buffer 21 |         |          |          |          |          |                         |                         | 0000          |

| I edend:    |       |                         |                                                                              | et values are           |                         |                         |                         |                        |                        |             |         |          |          |          |          |                         |                         |               |

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Implemented on dsPlC33EPXXGS506 devices only.

Implemented on dsPlC33EPXXGS504/505 and dsPlC33EPXXGS506 devices only.

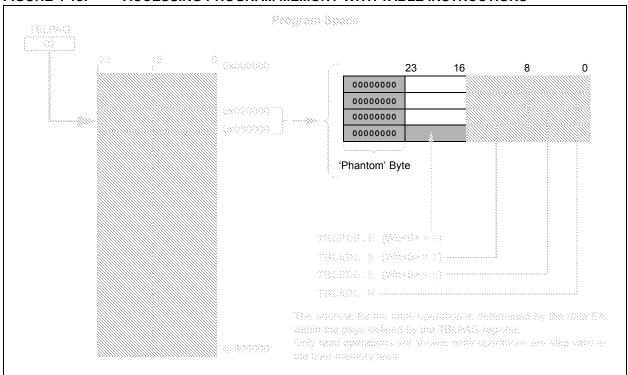

# 4.9.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte

of the lower program word is mapped to the

lower byte of a data address. The upper byte

is selected when Byte Select is '1'; the lower

byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0** "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-15: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

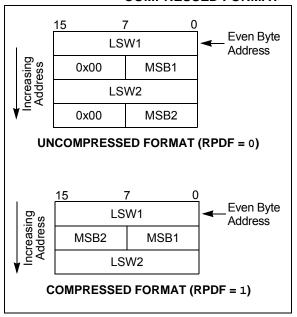

### 5.2 RTSP Operation

The dsPIC33EPXXGS50X family Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a single page (8 rows or 512 instructions) of memory at a time and to program one row at a time. It is possible to program two instructions at a time as well.

The page erase and single row write blocks are edgealigned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Figure 26-14 in **Section 26.0 "Electrical Characteristics"** lists the typical erase and programming times.

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

The basic sequence for RTSP word programming is to use the <code>TBLWTL</code> and <code>TBLWTH</code> instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. Refer to Figure 4-1 through Figure 4-4 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation. For example, when performing Flash write operations on the Inactive Partition in Dual Partition mode, where the CPU remains running, it is necessary to wait for the NVM interrupt before programming the next block of Flash program memory.

FIGURE 5-2: UNCOMPRESSED/

COMPRESSED FORMAT

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

# 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000000, 0x000004, 0x000008, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|---------|---------|-------|-------|-------|

| NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE | OVBTE | COVTE |

| bit 15 |        |        |         |         |       |       | bit 8 |

| R/W-0    | R/W-0   | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|----------|---------|-----|---------|---------|--------|---------|-------|

| SFTACERR | DIV0ERR | _   | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7    |         |     |         |         |        |         | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | NSTDIS: Interrupt Nesting Disable bit                                                                                                                       |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIL 13 | 1 = Interrupt nesting is disabled                                                                                                                           |

|        | 0 = Interrupt nesting is enabled                                                                                                                            |

| bit 14 | OVAERR: Accumulator A Overflow Trap Flag bit                                                                                                                |

|        | 1 = Trap was caused by overflow of Accumulator A                                                                                                            |

|        | 0 = Trap was not caused by overflow of Accumulator A                                                                                                        |

| bit 13 | OVBERR: Accumulator B Overflow Trap Flag bit                                                                                                                |

|        | 1 = Trap was caused by overflow of Accumulator B                                                                                                            |

|        | 0 = Trap was not caused by overflow of Accumulator B                                                                                                        |

| bit 12 | COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit                                                                                                  |

|        | 1 = Trap was caused by catastrophic overflow of Accumulator A 0 = Trap was not caused by catastrophic overflow of Accumulator A                             |

| bit 11 | COVBERR: Accumulator B Catastrophic Overflow Trap Flag bit                                                                                                  |

|        | 1 = Trap was caused by catastrophic overflow of Accumulator B                                                                                               |

|        | 0 = Trap was not caused by catastrophic overflow of Accumulator B                                                                                           |

| bit 10 | <b>OVATE:</b> Accumulator A Overflow Trap Enable bit                                                                                                        |

|        | 1 = Trap overflow of Accumulator A<br>0 = Trap is disabled                                                                                                  |

| bit 9  | OVBTE: Accumulator B Overflow Trap Enable bit                                                                                                               |

|        | 1 = Trap overflow of Accumulator B                                                                                                                          |

|        | 0 = Trap is disabled                                                                                                                                        |

| bit 8  | COVTE: Catastrophic Overflow Trap Enable bit                                                                                                                |

|        | <ul><li>1 = Trap on catastrophic overflow of Accumulator A or B is enabled</li><li>0 = Trap is disabled</li></ul>                                           |

| bit 7  | SFTACERR: Shift Accumulator Error Status bit                                                                                                                |

|        | <ul><li>1 = Math error trap was caused by an invalid accumulator shift</li><li>0 = Math error trap was not caused by an invalid accumulator shift</li></ul> |

| bit 6  | DIV0ERR: Divide-by-Zero Error Status bit                                                                                                                    |

|        | 1 = Math error trap was caused by a divide-by-zero                                                                                                          |

|        | 0 = Math error trap was not caused by a divide-by-zero                                                                                                      |

| bit 5  | Unimplemented: Read as '0'                                                                                                                                  |

| bit 4  | MATHERR: Math Error Status bit                                                                                                                              |

|        | 1 = Math error trap has occurred                                                                                                                            |

|        | 0 = Math error trap has not occurred                                                                                                                        |

| bit 3  | ADDRERR: Address Error Trap Status bit                                                                                                                      |

|        | 1 = Address error trap has occurred                                                                                                                         |

|        | 0 = Address error trap has not occurred                                                                                                                     |

### REGISTER 15-13: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER (x = 1 to 5) $^{(1,2,3)}$

| R/W-0  | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | PDCx<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |            |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | PDCx<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 |           |       |       |       |       |       | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

- Note 1: In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In the Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL.

- 2: The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period 0x0008.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

## REGISTER 15-14: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER (x = 1 to 5) $^{(1,2,3)}$

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | SDCx<15:8>   |       |       |       |       |       |       |  |  |  |

| bit 15 | bit 15 bit 8 |       |       |       |       |       |       |  |  |  |

| R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | SDCx<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 |           |       |       |       |       |       | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-0 SDCx<15:0>: PWMx Secondary Duty Cycle for PWMxL Output Pin bits

- **Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

- 2: The smallest pulse width that can be generated on the PWMx output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period 0x0008.

- **3:** As the duty cycle gets closer to 0% or 100% of the PWMx period (0 to 40 ns, depending on the mode of operation), PWMx duty cycle resolution will increase from 1 to 3 LSBs.

### REGISTER 15-16: SPHASEx: PWMx SECONDARY PHASE-SHIFT REGISTER (x = 1 to 5) $^{(1,2)}$

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | SPHASEx<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |               |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|

| SPHASEx<7:0> |       |       |       |       |       |       |       |

| bit 7        |       |       |       |       |       |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **SPHASEx<15:0>:** Secondary Phase Offset for PWMxL Output Pin bits (used in Independent PWM mode only)

**Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11), PHASEx<15:0> = Phase-shift value for PWMxL only

- 2: If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); SPHASEx<15:0> = Not used

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxL only

- When the PHASEx/SPHASEx registers provide the local period, the valid range of values is 0x0010-0xFFF8

### **REGISTER 15-17: DTRx: PWMx DEAD-TIME REGISTER (x = 1 to 5)**

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      |     |       |       | DTRx< | <13:8> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| DTRx<7:0> |       |       |       |       |       |       |       |

| bit 7     |       |       |       |       |       |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

### REGISTER 15-18: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER (x = 1 to 5)

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 |

|--------|-----|-------|-------|--------|----------|-------|-------|

| _      | _   |       |       | ALTDTR | Rx<13:8> |       |       |

| bit 15 |     |       |       |        |          |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|---------|-------|-------|-------|-------|

|       |       |       | Rx<7:0> |       |       |       |       |

| bit 7 |       |       |         |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

### REGISTER 15-27: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER (x = 1 to 5)

| R-0                   | R-0 | R-0   | R-0 | R-0 | R-0 | R-0 | R-0 |  |

|-----------------------|-----|-------|-----|-----|-----|-----|-----|--|

| PWMCAP<12:5>(1,2,3,4) |     |       |     |     |     |     |     |  |

| bit 15                |     | bit 8 |     |     |     |     |     |  |

| R-0   | R-0 | R-0                       | R-0 | R-0 | U-0   | U-0 | U-0 |

|-------|-----|---------------------------|-----|-----|-------|-----|-----|

|       | PW  | MCAP<4:0> <sup>(1,2</sup> | _   | _   | _     |     |     |

| bit 7 |     |                           |     |     | bit 0 |     |     |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **PWMCAP<12:0>:** PWMx Primary Time Base Capture Value bits<sup>(1,2,3,4)</sup>

The value in this register represents the captured PWMx time base value when a leading edge is

detected on the current-limit input.

bit 2-0 **Unimplemented:** Read as '0'

**Note 1:** The capture feature is only available on a primary output (PWMxH).

2: This feature is active only after LEB processing on the current-limit input signal is complete.

3: The minimum capture resolution is 8.32 ns.

4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPIx Master modes only)

1 = Internal SPIx clock is disabled, pin functions as I/O

0 = Internal SPIx clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 **MODE16:** Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master Mode:

1 = Input data is sampled at the end of data output time

0 = Input data is sampled at the middle of data output time

Slave Mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module; pin is controlled by port function

bit 6 CKP: Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to the value of 1:1.

### REGISTER 17-3: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC | R-0, HSC | R-0, HSC | U-0 | U-0 | R/C-0, HS | R-0, HSC | R-0, HSC |

|----------|----------|----------|-----|-----|-----------|----------|----------|

| ACKSTAT  | TRSTAT   | ACKTIM   | _   | _   | BCL       | GCSTAT   | ADD10    |

| bit 15   |          |          |     |     |           |          | bit 8    |

| R/C-0, HS | R/C-0, HS | R-0, HSC | R/C-0, HSC | R/C-0, HSC | R-0, HSC | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|------------|------------|----------|----------|----------|

| IWCOL     | I2COV     | D_A      | Р          | S          | R_W      | RBF      | TBF      |

| bit 7     |           |          |            |            |          |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit         | HSC = Hardware Settable/Clearable bit |  |

|-------------------|-------------------|------------------------------------|---------------------------------------|--|

| R = Readable bit  | W = Writable bit  | '0' = Bit is cleared               | x = Bit is unknown                    |  |

| -n = Value at POR | '1' = Bit is set  | U = Unimplemented bit, read as '0' |                                       |  |

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = NACK was received from slave

- 0 = ACK was received from slave

Hardware is set or clear at the end of a slave Acknowledge.

- bit 14 TRSTAT: Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.

- bit 13 **ACKTIM:** Acknowledge Time Status bit (I<sup>2</sup>C Slave mode only)

- $1 = I^2C$  bus is an Acknowledge sequence, set on the 8th falling edge of SCLx

- 0 = Not an Acknowledge sequence, cleared on the 9th rising edge of SCLx

- bit 12-11 **Unimplemented:** Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No bus collision detected

Hardware is set at detection of a bus collision.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware is set when address matches the general call address. Hardware is clear at Stop detection.

- bit 8 ADD10: 10-Bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop detection.

- bit 7 IWCOL: I2Cx Write Collision Detect bit

- 1 = An attempt to write to the I2CxTRN register failed because the I2C module is busy

- 0 = No collision

Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: I2Cx Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register was still holding the previous byte

- 0 = No overflow

Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (I<sup>2</sup>C Slave mode only)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was a device address

Hardware is clear at a device address match. Hardware is set by reception of a slave byte.

### 18.3 UART Control Registers

### REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | _   | USIDL | IREN <sup>(2)</sup> | RTSMD | _   | UEN1  | UEN0  |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0, HC | R/W-0  | R/W-0, HC | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0 |

|-----------|--------|-----------|--------|-------|--------|--------|-------|

| WAKE      | LPBACK | ABAUD     | URXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL |

| bit 7     |        |           |        |       |        |        | bit 0 |

Legend:HC = Hardware Clearable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **UARTEN:** UARTX Enable bit<sup>(1)</sup>

1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN<1:0>

0 = UARTx is disabled; all UARTx pins are controlled by PORT latches; UARTx power consumption is minimal

bit 14 Unimplemented: Read as '0'

bit 13 USIDL: UARTx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 IREN: IrDA® Encoder and Decoder Enable bit(2)

1 = IrDA encoder and decoder are enabled

0 = IrDA encoder and decoder are disabled

bit 11 RTSMD: Mode Selection for UxRTS Pin bit

$1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

$0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

bit 10 **Unimplemented:** Read as '0'

bit 9-8 **UEN<1:0>:** UARTx Pin Enable bits

11 = UxTX, UxRX and BCLKx pins are enabled and used; UxCTS pin is controlled by PORT latches

10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

01 = UxTX, UxRX and  $\overline{\text{UxRTS}}$  pins are enabled and used;  $\overline{\text{UxCTS}}$  pin is controlled by PORT latches

00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLKx pins are controlled by PORT latches

bit 7 WAKE: Wake-up on Start Bit Detect During Sleep Mode Enable bit

1 = UARTx continues to sample the UxRX pin, interrupt is generated on the falling edge; bit is cleared in hardware on the following rising edge

0 = No wake-up is enabled

bit 6 LPBACK: UARTx Loopback Mode Select bit

1 = Enables Loopback mode

0 = Loopback mode is disabled

Note 1: Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.

2: This feature is only available for the  $16x BRG \mod (BRGH = 0)$ .

### REGISTER 19-4: ADCON2H: ADC CONTROL REGISTER 2 HIGH

| R-0, HSC | R-0, HSC | r-0 | r-0 | r-0 | r-0 | R/W-0    | R/W-0    |

|----------|----------|-----|-----|-----|-----|----------|----------|

| REFRDY   | REFERR   | _   | _   | _   | _   | SHRSAMC9 | SHRSAMC8 |

| bit 15   |          |     |     |     |     |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SHRSAMC7 | SHRSAMC6 | SHRSAMC5 | SHRSAMC4 | SHRSAMC3 | SHRSAMC2 | SHRSAMC1 | SHRSAMC0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend: r = Reserved bit          |                  | U = Unimplemented bit, | U = Unimplemented bit, read as '0'    |  |  |  |

|-----------------------------------|------------------|------------------------|---------------------------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | HSC = Hardware Settal  | HSC = Hardware Settable/Clearable bit |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                    |  |  |  |

bit 15 REFRDY: Band Gap and Reference Voltage Ready Flag bit

1 = Band gap is ready

0 = Band gap is not ready

bit 14 REFERR: Band Gap or Reference Voltage Error Flag bit

1 = Band gap was removed after the ADC module was enabled (ADON = 1)

0 = No band gap error was detected

bit 13-10 Reserved: Maintain as '0'

bit 9-0 SHRSAMC<9:0>: Shared ADC Core Sample Time Selection bits

These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core sample time.

1111111111 = 1025 TADCORE

•

•

0000000001 = 3 TADCORE 0000000000 = 2 TADCORE

### 20.3 Module Applications

This module provides a means for the SMPS dsPIC® DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 12-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWMx Signal (current limit)

- Truncate the PWMx Period (current minimum)

- Disable the PWMx Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWMx output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

### 20.4 Digital-to-Analog Comparator (DAC)

Each analog comparator has a dedicated 12-bit DAC that is used to program the comparator threshold voltage via the CMPxDAC register. The DAC voltage reference source is selected using the EXTREF and RANGE bits in the CMPxCON register.

The EXTREF bit selects either the external voltage reference, EXTREFx, or an internal source as the voltage reference source. The EXTREFx input enables users to connect to a voltage reference that better suits their application. The RANGE bit enables AVDD as the voltage reference source for the DAC when an internal voltage reference is selected.

Note: EXTREF2 is not available on all devices.

Each DACx has an output enable bit, DACOE, in the CMPxCON register that enables the DACx reference voltage to be routed to an external output pin (DACOUTx). Refer to Figure 20-1 for connecting the DACx output voltage to the DACOUTx pins.

- Note 1: Ensure that multiple DACOE bits are not set in software. The output on the DACOUTx pin will be indeterminate if multiple comparators enable the DACx output.

- 2: DACOUT2 is not available on all devices.

### 20.5 Pulse Stretcher and Digital Logic

The analog comparator can respond to very fast transient signals. After the comparator output is given the desired polarity, the signal is passed to a pulse stretching circuit. The pulse stretching circuit has an asynchronous set function and a delay circuit that ensures the minimum pulse width is three system clock cycles wide to allow the attached circuitry to properly respond to a narrow pulse event.

The pulse stretcher circuit is followed by a digital filter. The digital filter is enabled via the FLTREN bit in the CMPxCON register. The digital filter operates with the clock specified via the FCLKSEL bit in the CMPxCON register. The comparator signal must be stable in a high or low state, for at least three of the selected clock cycles, for it to pass through the digital filter.

TABLE 24-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | str Assembly Mnemonic |        | Assembly Syntax | Description                                    | # of<br>Words | # of<br>Cycles <sup>(1)</sup> | Status Flags<br>Affected |

|--------------------|-----------------------|--------|-----------------|------------------------------------------------|---------------|-------------------------------|--------------------------|

| 55                 | NEG                   | NEG    | Acc             | Negate Accumulator                             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                       | NEG    | f               | $f = \overline{f} + 1$                         | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                       | NEG    | f,WREG          | WREG = <del>f</del> + 1                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                       | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                       | 1             | 1                             | C,DC,N,OV,Z              |

| 56                 | NOP                   | NOP    | ,               | No Operation                                   | 1             | 1                             | None                     |

|                    |                       | NOPR   |                 | No Operation                                   | 1             | 1                             | None                     |

| 57                 | POP                   | POP    | f               | Pop f from Top-of-Stack (TOS)                  | 1             | 1                             | None                     |

|                    |                       | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo             | 1             | 1                             | None                     |

|                    |                       | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to W(nd):W(nd + 1) | 1             | 2                             | None                     |

|                    |                       | POP.S  |                 | Pop Shadow Registers                           | 1             | 1                             | All                      |

| 58                 | PUSH                  | PUSH   | f               | Push f to Top-of-Stack (TOS)                   | 1             | 1                             | None                     |

|                    |                       | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                 | 1             | 1                             | None                     |

|                    |                       | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)     | 1             | 2                             | None                     |

|                    |                       | PUSH.S |                 | Push Shadow Registers                          | 1             | 1                             | None                     |

| 59                 | PWRSAV                | PWRSAV | #lit1           | Go into Sleep or Idle mode                     | 1             | 1                             | WDTO,Sleep               |

| 60                 | RCALL                 | RCALL  | Expr            | Relative Call                                  | 1             | 4                             | SFA                      |

|                    |                       | RCALL  | Wn              | Computed Call                                  | 1             | 4                             | SFA                      |

| 61                 | REPEAT                | REPEAT | #lit15          | Repeat Next Instruction lit15 + 1 time         | 1             | 1                             | None                     |

|                    |                       | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 time          | 1             | 1                             | None                     |

| 62                 | RESET                 | RESET  |                 | Software device Reset                          | 1             | 1                             | None                     |

| 63                 | RETFIE                | RETFIE |                 | Return from interrupt                          | 1             | 6 (5)                         | SFA                      |

| 64                 | RETLW                 | RETLW  | #lit10,Wn       | Return with literal in Wn                      | 1             | 6 (5)                         | SFA                      |

| 65                 | RETURN                | RETURN |                 | Return from Subroutine                         | 1             | 6 (5)                         | SFA                      |

| 66                 | RLC                   | RLC    | f               | f = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                    |

|                    |                       | RLC    | f,WREG          | WREG = Rotate Left through Carry f             | 1             | 1                             | C,N,Z                    |

|                    |                       | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws              | 1             | 1                             | C,N,Z                    |

| 67                 | RLNC                  | RLNC   | f               | f = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                      |

|                    |                       | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f                | 1             | 1                             | N,Z                      |

|                    |                       | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws                 | 1             | 1                             | N,Z                      |

| 68                 | RRC                   | RRC    | f               | f = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                    |

|                    |                       | RRC    | f,WREG          | WREG = Rotate Right through Carry f            | 1             | 1                             | C,N,Z                    |

|                    |                       | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws             | 1             | 1                             | C,N,Z                    |

| 69                 | RRNC                  | RRNC   | f               | f = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                      |

|                    |                       | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f               | 1             | 1                             | N,Z                      |

|                    |                       | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws                | 1             | 1                             | N,Z                      |

| 70                 | SAC                   | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                              | 1             | 1                             | None                     |

|                    |                       | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator                      | 1             | 1                             | None                     |

| 71                 | SE                    | SE     | Ws,Wnd          | Wnd = sign-extended Ws                         | 1             | 1                             | C,N,Z                    |

| 72                 | SETM                  | SETM   | f               | f = 0xFFFF                                     | 1             | 1                             | None                     |

|                    |                       | SETM   | WREG            | WREG = 0xFFFF                                  | 1             | 1                             | None                     |

|                    |                       | SETM   | Ws              | Ws = 0xFFFF                                    | 1             | 1                             | None                     |

| 73                 | SFTAC                 | SFTAC  | Acc, Wn         | Arithmetic Shift Accumulator by (Wn)           | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                       | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                       |        |                 | -                                              |               |                               |                          |

Note 1: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

TABLE 26-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CHARACTERISTICS |        |                                                                  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |   |    |    |                                                                                                               |  |

|--------------------|--------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|---------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | ool Characteristic Min. Typ. <sup>(1)</sup> Max. Units Condition |                                                                                                                                                                                                                                                  |   |    |    |                                                                                                               |  |

|                    | lıL    | Input Leakage Current <sup>(2,3)</sup>                           |                                                                                                                                                                                                                                                  |   |    |    |                                                                                                               |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(4)</sup>                              | -1                                                                                                                                                                                                                                               | _ | +1 | μА | Vss ≤ VPIN ≤ VDD,<br>pin at high-impedance                                                                    |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                          | -1                                                                                                                                                                                                                                               | _ | +1 | μА | $Vss \leq VPIN \leq VDD, \\ pin at high-impedance, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C$                 |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                          | -1                                                                                                                                                                                                                                               | _ | +1 | μА | Analog pins shared with external reference pins, -40°C ≤ TA ≤ +85°C                                           |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                          | -1                                                                                                                                                                                                                                               | - | +1 | μА | Vss ≤ VPIN ≤ VDD,<br>pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                            |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(4)</sup>                          | -1                                                                                                                                                                                                                                               | - | +1 | μА | Analog pins shared with external reference pins, $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |  |

| DI55               |        | MCLR                                                             | -5                                                                                                                                                                                                                                               | _ | +5 | μΑ | $Vss \leq VPIN \leq VDD$                                                                                      |  |