Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

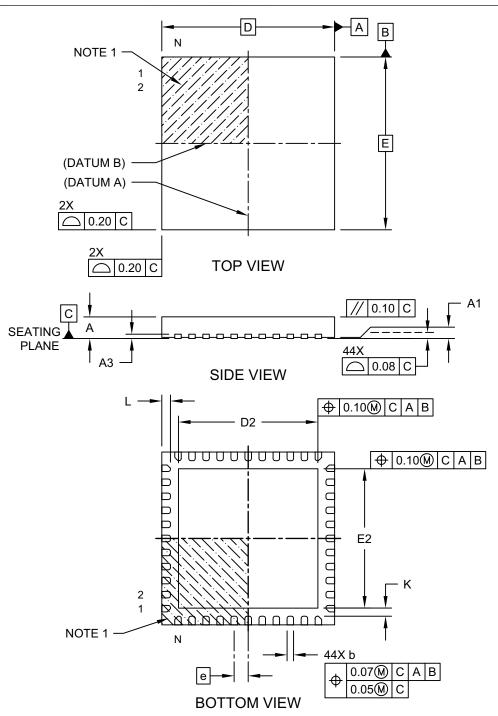

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs502t-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Communication Interfaces**

- Two UART modules (15 Mbps):

- Supports LIN/J2602 protocols and IrDA®

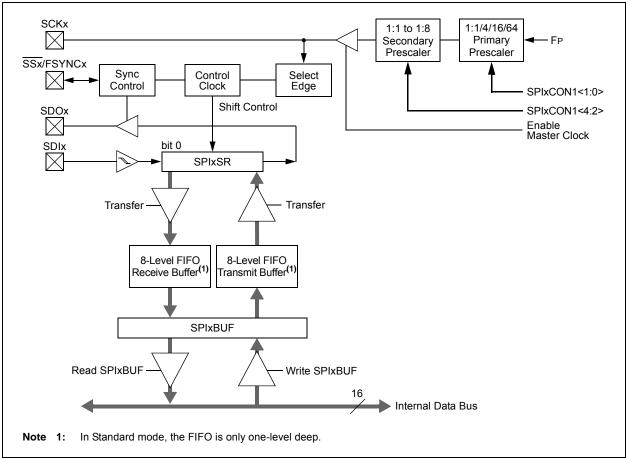

- Two 4-Wire SPI modules (15 Mbps)

- Two I<sup>2</sup>C modules (up to 1 Mbaud) with SMBus Support

# Input/Output

- Constant-Current Source (10 µA nominal)

- Sink/Source up to 12mA/15mA, respectively; Pin-Specific for Standard VOH/VOL

- 5V Tolerant Pins

- · Selectable, Open-Drain Pull-ups and Pull-Downs

- External Interrupts on All I/O Pins

- Peripheral Pin Select (PPS) to allow Function Remap with Six Virtual I/Os

# **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1, -40°C to +125°C)

- Class B Safety Library, IEC 60730

- The 6x6x0.5 mm UQFN Package is Designed and Optimized to ease IPC9592B 2nd Level Temperature Cycle Qualification

## **Debugger Development Support**

- In-Circuit and In-Application Programming

- Five Program and Three Complex Data Breakpoints

- IEEE 1149.2 Compatible (JTAG) Boundary Scan

- Trace and Run-Time Watch

|                  |      | Bytes             |             | (GPIO)                |                       | Rei           | napj           | pable | Peri | phera              | als                                |                 |     |               | ·Bit<br>DC   |     | r                 |            | Source               |              |

|------------------|------|-------------------|-------------|-----------------------|-----------------------|---------------|----------------|-------|------|--------------------|------------------------------------|-----------------|-----|---------------|--------------|-----|-------------------|------------|----------------------|--------------|

| Device           | Pins | Program Memory By | RAM (Bytes) | General Purpose I/O ( | Timers <sup>(1)</sup> | Input Capture | Output Compare | UART  | SPI  | PWM <sup>(2)</sup> | External Interrupts <sup>(3)</sup> | Reference Clock | l²C | Analog Inputs | S&H Circuits | V9d | Analog Comparator | DAC Output | Constant-Current Sou | Packages     |

| dsPIC33EP16GS502 | 28   | 16K               | 2K          | 21                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 12            | 5            | 2   | 4                 | 1          | 1                    | SOIC,        |

| dsPIC33EP32GS502 | 28   | 32K               | 4K          | 21                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 12            | 5            | 2   | 4                 | 1          | 1                    | QFN-S,       |

| dsPIC33EP64GS502 | 28   | 64K               | 8K          | 21                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 12            | 5            | 2   | 4                 | 1          | 1                    | UQFN         |

| dsPIC33EP16GS504 | 44   | 16K               | 2K          | 35                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 19            | 5            | 2   | 4                 | 1          | 1                    |              |

| dsPIC33EP32GS504 | 44   | 32K               | 4K          | 35                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 19            | 5            | 2   | 4                 | 1          | 1                    | QFN,<br>TQFP |

| dsPIC33EP64GS504 | 44   | 64K               | 8K          | 35                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 19            | 5            | 2   | 4                 | 1          | 1                    | i Qi i       |

| dsPIC33EP16GS505 | 48   | 16K               | 2K          | 35                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 19            | 5            | 2   | 4                 | 1          | 1                    |              |

| dsPIC33EP32GS505 | 48   | 32K               | 4K          | 35                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 19            | 5            | 2   | 4                 | 1          | 1                    | TQFP         |

| dsPIC33EP64GS505 | 48   | 64K               | 8K          | 35                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 3                                  | 1               | 2   | 19            | 5            | 2   | 4                 | 1          | 1                    |              |

| dsPIC33EP16GS506 | 64   | 16K               | 2K          | 53                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 4                                  | 1               | 2   | 22            | 5            | 2   | 4                 | 2          | 1                    |              |

| dsPIC33EP32GS506 | 64   | 32K               | 4K          | 53                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 4                                  | 1               | 2   | 22            | 5            | 2   | 4                 | 2          | 1                    | TQFP         |

| dsPIC33EP64GS506 | 64   | 64K               | 8K          | 53                    | 5                     | 4             | 4              | 2     | 2    | 5x2                | 4                                  | 1               | 2   | 22            | 5            | 2   | 4                 | 2          | 1                    |              |

Note 1: The external clock for Timer1, Timer2 and Timer3 is remappable.

2: PWM4 and PWM5 are remappable on all devices except the 64-pin devices.

3: External interrupts, INT0 and INT4, are not remappable.

# 5.4 Dual Partition Flash Configuration

For dsPIC33EP64GS50X devices operating in Dual Partition Flash Program Memory modes, the Inactive Partition can be erased and programmed without stalling the processor. The same programming algorithms are used for programming and erasing the Flash in the Inactive Partition, as described in **Section 5.2 "RTSP Operation"**. On top of the page erase option, the entire Flash memory of the Inactive Partition can be erased by configuring the NVMOP<3:0> bits in the NVMCON register.

Note 1: The application software to be loaded into the Inactive Partition will have the address of the Active Partition. The bootloader firmware will need to offset the address by 0x400000 in order to write to the Inactive Partition.

## 5.4.1 FLASH PARTITION SWAPPING

The Boot Sequence Number is used for determining the Active Partition at start-up and is encoded within the FBTSEQ Configuration register bits. Unlike most Configuration registers, which only utilize the lower 16 bits of the program memory, FBTSEQ is a 24-bit Configuration Word. The Boot Sequence Number (BSEQ) is a 12-bit value and is stored in FBTSEQ twice. The true value is stored in bits, FBTSEQ<11:0>, and its complement is stored in bits, FBTSEQ<23:12>. At device Reset, the sequence numbers are read and the partition with the lowest sequence number becomes the Active Partition. If one of the Boot Sequence Numbers is invalid, the device will select the partition with the valid Boot Sequence Number, or default to Partition 1 if both sequence numbers are invalid. See Section 23.0 "Special Features" for more information.

The BOOTSWP instruction provides an alternative means of swapping the Active and Inactive Partitions (soft swap) without the need for a device Reset. The BOOTSWP must always be followed by a GOTO instruction. The BOOTSWP instruction swaps the Active and Inactive Partitions, and the PC vectors to the location specified by the GOTO instruction in the newly Active Partition.

It is important to note that interrupts should temporarily be disabled while performing the soft swap sequence and that after the partition swap, all peripherals and interrupts which were enabled remain enabled. Additionally, the RAM and stack will maintain state after the switch. As a result, it is recommended that applications using soft swaps jump to a routine that will reinitialize the device in order to ensure the firmware runs as expected. The Configuration registers will have no effect during a soft swap. For robustness of operation, in order to execute the BOOTSWP instruction, it is necessary to execute the NVM unlocking sequence as follows:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Execute the BOOTSWP instruction.

If the unlocking sequence is not performed, the BOOTSWP instruction will be executed as a forced NOP and a GOTO instruction, following the BOOTSWP instruction, will be executed, causing the PC to jump to that location in the current operating partition.

The SFTSWP and P2ACTIV bits in the NVMCON register are used to determine a successful swap of the Active and Inactive Partitions, as well as which partition is active. After the BOOTSWP and GOTO instructions, the SFTSWP bit should be polled to verify the partition swap has occurred and then cleared for the next panel swap event.

## 5.4.2 DUAL PARTITION MODES

While operating in Dual Partition mode, dsPIC33EP64GS50X family devices have the option for both partitions to have their own defined security segments, as shown in Figure 23-4. Alternatively, the device can operate in Protected Dual Partition mode, where Partition 1 becomes permanently erase/write-protected. Protected Dual Partition mode allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1.

dsPIC33EP64GS50X family devices can also operate in Privileged Dual Partition mode, where additional security protections are implemented to allow for protection of intellectual property when multiple parties have software within the device. In Privileged Dual Partition mode, both partitions place additional restrictions on the BSLIM register. These prevent changes to the size of the Boot Segment and General Segment, ensuring that neither segment will be altered.

# 5.5 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 5.5.1 KEY RESOURCES

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0            | U-0 | U-0              | U-0  | U-0          | U-0              | U-0      | U-0   |

|----------------|-----|------------------|------|--------------|------------------|----------|-------|

| —              | _   | —                | _    | —            | —                | —        | _     |

| bit 15         |     | · · ·            |      |              | •                |          | bit 8 |

|                |     |                  |      |              |                  |          |       |

| W-0            | W-0 | W-0              | W-0  | W-0          | W-0              | W-0      | W-0   |

|                |     |                  | NVMK | EY<7:0>      |                  |          |       |

| bit 7          |     |                  |      |              |                  |          | bit 0 |

|                |     |                  |      |              |                  |          |       |

| Legend:        |     |                  |      |              |                  |          |       |

| R = Readable b | oit | W = Writable bit | t    | U = Unimpler | mented bit, read | l as '0' |       |

|                |     |                  |      |              |                  |          |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** NVM Key Register bits (write-only)

### REGISTER 5-5: NVMSRCADR: NVM SOURCE DATA ADDRESS REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|-----------------|-------|------------------|--------|-----------------------------------------|-----------------|----------|-------|

|                 |       |                  | NVMSRC | CADR<15:8>                              |                 |          |       |

| bit 15          |       |                  |        |                                         |                 |          | bit 8 |

|                 |       |                  |        |                                         |                 |          |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|                 |       |                  | NVMSR  | CADR<7:0>                               |                 |          |       |

| bit 7           |       |                  |        |                                         |                 |          | bit 0 |

|                 |       |                  |        |                                         |                 |          |       |

| Legend:         |       |                  |        |                                         |                 |          |       |

| R = Readable    | bit   | W = Writable b   | it     | U = Unimplen                            | nented bit, rea | d as '0' |       |

| -n = Value at P | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |                 |          |       |

### bit 15-0 NVMSRCADR<15:0>: NVM Source Data Address bits

The RAM address of the data to be programmed into Flash when the NVMOP<3:0> bits are set to row programming.

# 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0          | U-0                | U-0              | U-0              | U-0              | U-0             | R/W-0 |

|--------------|--------------|--------------------|------------------|------------------|------------------|-----------------|-------|

| _            | —            | —                  | —                | _                | —                | —               | NAE   |

| bit 15       |              |                    |                  |                  |                  |                 | bit 8 |

|              |              |                    |                  |                  |                  |                 |       |

| U-0          | U-0          | U-0                | R/W-0            | U-0              | U-0              | U-0             | R/W-0 |

| —            | —            |                    | DOOVR            | —                |                  |                 | APLL  |

| bit 7        |              |                    |                  |                  |                  |                 | bit 0 |

|              |              |                    |                  |                  |                  |                 |       |

| Legend:      |              |                    |                  |                  |                  |                 |       |

| R = Readal   | ole bit      | W = Writable       | bit              | U = Unimple      | mented bit, read | as '0'          |       |

| -n = Value a | at POR       | '1' = Bit is se    | t                | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|              |              |                    |                  |                  |                  |                 |       |

| bit 15-9     | Unimplemer   | nted: Read as      | '0'              |                  |                  |                 |       |

| bit 8        | NAE: NVM A   | ddress Error S     | Soft Trap Status | s bit            |                  |                 |       |

|              |              |                    | trap has occur   |                  |                  |                 |       |

|              |              |                    | trap has not o   | ccurred          |                  |                 |       |

| bit 7-5      | Unimplemer   | nted: Read as      | '0'              |                  |                  |                 |       |

| bit 4        | DOOVR: DO    | Stack Overflov     | v Soft Trap Sta  | tus bit          |                  |                 |       |

|              | 1 = DO stack | overflow soft t    | rap has occurre  | ed               |                  |                 |       |

|              | 0 = DO stack | overflow soft t    | rap has not oc   | curred           |                  |                 |       |

| bit 3-1      | Unimplemer   | nted: Read as      | '0'              |                  |                  |                 |       |

| bit 0        | APLL: Auxili | ary PLL Loss o     | of Lock Soft Tra | ap Status bit    |                  |                 |       |

|              | 1 = APLL loc | k soft trap has    | occurred         |                  |                  |                 |       |

|              |              | le a aft trans has | wet easy word    |                  |                  |                 |       |

0 = APLL lock soft trap has not occurred

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0          | U-0          | U-0              | U-0            | U-0                                | U-0  | U-0             | U-0   |  |  |  |

|--------------|--------------|------------------|----------------|------------------------------------|------|-----------------|-------|--|--|--|

| _            | —            | —                | —              | —                                  | —    | —               | —     |  |  |  |

| bit 15       |              |                  |                |                                    |      |                 | bit 8 |  |  |  |

|              |              |                  |                |                                    |      |                 |       |  |  |  |

| U-0          | U-0          | U-0              | U-0            | U-0                                | U-0  | U-0             | R/W-0 |  |  |  |

| _            | —            | —                | —              | —                                  | —    | —               | SGHT  |  |  |  |

| bit 7        |              | •                |                |                                    |      | •               | bit 0 |  |  |  |

|              |              |                  |                |                                    |      |                 |       |  |  |  |

| Legend:      |              |                  |                |                                    |      |                 |       |  |  |  |

| R = Readab   | le bit       | W = Writable     | bit            | U = Unimplemented bit, read as '0' |      |                 |       |  |  |  |

| -n = Value a | t POR        | '1' = Bit is set | t              | '0' = Bit is cle                   | ared | x = Bit is unki | nown  |  |  |  |

|              |              |                  |                |                                    |      |                 |       |  |  |  |

| bit 15-1     | Unimplemen   | ted: Read as     | '0'            |                                    |      |                 |       |  |  |  |

| bit 0        | SGHT: Softwa | are Generated    | Hard Trap Sta  | tus bit                            |      |                 |       |  |  |  |

|              | 1 = Software | generated har    | d trap has occ | urred                              |      |                 |       |  |  |  |

|              | 0 = Software | generated har    | d trap has not | occurred                           |      |                 |       |  |  |  |

|              |              |                  |                |                                    |      |                 |       |  |  |  |

|              |              |                  |                |                                    |      |                 |       |  |  |  |

# 8.5 Oscillator Control Registers

# REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|--------|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | IOLOCK | LOCK | —   | CF <sup>(3)</sup> | —   | —   | OSWEN |

| bit 7   |        |      |     |                   |     |     | bit 0 |

| Legend:           | y = Value set from Cor | nfiguration bits on POR | ation bits on POR  |  |  |  |

|-------------------|------------------------|-------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit   | t, read as '0'     |  |  |  |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared    | x = Bit is unknown |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | <b>COSC&lt;2:0&gt;:</b> Current Oscillator Selection bits (read-only)<br>111 = Fast RC Oscillator (FRC) with Divide-by-n<br>110 = Fast RC Oscillator (FRC) with Divide-by-16                  |

|           | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved                                                                                                                                        |

|           | 011 = Primary Oscillator (XT, HS, EC) with PLL<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                    |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                                                       |

|           | 111 = Fast RC Oscillator (FRC) with Divide-by-n                                                                                                                                               |

|           | 110 = Fast RC Oscillator (FRC) with Divide-by-16<br>101 = Low-Power RC Oscillator (LPRC)                                                                                                      |

|           | 100 = Reserved                                                                                                                                                                                |

|           | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                                                                                                                |

|           | 010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)                                                                                     |

|           | 000 = Fast RC Oscillator (FRC)                                                                                                                                                                |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                |

|           | 1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and<br>PLL configurations may be modified                                                      |

|           | <ul> <li>0 = Clock and PLL selections are not locked, configurations may be modified</li> </ul>                                                                                               |

| bit 6     | IOLOCK: I/O Lock Enable bit                                                                                                                                                                   |

|           | 1 = I/O lock is active                                                                                                                                                                        |

| hit E     | 0 = I/O lock is not active                                                                                                                                                                    |

| bit 5     | <b>LOCK:</b> PLL Lock Status bit (read-only)<br>1 = Indicates that PLL is in lock or PLL start-up timer is satisfied                                                                          |

|           | 0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled                                                                                                       |

| Note 1:   | Writes to this register require an unlock sequence.                                                                                                                                           |

| 2:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.                                                                                         |

|           | This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.                     |

| 3:        | This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an                                                                                |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 CF: Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected a clock failure

- 0 = FSCM has not detected a clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to the selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

# 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

### 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

## 9.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 9.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

|                 | U-0                                                                                                                                              | U-0                                                                                                                                                               | R/W-0                                                                | R/W-0             | R/W-0            | R/W-0              | R/W-0  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|------------------|--------------------|--------|--|

| _               | —                                                                                                                                                | —                                                                                                                                                                 | PWM5MD                                                               | PWM4MD            | PWM3MD           | PWM2MD             | PWM1MD |  |

| bit 15          |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    | bit 8  |  |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |

| U-0             | U-0                                                                                                                                              | U-0                                                                                                                                                               | U-0                                                                  | U-0               | U-0              | U-0                | U-0    |  |

|                 |                                                                                                                                                  | _                                                                                                                                                                 | _                                                                    | —                 |                  |                    |        |  |

| bit 7           |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    | bit C  |  |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |

| Legend:         |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |

| R = Readabl     | le bit                                                                                                                                           | W = Writable I                                                                                                                                                    | oit                                                                  | U = Unimplem      | nented bit, read | l as '0'           |        |  |

| -n = Value at   | t POR                                                                                                                                            | '1' = Bit is set                                                                                                                                                  |                                                                      | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |

| bit 15-13       | Unimplement                                                                                                                                      | ted: Read as '0                                                                                                                                                   | )'                                                                   |                   |                  |                    |        |  |

| bit 12          | PWM5MD: P\                                                                                                                                       | WM5 Module D                                                                                                                                                      | isable bit                                                           |                   |                  |                    |        |  |

|                 |                                                                                                                                                  | odule is disable                                                                                                                                                  | -                                                                    |                   |                  |                    |        |  |

|                 |                                                                                                                                                  | odule is enable                                                                                                                                                   | -                                                                    |                   |                  |                    |        |  |

| bit 11          | PWM4MD: P\                                                                                                                                       | VM4 Module D                                                                                                                                                      | isable bit                                                           |                   |                  |                    |        |  |

|                 |                                                                                                                                                  |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |

|                 |                                                                                                                                                  | odule is disable                                                                                                                                                  | -                                                                    |                   |                  |                    |        |  |

|                 | 0 = PWM4 mo                                                                                                                                      | odule is enable                                                                                                                                                   | d                                                                    |                   |                  |                    |        |  |

|                 | 0 = PWM4 mo<br><b>PWM3MD:</b> P\                                                                                                                 | odule is enable<br>VM3 Module D                                                                                                                                   | d<br>isable bit                                                      |                   |                  |                    |        |  |

|                 | 0 = PWM4 mo<br>PWM3MD: P\<br>1 = PWM3 mo                                                                                                         | odule is enable                                                                                                                                                   | d<br>isable bit<br>d                                                 |                   |                  |                    |        |  |

| bit 10<br>bit 9 | 0 = PWM4 mc<br>PWM3MD: P\<br>1 = PWM3 mc<br>0 = PWM3 mc                                                                                          | odule is enable<br>WM3 Module D<br>odule is disable                                                                                                               | d<br>isable bit<br>d                                                 |                   |                  |                    |        |  |

| bit 10          | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV                                                            | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable                                                                                            | d<br>isable bit<br>d<br>d<br>isable bit                              |                   |                  |                    |        |  |

| bit 10          | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV<br>1 = PWM2 mc                                             | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D                                                                            | d<br>isable bit<br>d<br>d<br>isable bit<br>d                         |                   |                  |                    |        |  |

| bit 10          | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV<br>1 = PWM2 mc<br>0 = PWM2 mc                              | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable                                                        | d<br>isable bit<br>d<br>d<br>isable bit<br>d<br>d                    |                   |                  |                    |        |  |

| bit 10<br>bit 9 | 0 = PWM4 mo<br>PWM3MD: PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br>PWM2MD: PV<br>1 = PWM2 mo<br>0 = PWM2 mo<br>0 = PWM2 mo<br>PWM1MD: PV<br>1 = PWM1 mo  | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable<br>odule is enable<br>WM1 Module D<br>odule is disable | d<br>isable bit<br>d<br>isable bit<br>d<br>d<br>isable bit<br>d      |                   |                  |                    |        |  |

| bit 10<br>bit 9 | 0 = PWM4 mo<br>PWM3MD: PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br>PWM2MD: PV<br>1 = PWM2 mo<br>0 = PWM2 mo<br>0 = PWM1 mo<br>0 = PWM1 mo<br>0 = PWM1 mo | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable<br>odule is enable<br>WM1 Module D                     | d<br>isable bit<br>d<br>isable bit<br>d<br>d<br>isable bit<br>d<br>d |                   |                  |                    |        |  |

### REGISTER 10-28: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| —         —         RP49R5         RP49R4         RP49R3         RP49R2         RP49R1         RP49R1           bit 15         U-0         U-0         R/W-0         R/W-0 <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |                            |                |                                         |              |                  |          |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|----------------|-----------------------------------------|--------------|------------------|----------|--------|

| bit 15U-0U-0R/W-0R/W-0R/W-0R/W-0R/W-0———RP48R5RP48R4RP48R3RP48R2RP48R1RP4bit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15-14Unimplemented: Read as '0'<br>bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits<br>(see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                | U-0                        | R/W-0          | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

| U-0U-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                  | —                          | RP49R5         | RP49R4                                  | RP49R3       | RP49R2           | RP49R1   | RP49R0 |

| —       —       RP48R5       RP48R4       RP48R3       RP48R2       RP48R1       RP4         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15                             |                            |                |                                         |              |                  |          | bit 8  |

| —       —       RP48R5       RP48R4       RP48R3       RP48R2       RP48R1       RP4         bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |                            |                |                                         |              |                  |          |        |

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                | U-0                        | R/W-0          | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'         bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                                  | —                          | RP48R5         | RP48R4                                  | RP48R3       | RP48R2           | RP48R1   | RP48R0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'         bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 7                              |                            | •              | -                                       |              |                  |          | bit 0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'         bit 13-8       RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |                            |                |                                         |              |                  |          |        |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       Image: Second se | Legend:                            |                            |                |                                         |              |                  |          |        |

| bit 15-14Unimplemented: Read as '0'bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits<br>(see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R = Readable                       | bit                        | W = Writable   | bit                                     | U = Unimpler | nented bit, read | l as '0' |        |

| bit 13-8 <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n = Value at POR '1' = Bit is set |                            |                | '0' = Bit is cleared x = Bit is unknown |              |                  | nown     |        |

| bit 13-8 <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |                            |                |                                         |              |                  |          |        |

| (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15-14                          | Unimplemen                 | ted: Read as ' | 0'                                      |              |                  |          |        |