Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs504-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

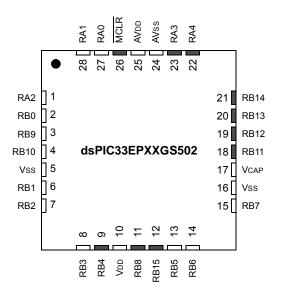

## **Pin Diagrams**

28-Pin SOIC

| MCLR | 1  | $\bigcirc$       | 28 | AVdd |

|------|----|------------------|----|------|

| RA0  | 2  |                  | 27 | AVss |

| RA1  | 3  |                  | 26 | RA3  |

| RA2  | 4  | ٩                | 25 | RA4  |

| RB0  | 5  | sPI              | 24 | RB14 |

| RB9  | 6  | ទួ               | 23 | RB13 |

| RB10 | 7  | Ĕ                | 22 | RB12 |

| Vss  | 8  | dsPIC33EPXXGS502 | 21 | RB11 |

| RB1  | 9  | GS               | 20 | VCAP |

| RB2  | 10 | 502              | 19 | Vss  |

| RB3  | 11 |                  | 18 | RB7  |

| RB4  | 12 |                  | 17 | RB6  |

| Vdd  | 13 |                  | 16 | RB5  |

| RB8  | 14 |                  | 15 | RB15 |

|      |    |                  |    |      |

| Pin | Pin Function                              | Pin | Pin Function                      |

|-----|-------------------------------------------|-----|-----------------------------------|

| 1   | MCLR                                      | 15  | PGEC3/SCL2/ <b>RP47</b> /RB15     |

| 2   | AN0/PGA1P1/CMP1A/RA0                      | 16  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5 |

| 3   | AN1/PGA1P2/PGA2P1/CMP1B/RA1               | 17  | PGED1/TDI/AN20/SCL1/RP38/RB6      |

| 4   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         | 18  | PGEC1/AN21/SDA1/RP39/RB7          |

| 5   | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           | 19  | Vss                               |

| 6   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            | 20  | VCAP                              |

| 7   | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           | 21  | TMS/PWM3H/ <b>RP43</b> /RB11      |

| 8   | Vss                                       | 22  | TCK/PWM3L/RP44/RB12               |

| 9   | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  | 23  | PWM2H/ <b>RP45</b> /RB13          |

| 10  | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 | 24  | PWM2L/ <b>RP46</b> /RB14          |

| 11  | PGED2/AN18/DACOUT1/INT0/RP35/RB3          | 25  | PWM1H/RA4                         |

| 12  | PGEC2/ADTRG31/EXTREF1/RP36/RB4            | 26  | PWM1L/RA3                         |

| 13  | VDD                                       | 27  | AVss                              |

| 14  | PGED3/SDA2/FLT31/RP40/RB8                 | 28  | AVDD                              |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

## **Pin Diagrams (Continued)**

#### 28-Pin QFN-S, UQFN

| Pin | Pin Function                              |    | Pin Function                 |

|-----|-------------------------------------------|----|------------------------------|

| 1   | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         | 15 | PGEC1/AN21/SDA1/RP39/RB7     |

| 2   | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           | 16 | Vss                          |

| 3   | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            | 17 | VCAP                         |

| 4   | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           | 18 | TMS/PWM3H/ <b>RP43</b> /RB11 |

| 5   | Vss                                       | 19 | TCK/PWM3L/RP44/RB12          |

| 6   | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  | 20 | PWM2H/ <b>RP45</b> /RB13     |

| 7   | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 | 21 | PWM2L/ <b>RP46</b> /RB14     |

| 8   | PGED2/AN18/DACOUT1/INT0/ <b>RP35</b> /RB3 | 22 | PWM1H/RA4                    |

| 9   | PGEC2/ADTRG31/EXTREF1/RP36/RB4            | 23 | PWM1L/RA3                    |

| 10  | Vdd                                       | 24 | AVss                         |

| 11  | PGED3/SDA2/FLT31/RP40/RB8                 | 25 | AVdd                         |

| 12  | PGEC3/SCL2/ <b>RP47</b> /RB15             | 26 | MCLR                         |

| 13  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         | 27 | AN0/PGA1P1/CMP1A/RA0         |

| 14  | PGED1/TDI/AN20/SCL1/ <b>RP38</b> /RB6     | 28 | AN1/PGA1P2/PGA2P1/CMP1B/RA1  |

Legend: Shaded pins are up to 5 VDC tolerant. RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for Digital Signal Processing (DSP). The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXGS50X devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EPXXGS50X devices include two Alternate Working register sets which consist of W0 through W14. The Alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The Alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register. The Alternate Working registers can also be accessed manually by using the CTXTSWP instruction. The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current and most recent, manually selected Working register sets.

## 3.2 Instruction Set

The instruction set for dsPIC33EPXXGS50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The base Data Space can be addressed as up to 4K words or 8 Kbytes, and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Refer to "**Data Memory**" (DS70595) in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on PSV and table accesses.

On dsPIC33EPXXGS50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- · Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

#### 4.7.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

## 4.8 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.8.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these situations are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume<br>word-sized data (LSb of every EA is<br>always clear). The XB value is scaled<br>accordingly to generate compatible (byte) |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | addresses.                                                                                                                                                           |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed        |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | Addressing can be enabled simultaneously  |  |  |  |  |  |  |

|       | using the same W register, but Bit-       |  |  |  |  |  |  |

|       | Reversed Addressing operation will always |  |  |  |  |  |  |

|       | take precedence for data writes when      |  |  |  |  |  |  |

|       | enabled.                                  |  |  |  |  |  |  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0            | U-0 | U-0                                                 | U-0  | U-0     | U-0 | U-0 | U-0   |

|----------------|-----|-----------------------------------------------------|------|---------|-----|-----|-------|

| —              | _   | —                                                   | _    | —       | —   | —   | _     |

| bit 15         |     | · · ·                                               |      |         | •   |     | bit 8 |

|                |     |                                                     |      |         |     |     |       |

| W-0            | W-0 | W-0                                                 | W-0  | W-0     | W-0 | W-0 | W-0   |

|                |     |                                                     | NVMK | EY<7:0> |     |     |       |

| bit 7          |     |                                                     |      |         |     |     | bit 0 |

|                |     |                                                     |      |         |     |     |       |

| Legend:        |     |                                                     |      |         |     |     |       |

| R = Readable b | oit | W = Writable bit U = Unimplemented bit, read as '0' |      |         |     |     |       |

|                |     |                                                     |      |         |     |     |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** NVM Key Register bits (write-only)

#### REGISTER 5-5: NVMSRCADR: NVM SOURCE DATA ADDRESS REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|--------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | NVMSRC | CADR<15:8>                              |       |       |       |

| bit 15          |       |                  |        |                                         |       |       | bit 8 |

|                 |       |                  |        |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | NVMSR  | CADR<7:0>                               |       |       |       |

| bit 7           |       |                  |        |                                         |       |       | bit 0 |

|                 |       |                  |        |                                         |       |       |       |

| Legend:         |       |                  |        |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | it     | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |       |       |       |

#### bit 15-0 NVMSRCADR<15:0>: NVM Source Data Address bits

The RAM address of the data to be programmed into Flash when the NVMOP<3:0> bits are set to row programming.

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 CF: Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected a clock failure

- 0 = FSCM has not detected a clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to the selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

## 10.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features, while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 10.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions.

#### 10.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. One example includes  $I^2C$  modules. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 10.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## 15.0 HIGH-SPEED PWM

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM Module" (DS70000323) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The high-speed PWM module on dsPIC33EPXXGS50X devices supports a wide variety of PWM modes and output formats. This PWM module is ideal for power conversion applications, such as:

- AC/DC Converters

- DC/DC Converters

- Power Factor Correction

- Uninterruptible Power Supply (UPS)

- Inverters

- Battery Chargers

- Digital Lighting

#### 15.1 Features Overview

The high-speed PWM module incorporates the following features:

- Five PWMx Generators with Two Outputs per Generator

- · Two Master Time Base Modules

- Individual Time Base and Duty Cycle for Each PWM Output

- Duty Cycle, Dead Time, Phase Shift and a Frequency Resolution of 1.04 ns

- Independent Fault and Current-Limit Inputs

- Redundant Output

- True Independent Output

- Center-Aligned PWM mode

- Output Override Control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Dual Trigger from PWMx to Analog-to-Digital Converter (ADC)

- PWMxL and PWMxH Output Pin Swapping

- Independent PWMx Frequency, Duty Cycle and Phase-Shift Changes

- Enhanced Leading-Edge Blanking (LEB) Functionality

- PWM Capture Functionality

**Note:** Duty cycle, dead time, phase shift and frequency resolution is 8.32 ns in Center-Aligned PWM mode.

Figure 15-1 conceptualizes the PWM module in a simplified block diagram. Figure 15-2 illustrates how the module hardware is partitioned for each PWMx output pair for the Complementary PWM mode.

The PWM module contains five PWM generators. The module has up to 10 PWMx output pins: PWM1H/ PWM1L through PWM5H/PWM5L. For complementary outputs, these 10 I/O pins are grouped into high/low pairs.

#### 15.2 Feature Description

The PWM module is designed for applications that require:

- High resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode and Push-Pull mode outputs

- · The ability to create multiphase PWM outputs

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable.

Multiphase PWM is often used to improve DC/DC converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC converters are often operated in parallel, but phase shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu$ s but an array of four PWM channels, staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50% and the power flow is controlled by varying the relative phase shift between the two PWM generators.

x = Bit is unknown

#### **REGISTER 15-15:** PHASEX: PWMx PRIMARY PHASE-SHIFT REGISTER (x = 1 to 5)<sup>(1,2)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PHASE | Ex<15:8>     |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PHAS  | Ex<7:0>      |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit |       | U = Unimplen | nented bit. read | l as '0' |       |

bit 15-0 **PHASEx<15:0>:** PWMx Phase-Shift Value or Independent Time Base Period for the PWMx Generator bits

**Note 1:** If PWMCONx<9> = 0, the following applies based on the mode of operation:

'1' = Bit is set

- Complementary, Redundant and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Phase-shift value for PWMxH only

- When the PHASEx/SPHASEx registers provide the phase shift with respect to the master time base; therefore, the valid range is 0x0000 through period

'0' = Bit is cleared

- **2:** If PWMCONx<9> = 1, the following applies based on the mode of operation:

- Complementary, Redundant, and Push-Pull Output mode (IOCONx<11:10> = 00, 01 or 10); PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

- True Independent Output mode (IOCONx<11:10> = 11); PHASEx<15:0> = Independent time base period value for PWMxH only

- When the PHASEx/SPHASEx registers provide the local period, the valid range is 0x0000 through 0xFFF8

-n = Value at POR

#### REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5)

|              | (X = 1         | 10 5)                                                                                                                                                                                           |                    |                                        |                   |                 |                  |  |

|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------|-------------------|-----------------|------------------|--|

| R/W-0        | R/W-0          | R/W-0                                                                                                                                                                                           | R/W-0              | R/W-0                                  | R/W-0             | U-0             | U-0              |  |

| PHR          | PHF            | PLR                                                                                                                                                                                             | PLF                | FLTLEBEN                               | CLLEBEN           | —               |                  |  |

| bit 15       |                |                                                                                                                                                                                                 |                    |                                        |                   |                 | bit 8            |  |

|              |                |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |

| U-0          | U-0            | R/W-0                                                                                                                                                                                           | R/W-0              | R/W-0                                  | R/W-0             | R/W-0           | R/W-0            |  |

|              |                | BCH <sup>(1)</sup>                                                                                                                                                                              | BCL <sup>(1)</sup> | BPHH                                   | BPHL              | BPLH            | BPLL             |  |

| bit 7        |                |                                                                                                                                                                                                 |                    |                                        |                   |                 | bit 0            |  |

| Legend:      |                |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |

| R = Readat   | ole bit        | W = Writable b                                                                                                                                                                                  | oit                | U = Unimpler                           | nented bit, read  | as '0'          |                  |  |

| -n = Value a | at POR         | '1' = Bit is set                                                                                                                                                                                |                    | '0' = Bit is clea                      |                   | x = Bit is unkr | nown             |  |

| bit 15       |                | H Rising Edge T                                                                                                                                                                                 | riggor Epoble      | 2 bit                                  |                   |                 |                  |  |

| bit 15       | 1 = Rising edg | ge of PWMxH v                                                                                                                                                                                   | vill trigger the   | Leading-Edge E<br>ling edge of PW      | •                 | PL              |                  |  |

| bit 14       | -              | I Falling Edge 1                                                                                                                                                                                | -                  |                                        |                   |                 |                  |  |

|              |                |                                                                                                                                                                                                 |                    | e Leading-Edge                         | Blanking counte   | er              |                  |  |

|              | -              |                                                                                                                                                                                                 | -                  | lling edge of PW                       | /MxH              |                 |                  |  |

| bit 13       |                | Rising Edge T                                                                                                                                                                                   |                    |                                        |                   |                 |                  |  |

|              |                |                                                                                                                                                                                                 |                    | Leading-Edge E<br>sing edge of PW      |                   | r               |                  |  |

| bit 12       | -              | Falling Edge T                                                                                                                                                                                  | -                  |                                        |                   |                 |                  |  |

|              | 1 = Falling ed | ge of PWMxL v                                                                                                                                                                                   | vill trigger the   | Leading-Edge E<br>lling edge of PW     | •                 | er              |                  |  |

| bit 11       | -              |                                                                                                                                                                                                 | -                  | anking Enable bi                       |                   |                 |                  |  |

|              |                |                                                                                                                                                                                                 |                    | ne selected Faul<br>to the selected F  |                   |                 |                  |  |

| bit 10       | CLLEBEN: C     | urrent-Limit Lea                                                                                                                                                                                | ading-Edge B       | lanking Enable I                       | bit               |                 |                  |  |

|              |                |                                                                                                                                                                                                 |                    | ne selected curre<br>to the selected o |                   | ut              |                  |  |

| bit 9-6      | Unimplemen     | ted: Read as '0                                                                                                                                                                                 | 2                  |                                        |                   |                 |                  |  |

| bit 5        | BCH: Blankin   | g in Selected B                                                                                                                                                                                 | lanking Signa      | al High Enable b                       | it <sup>(1)</sup> |                 |                  |  |

|              |                |                                                                                                                                                                                                 |                    | Fault input signa<br>ng signal is high |                   | lected blanking | g signal is high |  |

| bit 4        | BCL: Blankin   | g in Selected B                                                                                                                                                                                 | lanking Signa      | I Low Enable bit                       | t(1)              |                 |                  |  |

|              |                | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is low</li> <li>0 = No blanking when the selected blanking signal is low</li> </ul> |                    |                                        |                   |                 |                  |  |

| bit 3        | BPHH: Blank    | ing in PWMxH I                                                                                                                                                                                  | High Enable b      | oit                                    |                   |                 |                  |  |

|              |                | nking (of currenting when the PV                                                                                                                                                                |                    | Fault input signa<br>is high           | als) when the P   | WMxH output i   | s high           |  |

| bit 2        | BPHL: Blanki   | ing in PWMxH L                                                                                                                                                                                  | ow Enable b        | it                                     |                   |                 |                  |  |

|              |                | nking (of currenting when the PV                                                                                                                                                                |                    | Fault input signa<br>is low            | als) when the P\  | WMxH output i   | s low            |  |

|              |                |                                                                                                                                                                                                 |                    |                                        |                   |                 |                  |  |

**Note 1:** The blanking signal is selected via the BLANKSEL<3:0> bits in the AUXCONx register.

#### **REGISTER 15-27: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER (x = 1 to 5)**

| R-0              | R-0 | R-0             | R-0  | R-0                          | R-0            | R-0      | R-0   |

|------------------|-----|-----------------|------|------------------------------|----------------|----------|-------|

|                  |     |                 |      | P<12:5> <sup>(1,2,3,4)</sup> |                |          |       |

| bit 15           |     |                 |      |                              |                |          | bit 8 |

|                  |     |                 |      |                              |                |          |       |

| R-0              | R-0 | R-0             | R-0  | R-0                          | U-0            | U-0      | U-0   |

|                  | PW  | MCAP<4:0>(1,2,3 | 8,4) |                              | _              |          |       |

| bit 7            |     |                 |      |                              |                |          | bit 0 |

|                  |     |                 |      |                              |                |          |       |

| Legend:          |     |                 |      |                              |                |          |       |

| R = Readable bit |     | W = Writable bi | t    | II = I Inimplem              | onted hit read | 1 26 '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-3 **PWMCAP<12:0>:** PWMx Primary Time Base Capture Value bits<sup>(1,2,3,4)</sup> The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

#### bit 2-0 Unimplemented: Read as '0'

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

- **3:** The minimum capture resolution is 8.32 ns.

- 4: This feature can be used when the XPRES bit (PWMCONx<1>) is set to '0'.

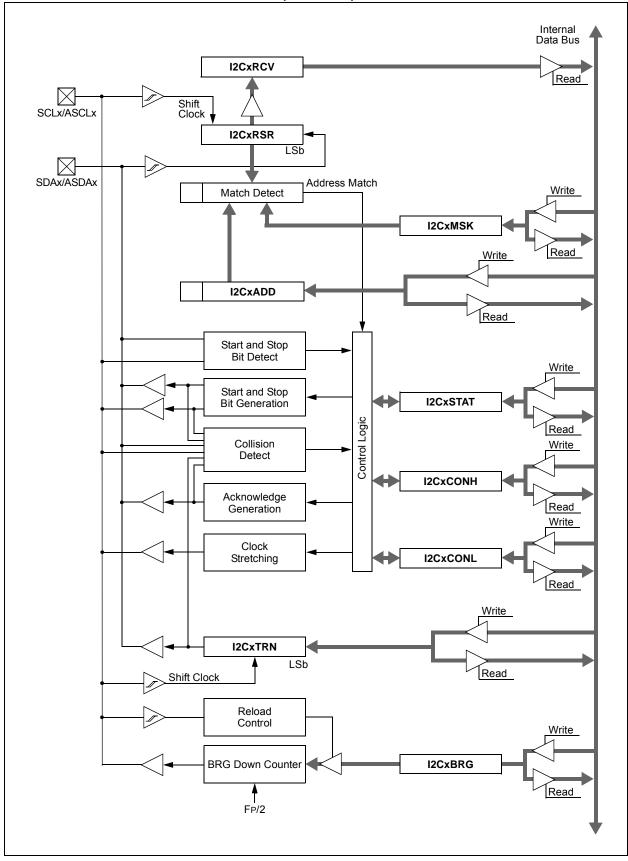

FIGURE 17-1: I2Cx BLOCK DIAGRAM (x = 1 OR 2)

| DC CHARACTERISTICS |                     |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |        |           |  |  |

|--------------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-----------|--|--|

| Parameter<br>No.   | Тур.                | Max. | Units                                                                                                                                                                                                | Conditions |        |           |  |  |

| Idle Current (II   | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                      |            |        |           |  |  |

| DC40d              | 2                   | 4    | mA                                                                                                                                                                                                   | -40°C      |        |           |  |  |

| DC40a              | 2                   | 4    | mA                                                                                                                                                                                                   | +25°C      | - 3.3V | 10 MIPS   |  |  |

| DC40b              | 2                   | 4    | mA                                                                                                                                                                                                   | +85°C      | 5.3V   | TO MIES   |  |  |

| DC40c              | 2                   | 4    | mA                                                                                                                                                                                                   | +125°C     |        |           |  |  |

| DC42d              | 3                   | 6    | mA                                                                                                                                                                                                   | -40°C      |        |           |  |  |

| DC42a              | 3                   | 6    | mA                                                                                                                                                                                                   | +25°C      | - 3.3V | 20 MIPS   |  |  |

| DC42b              | 3                   | 6    | mA                                                                                                                                                                                                   | +85°C      | 5.3V   | 20 Mill 3 |  |  |

| DC42c              | 3                   | 6    | mA                                                                                                                                                                                                   | +125°C     |        |           |  |  |

| DC44d              | 6                   | 12   | mA                                                                                                                                                                                                   | -40°C      |        |           |  |  |

| DC44a              | 6                   | 12   | mA                                                                                                                                                                                                   | +25°C      | - 3.3V | 40 MIPS   |  |  |

| DC44b              | 6                   | 12   | mA                                                                                                                                                                                                   | +85°C      | 5.3V   | 40 MIF 3  |  |  |

| DC44c              | 6                   | 12   | mA                                                                                                                                                                                                   | +125°C     |        |           |  |  |

| DC45d              | 8                   | 15   | mA                                                                                                                                                                                                   | -40°C      |        |           |  |  |

| DC45a              | 8                   | 15   | mA                                                                                                                                                                                                   | +25°C      | - 3.3V | 60 MIPS   |  |  |

| DC45b              | 8                   | 15   | mA                                                                                                                                                                                                   | +85°C      | 3.3V   | OU IVIIPS |  |  |

| DC45c              | 8                   | 15   | mA                                                                                                                                                                                                   | +125°C     | ]      |           |  |  |

| DC46d              | 10                  | 20   | mA                                                                                                                                                                                                   | -40°C      |        |           |  |  |

| DC46a              | 10                  | 20   | mA                                                                                                                                                                                                   | +25°C      | 3.3V   | 70 MIPS   |  |  |

| DC46b              | 10                  | 20   | mA                                                                                                                                                                                                   | +85°C      | ]      |           |  |  |

#### TABLE 26-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                                                                          |

|--------------------|--------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions                                                                                                                                                                               |

| DO10               | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    | _                                                                                                                                                                                                                                                                                   |      | 0.4  | V     | $V_{DD} = 3.3V,$<br>$I_{OL} \le 6 \text{ mA}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C},$<br>$I_{OL} \le 5 \text{ mA}, +85^{\circ}\text{C} < T_{A} \le +125^{\circ}\text{C}$ |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                   | —    | 0.4  | V     | $V_{DD}$ = 3.3V,<br>IOL $\leq$ 12 mA, -40°C $\leq$ TA $\leq$ +85°C,<br>IOL $\leq$ 8 mA, +85°C $<$ TA $\leq$ +125°C                                                                       |

| DO20 Voh           | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                 | _    | _    | V     | IOH ≥ -10 mA, VDD = 3.3V                                                                                                                                                                 |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                                 | _    | _    | V     | IOH ≥ -15 mA, VDD = 3.3V                                                                                                                                                                 |

| DO20A              | Von1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                  | _    | _    |       | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                    |

|                    |        |                                                             | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                  |      |      | V     | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                    |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                              | _    | -    |       | IOH $\ge$ -7 mA, VDD = 3.3V                                                                                                                                                              |

|                    |        | Output High Voltage                                         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                  | _    | _    | V     | $IOH \ge -22 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                    |

|                    |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                  | _    | _    |       | $IOH \ge -18 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                    |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                              | —    | —    |       | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                                            |

#### TABLE 26-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes RA0-RA2, RB0-RB1, RB9-RB10, RC1-RC2, RC9-RC10, RC12 and RD7 pins.

3: Includes all I/O pins that are not 4x driver pins (see **Note 2**).

#### TABLE 26-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                        |  |

|--------------------|--------|--------------------------------------------|-------------------------------------------------------|------|------|-------|------------------------|--|

| Param<br>No.       | Symbol | Characteristic                             | Min. <sup>(2)</sup>                                   | Тур. | Max. | Units | Conditions             |  |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low | 2.65                                                  | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, PGAs and comparators) may have degraded performance.

2: Parameters are for design guidance only and are not tested in manufacturing.

**3:** The VBOR specification is relative to VDD.

### 26.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXGS50X family AC characteristics and timing parameters.

#### TABLE 26-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)               |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial            |  |  |  |  |

|                    | $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                                   |  |  |  |  |

|                    | Operating voltage VDD range as described in <b>Section 26.1 "DC Characteristics</b> ". |  |  |  |  |

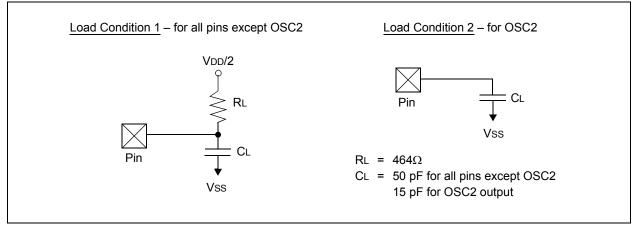

### FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 26-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            |      | _    | 400  | pF    | In I <sup>2</sup> C mode                                            |

## TABLE 26-23:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                             |  |

|--------------------|-----------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |  |

| SY00               | Tpu       | Power-up Period                                                | _                                                                                                                                                                                                                                                                                     | 400                 | 600  | μS    |                                                                                                             |  |

| SY10               | Тоѕт      | Oscillator Start-up Time                                       | —                                                                                                                                                                                                                                                                                     | 1024 Tosc           | _    | —     | Tosc = OSC1 period                                                                                          |  |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                                                                  | _                   | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21 (see Table 26-21) at +85°C |  |

|                    |           |                                                                | 3.25                                                                                                                                                                                                                                                                                  | _                   | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21 (see Table 26-21) at +85°C |  |

| SY13               | Tioz      | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68                                                                                                                                                                                                                                                                                  | 0.72                | 1.2  | μS    |                                                                                                             |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                                                     | _                   |      | μS    |                                                                                                             |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1                                                                                                                                                                                                                                                                                     |                     |      | μS    |                                                                                                             |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | —                                                                                                                                                                                                                                                                                     | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |  |

| SY36               | Tvreg     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | —                                                                                                                                                                                                                                                                                     | _                   | 30   | μS    |                                                                                                             |  |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               | _                                                                                                                                                                                                                                                                                     | 48                  | _    | μS    |                                                                                                             |  |

| SY38               | TOSCDLPRC | LPRC Oscillator Start-up<br>Delay                              | —                                                                                                                                                                                                                                                                                     | —                   | 70   | μS    |                                                                                                             |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

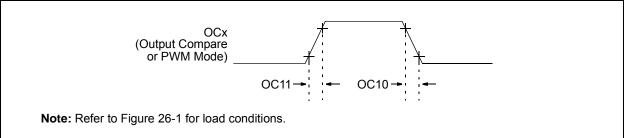

### FIGURE 26-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 26-28: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |

|--------------------|--------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                                                       | _    | _    | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                                                       | —    | —    | ns    | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

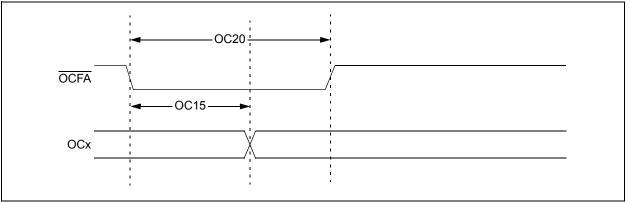

#### FIGURE 26-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 26-29: OCx/PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |          |       |            |  |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max.     | Units | Conditions |  |

| OC15               | TFD    | Fault Input to PWMx I/O<br>Change | _                                                                                                                                                                                                                                                                                       | _    | Tcy + 20 | ns    |            |  |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                                                                                                                                                                                                                                                                | _    | —        | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

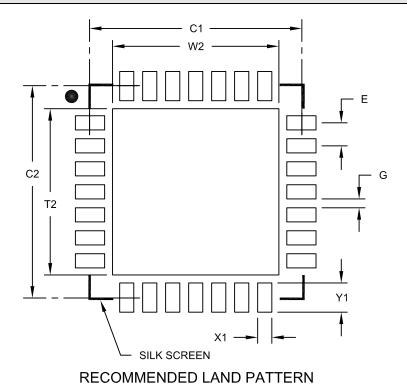

## 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |      |          |      |  |

|----------------------------|------------------|------|----------|------|--|

| Dimensio                   | Dimension Limits |      |          | MAX  |  |

| Contact Pitch              | E                |      | 0.65 BSC |      |  |

| Optional Center Pad Width  | W2               |      |          | 4.70 |  |

| Optional Center Pad Length | T2               |      |          | 4.70 |  |

| Contact Pad Spacing        | C1               |      | 6.00     |      |  |

| Contact Pad Spacing        | C2               |      | 6.00     |      |  |

| Contact Pad Width (X28)    | X1               |      |          | 0.40 |  |

| Contact Pad Length (X28)   | Y1               |      |          | 0.85 |  |

| Distance Between Pads      | G                | 0.25 |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

### **Revision C (October 2015)**

Updates Note 2 in Table 1-1.

Updates Figure 2-5.

Inserts new Section 4.2 "Unique Device Identifier (UDID)" and adds Table 4-1. Subsequent tables were renumbered accordingly. Updates Table 4-3 (which was Table 4-2), Table 4-5 (which was Table 4-2), Table 4-10 (which was Table 4-9), Table 4-11 (which was Table 4-10), Table 4-21 (which was Table 4-20), Table 4-32 (which was Table 4-31), Table 4-36 (which was Table 4-35) and Table 4-37 (which was Table 4-36). Updates Section 4.8.1 "Bit-Reversed Addressing Implementation" (which was Section 4.7.1).

Updates Register 9-1.

Updates Figure 12-2 and Register 12-2.

Updates Register 13-1.

#### Updates Note 1 in Section 14.0 "Output Compare".

Updates Register 15-1, Register 15-6, Register 15-20 and Register 15-22.

Updates Figure 17-1.

Updates Register 18-2.

Updates Figure 19-2 and Figure 19-3. Updates Register 19-1, Register 19-2, Register 19-3, Register 19-4, Register 19-26 and Register 19-33. Adds Register 19-27.

Updates Figure 21-2.

#### Updates Section 23.6.2 "Sleep and Idle Modes".

Updates Table 26-8, Table 26-11, Table 26-29. Adds new Table 26-42. Subsequent tables were renumbered accordingly. Updates Table 26-43 (which was Table 26-42), Table 26-46 (which was Table 26-45) and Table 26-48 (which was Table 26-47).

## Updated diagrams in Section 28.0 "Packaging Information".

Updates the Product Identification System section.

Other minor typographic corrections throughout the document.

#### Revision D (May 2017)

Updates Pin 14 Function on page 3, updates Pin 11 Function on page 4, updates Pin 41 Function on page 5, updates Pin 41 Function on page 6, updates Pin 45 Function on page 7 and updates Pin 43 Function on page 8.

Updates Table 1-1, Table 4-8, Table 4-9, Table 4-10, Table 4-11, Table 4-12, Table 4-16, Table 26-4, Table 26-40, Table 26-43 and Table 26-45.