Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs504t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

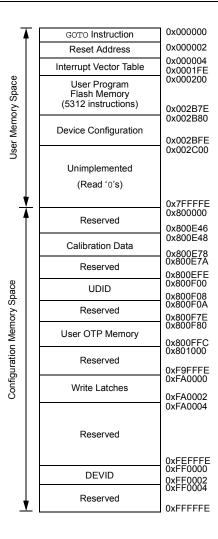

### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP16GS50X DEVICES

Note: Memory areas are not shown to scale.

## 5.4 Dual Partition Flash Configuration

For dsPIC33EP64GS50X devices operating in Dual Partition Flash Program Memory modes, the Inactive Partition can be erased and programmed without stalling the processor. The same programming algorithms are used for programming and erasing the Flash in the Inactive Partition, as described in **Section 5.2 "RTSP Operation"**. On top of the page erase option, the entire Flash memory of the Inactive Partition can be erased by configuring the NVMOP<3:0> bits in the NVMCON register.

Note 1: The application software to be loaded into the Inactive Partition will have the address of the Active Partition. The bootloader firmware will need to offset the address by 0x400000 in order to write to the Inactive Partition.

### 5.4.1 FLASH PARTITION SWAPPING

The Boot Sequence Number is used for determining the Active Partition at start-up and is encoded within the FBTSEQ Configuration register bits. Unlike most Configuration registers, which only utilize the lower 16 bits of the program memory, FBTSEQ is a 24-bit Configuration Word. The Boot Sequence Number (BSEQ) is a 12-bit value and is stored in FBTSEQ twice. The true value is stored in bits, FBTSEQ<11:0>, and its complement is stored in bits, FBTSEQ<23:12>. At device Reset, the sequence numbers are read and the partition with the lowest sequence number becomes the Active Partition. If one of the Boot Sequence Numbers is invalid, the device will select the partition with the valid Boot Sequence Number, or default to Partition 1 if both sequence numbers are invalid. See Section 23.0 "Special Features" for more information.

The BOOTSWP instruction provides an alternative means of swapping the Active and Inactive Partitions (soft swap) without the need for a device Reset. The BOOTSWP must always be followed by a GOTO instruction. The BOOTSWP instruction swaps the Active and Inactive Partitions, and the PC vectors to the location specified by the GOTO instruction in the newly Active Partition.

It is important to note that interrupts should temporarily be disabled while performing the soft swap sequence and that after the partition swap, all peripherals and interrupts which were enabled remain enabled. Additionally, the RAM and stack will maintain state after the switch. As a result, it is recommended that applications using soft swaps jump to a routine that will reinitialize the device in order to ensure the firmware runs as expected. The Configuration registers will have no effect during a soft swap. For robustness of operation, in order to execute the BOOTSWP instruction, it is necessary to execute the NVM unlocking sequence as follows:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Execute the BOOTSWP instruction.

If the unlocking sequence is not performed, the BOOTSWP instruction will be executed as a forced NOP and a GOTO instruction, following the BOOTSWP instruction, will be executed, causing the PC to jump to that location in the current operating partition.

The SFTSWP and P2ACTIV bits in the NVMCON register are used to determine a successful swap of the Active and Inactive Partitions, as well as which partition is active. After the BOOTSWP and GOTO instructions, the SFTSWP bit should be polled to verify the partition swap has occurred and then cleared for the next panel swap event.

### 5.4.2 DUAL PARTITION MODES

While operating in Dual Partition mode, dsPIC33EP64GS50X family devices have the option for both partitions to have their own defined security segments, as shown in Figure 23-4. Alternatively, the device can operate in Protected Dual Partition mode, where Partition 1 becomes permanently erase/write-protected. Protected Dual Partition mode allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1.

dsPIC33EP64GS50X family devices can also operate in Privileged Dual Partition mode, where additional security protections are implemented to allow for protection of intellectual property when multiple parties have software within the device. In Privileged Dual Partition mode, both partitions place additional restrictions on the BSLIM register. These prevent changes to the size of the Boot Segment and General Segment, ensuring that neither segment will be altered.

### 5.5 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 5.5.1 KEY RESOURCES

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### 5.6 Control Registers

Five SFRs are used to write and erase the program Flash memory: NVMCON, NVMKEY, NVMADR, NVMADRU and NVMSRCADR/H.

The NVMCON register (Register 5-1) selects the operation to be performed (page erase, word/row program, Inactive Partition erase), initiates the program or erase cycle and is used to determine the Active Partition in Dual Partition modes.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word/row for programming operations, or the selected page for erase operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

For row programming operation, data to be written to program Flash memory is written into data memory space (RAM) at an address defined by the NVMSRCADR register (location of first element in row programming data).

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1

OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

| R/W-0           | R/W-0                                                                                                                                                                                                                  | R/W-0                                | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|------------------|------------------|-----------------|---------|--|

| U2CTSR7         | U2CTSR6                                                                                                                                                                                                                | U2CTSR5                              | U2CTSR4 | U2CTSR3          | U2CTSR2          | U2CTSR1         | U2CTSR0 |  |

| bit 15          |                                                                                                                                                                                                                        |                                      | ·       | ·                |                  | ·               | bit 8   |  |

|                 |                                                                                                                                                                                                                        |                                      |         |                  |                  |                 |         |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                  | R/W-0                                | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

| U2RXR7          | U2RXR6                                                                                                                                                                                                                 | U2RXR5                               | U2RXR4  | U2RXR3           | U2RXR2           | U2RXR1          | U2RXR0  |  |

| bit 7           |                                                                                                                                                                                                                        |                                      |         |                  |                  |                 | bit (   |  |

|                 |                                                                                                                                                                                                                        |                                      |         |                  |                  |                 |         |  |

| Legend:         | 1.11                                                                                                                                                                                                                   |                                      | 1.11    |                  |                  |                 |         |  |

| R = Readable    |                                                                                                                                                                                                                        | W = Writable                         |         | •                | nented bit, read |                 |         |  |

| -n = Value at I | POR                                                                                                                                                                                                                    | '1' = Bit is set                     |         | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |

| bit 7-0         | U2CTSR<7:0>: Assign UART2 Clear-to-Send (U2CTS) to the Corresponding RPn Pin bits<br>10110101 = Input tied to RP181<br>10110100 = Input tied to RP180<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                                      |         |                  |                  |                 |         |  |

|                 |                                                                                                                                                                                                                        | Input fied to RI<br>Input fied to Vs |         |                  |                  |                 |         |  |

|                 |                                                                                                                                                                                                                        |                                      |         |                  |                  |                 |         |  |

### REGISTER 10-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| R/W-0           | R/W-0                                                                                                                                                         | R/W-0                                | R/W-0    | R/W-0                | R/W-0            | R/W-0              | R/W-0    |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|----------------------|------------------|--------------------|----------|--|

| SCK1INR7        | SCK1INR6                                                                                                                                                      | SCK1INR5                             | SCK1INR4 | SCK1INR3             | SCK1INR2         | SCK1INR1           | SCK1INR0 |  |

| bit 15          |                                                                                                                                                               |                                      |          |                      |                  |                    | bit 8    |  |

|                 |                                                                                                                                                               |                                      |          |                      |                  |                    |          |  |

| R/W-0           | R/W-0                                                                                                                                                         | R/W-0                                | R/W-0    | R/W-0                | R/W-0            | R/W-0              | R/W-0    |  |

| SDI1R7          | SDI1R6                                                                                                                                                        | SDI1R5                               | SDI1R4   | SDI1R3               | SDI1R2           | SDI1R1             | SDI1R0   |  |

| bit 7           |                                                                                                                                                               |                                      |          |                      |                  |                    | bit 0    |  |

| Legend:         |                                                                                                                                                               |                                      |          |                      |                  |                    |          |  |

| R = Readable    | bit                                                                                                                                                           | W = Writable                         | bit      | U = Unimpler         | nented bit, read | as '0'             |          |  |

| -n = Value at F | POR                                                                                                                                                           | '1' = Bit is set                     |          | '0' = Bit is cleared |                  | x = Bit is unknown |          |  |

| bit 7-0         | <pre>SCK1INR&lt;7:0&gt;: Assign SPI1 Clock Input (SCK1) to the Corresponding RPn Pin bits 10110101 = Input tied to RP181 10110100 = Input tied to RP180</pre> |                                      |          |                      |                  |                    |          |  |

|                 |                                                                                                                                                               | Input tied to RF<br>Input tied to Vs |          |                      |                  |                    |          |  |

### REGISTER 10-12: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP37R5 | RP37R4 | RP37R3 | RP37R2 | RP37R1 | RP37R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      |     | RP36R5 | RP36R4 | RP36R3 | RP36R2 | RP36R1 | RP36R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-23: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

|-----------------|-----|------------------|--------|-----------------------------------------|--------|--------|--------|

| —               | —   | RP39R5           | RP39R4 | RP39R3                                  | RP39R2 | RP39R1 | RP39R0 |

| bit 15          |     |                  |        |                                         |        |        | bit 8  |

|                 |     |                  |        |                                         |        |        |        |

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

| —               | —   | RP38R5           | RP38R4 | RP38R3                                  | RP38R2 | RP38R1 | RP38R0 |

| bit 7           |     |                  |        |                                         |        |        | bit 0  |

|                 |     |                  |        |                                         |        |        |        |

| Legend:         |     |                  |        |                                         |        |        |        |

| R = Readable    | bit | W = Writable     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at P | POR | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP39R<5:0>:** Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP38R<5:0>:** Peripheral Output Function is Assigned to RP38 Output Pin bits (see Table 10-2 for peripheral function numbers)

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP53R5 | RP53R4 | RP53R3 | RP53R2 | RP53R1 | RP53R0 |

| bit 15 | ·   | •      |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _      |     | RP52R5 | RP52R4 | RP52R3 | RP52R2 | RP52R1 | RP52R0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP53R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP53 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP52R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP52 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-31: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0                                | U-0 | R/W-0        | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|-----|--------------|--------|-----------------------------------------|--------|--------|--------|

| —                                  | —   | RP55R5       | RP55R4 | RP55R3                                  | RP55R2 | RP55R1 | RP55R0 |

| bit 15                             |     |              |        |                                         |        |        | bit 8  |

|                                    |     |              |        |                                         |        |        |        |

| U-0                                | U-0 | R/W-0        | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

| —                                  | —   | RP54R5       | RP54R4 | RP54R3                                  | RP54R2 | RP54R1 | RP54R0 |

| bit 7                              |     |              |        |                                         |        |        | bit 0  |

|                                    |     |              |        |                                         |        |        |        |

| Legend:                            |     |              |        |                                         |        |        |        |

| R = Readable                       | bit | W = Writable | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at POR '1' = Bit is set |     |              |        | '0' = Bit is cleared x = Bit is unknown |        |        |        |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP55R<5:0>:** Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP54R<5:0>:** Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 0

| REGISTER 16-2: | SPIxCON1: SPIx CONTROL REGISTER 1 |

|----------------|-----------------------------------|

|----------------|-----------------------------------|

| U-0                 | U-0                          | U-0                                   | R/W-0                  | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |

|---------------------|------------------------------|---------------------------------------|------------------------|----------------------|-----------------------------------------|----------------------|----------------------|

| _                   | —                            |                                       | DISSCK                 | DISSDO               | MODE16                                  | SMP                  | CKE <sup>(1)</sup>   |

| bit 15              |                              | ·                                     |                        |                      |                                         |                      | bit                  |

| R/W-0               | R/W-0                        | R/W-0                                 | R/W-0                  | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |

| SSEN <sup>(2)</sup> |                              | MSTEN                                 | SPRE2 <sup>(3)</sup>   | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup>                    | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               | - Or u                       | moren                                 | 011122                 | 011121               | 011120                                  |                      | bit                  |

|                     |                              |                                       |                        |                      |                                         |                      |                      |

| Legend:             |                              |                                       |                        |                      |                                         |                      |                      |

| R = Readable        | e bit                        | W = Writable                          | bit                    | U = Unimpler         | mented bit, read                        | d as '0'             |                      |

| -n = Value at       | POR                          | '1' = Bit is se                       | t                      | '0' = Bit is cle     | ared                                    | x = Bit is unkr      | nown                 |

|                     |                              |                                       |                        |                      |                                         |                      |                      |

| bit 15-13           | Unimplemer                   | nted: Read as                         | 0'                     |                      |                                         |                      |                      |

| bit 12              |                              | able SCKx Pin                         | •                      |                      | <i>'</i> )                              |                      |                      |

|                     |                              | SPIx clock is di:<br>SPIx clock is er | •                      | ctions as I/O        |                                         |                      |                      |

| bit 11              |                              | able SDOx Pir                         |                        |                      |                                         |                      |                      |

|                     |                              | n is not used by                      |                        | oin functions as     | s I/O                                   |                      |                      |

|                     |                              | n is controlled b                     |                        |                      |                                         |                      |                      |

| bit 10              | MODE16: W                    | ord/Byte Comn                         | nunication Sele        | ect bit              |                                         |                      |                      |

|                     |                              | ication is word                       | ,                      |                      |                                         |                      |                      |

|                     |                              | ication is byte-                      |                        |                      |                                         |                      |                      |

| bit 9               |                              | ata Input Sam                         | ole Phase bit          |                      |                                         |                      |                      |

|                     | Master Mode                  | <u>:</u><br>a is sampled at           | the end of da          | ta output time       |                                         |                      |                      |

|                     |                              | a is sampled at                       |                        |                      | ne                                      |                      |                      |

|                     | Slave Mode:<br>SMP must be   | e cleared when                        | SPIx is used i         | n Slave mode.        |                                         |                      |                      |

| bit 8               | CKE: SPIx C                  | lock Edge Sele                        | ect bit <sup>(1)</sup> |                      |                                         |                      |                      |

|                     |                              |                                       |                        |                      | clock state to lo<br>ock state to activ |                      |                      |

| bit 7               |                              | Select Enable                         |                        |                      |                                         | ,                    |                      |

|                     |                              | s used for Slav                       |                        | is controlled h      | by port function                        |                      |                      |

| bit 6               | -                            | Polarity Select                       | -                      |                      | .,                                      |                      |                      |

|                     | 1 = Idle state               | for clock is a h                      | nigh level; activ      |                      |                                         |                      |                      |

| bit 5               |                              | ster Mode Enal                        |                        |                      |                                         |                      |                      |

|                     | 1 = Master m<br>0 = Slave mo | node                                  |                        |                      |                                         |                      |                      |

| Note 1: Th          | ne CKE bit is not            | used in Frame                         | d SPI modes            | Program this bi      | t to '0' for Fram                       | ed SPI modes (       | FRMEN = 1            |

| 0. Th               |                              |                                       |                        |                      |                                         |                      |                      |

- **2:** This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# REGISTER 19-26: ADTRIGxL: ADC CHANNEL TRIGGER x SELECTION REGISTER LOW (x = 0 to 5) (CONTINUED)

bit 4-0 TRGSRC(4x)<4:0>: Trigger Source Selection for Corresponding Analog Inputs bits

- 11111 = ADTRG31

- 11110 = Reserved

- 11101 = Reserved

- 11100 = PWM Generator 5 current-limit trigger

- 11011 = PWM Generator 4 current-limit trigger

- 11010 = PWM Generator 3 current-limit trigger

- 11001 = PWM Generator 2 current-limit trigger

- 11000 = PWM Generator 1 current-limit trigger

- 10111 = Output Compare 2 trigger

- 10110 = Output Compare 1 trigger 10101 = Reserved

- 10100 = Reserved

- 10011 = PWM Generator 5 secondary trigger

- 10010 = PWM Generator 4 secondary trigger

- 10001 = PWM Generator 3 secondary trigger

- 10000 = PWM Generator 2 secondary trigger

- 01111 = PWM Generator 1 secondary trigger

- 01110 = PWM secondary Special Event Trigger

- 01101 = Timer2 period match

- 01100 = Timer1 period match

- 01011 = Reserved

- 01010 = Reserved

- 01001 = PWM Generator 5 primary trigger

- 01000 = PWM Generator 4 primary trigger

- 00111 = PWM Generator 3 primary trigger

- 00110 = PWM Generator 2 primary trigger

- 00101 = PWM Generator 1 primary trigger

- 00100 = PWM Special Event Trigger

- 00011 = Reserved

- 00010 = Level software trigger

- 00001 = Common software trigger

- 00000 = No trigger is enabled

### REGISTER 19-30: ADCAL1H: ADC CALIBRATION REGISTER 1 HIGH

| R/W-0, HS     | U-0                              | U-0              | U-0               | r-0                                | R/W-0    | R/W-0              | R/W-0   |  |  |

|---------------|----------------------------------|------------------|-------------------|------------------------------------|----------|--------------------|---------|--|--|

| CSHRRDY       | _                                | —                | _                 | —                                  | CSHRDIFF | CSHREN             | CSHRRUN |  |  |

| bit 15        | ·                                | •                |                   |                                    |          |                    | bit 8   |  |  |

|               |                                  |                  |                   |                                    |          |                    |         |  |  |

| U-0           | U-0                              | U-0              | U-0               | U-0                                | U-0      | U-0                | U-0     |  |  |

| _             | —                                | —                | —                 | —                                  | —        | —                  | —       |  |  |

| bit 7         |                                  |                  |                   | •                                  |          |                    | bit 0   |  |  |

|               |                                  |                  |                   |                                    |          |                    |         |  |  |

| Legend:       |                                  | r = Reserved     | bit               | U = Unimplemented bit, read as '0' |          |                    |         |  |  |

| R = Readabl   | e bit                            | W = Writable I   | oit               | HS = Hardware Settable bit         |          |                    |         |  |  |

| -n = Value at | POR                              | '1' = Bit is set |                   | '0' = Bit is clea                  | ared     | x = Bit is unknown |         |  |  |

| <u> </u>      |                                  |                  |                   |                                    |          |                    |         |  |  |

| bit 15        | CSHRRDY: S                       | Shared ADC Co    | re Calibration    | Status Flag bit                    |          |                    |         |  |  |

|               | 1 = Shared A                     | DC core calibra  | tion is finished  | _                                  |          |                    |         |  |  |

|               | 0 = Shared A                     | DC core calibra  | ition is in progr | ess                                |          |                    |         |  |  |

| bit 14-12     | Unimplemen                       | ted: Read as 'd  | )'                |                                    |          |                    |         |  |  |

| bit 11        | Reserved: Must be written as '0' |                  |                   |                                    |          |                    |         |  |  |

- bit 10 **CSHRDIFF:** Shared ADC Core Differential-Mode Calibration bit

- 1 = Shared ADC core will be calibrated in Differential Input mode

- 0 = Shared ADC core will be calibrated in Single-Ended Input mode

- bit 9 **CSHREN:** Shared ADC Core Calibration Enable bit

- 1 = Shared ADC core calibration bits (CSHRRDY, CSHRDIFF and CSHRRUN) can be accessed by software

- 0 = Shared ADC core calibration bits are disabled

- bit 8 CSHRRUN: Shared ADC Core Calibration Start bit

- 1 = If this bit is set by software, the shared ADC core calibration cycle is started; this bit is cleared automatically by hardware

- 0 = Software can start the next calibration cycle

- bit 7-0 Unimplemented: Read as '0'

### **REGISTER 19-31:** ADCMPxCON: ADC DIGITAL COMPARATOR x CONTROL REGISTER (x = 0 or 1)

| U-0                   | U-0                                                                                                      | U-0                                                   | R-0, HSC                       | R-0, HSC          | R-0, HSC         | R-0, HSC          | R-0, HSC       |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|-------------------|------------------|-------------------|----------------|

| —                     | —                                                                                                        | —                                                     | CHNL4                          | CHNL3             | CHNL2            | CHNL1             | CHNL0          |

| bit 15                |                                                                                                          |                                                       |                                |                   |                  |                   | bit 8          |

| R/W-0                 | R/W-0                                                                                                    | R-0, HC, HS                                           | R/W-0                          | R/W-0             | R/W-0            | R/W-0             | R/W-0          |

| CMPEN                 | IE                                                                                                       | STAT                                                  | BTWN                           | НІНІ              | HILO             | LOHI              | LOLO           |

| bit 7                 |                                                                                                          | ••••                                                  |                                |                   |                  |                   | bit 0          |

| Legend:               |                                                                                                          | HC = Hardwar                                          | e Clearable bit                | U = Unimplerr     | nented bit, read | as '0'            |                |

| R = Readable          | e bit                                                                                                    | W = Writable                                          |                                |                   | are Settable/Cle |                   |                |

| -n = Value at         | POR                                                                                                      | '1' = Bit is set                                      |                                | '0' = Bit is cle  | ared             | HS = Hardwar      | e Settable bit |

|                       |                                                                                                          | tada Daadaa (                                         | <u>,</u>                       |                   |                  |                   |                |

| bit 15-13<br>bit 12-8 | -                                                                                                        | ted: Read as '0<br>Input Channel I                    |                                |                   |                  |                   |                |

|                       | If the compara<br>11111 = Res<br>10110 = Res<br>10101 = AN2<br>10100 = AN2<br>00001 = AN1<br>00000 = AN0 | erved<br>11<br>10                                     | ed an event for                | a channel, thi    | s channel numb   | per is written to | these bits.    |

| bit 7                 |                                                                                                          | nparator Enable                                       | e bit                          |                   |                  |                   |                |

|                       | 1 = Comparat<br>0 = Comparat                                                                             | tor is enabled<br>tor is disabled a                   | and the STAT s                 | tatus bit is clea | ared             |                   |                |

| bit 6                 | IE: Comparat                                                                                             | or Common AE                                          | C Interrupt En                 | able bit          |                  |                   |                |

|                       |                                                                                                          | ADC interrupt v<br>ADC interrupt v                    | 0                              |                   |                  | comparison ev     | vent           |

| bit 5                 | STAT: Compa                                                                                              | arator Event Sta                                      | itus bit                       |                   |                  |                   |                |

|                       | 1 = A compar                                                                                             | ared by hardwa<br>ison event has<br>ison event has    | been detected                  | since the last    | read of the CH   | NL<4:0> bits      |                |

| bit 4                 | BTWN: Betwe                                                                                              | een Low/High (                                        | Comparator Ev                  | ent bit           |                  |                   |                |

|                       |                                                                                                          | s a comparator<br>generate a digi                     |                                |                   |                  |                   | CMPxHI         |

| bit 3                 | HIHI: High/Hig                                                                                           | gh Comparator                                         | Event bit                      |                   |                  |                   |                |

|                       |                                                                                                          | s a digital comp<br>generate a digi                   |                                |                   |                  | CMPxHI            |                |

| bit 2                 | HILO: High/L                                                                                             | ow Comparator                                         | Event bit                      |                   |                  |                   |                |

|                       |                                                                                                          | s a digital comp<br>generate a digi                   |                                |                   |                  |                   |                |

| bit 1                 | 1 = Generate                                                                                             | igh Comparator<br>s a digital comp<br>generate a digi | arator event w                 |                   |                  |                   |                |

| bit 0                 | LOLO: Low/L<br>1 = Generate                                                                              | ow Comparato<br>s a digital comp<br>generate a digi   | r Event bit<br>parator event w | /hen ADCBUF>      | x < ADCMPxLC     | )                 |                |

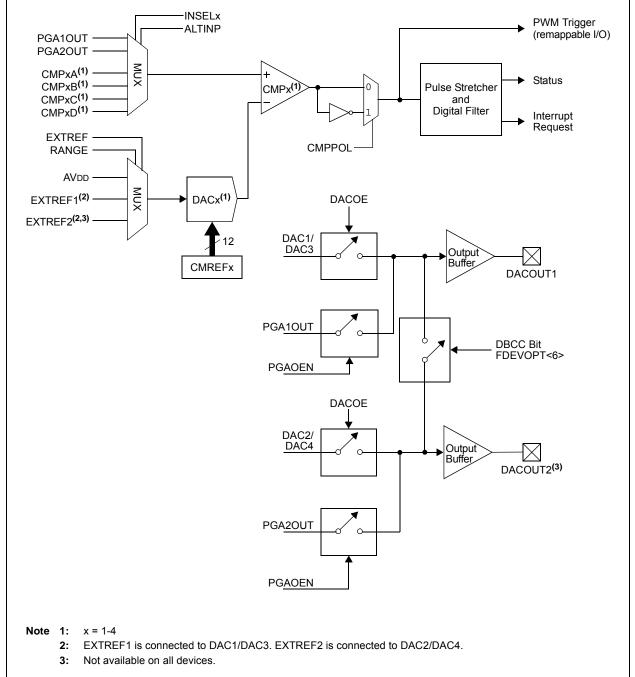

### 20.2 Module Description

Figure 20-1 shows a functional block diagram of one analog comparator from the high-speed analog comparator module. The analog comparator provides high-speed operation with a typical delay of 15 ns. The negative input of the comparator is always connected to the DACx circuit. The positive input of the comparator is connected to an analog multiplexer that selects the desired source pin. The analog comparator input pins are typically shared with pins used by the Analog-to-Digital Converter (ADC) module. Both the comparator and the ADC can use the same pins at the same time. This capability enables a user to measure an input voltage with the ADC and detect voltage transients with the comparator.

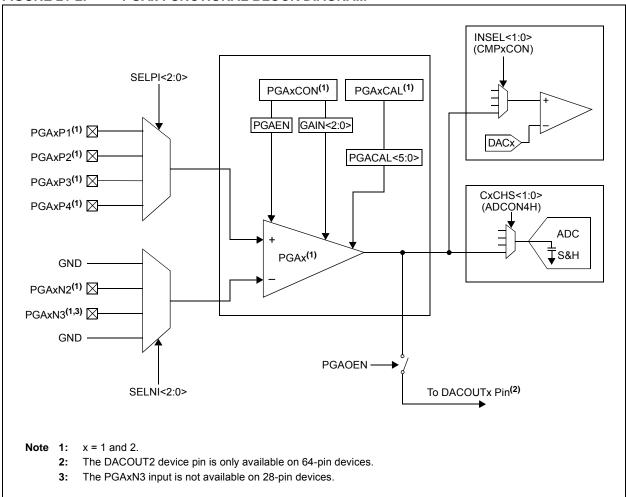

### 21.1 Module Description

The Programmable Gain Amplifiers are used to amplify small voltages (i.e., voltages across burden/shunt resistors) to improve the signal-to-noise ratio of the measured signal. The PGAx output voltage can be read by any of the four dedicated Sample-and-Hold circuits on the ADC module. The output voltage can also be fed to the comparator module for overcurrent/ voltage protection. Figure 21-2 shows a functional block diagram of the PGAx module. Refer to **Section 19.0 "High-Speed, 12-Bit Analog-to-Digital Converter (ADC)"** and **Section 20.0 "High-Speed Analog Comparator"** for more interconnection details.

The gain of the PGAx module is selectable via the GAIN<2:0> bits in the PGAxCON register. There are five selectable gains, ranging from 4x to 64x. The SELPI<2:0> and SELNI<2:0> bits in the PGAxCON register select one of four positive/negative inputs to the PGAx module. For single-ended applications, the SELNI<2:0> bits will select the ground as the negative

input source. To provide an independent ground reference, PGAxN2 and PGAxN3 pins are available as the negative input source to the PGAx module.

Note 1: Not all PGA positive/negative inputs are available on all devices. Refer to the specific device pinout for available input source pins.

The output voltage of the PGAx module can be connected to the DACOUTx pin by setting the PGAOEN bit in the PGAxCON register. When the PGAOEN bit is enabled, the output voltage of PGA1 is connected to DACOUT1 and PGA2 is connected to DACOUT2. For devices with a single DACOUTx pin, the output voltage of PGA2 can be connected to DACOUT1 by configuring the DBCC Configuration bit in the FDEVOPT register (FDEVOPT<6>).

If both the DACx output voltage and PGAx output voltage are connected to the DACOUTx pin, the resulting output voltage would be a combination of signals. There is no assigned priority between the PGAx module and the DACx module.

### FIGURE 21-2: PGAx FUNCTIONAL BLOCK DIAGRAM

| TABLE 26-14: | DC CHARACTERISTICS: PROGRAM MEMORY |

|--------------|------------------------------------|

|--------------|------------------------------------|

| DC CHARACTERISTICS |        |                                                     | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |                     |      |       |                                                                |  |

|--------------------|--------|-----------------------------------------------------|---------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                      | Min.                                                                      | Typ. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|                    |        | Program Flash Memory                                |                                                                           |                     |      |       |                                                                |  |

| D130               | Eр     | Cell Endurance                                      | 10,000                                                                    |                     | _    | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                        | 3.0                                                                       | _                   | 3.6  | V     |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0                                                                       |                     | 3.6  | V     |                                                                |  |

| D134               | TRETD  | Characteristic Retention                            | 20                                                                        | —                   | —    | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                         | 10                  | —    | mA    |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —                                                                         | —                   | 150  | mA    |                                                                |  |

| D137a              | Тре    | Page Erase Time                                     | 19.7                                                                      | —                   | 20.1 | ms    | TPE = 146893 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>         |  |

| D137b              | TPE    | Page Erase Time                                     | 19.5                                                                      | —                   | 20.3 | ms    | TPE = 146893 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>        |  |

| D138a              | Tww    | Word Write Cycle Time                               | 46.5                                                                      | —                   | 47.3 | μs    | Tww = 346 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>            |  |

| D138b              | Tww    | Word Write Cycle Time                               | 46.0                                                                      | —                   | 47.9 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C <b>(Note 3)</b>           |  |

| D139a              | Trw    | Row Write Time                                      | 667                                                                       | _                   | 679  | μs    | Trw = 4965 FRC cycles,<br>Ta = +85°C <b>(Note 3)</b>           |  |

| D139b              | Trw    | Row Write Time                                      | 660                                                                       | —                   | 687  | μs    | Trw = 4965 FRC cycles,<br>Ta = +125°C <b>(Note 3)</b>          |  |

**Note 1:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 26-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

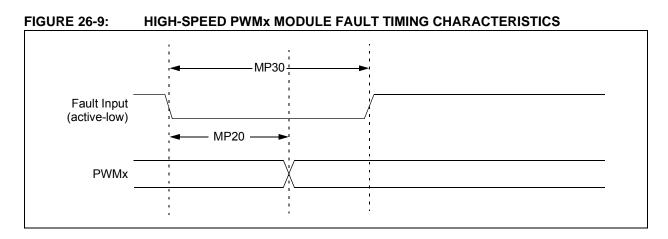

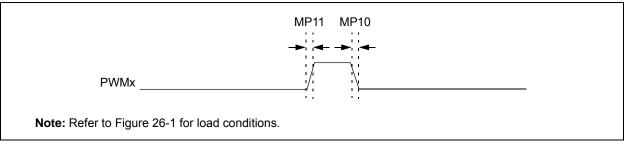

### FIGURE 26-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

### TABLE 26-30: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |

|--------------------|--------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions         |

| MP10               | TFPWM  | PWMx Output Fall Time               | —                                                                                                                                                                                                                                                                                     | —    | —    | ns    | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                                                                                                                                                                                                                                                                                     | _    | _    | ns    | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                                                                                                                                                                                                                                                     | _    | 15   | ns    |                    |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                                                                                                                                                                                                                                                    | —    | —    | ns    |                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

## TABLE 26-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |                        |       |                                |  |

|--------------------|-----------------------|------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|------------------------|-------|--------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                | Min.                                                  | Тур. <sup>(2)</sup> | Max.                   | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCKx Input<br>Frequency                                              | _                                                     | —                   | Lesser of:<br>FP or 11 | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCKx Input Fall Time                                                         | —                                                     | _                   | _                      | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                                                         | _                                                     | —                   |                        | ns    | See Parameter DO31 (Note 4)    |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                                   | _                                                     | _                   |                        | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                                   | —                                                     | _                   |                        | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After<br>SCKx Edge                                    | —                                                     | 6                   | 20                     | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                 | 30                                                    | —                   | —                      | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                   | 30                                                    | _                   | _                      | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                    | 30                                                    | _                   | _                      | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx $\downarrow$<br>Input | 120                                                   | —                   | —                      | ns    |                                |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                       | 10                                                    | —                   | 50                     | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx Edge                                                        | 1.5 Tcy + 40                                          | _                   | _                      | ns    | (Note 4)                       |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                     | —                                                     | —                   | 50                     | ns    |                                |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

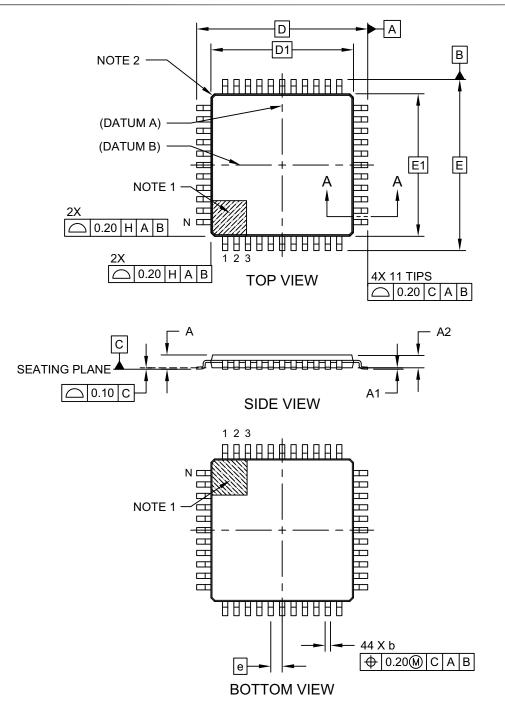

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

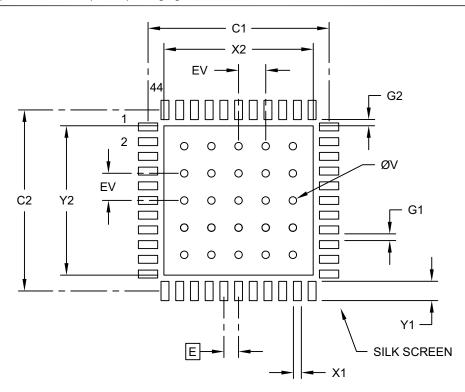

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                                  | Ν      | /ILLIMETER | S        |      |

|----------------------------------|--------|------------|----------|------|

| Dimension                        | Limits | MIN        | NOM      | MAX  |

| Contact Pitch                    | E      |            | 0.65 BSC |      |

| Optional Center Pad Width        | X2     |            |          | 6.60 |

| Optional Center Pad Length       | Y2     |            |          | 6.60 |

| Contact Pad Spacing              | C1     |            | 8.00     |      |

| Contact Pad Spacing              | C2     |            | 8.00     |      |

| Contact Pad Width (X44)          | X1     |            |          | 0.35 |

| Contact Pad Length (X44)         | Y1     |            |          | 0.85 |

| Contact Pad to Contact Pad (X40) | G1     | 0.30       |          |      |

| Contact Pad to Center Pad (X44)  | G2     | 0.28       |          |      |

| Thermal Via Diameter             | V      |            | 0.33     |      |

| Thermal Via Pitch                | EV     |            | 1.20     |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C

NOTES: