Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

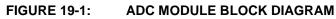

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

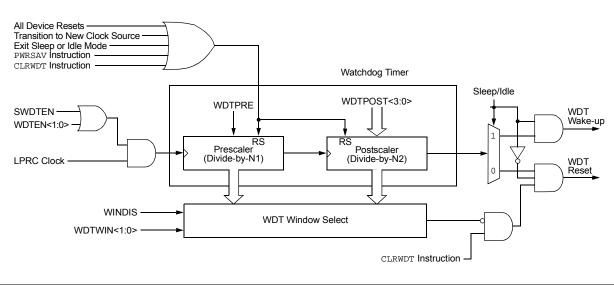

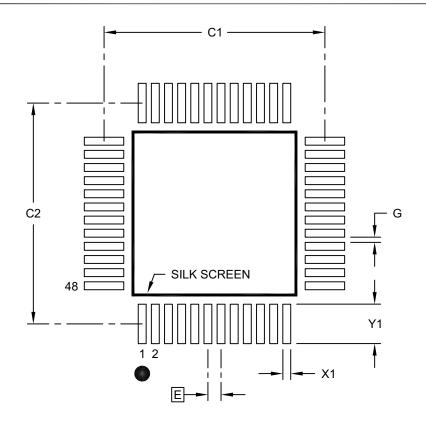

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs504t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

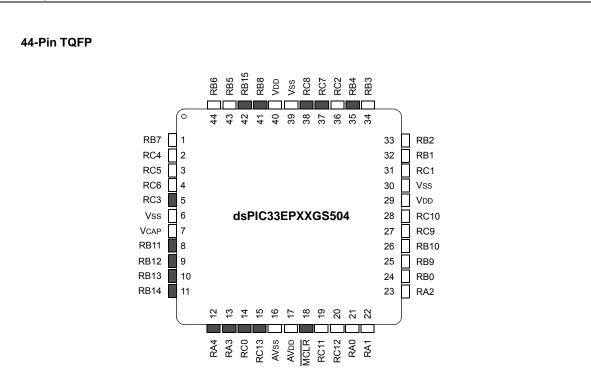

# **Pin Diagrams (Continued)**

| Pin | Pin Function                      | Pin | Pin Function                              |

|-----|-----------------------------------|-----|-------------------------------------------|

| 1   | PGEC1/AN21/SDA1/ <b>RP39</b> /RB7 | 23  | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2         |

| 2   | AN1ALT/ <b>RP52</b> /RC4          | 24  | AN3/PGA2P3/CMP1D/CMP2B/RP32/RB0           |

| 3   | AN0ALT/RP53/RC5                   | 25  | AN4/CMP2C/CMP3A/ISRC4/RP41/RB9            |

| 4   | AN17/ <b>RP54</b> /RC6            | 26  | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10           |

| 5   | RP51/RC3                          | 27  | AN11/PGA1N3/ <b>RP57</b> /RC9             |

| 6   | Vss                               | 28  | AN10/PGA1P4/EXTREF2/RP58/RC10             |

| 7   | VCAP                              | 29  | VDD                                       |

| 8   | TMS/PWM3H/RP43/RB11               | 30  | Vss                                       |

| 9   | TCK/PWM3L/ <b>RP44</b> /RB12      | 31  | AN8/PGA2P4/CMP4C/RP49/RC1                 |

| 10  | PWM2H/ <b>RP45</b> /RB13          | 32  | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1  |

| 11  | PWM2L/ <b>RP46</b> /RB14          | 33  | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/RP34/RB2 |

| 12  | PWM1H/RA4                         | 34  | PGED2/AN18/DACOUT1/INT0/RP35/RB3          |

| 13  | PWM1L/RA3                         | 35  | PGEC2/ADTRG31/ <b>RP36</b> /RB4           |

| 14  | FLT12/ <b>RP48</b> /RC0           | 36  | AN9/CMP4D/EXTREF1/RP50 /RC2               |

| 15  | FLT11/ <b>RP61</b> /RC13          | 37  | ASDA1/ <b>RP55</b> /RC7                   |

| 16  | AVss                              | 38  | ASCL1/RP56/RC8                            |

| 17  | AVDD                              | 39  | Vss                                       |

| 18  | MCLR                              | 40  | VDD                                       |

| 19  | AN12/ISRC1/ <b>RP59</b> /RC11     | 41  | PGED3/SDA2/FLT31/RP40/RB8                 |

| 20  | AN14/PGA2N3/ <b>RP60</b> /RC12    | 42  | PGEC3/SCL2/RP47/RB15                      |

| 21  | AN0/PGA1P1/CMP1A/RA0              | 43  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5         |

| 22  | AN1/PGA1P2/PGA2P1/CMP1B/RA1       | 44  | PGED1/TDI/AN20/SCL1/RP38/RB6              |

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

# TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name <sup>(1)</sup>   | Pin<br>Type | Buffer<br>Type   | PPS        | Description                                                                                                                              |  |  |  |

|---------------------------|-------------|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AN0-AN21<br>AN0ALT-AN1ALT |             | Analog<br>Analog | No<br>No   | Analog input channels.<br>Alternate analog input channels.                                                                               |  |  |  |

| CLKI                      | I           | ST/<br>CMOS      | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |  |  |  |

| CLKO                      | 0           | —                | No         | Always associated with OSC2 pin function.                                                                                                |  |  |  |

| OSC1                      | I           | ST/<br>CMOS      | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                          |  |  |  |

| OSC2                      | I/O         | —                | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |  |  |  |

| REFCLKO                   | 0           | _                | Yes        | Reference clock output.                                                                                                                  |  |  |  |

| IC1-IC4                   | 1           | ST               | Yes        | Capture Inputs 1 through 4.                                                                                                              |  |  |  |

| OCFA                      | 1           | ST               | Yes        | Compare Fault A input (for compare channels).                                                                                            |  |  |  |

| OC1-OC4                   | Ó           | _                | Yes        | Compare Outputs 1 through 4.                                                                                                             |  |  |  |

| INT0                      | 1           | ST               | No         | External Interrupt 0.                                                                                                                    |  |  |  |

| INT1                      | I           | ST               | Yes        | External Interrupt 1.                                                                                                                    |  |  |  |

| INT2                      | I           | ST               | Yes        | External Interrupt 2.                                                                                                                    |  |  |  |

| INT4                      | Ι           | ST               | No         | External Interrupt 4.                                                                                                                    |  |  |  |

| RA0-RA4                   | I/O         | ST               | No         | PORTA is a bidirectional I/O port.                                                                                                       |  |  |  |

| RB0-RB15                  | I/O         | ST               | No         | PORTB is a bidirectional I/O port.                                                                                                       |  |  |  |

| RC0-RC15                  | I/O         | ST               | No         | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |

| RD0-RD15                  | I/O         | ST               | No         | PORTD is a bidirectional I/O port.                                                                                                       |  |  |  |

| T1CK                      | 1           | ST               | Yes        | Timer1 external clock input.                                                                                                             |  |  |  |

| T2CK                      |             | ST               | Yes        | Timer2 external clock input.                                                                                                             |  |  |  |

| T3CK                      | İ           | ST               | Yes        | Timer3 external clock input.                                                                                                             |  |  |  |

| T4CK                      | I           | ST               | No         | Timer4 external clock input.                                                                                                             |  |  |  |

| T5CK                      | I.          | ST               | No         | Timer5 external clock input.                                                                                                             |  |  |  |

| U1CTS                     | I           | ST               | Yes        | UART1 Clear-to-Send.                                                                                                                     |  |  |  |

| U1RTS                     | 0           | _                | Yes        | UART1 Request-to-Send.                                                                                                                   |  |  |  |

| U1RX                      | I           | ST               | Yes        | UART1 receive.                                                                                                                           |  |  |  |

| U1TX                      | 0           | —                | Yes        | UART1 transmit.                                                                                                                          |  |  |  |

| BCLK1                     | 0           | ST               | Yes        | UART1 IrDA <sup>®</sup> baud clock output.                                                                                               |  |  |  |

| U2CTS                     | I           | ST               | Yes        |                                                                                                                                          |  |  |  |

| U2RTS                     | 0           | —                |            | UART2 Request-to-Send.                                                                                                                   |  |  |  |

| U2RX                      |             | ST               |            | UART2 receive.                                                                                                                           |  |  |  |

| U2TX                      | 0           |                  | Yes        | UART2 transmit.                                                                                                                          |  |  |  |

| BCLK2                     | 0           | ST               | Yes        | UART2 IrDA baud clock output.                                                                                                            |  |  |  |

| SCK1                      | 1/0         | ST               | Yes        | Synchronous serial clock input/output for SPI1.                                                                                          |  |  |  |

| SDI1                      |             | ST               | Yes        | SPI1 data in.                                                                                                                            |  |  |  |

| SDO1<br>SS1               | 0<br>I/O    | ST               | Yes<br>Yes | SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                         |  |  |  |

| SCK2                      | I/O         | ST               | Yes        | Synchronous serial clock input/output for SPI2.                                                                                          |  |  |  |

| SDI2                      | 1           | ST               | Yes        | SPI2 data in.                                                                                                                            |  |  |  |

| SDO2                      | 0           |                  | Yes        | SPI2 data ini.<br>SPI2 data out.                                                                                                         |  |  |  |

| <u>SS2</u>                | 1/0         | ST               | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                           |  |  |  |

| Legend: CMOS = C          | _           |                  |            |                                                                                                                                          |  |  |  |

| ST = Schm<br>PPS = Peri   | itt Trigg   | er input v       | vith CN    |                                                                                                                                          |  |  |  |

1: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**2:** These pins are dedicated on 64-pin devices.

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70005156) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXGS50X family device to be serially programmed while in the end application circuit. This is done with a programming clock and programming data (PGECx/PGEDx) line, and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the Program Executive, to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data with a single program memory word and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

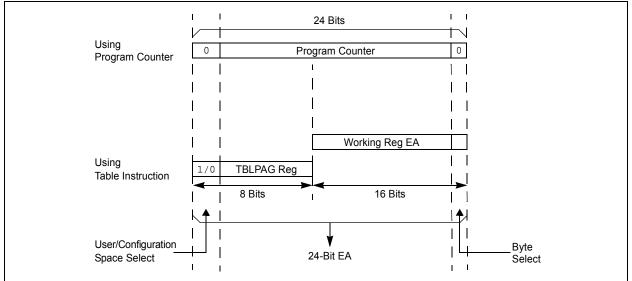

# 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1. The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes. The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-1         | R/W-0       | R/W-0                                     | U-0            | U-0              | U-0              | U-0             | R/W-0  |

|---------------|-------------|-------------------------------------------|----------------|------------------|------------------|-----------------|--------|

| GIE           | DISI        | SWTRAP                                    | _              | _                | _                |                 | AIVTEN |

| bit 15        |             |                                           |                |                  |                  |                 | bit    |

|               |             |                                           |                |                  |                  |                 |        |

| U-0           | U-0         | U-0                                       | R/W-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |

|               |             | —                                         | INT4EP         |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7         |             |                                           |                |                  |                  |                 | bit    |

| Legend:       |             |                                           |                |                  |                  |                 |        |

| R = Readable  | e bit       | W = Writable                              | bit            | U = Unimple      | mented bit, read | l as '0'        |        |

| -n = Value at | POR         | '1' = Bit is set                          |                | '0' = Bit is cle | eared            | x = Bit is unki | nown   |

|               |             |                                           |                |                  |                  |                 |        |

| bit 15        | GIE: Global | Interrupt Enable                          | e bit          |                  |                  |                 |        |

|               |             | ts and associate                          |                |                  |                  |                 |        |

|               |             | ts are disabled, I                        | •              | till enabled     |                  |                 |        |

| bit 14        |             | Instruction Statu                         |                |                  |                  |                 |        |

|               |             | struction is active<br>struction is not a |                |                  |                  |                 |        |

| bit 13        |             | Software Trap St                          |                |                  |                  |                 |        |

| DIL 15        |             | e trap is enabled                         |                |                  |                  |                 |        |

|               |             | e trap is disabled                        |                |                  |                  |                 |        |

| bit 12-9      | Unimpleme   | ented: Read as '                          | 0'             |                  |                  |                 |        |

| bit 8         | AIVTEN: Al  | ternate Interrupt                         | Vector Table E | Enable           |                  |                 |        |

|               |             | ternate Interrupt                         |                |                  |                  |                 |        |

|               |             | andard Interrupt                          |                |                  |                  |                 |        |

| bit 7-5       | -           | ented: Read as '                          |                |                  |                  |                 |        |

| bit 4         |             | ternal Interrupt 4                        | -              | Polarity Selec   | ct bit           |                 |        |

|               | •           | t on negative ed<br>t on positive edg     | •              |                  |                  |                 |        |

| bit 3         | -           | ented: Read as '                          |                |                  |                  |                 |        |

| bit 2         | -           | ternal Interrupt 2                        |                | Polarity Selec   | rt hit           |                 |        |

| SIL 2         |             | t on negative ed                          | 0              |                  |                  |                 |        |

|               |             | t on positive edg                         |                |                  |                  |                 |        |

| bit 1         | INT1EP: Ex  | ternal Interrupt 1                        | Edge Detect    | Polarity Selec   | ct bit           |                 |        |

|               |             | t on negative ed                          |                |                  |                  |                 |        |

|               | •           | t on positive edg                         |                |                  |                  |                 |        |

| bit 0         |             | ternal Interrupt (                        | -              | Polarity Selec   | ct bit           |                 |        |

|               |             | t on negative edg                         |                |                  |                  |                 |        |

|               | 0 = memup   | t on positive edg                         | e              |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0          | U-0          | U-0                | U-0              | U-0                                     | U-0              | U-0    | R/W-0 |  |

|--------------|--------------|--------------------|------------------|-----------------------------------------|------------------|--------|-------|--|

| _            | —            | _                  | —                | _                                       | —                | —      | NAE   |  |

| bit 15       |              |                    |                  |                                         |                  |        | bit 8 |  |

|              |              |                    |                  |                                         |                  |        |       |  |

| U-0          | U-0          | U-0                | R/W-0            | U-0                                     | U-0              | U-0    | R/W-0 |  |

| —            | —            |                    | DOOVR            | —                                       |                  |        | APLL  |  |

| bit 7        |              |                    |                  |                                         |                  |        | bit 0 |  |

|              |              |                    |                  |                                         |                  |        |       |  |

| Legend:      |              |                    |                  |                                         |                  |        |       |  |

| R = Readal   | ole bit      | W = Writable       | bit              | U = Unimple                             | mented bit, read | as '0' |       |  |

| -n = Value a | at POR       | '1' = Bit is se    | t                | '0' = Bit is cleared x = Bit is unknown |                  |        |       |  |

|              |              |                    |                  |                                         |                  |        |       |  |

| bit 15-9     | Unimplemer   | nted: Read as      | '0'              |                                         |                  |        |       |  |

| bit 8        | NAE: NVM A   | ddress Error S     | Soft Trap Status | s bit                                   |                  |        |       |  |

|              |              |                    | trap has occur   |                                         |                  |        |       |  |

|              |              |                    | trap has not o   | ccurred                                 |                  |        |       |  |

| bit 7-5      | Unimplemer   | nted: Read as      | '0'              |                                         |                  |        |       |  |

| bit 4        | DOOVR: DO    | Stack Overflov     | v Soft Trap Sta  | tus bit                                 |                  |        |       |  |

|              | 1 = DO stack | overflow soft t    | rap has occurre  | ed                                      |                  |        |       |  |

|              | 0 = DO stack | overflow soft t    | rap has not oc   | curred                                  |                  |        |       |  |

| bit 3-1      | Unimplemer   | nted: Read as      | '0'              |                                         |                  |        |       |  |

| bit 0        | APLL: Auxili | ary PLL Loss o     | of Lock Soft Tra | ap Status bit                           |                  |        |       |  |

|              | 1 = APLL loc | k soft trap has    | occurred         |                                         |                  |        |       |  |

|              |              | le a aft trans has | wet easy word    |                                         |                  |        |       |  |

0 = APLL lock soft trap has not occurred

#### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|--------------|------------------|----------------|------------------|------------------|-----------------|-------|

| _            | —            | —                | —              | —                | —                | —               | —     |

| bit 15       |              |                  |                |                  |                  |                 | bit 8 |

|              |              |                  |                |                  |                  |                 |       |

| U-0          | U-0          | U-0              | U-0            | U-0              | U-0              | U-0             | R/W-0 |

| _            | —            | —                | —              | —                | —                | —               | SGHT  |

| bit 7        |              | •                |                |                  |                  | •               | bit 0 |

|              |              |                  |                |                  |                  |                 |       |

| Legend:      |              |                  |                |                  |                  |                 |       |

| R = Readab   | le bit       | W = Writable     | bit            | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value a | t POR        | '1' = Bit is set | t              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

|              |              |                  |                |                  |                  |                 |       |

| bit 15-1     | Unimplemen   | ted: Read as     | '0'            |                  |                  |                 |       |

| bit 0        | SGHT: Softwa | are Generated    | Hard Trap Sta  | tus bit          |                  |                 |       |

|              | 1 = Software | generated har    | d trap has occ | urred            |                  |                 |       |

|              | 0 = Software | generated har    | d trap has not | occurred         |                  |                 |       |

|              |              |                  |                |                  |                  |                 |       |

|              |              |                  |                |                  |                  |                 |       |

#### REGISTER 10-20: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0        | R/W-0                                                                                                                                    | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |  |  |  |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|------------------|----------|--------|--|--|--|

| _             | —          | RP33R5                                                                                                                                   | RP33R4 | RP33R3                                  | RP33R2           | RP33R1   | RP33R0 |  |  |  |

| bit 15        |            |                                                                                                                                          |        |                                         |                  |          | bit 8  |  |  |  |

|               |            |                                                                                                                                          |        |                                         |                  |          |        |  |  |  |

| U-0           | U-0        | R/W-0                                                                                                                                    | R/W-0  | R/W-0                                   | R/W-0            | R/W-0    | R/W-0  |  |  |  |

| _             | —          | RP32R5                                                                                                                                   | RP32R4 | RP32R3                                  | RP32R2           | RP32R1   | RP32R0 |  |  |  |

| bit 7         |            |                                                                                                                                          |        |                                         |                  |          | bit 0  |  |  |  |

|               |            |                                                                                                                                          |        |                                         |                  |          |        |  |  |  |

| Legend:       |            |                                                                                                                                          |        |                                         |                  |          |        |  |  |  |

| R = Readabl   | e bit      | W = Writable                                                                                                                             | bit    | U = Unimpler                            | mented bit, read | 1 as '0' |        |  |  |  |

| -n = Value at | POR        | '1' = Bit is set                                                                                                                         |        | '0' = Bit is cleared x = Bit is unknown |                  |          |        |  |  |  |

|               |            |                                                                                                                                          |        |                                         |                  |          |        |  |  |  |

| bit 15-14     | Unimplemen | ted: Read as '                                                                                                                           | 0'     |                                         |                  |          |        |  |  |  |

| bit 13-8      |            | <b>RP33R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP33 Output Pin bits (see Table 10-2 for peripheral function numbers) |        |                                         |                  |          |        |  |  |  |

| bit 7-6       | Unimplemen | ted: Read as '                                                                                                                           | 0'     |                                         |                  |          |        |  |  |  |

bit 5-0 **RP32R<5:0>:** Peripheral Output Function is Assigned to RP32 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-21: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                                                                              | U-0        | R/W-0          | R/W-0  | R/W-0                                   | R/W-0            | R/W-0  | R/W-0  |  |

|--------------------------------------------------------------------------------------------------|------------|----------------|--------|-----------------------------------------|------------------|--------|--------|--|

| _                                                                                                | —          | RP35R5         | RP35R4 | RP35R3                                  | RP35R2           | RP35R1 | RP35R0 |  |

| bit 15                                                                                           |            | •              |        |                                         |                  | •      | bit 8  |  |

|                                                                                                  |            |                |        |                                         |                  |        |        |  |

| U-0                                                                                              | U-0        | R/W-0          | R/W-0  | R/W-0                                   | R/W-0            | R/W-0  | R/W-0  |  |

| —                                                                                                | —          | RP34R5         | RP34R4 | RP34R3                                  | RP34R2           | RP34R1 | RP34R0 |  |

| bit 7                                                                                            |            | •              |        |                                         |                  | •      | bit 0  |  |

|                                                                                                  |            |                |        |                                         |                  |        |        |  |

| Legend:                                                                                          |            |                |        |                                         |                  |        |        |  |

| R = Readable                                                                                     | bit        | W = Writable   | bit    | U = Unimpler                            | mented bit, read | as '0' |        |  |

| -n = Value at POR '1' = Bit is set                                                               |            |                |        | '0' = Bit is cleared x = Bit is unknown |                  |        |        |  |

|                                                                                                  |            |                |        |                                         |                  |        |        |  |

| bit 15-14                                                                                        | Unimplemen | ted: Read as ' | כ'     |                                         |                  |        |        |  |

| bit 13-8 <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits |            |                |        |                                         |                  |        |        |  |

(see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to RP34 Output Pin bits (see Table 10-2 for peripheral function numbers)

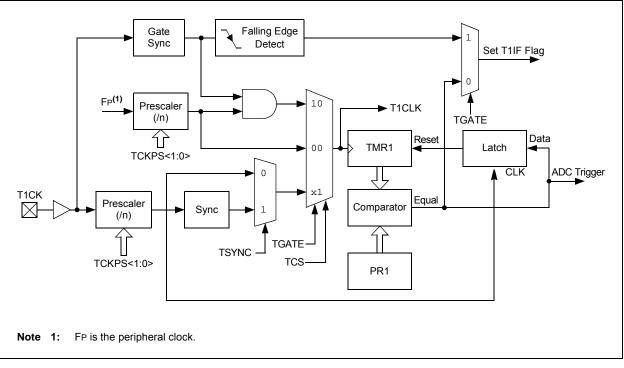

# 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

- A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are provided in Table 11-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | x     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

# TABLE 11-1: TIMER MODE SETTINGS

| REGISTER 16-2: | SPIxCON1: SPIx CONTROL REGISTER 1 |

|----------------|-----------------------------------|

|----------------|-----------------------------------|

| U-0                 | U-0                                                                                                           | U-0                                   | R/W-0                  | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------|----------------------|-----------------------------------------|----------------------|----------------------|--|--|--|--|

| _                   | —                                                                                                             | _                                     | DISSCK                 | DISSDO               | MODE16                                  | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |

| bit 15              |                                                                                                               | ·                                     |                        |                      |                                         |                      | bit                  |  |  |  |  |

| R/W-0               | R/W-0                                                                                                         | R/W-0                                 | R/W-0                  | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |  |  |  |  |

| SSEN <sup>(2)</sup> |                                                                                                               | MSTEN                                 | SPRE2 <sup>(3)</sup>   | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup>                    | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |  |

| bit 7               | ora                                                                                                           | moren                                 | 011122                 | 011121               | 011120                                  |                      | bit                  |  |  |  |  |

|                     |                                                                                                               |                                       |                        |                      |                                         |                      |                      |  |  |  |  |

| Legend:             |                                                                                                               |                                       |                        |                      |                                         |                      |                      |  |  |  |  |

| R = Readable        | e bit                                                                                                         | W = Writable                          | bit                    | U = Unimpler         | mented bit, read                        | d as '0'             |                      |  |  |  |  |

| -n = Value at       | POR                                                                                                           | '1' = Bit is se                       | t                      | '0' = Bit is cle     | ared                                    | x = Bit is unkr      | nown                 |  |  |  |  |

|                     |                                                                                                               |                                       |                        |                      |                                         |                      |                      |  |  |  |  |

| bit 15-13           | -                                                                                                             | nted: Read as                         |                        |                      |                                         |                      |                      |  |  |  |  |

| bit 12              |                                                                                                               | able SCKx Pin                         | •                      |                      | <i>'</i> )                              |                      |                      |  |  |  |  |

|                     |                                                                                                               | SPIx clock is di:<br>SPIx clock is er | •                      | ctions as I/O        |                                         |                      |                      |  |  |  |  |

| bit 11              |                                                                                                               | sable SDOx Pir                        |                        |                      |                                         |                      |                      |  |  |  |  |

|                     |                                                                                                               | n is not used by                      |                        | oin functions as     | s I/O                                   |                      |                      |  |  |  |  |

|                     |                                                                                                               | n is controlled b                     |                        |                      |                                         |                      |                      |  |  |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit                                                                    |                                       |                        |                      |                                         |                      |                      |  |  |  |  |

|                     | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ul> |                                       |                        |                      |                                         |                      |                      |  |  |  |  |

|                     |                                                                                                               | -                                     |                        |                      |                                         |                      |                      |  |  |  |  |

| bit 9               |                                                                                                               | ata Input Sam                         | ole Phase bit          |                      |                                         |                      |                      |  |  |  |  |

|                     | Master Mode                                                                                                   | <u>:</u><br>a is sampled at           | the end of da          | ta output time       |                                         |                      |                      |  |  |  |  |

|                     |                                                                                                               | a is sampled at                       |                        |                      | ne                                      |                      |                      |  |  |  |  |

|                     | Slave Mode:<br>SMP must be                                                                                    | e cleared when                        | SPIx is used i         | n Slave mode.        |                                         |                      |                      |  |  |  |  |

| bit 8               | CKE: SPIx C                                                                                                   | lock Edge Sele                        | ect bit <sup>(1)</sup> |                      |                                         |                      |                      |  |  |  |  |

|                     |                                                                                                               |                                       |                        |                      | clock state to lo<br>ock state to activ |                      |                      |  |  |  |  |

| bit 7               |                                                                                                               | Select Enable                         |                        |                      |                                         | ,                    |                      |  |  |  |  |

|                     |                                                                                                               | s used for Slav                       |                        | is controlled h      | by port function                        |                      |                      |  |  |  |  |

| bit 6               | -                                                                                                             | Polarity Select                       | -                      |                      |                                         |                      |                      |  |  |  |  |

|                     | 1 = Idle state                                                                                                | for clock is a h                      | nigh level; activ      |                      |                                         |                      |                      |  |  |  |  |

| bit 5               |                                                                                                               | ster Mode Enal                        |                        |                      |                                         |                      |                      |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                  | node                                  |                        |                      |                                         |                      |                      |  |  |  |  |

| Note 1: Th          | e CKE bit is not                                                                                              |                                       | d SPI modes. I         | Program this bi      | t to '0' for Fram                       | ed SPI modes (       | FRMEN =              |  |  |  |  |

| 0. Th               |                                                                                                               |                                       |                        |                      |                                         |                      |                      |  |  |  |  |

- **2:** This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0                | R-0   | R-1   |

|----------|--------|----------|-----|-----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV | UTXISEL0 | _   | UTXBRK    | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15   |        |          |     |           |                      |       | bit 8 |

| R/W-0    | R/W-0    | R/W-0 | R-1   | R-0  | R-0  | R/C-0 | R-0   |

|----------|----------|-------|-------|------|------|-------|-------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR | FERR | OERR  | URXDA |

| bit 7    |          |       |       |      |      |       | bit 0 |

| Legend:           | C = Clearable bit | HC = Hardware Clearat | HC = Hardware Clearable bit |  |  |

|-------------------|-------------------|-----------------------|-----------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'               |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown          |  |  |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- $\frac{\text{If IREN} = 0}{1} = \text{UxTX Idle state is } 0$

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- $1 = \text{IrDA}^{\mathbb{R}}$  encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup>

- 1 = Transmit is enabled, UxTX pin is controlled by UARTx

0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

REGISTER 19-9: ADCON5L: ADC CONTROL REGISTER 5 LOW

| R-0, HSC      | U-0                                                                                                               | U-0                              | U-0             | R-0, HSC          | R-0, HSC       | R-0, HSC        | R-0, HSC |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|-------------------|----------------|-----------------|----------|--|--|--|

| SHRRDY        | —                                                                                                                 |                                  |                 | C3RDY             | C2RDY          | C1RDY           | CORDY    |  |  |  |

| bit 15        |                                                                                                                   |                                  |                 |                   |                |                 | bit 8    |  |  |  |

|               |                                                                                                                   |                                  |                 |                   |                |                 |          |  |  |  |

| R/W-0         | U-0                                                                                                               | U-0                              | U-0             | R/W-0             | R/W-0          | R/W-0           | R/W-0    |  |  |  |

| SHRPWR        |                                                                                                                   |                                  |                 | C3PWR             | C2PWR          | C1PWR           | COPWR    |  |  |  |

| bit 7         |                                                                                                                   |                                  |                 |                   |                |                 | bit (    |  |  |  |

| Legend:       |                                                                                                                   | U = Unimplen                     | nented bit, rea | ad as '0'         |                |                 |          |  |  |  |

| R = Readable  | e bit                                                                                                             | W = Writable                     |                 |                   | are Settable/C | learable bit    |          |  |  |  |

| -n = Value at | POR                                                                                                               | '1' = Bit is set                 |                 | '0' = Bit is clea | ared           | x = Bit is unkr | iown     |  |  |  |

|               |                                                                                                                   |                                  |                 | L 14              |                |                 |          |  |  |  |

| bit 15        |                                                                                                                   | ared ADC Core<br>is powered an   |                 |                   |                |                 |          |  |  |  |

|               |                                                                                                                   | is not ready fo                  | • •             | beration          |                |                 |          |  |  |  |

| bit 14-12     |                                                                                                                   | ted: Read as '                   | -               |                   |                |                 |          |  |  |  |

| bit 11        | C3RDY: Dedi                                                                                                       | cated ADC Co                     | e 3 Ready Fl    | ag bit            |                |                 |          |  |  |  |

|               |                                                                                                                   | is powered an<br>is not ready fo |                 | peration          |                |                 |          |  |  |  |

| bit 10        |                                                                                                                   | cated ADC Co                     |                 | aq bit            |                |                 |          |  |  |  |

|               |                                                                                                                   |                                  |                 | •                 |                |                 |          |  |  |  |

|               | <ul><li>1 = ADC core is powered and ready for operation</li><li>0 = ADC core is not ready for operation</li></ul> |                                  |                 |                   |                |                 |          |  |  |  |

| bit 9         | C1RDY: Dedi                                                                                                       | cated ADC Co                     | e 1 Ready Fl    | ag bit            |                |                 |          |  |  |  |

|               |                                                                                                                   | is powered an<br>is not ready fo |                 | peration          |                |                 |          |  |  |  |

| bit 8         |                                                                                                                   | cated ADC Col                    | •               | ag bit            |                |                 |          |  |  |  |

|               | 1 = ADC core                                                                                                      | is powered an<br>is not ready fo | d ready for or  | -                 |                |                 |          |  |  |  |

| bit 7         |                                                                                                                   | nared ADC Cor                    | •               | able bit          |                |                 |          |  |  |  |

|               |                                                                                                                   | e x is powered                   |                 |                   |                |                 |          |  |  |  |

|               | 0 = ADC Core                                                                                                      |                                  |                 |                   |                |                 |          |  |  |  |

| bit 6-4       | Unimplemen                                                                                                        | ted: Read as '                   | )'              |                   |                |                 |          |  |  |  |

| bit 3         | C3PWR: Ded                                                                                                        | icated ADC Co                    | re 3 Power E    | nable bit         |                |                 |          |  |  |  |

|               | 1 = ADC core<br>0 = ADC core                                                                                      |                                  |                 |                   |                |                 |          |  |  |  |

| bit 2         | C2PWR: Ded                                                                                                        | icated ADC Co                    | re 2 Power E    | nable bit         |                |                 |          |  |  |  |

|               | 1 = ADC core                                                                                                      |                                  |                 |                   |                |                 |          |  |  |  |

| bit 1         | 0 = ADC core                                                                                                      | is oπ<br>icated ADC Co           | ro 1 Dowor E    | nabla bit         |                |                 |          |  |  |  |

| DIL           | 1 = ADC core                                                                                                      |                                  |                 |                   |                |                 |          |  |  |  |

|               | 0 = ADC core                                                                                                      |                                  |                 |                   |                |                 |          |  |  |  |

| bit 0         | COPWR: Ded                                                                                                        | icated ADC Co                    | re 0 Power E    | nable bit         |                |                 |          |  |  |  |

|               | 1 = ADC core                                                                                                      |                                  |                 |                   |                |                 |          |  |  |  |

#### REGISTER 19-17: ADEISTATL: ADC EARLY INTERRUPT STATUS REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                 |       |                  | EISTA | AT<15:8>                           |       |                 |       |

| bit 15          |       |                  |       |                                    |       |                 | bit 8 |

|                 |       |                  |       |                                    |       |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                 |       |                  | EIST  | AT<7:0>                            |       |                 |       |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |

| 1               |       |                  |       |                                    |       |                 |       |

| Legend:         |       |                  |       |                                    |       |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at I | POR   | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

bit 15-0 EISTAT<15:0>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

#### REGISTER 19-18: ADEISTATH: ADC EARLY INTERRUPT STATUS REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | _   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|--------|---------|-------|-------|

| —     | —   |       |       | EISTAT | <21:16> |       |       |

| bit 7 |     |       |       |        |         |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 EISTAT<21:16>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

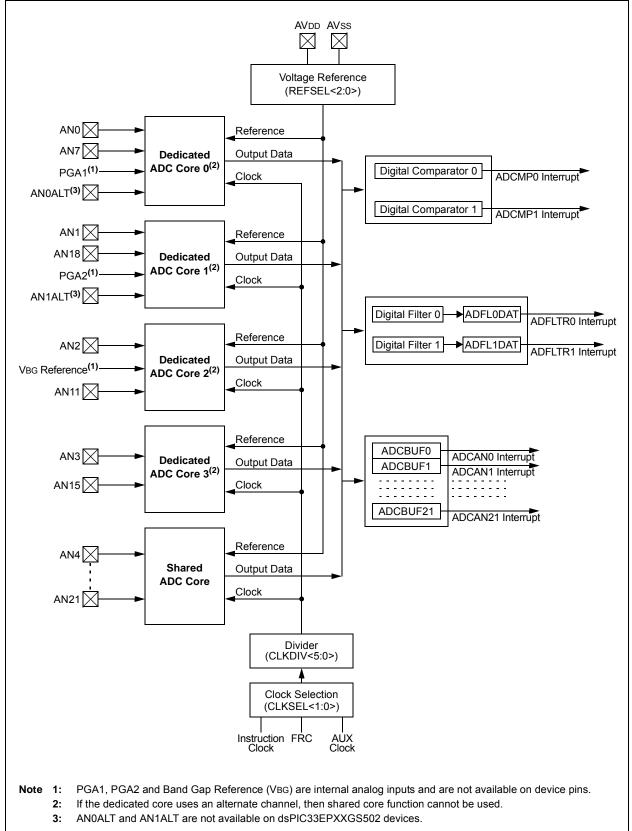

# 23.6 Watchdog Timer (WDT)

For dsPIC33EPXXGS50X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 23.6.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 26-23.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 23-2: WDT BLOCK DIAGRAM

# 23.6.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

## 23.6.3 ENABLING WDT

The WDT is enabled or disabled by the WDTEN<1:0> Configuration bits in the FWDT Configuration register. When the WDTEN<1:0> Configuration bits have been programmed to '0b11', the WDT is always enabled.

The WDT can be optionally controlled in software when the WDTEN<1:0> Configuration bits have been programmed to '0b10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disables the WDT during non-critical segments for maximum power savings.

The WDT Time-out flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 23.6.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

| DC CHARACT       | ERISTICS            |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |            |  |

|------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------|--|

| Parameter<br>No. | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |        |            |  |

| Idle Current (II | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |            |        |            |  |

| DC40d            | 2                   | 4    | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |            |  |

| DC40a            | 2                   | 4    | mA                                                                                                                                                                                                                                                                                      | +25°C      | - 3.3V | 10 MIPS    |  |

| DC40b            | 2                   | 4    | mA                                                                                                                                                                                                                                                                                      | +85°C      | 5.3V   | TO MIES    |  |

| DC40c            | 2                   | 4    | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |            |  |

| DC42d            | 3                   | 6    | mA                                                                                                                                                                                                                                                                                      | -40°C      |        |            |  |

| DC42a            | 3                   | 6    | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V   | 20 MIPS    |  |

| DC42b            | 3                   | 6    | mA                                                                                                                                                                                                                                                                                      | +85°C      |        | 20 10111 3 |  |

| DC42c            | 3                   | 6    | mA                                                                                                                                                                                                                                                                                      | +125°C     |        |            |  |

| DC44d            | 6                   | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C      |        | 40 MIPS    |  |