Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

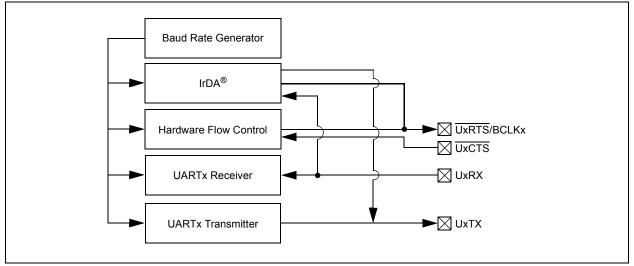

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

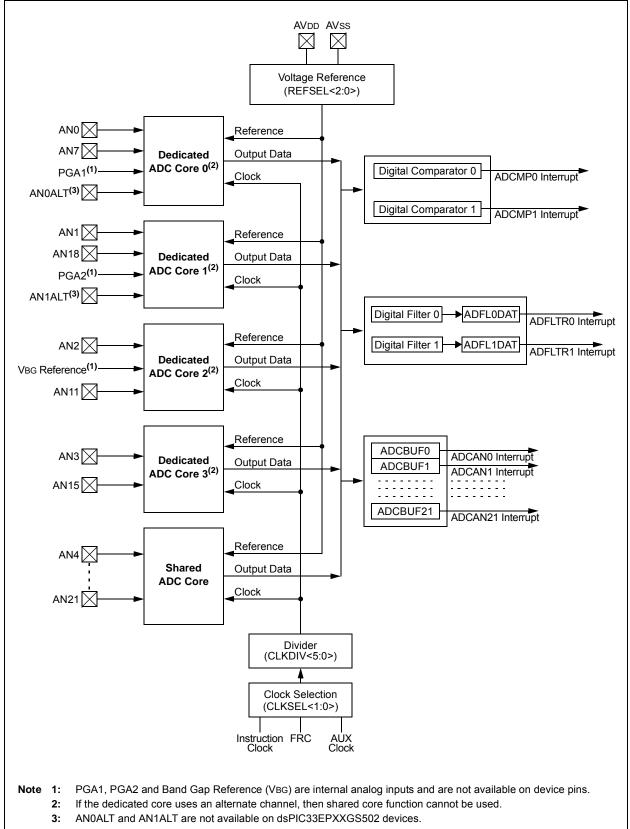

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

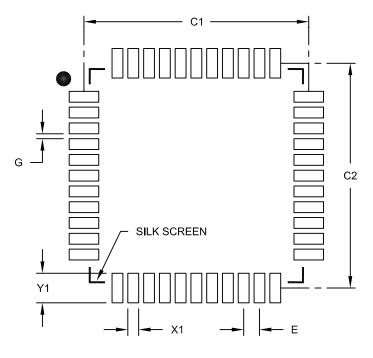

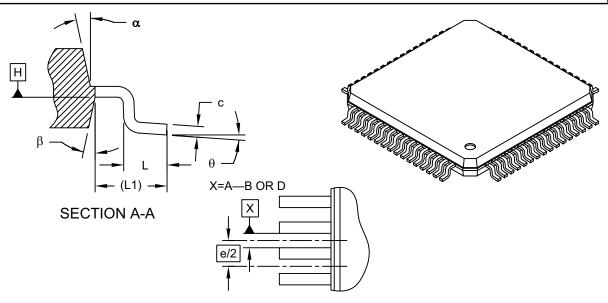

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs504t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

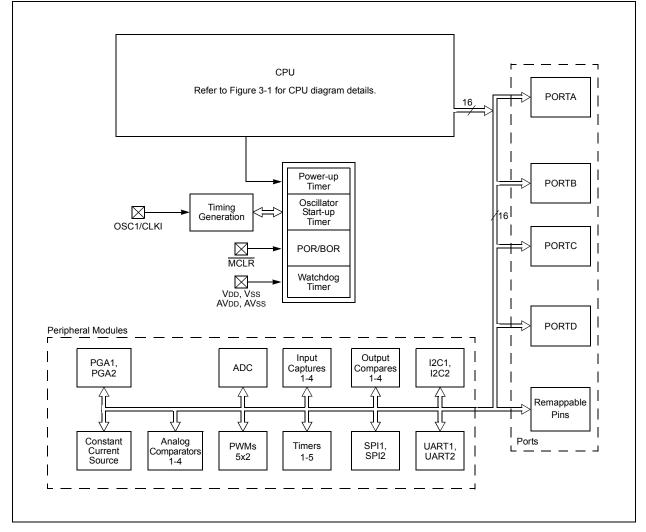

This document contains device-specific information for the dsPIC33EPXXGS50X Digital Signal Controller (DSC) devices.

dsPIC33EPXXGS50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EPXXGS50X FAMILY BLOCK DIAGRAM

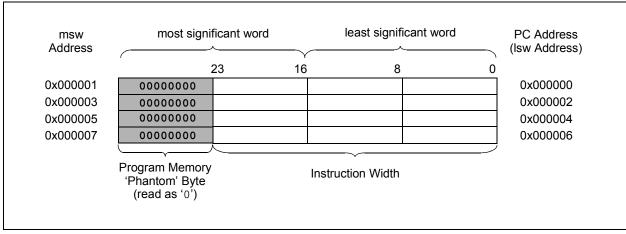

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-5).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented, or decremented, by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXGS50X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

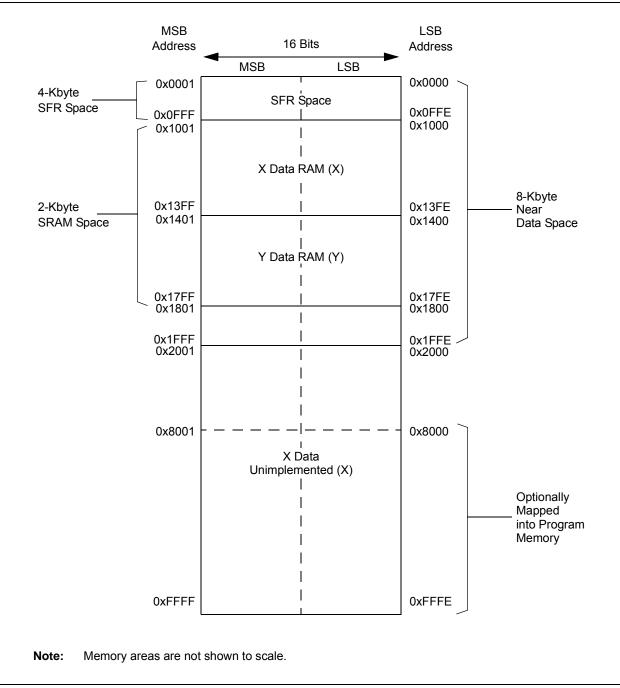

#### FIGURE 4-6: DATA MEMORY MAP FOR dsPIC33EP16GS50X DEVICES

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                   | Bit 14                   | Bit 13                   | Bit 12                   | Bit 11                   | Bit 10                   | Bit 9                    | Bit 8                   | Bit 7                   | Bit 6    | Bit 5    | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0                    | All<br>Resets |

|-------------|-------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------------------------|-------------------------|----------|----------|-----------|-----------|-----------|-----------|--------------------------|---------------|

| IFS0        | 0800  | NVMIF                    | -                        | ADCIF                    | U1TXIF                   | U1RXIF                   | SPI1IF                   | SPI1EIF                  | T3IF                    | T2IF                    | OC2IF    | IC2IF    | -         | T1IF      | OC1IF     | IC1IF     | INTOIF                   | 0000          |

| IFS1        | 0802  | U2TXIF                   | U2RXIF                   | INT2IF                   | T5IF                     | T4IF                     | OC4IF                    | OC3IF                    | -                       | _                       | -        | -        | INT1IF    | CNIF      | AC1IF     | MI2C1IF   | SI2C1IF                  | 0000          |

| IFS2        | 0804  | _                        | -                        | _                        | _                        | _                        | _                        | —                        | -                       | _                       | IC4IF    | IC3IF    | -         | _         | _         | SPI2IF    | SPI2EIF                  | 0000          |

| IFS3        | 0806  | _                        | _                        | _                        | _                        | _                        | _                        | PSEMIF                   | _                       | _                       | INT4IF   | _        | _         | _         | MI2C2IF   | SI2C2IF   | -                        | 0000          |

| IFS4        | 0808  | -                        | -                        | -                        | -                        | -                        | -                        | PSESIF                   | -                       | -                       | -        | -        | -         | -         | U2EIF     | U1EIF     | -                        | 0000          |

| IFS5        | 080A  | PWM2IF                   | PWM1IF                   | _                        | _                        | _                        | _                        | _                        | _                       |                         | _        | _        | _         | _         | -         | -         | -                        | 0000          |

| IFS6        | 080C  | ADCAN1IF                 | ADCAN0IF                 | —                        | _                        | _                        | _                        | AC4IF                    | AC3IF                   | AC2IF                   |          | _        | _         | _         | PWM5IF    | PWM4IF    | PWM3IF                   | 0000          |

| IFS7        | 080E  | -                        | -                        | -                        | -                        | -                        | -                        | -                        | -                       | -                       | -        | ADCAN7IF | ADCAN6IF  | ADCAN5IF  | ADCAN4IF  | ADCAN3IF  | ADCAN2IF                 | 0000          |

| IFS8        | 0810  | JTAGIF                   | ICDIF                    | -                        | -                        | -                        | -                        | -                        | -                       | -                       | -        | -        | -         | -         | -         | -         | -                        | 0000          |

| IFS9        | 0812  | ADCAN16IF <sup>(1)</sup> | ADCAN15IF <sup>(1)</sup> | ADCAN14IF <sup>(2)</sup> | ADCAN13IF(1)             | ADCAN12IF <sup>(2)</sup> | ADCAN11IF <sup>(2)</sup> | ADCAN10IF <sup>(2)</sup> | ADCAN9IF <sup>(2)</sup> | ADCAN8IF <sup>(2)</sup> | _        | _        | _         | _         | -         | -         | -                        | 0000          |

| IFS10       | 0814  | -                        | I2C2BCIF                 | I2C1BCIF                 | -                        | -                        | _                        | -                        | -                       | _                       | -        | -        | ADCAN21IF | ADCAN20IF | ADCAN19IF | ADCAN18IF | ADCAN17IF <sup>(2)</sup> | 0000          |

| IFS11       | 0816  | _                        | -                        | _                        | _                        | _                        | _                        | _                        | -                       | _                       | _        | _        | ADFLTR1IF | ADFLTR0IF | ADCMP1IF  | ADCMP0IF  | -                        | 0000          |

| IEC0        | 0820  | NVMIE                    | -                        | ADCIE                    | U1TXIE                   | U1RXIE                   | SPI1IE                   | SPI1EIE                  | T3IE                    | T2IE                    | OC2IE    | IC2IE    | -         | T1IE      | OC1IE     | IC1IE     | INTOIE                   | 0000          |

| IEC1        | 0822  | U2TXIE                   | U2RXIE                   | INT2IE                   | T5IE                     | T4IE                     | OC4IE                    | OC3IE                    | -                       | _                       | _        | -        | INT1IE    | CNIE      | AC1IF     | MI2C1IE   | SI2C1IE                  | 0000          |

| IEC2        | 0824  | _                        | _                        | _                        | _                        | _                        | _                        | _                        | _                       | _                       | IC4IE    | IC3IE    | -         | _         | _         | SPI2IE    | SPI2EIE                  | 0000          |

| IEC3        | 0826  | _                        | _                        | _                        | _                        | _                        | _                        | PSEMIE                   | _                       | _                       | INT4IE   | _        | -         | _         | MI2C2IE   | SI2C2IE   | -                        | 0000          |

| IEC4        | 0828  | _                        | _                        | _                        | -                        | _                        | _                        | PSESIE                   | -                       | _                       | _        | _        | -         | -         | U2EIE     | U1EIE     | -                        | 0000          |

| IEC5        | 082A  | PWM2IE                   | PWM1IE                   | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC6        | 082C  | ADCAN1IE                 | ADCAN0IE                 | _                        | _                        | _                        | _                        | AC4IE                    | AC3IE                   | AC2IE                   | _        | _        | -         | _         | PWM5IE    | PWM4IE    | PWM3IE                   | 0000          |

| IEC7        | 082E  | _                        | _                        | _                        | -                        | _                        | _                        | _                        | -                       | _                       | _        | ADCAN7IE | ADCAN6IE  | ADCAN5IE  | ADCAN4IE  | ADCAN3IE  | ADCAN2IE                 | 0000          |

| IEC8        | 0830  | JTAGIE                   | ICDIE                    | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC9        | 0832  | ADCAN16IE <sup>(1)</sup> | ADCAN15IE <sup>(1)</sup> | ADCAN14IE <sup>(2)</sup> | ADCAN13IE <sup>(1)</sup> | ADCAN12IE <sup>(2)</sup> | ADCAN11IE <sup>(2)</sup> | ADCAN10IE <sup>(2)</sup> | ADCAN9IE <sup>(2)</sup> | ADCAN8IE <sup>(2)</sup> | _        | _        | -         | _         | _         | _         | -                        | 0000          |

| IEC10       | 0834  | _                        | I2C2BCIE                 | I2C1BCIE                 | -                        | _                        | _                        | _                        | -                       | _                       | _        | _        | ADCAN21IE | ADCAN20IE | ADCAN19IE | ADCAN18IE | ADCAN17IE <sup>(2)</sup> | 0000          |

| IEC11       | 0836  | _                        | _                        | _                        | _                        | _                        | _                        | _                        | _                       | _                       | _        | _        | ADFLTR1IE | ADFLTR0IE | ADCMP1IE  | ADCMP0IE  | -                        | 0000          |

| IPC0        | 0840  | _                        | T1IP2                    | T1IP1                    | T1IP0                    | _                        | OC1IP2                   | OC1IP1                   | OC1IP0                  | _                       | IC1IP2   | IC1IP1   | IC1IP0    | -         | INT0IP2   | INT0IP1   | INT0IP0                  | 4444          |

| IPC1        | 0842  | -                        | T2IP2                    | T2IP1                    | T2IP0                    | -                        | OC2IP2                   | OC2IP1                   | OC2IP0                  | _                       | IC2IP2   | IC2IP1   | IC2IP0    | -         | -         | -         | -                        | 4440          |

| IPC2        | 0844  | _                        | U1RXIP2                  | U1RXIP1                  | U1RXIP0                  | _                        | SPI1IP2                  | SPI1IP1                  | SPI1IP0                 | _                       | SPI1EIP2 | SPI1EIP1 | SPI1EIP0  | -         | T3IP2     | T3IP1     | T3IP0                    | 4444          |

| IPC3        | 0846  | _                        | NVMIP2                   | NVMIP1                   | NVMIP0                   | _                        | _                        | _                        | _                       | _                       | ADCIP2   | ADCIP1   | ADCIP0    | -         | U1TXIP2   | U1TXIP1   | U1TXIP0                  | 4044          |

| IPC4        | 0848  | _                        | CNIP2                    | CNIP1                    | CNIP0                    | _                        | AC1IP2                   | AC1IP1                   | AC1IP0                  | _                       | MI2C1IP2 | MI2C1IP1 | MI2C1IP0  | -         | SI2C1IP2  | SI2C1IP1  | SI2C1IP0                 | 4444          |

| IPC5        | 084A  | _                        | -                        | _                        | -                        | _                        | -                        | -                        | —                       | _                       | —        | -        | -         | -         | INT1IP2   | INT1IP1   | INT1IP0                  | 0004          |

| IPC6        | 084C  | _                        | T4IP2                    | T4IP1                    | T4IP0                    | _                        | OC4IP2                   | OC4IP1                   | OC4IP0                  | _                       | OC3IP2   | OC3IP1   | OC3IP0    | -         | -         | -         | -                        | 4440          |

| IPC7        | 084E  | _                        | U2TXIP2                  | U2TXIP1                  | U2TXIP0                  | _                        | U2RXIP2                  | U2RXIP1                  | U2RXIP0                 | _                       | INT2IP2  | INT2IP1  | INT2IP0   | _         | T5IP2     | T5IP1     | T5IP0                    | 4444          |

| IPC8        | 0850  | _                        | -                        | _                        | -                        | _                        | _                        | -                        | -                       | _                       | SPI2IP2  | SPI2IP1  | SPI2IP0   | -         | SPI2EIP2  | SPI2EIP1  | SPI2EIP0                 | 0044          |

| IPC9        | 0852  | _                        | _                        | _                        | _                        | _                        | IC4IP2                   | IC4IP1                   | IC4IP0                  | _                       | IC3IP2   | IC3IP1   | IC3IP0    | _         | _         | _         | _                        | 0440          |

Legend:

Note 1:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal. Only available on dsPIC33EPXXGS506 devices. Only available on dsPIC33EPXXGS504/505 and dsPIC33EPXXGS506 devices.

2:

#### TABLE 4-21: NVM REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                                            | Bit 13 | Bit 12  | Bit 11 | Bit 10  | Bit 9 | Bit 8   | Bit 7                                                          | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|-------------------------------------------------------------------|--------|---------|--------|---------|-------|---------|----------------------------------------------------------------|-------|-------|-------|-----------|--------|--------|--------|---------------|

| NVMCON      | 0728  | WR     | WREN                                                              | WRERR  | NVMSIDL | SFTSWP | P2ACTIV | RPDF  | URERR   | —                                                              | —     | —     | —     | NVMOP3    | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        |                                                                   |        |         |        |         |       | NVMADR< | 15:0>                                                          |       |       |       |           |        |        |        | 0000          |

| NVMADRU     | 072C  | -      | _                                                                 | _      | _       |        | _       | _     | _       |                                                                |       |       | NVMAD | )R<23:16> |        |        |        | 0000          |

| NVMKEY      | 072E  | -      | _                                                                 | _      | _       |        | _       | _     | _       |                                                                |       |       | NVMK  | (EY<7:0>  |        |        |        | 0000          |

| NVMSRCADR   | 0730  |        | NVM Source Data Address Register, Lower Word (NVMSRCADR<15:0>) 00 |        |         |        |         |       |         |                                                                |       |       | 0000  |           |        |        |        |               |

| NVMSRCADRH  | 0732  | _      | —                                                                 | _      | —       | _      | _       | —     | _       | NVM Source Data Address Register, Upper Byte (NVMSRCADR<23:16> |       |       |       |           |        |        | 0000   |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9     | Bit 8         | Bit 7    | Bit 6    | Bit 5  | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|-----------|-----------|---------------|----------|----------|--------|----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR | _       | —      | VREGSF | _         | CM        | VREGS         | EXTR     | SWR      | SWDTEN | WDTO     | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | -      | COSC2  | COSC1   | COSC0  | _      | NOSC2     | NOSC1     | NOSC0         | CLKLOCK  | IOLOCK   | LOCK   | _        | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1   | DOZE0  | DOZEN  | FRCDIV2   | FRCDIV1   | FRCDIV0       | PLLPOST1 | PLLPOST0 | _      | PLLPRE4  | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 3040          |

| PLLFBD      | 0746  | -      |        | _       | _      | _      | _         | _         |               |          |          | PLL    | DIV<8:0> |         |         |         |         | 0030          |

| OSCTUN      | 0748  | -      |        | _       | _      | _      | _         | _         | _             | _        | _        |        |          | TUN     | <5:0>   |         |         | 0000          |

| LFSR        | 074C  | -      |        |         |        |        |           |           | LFSR<14:0> 00 |          |          |        |          |         |         | 0000    |         |               |

| REFOCON     | 074E  | ROON   |        | ROSSLP  | ROSEL  | RODIV3 | RODIV2    | RODIV1    | RODIV0        | _        | _        | _      | _        | _       | _       | _       | _       | 0000          |

| ACLKCON     | 0750  | ENAPLL | APLLCK | SELACLK | _      | _      | APSTSCLR2 | APSTSCLR1 | APSTSCLR0     | ASRCSEL  | FRCSEL   | —      | _        | _       | _       | _       | _       | 2740          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

| R/W-0           | R/W-0                                                                | R/W-0                                                                                                                              | R/W-0                                      | R/W-0            | R/W-0           | R/W-0              | R/W-0  |  |

|-----------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|-----------------|--------------------|--------|--|

| FLT2R7          | FLT2R6                                                               | FLT2R5                                                                                                                             | FLT2R4                                     | FLT2R3           | FLT2R2          | FLT2R1             | FLT2R0 |  |

| bit 15          |                                                                      |                                                                                                                                    |                                            |                  |                 |                    | bit 8  |  |

|                 |                                                                      |                                                                                                                                    |                                            |                  |                 |                    |        |  |

| R/W-0           | R/W-0                                                                | R/W-0                                                                                                                              | R/W-0                                      | R/W-0            | R/W-0           | R/W-0              | R/W-0  |  |

| FLT1R7          | FLT1R6                                                               | FLT1R5                                                                                                                             | FLT1R4                                     | FLT1R3           | FLT1R2          | FLT1R1             | FLT1R0 |  |

| bit 7           |                                                                      |                                                                                                                                    |                                            |                  |                 |                    | bit (  |  |

|                 |                                                                      |                                                                                                                                    |                                            |                  |                 |                    |        |  |

| Legend:         |                                                                      |                                                                                                                                    |                                            |                  |                 |                    |        |  |

| R = Readable    |                                                                      | W = Writable                                                                                                                       |                                            | •                | nented bit, rea |                    |        |  |

| -n = Value at I | POR                                                                  | '1' = Bit is set                                                                                                                   |                                            | '0' = Bit is cle | ared            | x = Bit is unknown |        |  |

| bit 7-0         | 10110100 =<br>000000001 =<br>00000000 =<br>FLT1R<7:0>:<br>10110101 = | Input tied to RI<br>Input tied to RI<br>Input tied to RI<br>Input tied to Vs<br>Assign PWM<br>Input tied to RI<br>Input tied to RI | ⊃180<br>⊃1<br>SS<br>Fault 1 (FLT1)<br>⊃181 | to the Corresp   | oonding RPn Pi  | in bits            |        |  |

|                 |                                                                      | Input tied to RI<br>Input tied to Ve                                                                                               |                                            |                  |                 |                    |        |  |

### REGISTER 10-8: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

| R/W-0         |        |                  |        |                  |                  |          |        |

|---------------|--------|------------------|--------|------------------|------------------|----------|--------|

|               | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0    | R/W-0  |

| FLT8R7        | FLT8R6 | FLT8R5           | FLT8R4 | FLT8R3           | FLT8R2           | FLT8R1   | FLT8R0 |

| bit 15        |        |                  |        |                  |                  |          | bit 8  |

|               |        |                  |        |                  |                  |          |        |

| R/W-0         | R/W-0  | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0    | R/W-0  |

| FLT7R7        | FLT7R6 | FLT7R5           | FLT7R4 | FLT7R3           | FLT7R2           | FLT7R1   | FLT7R0 |

| bit 7         |        |                  |        |                  |                  |          | bit C  |

|               |        |                  |        |                  |                  |          |        |

| Legend:       |        |                  |        |                  |                  |          |        |

| R = Readable  | e bit  | W = Writable     | bit    | U = Unimpler     | nented bit, read | d as '0' |        |

| -n = Value at | POR    | '1' = Bit is set | :      | '0' = Bit is cle | x = Bit is unkr  | nown     |        |

| bit 15-8      |        | Assign PWM       | · · ·  | to the Corresp   | onding RPn Pi    | n bits   |        |

### REGISTER 10-19: RPINR43: PERIPHERAL PIN SELECT INPUT REGISTER 43

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP45R5 | RP45R4 | RP45R3 | RP45R2 | RP45R1 | RP45R0 |

| bit 15 | ·   |        | •      |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| _      |     | RP44R5 | RP44R4 | RP44R3 | RP44R2 | RP44R1 | RP44R0 |

| bit 0 |

|-------|

|-------|

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP45R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP45 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP44R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP44 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-27: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | RP47R5 | RP47R4 | RP47R3 | RP47R2 | RP47R1 | RP47R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP46R5 | RP46R4 | RP46R3 | RP46R2 | RP46R1 | RP46R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

|         |     |        |        |        |        |        |        |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RP47R<5:0>:** Peripheral Output Function is Assigned to RP47 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP46R<5:0>:** Peripheral Output Function is Assigned to RP46 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-28: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| —    —    RP49R5    RP49R4    RP49R3    RP49R2    RP49R1    RP4      bit 15    U-0    U-0    R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |            |                  |        |                  |                  |                 |        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|------------------|--------|------------------|------------------|-----------------|--------|--|

| bit 15U-0U-0R/W-0R/W-0R/W-0R/W-0R/W-0———RP48R5RP48R4RP48R3RP48R2RP48R1RP4bit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>'0' = Bit is clearedx = Bit is unknownbit 15-14Unimplemented: Read as '0'<br>bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits<br>(see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

| U-0U-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0RP48R5RP48R4RP48R3RP48R2RP48R1RP4bit 7Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15-14Unimplemented: Read as '0'bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                  | —          | RP49R5           | RP49R4 | RP49R3           | RP49R2           | RP49R1          | RP49R0 |  |

| —  —  RP48R5  RP48R4  RP48R3  RP48R2  RP48R1  RP4    bit 7    Legend:  R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'  bit 13-8  RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 15                             | -          |                  |        |                  |                  |                 | bit 8  |  |

| —  —  RP48R5  RP48R4  RP48R3  RP48R2  RP48R1  RP4    bit 7    Legend:  R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'  bit 13-8  RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |            |                  |        |                  |                  |                 |        |  |

| bit 7    Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'    bit 13-8  RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |

| Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'    bit 13-8  RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    | —          | RP48R5           | RP48R4 | RP48R3           | RP48R2           | RP48R1          | RP48R0 |  |

| R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'    bit 13-8  RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7                              |            | •                | -      |                  |                  | •               | bit 0  |  |

| R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'    bit 13-8  RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |            |                  |        |                  |                  |                 |        |  |

| -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-14  Unimplemented: Read as '0'  Image: Second Se | Legend:                            |            |                  |        |                  |                  |                 |        |  |

| bit 15-14Unimplemented: Read as '0'bit 13-8RP49R<5:0>: Peripheral Output Function is Assigned to RP49 Output Pin bits<br>(see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R = Readable                       | bit        | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |  |

| bit 13-8 <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -n = Value at F                    | POR        | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unki | nown   |  |

| bit 13-8 <b>RP49R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP49 Output Pin bits (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |            |                  |        |                  |                  |                 |        |  |

| (see Table 10-2 for peripheral function numbers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 15-14                          | Unimplemen | ted: Read as '   | 0'     |                  |                  |                 |        |  |

| bit 7-6 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                    |            |                  |        |                  |                  |                 |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7-6 Unimplemented: Read as '0' |            |                  |        |                  |                  |                 |        |  |

bit 5-0 **RP48R<5:0>:** Peripheral Output Function is Assigned to RP48 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-29: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0             | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|------------|------------------|--------|------------------|------------------|-----------------|--------|

| —               | —          | RP51R5           | RP51R4 | RP51R3           | RP51R2           | RP51R1          | RP51R0 |

| bit 15          |            |                  |        |                  |                  | -<br>-          | bit 8  |

|                 |            |                  |        |                  |                  |                 |        |

| U-0             | U-0        | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —               | —          | RP50R5           | RP50R4 | RP50R3           | RP50R2           | RP50R1          | RP50R0 |

| bit 7           | •          |                  |        | ·                |                  |                 | bit 0  |

|                 |            |                  |        |                  |                  |                 |        |

| Legend:         |            |                  |        |                  |                  |                 |        |

| R = Readable    | bit        | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at P | OR         | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|                 |            |                  |        |                  |                  |                 |        |

| bit 15-14       | Unimplemen | ted: Read as '   | )'     |                  |                  |                 |        |

bit 13-8 **RP51R<5:0>:** Peripheral Output Function is Assigned to RP51 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP50R<5:0>:** Peripheral Output Function is Assigned to RP50 Output Pin bits (see Table 10-2 for peripheral function numbers)

| <b>REGISTER 12-2:</b> | TyCON: ( | (TIMER3 AND TIMERS | 5) CONTROL REGISTER |

|-----------------------|----------|--------------------|---------------------|

|-----------------------|----------|--------------------|---------------------|

| R/W-0              | U-0                                      | R/W-0                        | U-0                     | U-0                          | U-0             | U-0                  | U-0            |

|--------------------|------------------------------------------|------------------------------|-------------------------|------------------------------|-----------------|----------------------|----------------|

| TON <sup>(1)</sup> | _                                        | TSIDL <sup>(2)</sup>         | —                       |                              | _               | _                    | _              |

| bit 15             |                                          |                              |                         |                              |                 |                      | bit            |

| U-0                | R/W-0                                    | R/W-0                        | R/W-0                   | U-0                          | U-0             | R/W-0                | U-0            |

| _                  | TGATE <sup>(1)</sup>                     | TCKPS1 <sup>(1)</sup>        | TCKPS0 <sup>(1)</sup>   | _                            | _               | TCS <sup>(1,3)</sup> | _              |

| bit 7              |                                          |                              |                         |                              |                 |                      | bit            |

| Legend:            |                                          |                              |                         |                              |                 |                      |                |

| R = Readab         | le hit                                   | W = Writable                 | hit                     |                              | mented bit, rea | ad as 'O'            |                |

| -n = Value a       |                                          | '1' = Bit is set             |                         | '0' = Bit is cle             |                 | x = Bit is unkno     |                |

|                    | IFOR                                     | I – Dit is set               |                         |                              | areu            |                      | JWII           |

| bit 15             | TON: Timery                              | On bit <sup>(1)</sup>        |                         |                              |                 |                      |                |

|                    | 1 = Starts 16-                           | -bit Timery                  |                         |                              |                 |                      |                |

|                    | 0 = Stops 16-                            | bit Timery                   |                         |                              |                 |                      |                |

| bit 14             |                                          | ted: Read as '               |                         |                              |                 |                      |                |

| oit 13             | TSIDL: Time                              | ry Stop in Idle M            | lode bit <sup>(2)</sup> |                              |                 |                      |                |

|                    |                                          | ues module op                |                         |                              | dle mode        |                      |                |

|                    |                                          | s module opera               |                         | ode                          |                 |                      |                |

| bit 12-7           | -                                        | ted: Read as '               |                         | (4)                          |                 |                      |                |

| bit 6              |                                          | ery Gated Time               | Accumulation            | Enable bit <sup>(1)</sup>    |                 |                      |                |

|                    | When TCS =<br>This bit is ign            |                              |                         |                              |                 |                      |                |

|                    | When TCS =                               |                              |                         |                              |                 |                      |                |

|                    |                                          | <u>o.</u><br>ne accumulatior | n is enabled            |                              |                 |                      |                |

|                    |                                          | ne accumulation              |                         |                              |                 |                      |                |

| bit 5-4            | TCKPS<1:0>                               | : Timery Input               | Clock Prescal           | e Select bits <sup>(1)</sup> |                 |                      |                |

|                    | 11 <b>= 1:256</b>                        |                              |                         |                              |                 |                      |                |

|                    | 10 = 1:64                                |                              |                         |                              |                 |                      |                |

|                    | 01 = 1:8<br>00 = 1:1                     |                              |                         |                              |                 |                      |                |

| bit 3-2            |                                          | ted: Read as '               | ר'                      |                              |                 |                      |                |

| bit 1              | -                                        | Clock Source S               |                         |                              |                 |                      |                |

|                    |                                          | clock is from pir            |                         | e risina edae)               |                 |                      |                |

|                    | 0 = Internal c                           |                              |                         |                              |                 |                      |                |

| bit 0              | Unimplemen                               | ted: Read as '               | כי                      |                              |                 |                      |                |

|                    | Vhen 32-bit opera<br>unctions are set tl |                              |                         | 1), these bits               | have no effec   | t on Timery opera    | tion; all time |

|                    | When 32-bit timer                        | •                            |                         | · · · · <del>·</del>         |                 |                      |                |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all devices. See the "Pin Diagrams" section for the available pins.

## **REGISTER 15-17: DTRx: PWMx DEAD-TIME REGISTER (x = 1 to 5)**

| U-0                                                                      | U-0   | R/W-0            | R/W-0      | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------------------------------------------------------------------|-------|------------------|------------|-----------------------------------------|-------|-------|-------|--|--|--|

| —                                                                        | —     |                  | DTRx<13:8> |                                         |       |       |       |  |  |  |

| bit 15                                                                   |       | ·                |            |                                         |       |       | bit 8 |  |  |  |

| R/W-0                                                                    | R/W-0 | R/W-0            | R/W-0      | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                                                                          |       |                  | DTF        | Rx<7:0>                                 |       |       |       |  |  |  |

| bit 7                                                                    |       |                  |            |                                         |       |       | bit 0 |  |  |  |