Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-TQFP Exposed Pad                                                              |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs505t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

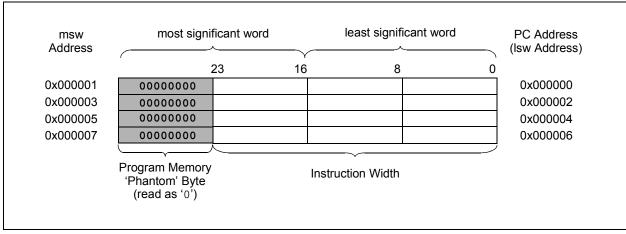

#### 4.2.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-5).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented, or decremented, by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.2.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXGS50X family devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-5: PROGRAM MEMORY ORGANIZATION

# 4.5.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible, regardless of the contents of the Data Space Page register. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space in combination with DSRPAG = 0x00. Consequently, DSRPAG is initialized to 0x001 at Reset.

- Note 1: DSRPAG should not be used to access Page 0. An EDS access with DSRPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSRPAG in software has no effect.

The remaining PSV pages are only accessible using the DSRPAG register in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

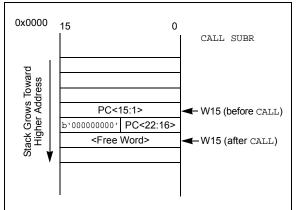

### 4.5.3 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP), and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXGS50X devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-11 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes). When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-11. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

### FIGURE 4-11: CALL STACK FRAME

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS7000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXGS50X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXGS50X family CPU.

The interrupt controller has the following features:

- Six processor exceptions and software traps

- · Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

- Alternate Interrupt Vector Table (AIVT) for debug support

# 7.1 Interrupt Vector Table

The dsPIC33EPXXGS50X family Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains six non-maskable trap vectors and up to 246 sources of interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-2, is available only when the Boot Segment is defined and the AIVT has been enabled. To enable the Alternate Interrupt Vector Table, the Configuration bit, AIVTDIS in the FSEC register, must be programmed and the AIVTEN bit must be set (INTCON2<8> = 1). When the AIVT is enabled, all interrupt and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment, defined by BSLIM<12:0>. The second half of the page is no longer usable space. The Boot Segment must be at least 2 pages to enable the AIVT.

Note: Although the Boot Segment must be enabled in order to enable the AIVT, application code does not need to be present inside of the Boot Segment. The AIVT (and IVT) will inherit the Boot Segment code protection.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXGS50X family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# TABLE 7-1: INTERRUPT VECTOR DETAILS

|                                      | Vector | IRQ       |                     | Interrupt Bit Location |          |             |  |

|--------------------------------------|--------|-----------|---------------------|------------------------|----------|-------------|--|

| Interrupt Source                     | #      | #         | IVT Address         | Flag                   | Enable   | Priority    |  |

|                                      | Hi     | ghest Nat | ural Order Priority | •                      |          |             |  |

| INT0 – External Interrupt 0          | 8      | 0         | 0x000014            | IFS0<0>                | IEC0<0>  | IPC0<2:0>   |  |

| IC1 – Input Capture 1                | 9      | 1         | 0x000016            | IFS0<1>                | IEC0<1>  | IPC0<6:4>   |  |

| OC1 – Output Compare 1               | 10     | 2         | 0x000018            | IFS0<2>                | IEC0<2>  | IPC0<10:8>  |  |

| T1 – Timer1                          | 11     | 3         | 0x00001A            | IFS0<3>                | IEC0<3>  | IPC0<14:12> |  |

| Reserved                             | 12     | 4         | 0x00001C            | _                      | _        | _           |  |

| IC2 – Input Capture 2                | 13     | 5         | 0x00001E            | IFS0<5>                | IEC0<5>  | IPC1<6:4>   |  |

| OC2 – Output Compare 2               | 14     | 6         | 0x000020            | IFS0<6>                | IEC0<6>  | IPC1<10:8>  |  |

| T2 – Timer2                          | 15     | 7         | 0x000022            | IFS0<7>                | IEC0<7>  | IPC1<14:12> |  |

| T3 – Timer3                          | 16     | 8         | 0x000024            | IFS0<8>                | IEC0<8>  | IPC2<2:0>   |  |

| SPI1E – SPI1 Error                   | 17     | 9         | 0x000026            | IFS0<9>                | IEC0<9>  | IPC2<6:4>   |  |

| SPI1 – SPI1 Transfer Done            | 18     | 10        | 0x000028            | IFS0<10>               | IEC0<10> | IPC2<10:8>  |  |

| U1RX – UART1 Receiver                | 19     | 11        | 0x00002A            | IFS0<11>               | IEC0<11> | IPC2<14:12> |  |

| U1TX – UART1 Transmitter             | 20     | 12        | 0x00002C            | IFS0<12>               | IEC0<12> | IPC3<2:0>   |  |

| ADC – ADC Global Convert Done        | 21     | 13        | 0x00002E            | IFS0<13>               | IEC0<13> | IPC3<6:4>   |  |

| Reserved                             | 22     | 14        | 0x000030            | _                      | _        | _           |  |

| NVM – NVM Write Complete             | 23     | 15        | 0x000032            | IFS0<15>               | IEC0<15> | IPC3<14:12> |  |

| SI2C1 – I2C1 Slave Event             | 24     | 16        | 0x000034            | IFS1<0>                | IEC1<0>  | IPC4<2:0>   |  |

| MI2C1 – I2C1 Master Event            | 25     | 17        | 0x000036            | IFS1<1>                | IEC1<1>  | IPC4<6:4>   |  |

| CMP1 – Analog Comparator 1 Interrupt | 26     | 18        | 0x000038            | IFS1<2>                | IEC1<2>  | IPC4<10:8>  |  |

| CN – Input Change Interrupt          | 27     | 19        | 0x00003A            | IFS1<3>                | IEC1<3>  | IPC4<14:12> |  |

| INT1 – External Interrupt 1          | 28     | 20        | 0x00003C            | IFS1<4>                | IEC1<4>  | IPC5<2:0>   |  |

| Reserved                             | 29-32  | 21-24     | 0x00003E-0x000044   | _                      | _        | _           |  |

| OC3 – Output Compare 3               | 33     | 25        | 0x000046            | IFS1<9>                | IEC1<9>  | IPC6<6:4>   |  |

| OC4 – Output Compare 4               | 34     | 26        | 0x000048            | IFS1<10>               | IEC1<10> | IPC6<10:8>  |  |

| T4 – Timer4                          | 35     | 27        | 0x00004A            | IFS1<11>               | IEC1<11> | IPC6<14:12> |  |

| T5 – Timer5                          | 36     | 28        | 0x00004C            | IFS1<12>               | IEC1<12> | IPC7<2:0>   |  |

| INT2 – External Interrupt 2          | 37     | 29        | 0x00004E            | IFS1<13>               | IEC1<13> | IPC7<6:4>   |  |

| U2RX – UART2 Receiver                | 38     | 30        | 0x000050            | IFS1<14>               | IEC1<14> | IPC7<10:8>  |  |

| U2TX – UART2 Transmitter             | 39     | 31        | 0x000052            | IFS1<15>               | IEC1<15> | IPC7<14:12> |  |

| SPI2E – SPI2 Error                   | 40     | 32        | 0x000054            | IFS2<0>                | IEC2<0>  | IPC8<2:0>   |  |

| SPI2 – SPI2 Transfer Done            | 41     | 33        | 0x000056            | IFS2<1>                | IEC2<1>  | IPC8<6:4>   |  |

| Reserved                             | 42-44  | 34-36     | 0x000058-0x00005C   | —                      | _        | _           |  |

| IC3 – Input Capture 3                | 45     | 37        | 0x00005E            | IFS2<5>                | IEC2<5>  | IPC9<6:4>   |  |

| IC4 – Input Capture 4                | 46     | 38        | 0x000060            | IFS2<6>                | IEC2<6>  | IPC9<10:8>  |  |

| Reserved                             | 47-56  | 39-48     | 0x000062-0x000074   | _                      | _        | _           |  |

| SI2C2 – I2C2 Slave Event             | 57     | 49        | 0x000076            | IFS3<1>                | IEC3<1>  | IPC12<6:4>  |  |

| MI2C2 – I2C2 Master Event            | 58     | 50        | 0x000078            | IFS3<2>                | IEC3<2>  | IPC12<10:8> |  |

| Reserved                             | 59-61  | 51-53     | 0x00007A-0x00007E   | _                      | _        | _           |  |

| INT4 – External Interrupt 4          | 62     | 54        | 0x000080            | IFS3<6>                | IEC3<6>  | IPC13<10:8> |  |

| Reserved                             | 63-64  | 55-54     | 0x000082-0x000084   | —                      |          | _           |  |

| PSEM – PWM Special Event Match       | 65     | 57        | 0x000086            | IFS3<9>                | IEC3<9>  | IPC14<6:4>  |  |

| Reserved                             | 66-72  | 58-64     | 0x000088-0x000094   | —                      |          | _           |  |

| U1E – UART1 Error Interrupt          | 73     | 65        | 0x000096            | IFS4<1>                | IEC4<1>  | IPC16<6:4>  |  |

| U2E – UART2 Error Interrupt          | 74     | 66        | 0x000098            | IFS4<2>                | IEC4<2>  | IPC16<10:8> |  |

| Reserved                             | 75-80  | 67-72     | 0x00009A-0x0000A4   | —                      |          | _           |  |

| R/W-0<br>U2CTSR6<br>R/W-0<br>U2RXR6                                      | R/W-0<br>U2CTSR5<br>R/W-0<br>U2RXR5                                                                           | R/W-0<br>U2CTSR4<br>R/W-0<br>U2RXR4                                                                                                                                                                                 | R/W-0<br>U2CTSR3<br>R/W-0<br>U2RXR3                                                                                                                                                                        | R/W-0<br>U2CTSR2<br>R/W-0<br>U2RXR2                                                                                                                                                                                                                          | R/W-0<br>U2CTSR1<br>R/W-0<br>U2RXR1                                                                                                                                                                                                                                                                   | R/W-0<br>U2CTSR0<br>bit 8<br>R/W-0<br>U2RXR0                                                                                                                                                                                                                                       |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R/W-0<br>U2RXR6                                                          | R/W-0                                                                                                         | R/W-0                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                 | bit 8<br>R/W-0                                                                                                                                                                                                                                                                     |  |  |

| U2RXR6                                                                   | -                                                                                                             | -                                                                                                                                                                                                                   | -                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                              |  |  |

| U2RXR6                                                                   | -                                                                                                             | -                                                                                                                                                                                                                   | -                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                  |  |  |

| U2RXR6                                                                   | -                                                                                                             | -                                                                                                                                                                                                                   | -                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                  |  |  |

|                                                                          | U2RXR5                                                                                                        | U2RXR4                                                                                                                                                                                                              | U2RXR3                                                                                                                                                                                                     | U2RXR2                                                                                                                                                                                                                                                       | U2RXR1                                                                                                                                                                                                                                                                                                | U2RXR0                                                                                                                                                                                                                                                                             |  |  |

|                                                                          |                                                                                                               |                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       | •=                                                                                                                                                                                                                                                                                 |  |  |

|                                                                          |                                                                                                               |                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       | bit (                                                                                                                                                                                                                                                                              |  |  |

|                                                                          |                                                                                                               |                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |  |  |

|                                                                          |                                                                                                               |                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              | (0)                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |  |  |

| t<br>_                                                                   | W = Writable                                                                                                  |                                                                                                                                                                                                                     | U = Unimplemented bit, read as '0'                                                                                                                                                                         |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |  |  |

| R                                                                        | '1' = Bit is set                                                                                              |                                                                                                                                                                                                                     | '0' = Bit is cleared                                                                                                                                                                                       |                                                                                                                                                                                                                                                              | x = Bit is unknown                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |  |  |

| <pre>10110101 = Input tied to RP181 10110100 = Input tied to RP180</pre> |                                                                                                               |                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |  |  |

|                                                                          | L0110101 =  <br>L0110100 =  <br>D00000001 =  <br>D00000000 =  <br>L0110101 =  <br>L0110100 =  <br>D00000001 = | 10110101 = Input tied to RF<br>10110100 = Input tied to RF<br>100000001 = Input tied to RF<br>100000000 = Input tied to VS<br>12RXR<7:0>: Assign UART<br>10110101 = Input tied to RF<br>10110100 = Input tied to RF | 10110101 = Input tied to RP181<br>10110100 = Input tied to RP180<br>00000001 = Input tied to RP1<br>00000000 = Input tied to Vss<br>J2RXR<7:0>: Assign UART2 Receive (U2<br>10110101 = Input tied to RP181 | 10110101 = Input tied to RP181<br>10110100 = Input tied to RP180<br>100000001 = Input tied to RP1<br>100000000 = Input tied to Vss<br>12RXR<7:0>: Assign UART2 Receive (U2RX) to the Con<br>10110101 = Input tied to RP181<br>10110100 = Input tied to RP180 | <pre>10110101 = Input tied to RP181 10110100 = Input tied to RP180 100000001 = Input tied to RP1 100000000 = Input tied to Vss J2RXR&lt;7:0&gt;: Assign UART2 Receive (U2RX) to the Corresponding RP 10110101 = Input tied to RP181 10110100 = Input tied to RP180 10000001 = Input tied to RP1</pre> | 10110100 = Input tied to RP180<br>100000001 = Input tied to RP1<br>100000000 = Input tied to Vss<br>102RXR<7:0>: Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits<br>10110101 = Input tied to RP181<br>10110100 = Input tied to RP180<br>10000001 = Input tied to RP1 |  |  |

#### REGISTER 10-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

# 12.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1. T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 12-2.

# 12.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 12.2 Timer Control Registers

#### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 TON TSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 U-0 R/W-0 TCS<sup>(1)</sup> TGATE TCKPS1 TCKPS0 T32 \_\_\_\_ \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set '0' = Bit is cleared -n = Value at POR x = Bit is unknown bit 15 TON: Timerx On bit When T32 = 1: 1 = Starts 32-bit Timerx/y 0 = Stops 32-bit Timerx/y When T32 = 0: 1 = Starts 16-bit Timerx 0 = Stops 16-bit Timerx bit 14 Unimplemented: Read as '0' bit 13 TSIDL: Timerx Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12-7 Unimplemented: Read as '0' bit 6 TGATE: Timerx Gated Time Accumulation Enable bit When TCS = 1: This bit is ignored. When TCS = 0: 1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits 11 = 1:256 10 = 1:64 01 = 1:8 00 = 1:1 bit 3 T32: 32-Bit Timer Mode Select bit 1 = Timerx and Timery form a single 32-bit timer 0 = Timerx and Timery act as two 16-bit timers bit 2 Unimplemented: Read as '0' bit 1 TCS: Timerx Clock Source Select bit<sup>(1)</sup> 1 = External clock is from pin, TxCK (on the rising edge) 0 = Internal clock (FP) bit 0 Unimplemented: Read as '0' Note 1: The TxCK pin is not available on all devices. Refer to the "Pin Diagrams" section for the available pins.

#### REGISTER 12-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

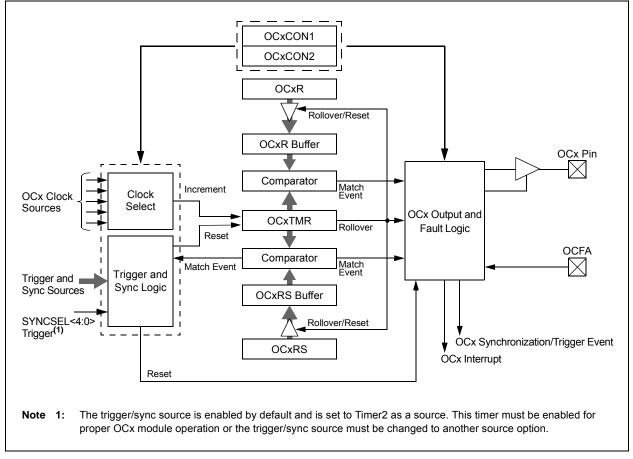

# 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare with Dedicated Timer" (DS70005159) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select one of six available clock sources for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

# 14.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 14.1.1 KEY RESOURCES

- "Output Compare with Dedicated Timer" (DS70005159) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### FIGURE 14-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

# 14.2 Output Compare Control Registers

#### REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0        | U-0                                                                                                                                | R/W-0                                     | R/W-0              | R/W-0             | R/W-0           | U-0              | U-0   |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------|-------------------|-----------------|------------------|-------|--|--|--|--|

|            | _                                                                                                                                  | OCSIDL                                    | OCTSEL2            | OCTSEL1           | OCTSEL0         | _                | _     |  |  |  |  |

| bit 15     |                                                                                                                                    |                                           |                    |                   |                 |                  | bit   |  |  |  |  |

| R/W-0      | U-0                                                                                                                                | U-0                                       | R/W-0, HSC         | R/W-0             | R/W-0           | R/W-0            | R/W-0 |  |  |  |  |

| ENFLTA     |                                                                                                                                    |                                           | OCFLTA             | TRIGMODE          | OCM2            | OCM1             | OCM0  |  |  |  |  |

| bit 7      |                                                                                                                                    |                                           |                    |                   |                 |                  | bit   |  |  |  |  |

|            |                                                                                                                                    |                                           |                    |                   |                 |                  |       |  |  |  |  |

| Legend:    |                                                                                                                                    | HSC = Hardw                               | are Settable/Cl    | earable bit       |                 |                  |       |  |  |  |  |

| R = Reada  | able bit                                                                                                                           | W = Writable                              | bit                | U = Unimplem      | ented bit, read | as '0'           |       |  |  |  |  |

| -n = Value | at POR                                                                                                                             | '1' = Bit is set                          |                    | '0' = Bit is clea | red             | x = Bit is unkno | own   |  |  |  |  |

|            |                                                                                                                                    |                                           |                    |                   |                 |                  |       |  |  |  |  |

| bit 15-14  | -                                                                                                                                  | nted: Read as '                           |                    |                   |                 |                  |       |  |  |  |  |

| bit 13     | OCSIDL: Output Compare x Stop in Idle Mode Control bit                                                                             |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 1 = Output Compare x halts in CPU Idle mode                                                                                        |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | <ul> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>                                                     |                                           |                    |                   |                 |                  |       |  |  |  |  |

| bit 12-10  | OCTSEL<2:0>: Output Compare x Clock Select bits                                                                                    |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 111 = Peripheral clock (FP)                                                                                                        |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 110 = Reserved                                                                                                                     |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 101 = Reserved                                                                                                                     |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 100 = T1CLK is the clock source of the OCx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the OCx |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 011 = T4CLK is the clock source of the OCx                                                                                         |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 001 = T3CLK is the clock source of the OCx                                                                                         |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 000 <b>= T2CLI</b>                                                                                                                 | 00 = T2CLK is the clock source of the OCx |                    |                   |                 |                  |       |  |  |  |  |

| bit 9-8    | Unimpleme                                                                                                                          | nted: Read as '                           | 0'                 |                   |                 |                  |       |  |  |  |  |

| bit 7      | ENFLTA: Fa                                                                                                                         | ult A Input Enal                          | ole bit            |                   |                 |                  |       |  |  |  |  |

|            | 1 = Output Compare Fault A input (OCFA) is enabled                                                                                 |                                           |                    |                   |                 |                  |       |  |  |  |  |

|            | 0 = Output Compare Fault A input (OCFA) is disabled                                                                                |                                           |                    |                   |                 |                  |       |  |  |  |  |

| bit 6-5    | Unimpleme                                                                                                                          | nted: Read as '                           | 0'                 |                   |                 |                  |       |  |  |  |  |

| bit 4      | OCFLTA: PV                                                                                                                         | VM Fault A Cor                            | ndition Status bir | t                 |                 |                  |       |  |  |  |  |

|            |                                                                                                                                    |                                           |                    | in has occurred   |                 |                  |       |  |  |  |  |

| 1.11.0     |                                                                                                                                    |                                           |                    | A pin has occur   | red             |                  |       |  |  |  |  |

| bit 3      |                                                                                                                                    |                                           | Mode Select bi     |                   |                 |                  |       |  |  |  |  |

|            |                                                                                                                                    |                                           |                    | when OCxRS =      | OCX I MR or in  | software         |       |  |  |  |  |

|            | U = IRIGSI                                                                                                                         | AT is cleared o                           | my by soltware     |                   |                 |                  |       |  |  |  |  |

| Note 1.    | OCxR and OC                                                                                                                        | CxRS are doubl                            | e-buffered in P\   | NM mode only      |                 |                  |       |  |  |  |  |

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

#### **REGISTER 14-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output is set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output is set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

NOTES:

#### REGISTER 15-24: LEBCONX: PWMx LEADING-EDGE BLANKING (LEB) CONTROL REGISTER (x = 1 to 5)

|              | (X = 1                                                                                                                                                                                          | 10 5)                                                                                                                                                                                         |                    |                          |                   |                 |        |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|-------------------|-----------------|--------|--|--|--|--|

| R/W-0        | R/W-0                                                                                                                                                                                           | R/W-0                                                                                                                                                                                         | R/W-0              | R/W-0                    | R/W-0             | U-0             | U-0    |  |  |  |  |

| PHR          | PHF                                                                                                                                                                                             | PLR                                                                                                                                                                                           | PLF                | FLTLEBEN                 | CLLEBEN           | _               |        |  |  |  |  |

| bit 15       |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    |                          | •                 |                 | bit 8  |  |  |  |  |

|              |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                             | R/W-0                                                                                                                                                                                         | R/W-0              | R/W-0                    | R/W-0             | R/W-0           | R/W-0  |  |  |  |  |

| —            |                                                                                                                                                                                                 | BCH <sup>(1)</sup>                                                                                                                                                                            | BCL <sup>(1)</sup> | BPHH                     | BPHL              | BPLH            | BPLL   |  |  |  |  |

| bit 7        |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    |                          |                   |                 | bit 0  |  |  |  |  |

| Legend:      |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

| R = Readat   | ole bit                                                                                                                                                                                         | W = Writable I                                                                                                                                                                                | oit                | U = Unimplem             | nented bit, read  | as '0'          |        |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                              |                    | '0' = Bit is clea        |                   | x = Bit is unkr | nown   |  |  |  |  |

|              |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

| bit 15       |                                                                                                                                                                                                 | HRising Edge 1                                                                                                                                                                                |                    |                          |                   |                 |        |  |  |  |  |

|              | •                                                                                                                                                                                               | •                                                                                                                                                                                             |                    | Leading-Edge             | •                 | er              |        |  |  |  |  |

| bit 14       | -                                                                                                                                                                                               | I Falling Edge                                                                                                                                                                                | -                  | ing edge of PW           |                   |                 |        |  |  |  |  |

|              |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    | e Leading-Edge           | Blanking counte   | er              |        |  |  |  |  |

|              |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    | lling edge of PW         |                   |                 |        |  |  |  |  |

| bit 13       | PLR: PWMxL                                                                                                                                                                                      | . Rising Edge T                                                                                                                                                                               | rigger Enable      | bit                      |                   |                 |        |  |  |  |  |

|              | <ul> <li>1 = Rising edge of PWMxL will trigger the Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores the rising edge of PWMxL</li> </ul>                                 |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

|              | -                                                                                                                                                                                               |                                                                                                                                                                                               |                    | MxL                      |                   |                 |        |  |  |  |  |

| bit 12       | PLF: PWMxL Falling Edge Trigger Enable bit                                                                                                                                                      |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

|              | <ol> <li>Falling edge of PWMxL will trigger the Leading-Edge Blanking counter</li> <li>Leading-Edge Blanking ignores the falling edge of PWMxL</li> </ol>                                       |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

| bit 11       | -                                                                                                                                                                                               | <b>FLTLEBEN:</b> Fault Input Leading-Edge Blanking Enable bit                                                                                                                                 |                    |                          |                   |                 |        |  |  |  |  |

|              | 1 = Leading-Edge Blanking is applied to the selected Fault input                                                                                                                                |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

|              | 0 = Leading-Edge Blanking is not applied to the selected Fault input                                                                                                                            |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

| bit 10       |                                                                                                                                                                                                 |                                                                                                                                                                                               |                    | lanking Enable I         |                   |                 |        |  |  |  |  |

|              | <ul> <li>1 = Leading-Edge Blanking is applied to the selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to the selected current-limit input</li> </ul>              |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

| bit 9-6      | •                                                                                                                                                                                               | ted: Read as '0                                                                                                                                                                               |                    | to the selected t        |                   | ul              |        |  |  |  |  |

| bit 5        | •                                                                                                                                                                                               |                                                                                                                                                                                               |                    | al High Enable b         | <sub>i+</sub> (1) |                 |        |  |  |  |  |

| DIL D        |                                                                                                                                                                                                 | <b>BCH:</b> Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup><br>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is high |                    |                          |                   |                 |        |  |  |  |  |

|              |                                                                                                                                                                                                 | <ul> <li>0 = No blanking when the selected blanking signal is high</li> </ul>                                                                                                                 |                    |                          |                   |                 |        |  |  |  |  |

| bit 4        | BCL: Blankin                                                                                                                                                                                    | BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup>                                                                                                                       |                    |                          |                   |                 |        |  |  |  |  |

|              | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the selected blanking signal is low</li> <li>0 = No blanking when the selected blanking signal is low</li> </ul> |                                                                                                                                                                                               |                    |                          |                   |                 |        |  |  |  |  |

|              |                                                                                                                                                                                                 | -                                                                                                                                                                                             |                    |                          |                   |                 |        |  |  |  |  |

| bit 3        |                                                                                                                                                                                                 | ing in PWMxH                                                                                                                                                                                  | •                  | oit<br>Fault input signa | la) when the D    |                 | a hiah |  |  |  |  |

|              |                                                                                                                                                                                                 | ng when the PV                                                                                                                                                                                |                    |                          | lis) when the P   |                 | snign  |  |  |  |  |

| bit 2        |                                                                                                                                                                                                 | ing in PWMxH L                                                                                                                                                                                | •                  | 0                        |                   |                 |        |  |  |  |  |

|              | 1 = State blar                                                                                                                                                                                  | nking (of current                                                                                                                                                                             | t-limit and/or l   | Fault input signa        | ls) when the P    | WMxH output i   | s low  |  |  |  |  |

|              |                                                                                                                                                                                                 | ng when the PV                                                                                                                                                                                |                    |                          |                   |                 |        |  |  |  |  |