Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs506-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "Multi-Tool Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 8.0 "Oscillator Configuration"** for details.

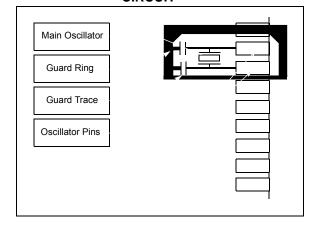

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 3.6.1 KEY RESOURCES

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 4.6.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

**Note:** For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- **Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.6.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.6.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

# 5.2 RTSP Operation

The dsPIC33EPXXGS50X family Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a single page (8 rows or 512 instructions) of memory at a time and to program one row at a time. It is possible to program two instructions at a time as well.

The page erase and single row write blocks are edgealigned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Figure 26-14 in **Section 26.0 "Electrical Characteristics"** lists the typical erase and programming times.

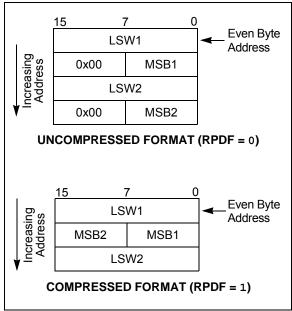

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. Refer to Figure 4-1 through Figure 4-4 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation. For example, when performing Flash write operations on the Inactive Partition in Dual Partition mode, where the CPU remains running, it is necessary to wait for the NVM interrupt before programming the next block of Flash program memory.

### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

# 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000000, 0x000004, 0x000008, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

# 5.4 Dual Partition Flash Configuration

For dsPIC33EP64GS50X devices operating in Dual Partition Flash Program Memory modes, the Inactive Partition can be erased and programmed without stalling the processor. The same programming algorithms are used for programming and erasing the Flash in the Inactive Partition, as described in **Section 5.2 "RTSP Operation"**. On top of the page erase option, the entire Flash memory of the Inactive Partition can be erased by configuring the NVMOP<3:0> bits in the NVMCON register.

Note 1: The application software to be loaded into the Inactive Partition will have the address of the Active Partition. The bootloader firmware will need to offset the address by 0x400000 in order to write to the Inactive Partition.

### 5.4.1 FLASH PARTITION SWAPPING

The Boot Sequence Number is used for determining the Active Partition at start-up and is encoded within the FBTSEQ Configuration register bits. Unlike most Configuration registers, which only utilize the lower 16 bits of the program memory, FBTSEQ is a 24-bit Configuration Word. The Boot Sequence Number (BSEQ) is a 12-bit value and is stored in FBTSEQ twice. The true value is stored in bits, FBTSEQ<11:0>, and its complement is stored in bits, FBTSEQ<23:12>. At device Reset, the sequence numbers are read and the partition with the lowest sequence number becomes the Active Partition. If one of the Boot Sequence Numbers is invalid, the device will select the partition with the valid Boot Sequence Number, or default to Partition 1 if both sequence numbers are invalid. See Section 23.0 "Special Features" for more information.

The BOOTSWP instruction provides an alternative means of swapping the Active and Inactive Partitions (soft swap) without the need for a device Reset. The BOOTSWP must always be followed by a GOTO instruction. The BOOTSWP instruction swaps the Active and Inactive Partitions, and the PC vectors to the location specified by the GOTO instruction in the newly Active Partition.

It is important to note that interrupts should temporarily be disabled while performing the soft swap sequence and that after the partition swap, all peripherals and interrupts which were enabled remain enabled. Additionally, the RAM and stack will maintain state after the switch. As a result, it is recommended that applications using soft swaps jump to a routine that will reinitialize the device in order to ensure the firmware runs as expected. The Configuration registers will have no effect during a soft swap. For robustness of operation, in order to execute the BOOTSWP instruction, it is necessary to execute the NVM unlocking sequence as follows:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Execute the BOOTSWP instruction.

If the unlocking sequence is not performed, the BOOTSWP instruction will be executed as a forced NOP and a GOTO instruction, following the BOOTSWP instruction, will be executed, causing the PC to jump to that location in the current operating partition.

The SFTSWP and P2ACTIV bits in the NVMCON register are used to determine a successful swap of the Active and Inactive Partitions, as well as which partition is active. After the BOOTSWP and GOTO instructions, the SFTSWP bit should be polled to verify the partition swap has occurred and then cleared for the next panel swap event.

### 5.4.2 DUAL PARTITION MODES

While operating in Dual Partition mode, dsPIC33EP64GS50X family devices have the option for both partitions to have their own defined security segments, as shown in Figure 23-4. Alternatively, the device can operate in Protected Dual Partition mode, where Partition 1 becomes permanently erase/write-protected. Protected Dual Partition mode allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1.

dsPIC33EP64GS50X family devices can also operate in Privileged Dual Partition mode, where additional security protections are implemented to allow for protection of intellectual property when multiple parties have software within the device. In Privileged Dual Partition mode, both partitions place additional restrictions on the BSLIM register. These prevent changes to the size of the Boot Segment and General Segment, ensuring that neither segment will be altered.

# 5.5 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

### 5.5.1 KEY RESOURCES

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

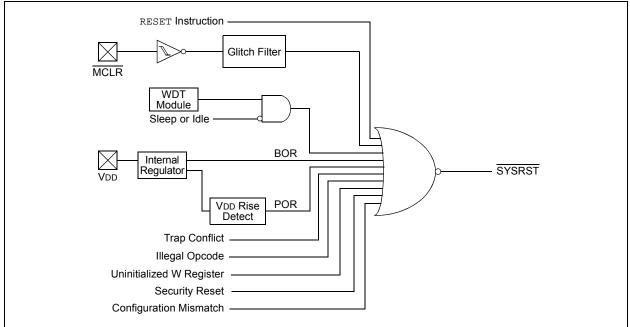

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the BOR and POR bits (RCON<1:0>) that are set. The user application can set or clear any bit, at any time, during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSCx bits is loaded into the NOSC<2:0> (OSCCON<10:8>) bits on Reset, which in turn, initializes the system clock.

| l≳ Å                              | Reserved                                                           | BSLIM<12:0> <sup>(1)</sup> + 0x000000 |                            |

|-----------------------------------|--------------------------------------------------------------------|---------------------------------------|----------------------------|

| iorit                             | Reserved                                                           | BSLIM<12:0> <sup>(1)</sup> + 0x000002 |                            |

| - La                              | Oscillator Fail Trap Vector                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000004 |                            |

| .der                              | Address Error Trap Vector                                          | BSLIM<12:0> <sup>(1)</sup> + 0x000006 |                            |

| Ō                                 | Generic Hard Trap Vector                                           | BSLIM<12:0> <sup>(1)</sup> + 0x000008 |                            |

| ura                               | Stack Error Trap Vector                                            | BSLIM<12:0> <sup>(1)</sup> + 0x00000A |                            |

| Nat                               | Math Error Trap Vector                                             | BSLIM<12:0> <sup>(1)</sup> + 0x00000C |                            |

| Decreasing Natural Order Priority | Reserved                                                           | BSLIM<12:0> <sup>(1)</sup> + 0x00000E |                            |

| asir                              | Generic Soft Trap Vector                                           | BSLIM<12:0> <sup>(1)</sup> + 0x000010 |                            |

| cre                               | Reserved                                                           | BSLIM<12:0> <sup>(1)</sup> + 0x000012 |                            |

| De                                | Interrupt Vector 0                                                 | BSLIM<12:0>(1) + 0x000014             |                            |

|                                   | Interrupt Vector 1                                                 | BSLIM<12:0> <sup>(1)</sup> + 0x000016 |                            |

|                                   | :                                                                  | :                                     |                            |

|                                   | :                                                                  |                                       |                            |

| _                                 | :                                                                  | :                                     |                            |

| AIVT                              | Interrupt Vector 52                                                | BSLIM<12:0> <sup>(1)</sup> + 0x00007C |                            |

| 4                                 | Interrupt Vector 53                                                | BSLIM<12:0> <sup>(1)</sup> + 0x00007E |                            |

|                                   | Interrupt Vector 54                                                | BSLIM<12:0> <sup>(1)</sup> + 0x000080 | See Table 7-1 for          |

|                                   |                                                                    |                                       | Interrupt Vector Details   |

|                                   | :                                                                  |                                       |                            |

|                                   | :                                                                  |                                       |                            |

|                                   | Interrupt Vector 116                                               | BSLIM<12:0> <sup>(1)</sup> + 0x0000FC |                            |

|                                   | Interrupt Vector 117                                               | BSLIM<12:0>(1) + 0x0000FE             |                            |

|                                   | Interrupt Vector 118                                               | BSLIM<12:0> <sup>(1)</sup> + 0x000100 |                            |

|                                   | Interrupt Vector 119                                               | BSLIM<12:0> <sup>(1)</sup> + 0x000102 |                            |

|                                   | Interrupt Vector 120                                               | BSLIM<12:0>(1) + 0x000104             |                            |

|                                   | · · · · · · · · · · · · · · · · · · ·                              |                                       |                            |

|                                   | :                                                                  |                                       |                            |

|                                   | :                                                                  | - :                                   |                            |

|                                   | Interrupt Vector 244                                               | BSLIM<12:0>(1) + 0x0001FC             |                            |

| ▼                                 | Interrupt Vector 245                                               | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE |                            |

| Note 1:                           | The address depends on the size<br>[(BSLIM<12:0> – 1) x 0x400] + C |                                       | y BSLIM<12:0>.             |

| 2:                                | In Dual Partition modes, each pa enabled).                         |                                       | Interrupt Vector Table (if |

#### 8.1 **CPU Clocking System**

The dsPIC33EPXXGS50X family of devices provides six system clock options:

- · Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (FRCPLL)

- · FRC Oscillator with Postscaler

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

0.8 MHz < FPLLI<sup>(1)</sup> < 8.0 MHz FPLLO<sup>(1)</sup> ≤ 120 MHz @ +125℃ 120 MHz < Fvco<sup>(1)</sup> < 340 MHz FPLLO<sup>(1)</sup> ≤ 140 MHz @ +85°C FPLL ÷N1 Fvco Fosc PFD VCO ÷ N2 PLLPRE<4:0> PLLPOST<1:0> ÷Μ PLLDIV<8:0> Note 1: This frequency range must be met at all times.

#### **FIGURE 8-2:** PLL BLOCK DIAGRAM

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

#### **EQUATION 8-1: DEVICE OPERATING** FREQUENCY

### FCY = FOSC/2

Figure 8-2 is a block diagram of the PLL module. Equation 8-2 provides the relationship between Input Frequency (FIN) and Output Frequency (FPLLO). Equation 8-3 provides the relationship between Input Frequency (FIN) and VCO Frequency (FVCO).

#### **EQUATION 8-2: FPLLO CALCULATION**

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{PLLDIV < 8:0 > + 2}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where: N1 = PLLPRE < 4:0 > +2

$N2 = 2 \times (PLLPOST < 1:0 > +1)$ M = PLLDIV < 8:0 > +2

#### **EQUATION 8-3: Fvco CALCULATION**

$$F_{VCO} = F_{IN} \times \left(\frac{M}{N1}\right) = F_{IN} \times \left(\frac{PLLDIV < 8:0 > +2}{(PLLPRE < 4:0 > +2)}\right)$$

# 11.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

## 11.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 11.2 Timer1 Control Register

| REGISTER           | 11-1: T1CO                                      | N: TIMER1 C                              | ONTROL RE                 | EGISTER          |                          |                    |             |

|--------------------|-------------------------------------------------|------------------------------------------|---------------------------|------------------|--------------------------|--------------------|-------------|

| R/W-0              | U-0                                             | R/W-0                                    | U-0                       | U-0              | U-0                      | U-0                | U-0         |

| TON <sup>(1)</sup> | —                                               | TSIDL                                    | _                         | _                | —                        | —                  | _           |

| bit 15             |                                                 |                                          |                           |                  |                          |                    | bit 8       |

|                    |                                                 |                                          |                           |                  |                          |                    |             |

| U-0                | R/W-0                                           | R/W-0                                    | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0         |

|                    | TGATE                                           | TCKPS1                                   | TCKPS0                    |                  | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> | —           |

| bit 7              |                                                 |                                          |                           |                  |                          |                    | bit 0       |

| Legend:            |                                                 |                                          |                           |                  |                          |                    |             |

| R = Readab         | ole bit                                         | W = Writable                             | bit                       | U = Unimple      | mented bit, read         | 1 as '0'           |             |

| -n = Value a       | at POR                                          | '1' = Bit is set                         |                           | '0' = Bit is cle |                          | x = Bit is unkno   | own         |

|                    |                                                 |                                          |                           |                  |                          |                    |             |

| bit 15             | TON: Timer1                                     | On bit <sup>(1)</sup>                    |                           |                  |                          |                    |             |

|                    | 1 = Starts 16-<br>0 = Stops 16-                 |                                          |                           |                  |                          |                    |             |

| bit 14             | Unimplemen                                      | ted: Read as '                           | 0'                        |                  |                          |                    |             |

| bit 13             | TSIDL: Timer                                    | 1 Stop in Idle N                         | Node bit                  |                  |                          |                    |             |

|                    |                                                 | ues module op<br>s module opera          |                           |                  | ldle mode                |                    |             |

| bit 12-7           | Unimplemen                                      | ted: Read as '                           | 0'                        |                  |                          |                    |             |

| bit 6              | TGATE: Time                                     | er1 Gated Time                           | Accumulation              | n Enable bit     |                          |                    |             |

|                    | When TCS =<br>This bit is ign                   |                                          |                           |                  |                          |                    |             |

|                    |                                                 | 0:<br>ne accumulation<br>ne accumulation |                           |                  |                          |                    |             |

| bit 5-4            | TCKPS<1:0>                                      | : Timer1 Input                           | Clock Presca              | le Select bits   |                          |                    |             |

|                    | 11 = 1:256<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1 |                                          |                           |                  |                          |                    |             |

| bit 3              |                                                 | ted: Read as '                           | 0'                        |                  |                          |                    |             |

| bit 2              | -                                               | er1 External Cl                          |                           | chronization S   | elect bit <sup>(1)</sup> |                    |             |

|                    | When TCS =                                      | 1:                                       |                           |                  |                          |                    |             |

|                    |                                                 | izes external c                          |                           |                  |                          |                    |             |

|                    |                                                 | synchronize ex                           | kternal clock II          | nput             |                          |                    |             |

|                    | When TCS =<br>This bit is ign                   |                                          |                           |                  |                          |                    |             |

| bit 1              | •                                               | Clock Source S                           | Select bit <sup>(1)</sup> |                  |                          |                    |             |

|                    |                                                 | clock is from pi                         |                           | ne rising edge)  | )                        |                    |             |

| bit 0              |                                                 | ted: Read as '                           | 0'                        |                  |                          |                    |             |

|                    | When Timer1 is er<br>attempts by user s         |                                          |                           |                  |                          | SYNC = 1, TON      | l = 1), any |

# REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

### 12.2 Timer Control Registers

#### R/W-0 U-0 R/W-0 U-0 U-0 U-0 U-0 U-0 TON TSIDL bit 15 bit 8 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 U-0 R/W-0 TCS<sup>(1)</sup> TGATE TCKPS1 TCKPS0 T32 \_\_\_\_ \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set '0' = Bit is cleared -n = Value at POR x = Bit is unknown bit 15 TON: Timerx On bit When T32 = 1: 1 = Starts 32-bit Timerx/y 0 = Stops 32-bit Timerx/y When T32 = 0: 1 = Starts 16-bit Timerx 0 = Stops 16-bit Timerx bit 14 Unimplemented: Read as '0' bit 13 TSIDL: Timerx Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12-7 Unimplemented: Read as '0' bit 6 TGATE: Timerx Gated Time Accumulation Enable bit When TCS = 1: This bit is ignored. When TCS = 0: 1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits 11 = 1:256 10 = 1:64 01 = 1:8 00 = 1:1 bit 3 T32: 32-Bit Timer Mode Select bit 1 = Timerx and Timery form a single 32-bit timer 0 = Timerx and Timery act as two 16-bit timers bit 2 Unimplemented: Read as '0' bit 1 TCS: Timerx Clock Source Select bit<sup>(1)</sup> 1 = External clock is from pin, TxCK (on the rising edge) 0 = Internal clock (FP) bit 0 Unimplemented: Read as '0' Note 1: The TxCK pin is not available on all devices. Refer to the "Pin Diagrams" section for the available pins.

### REGISTER 12-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = OCxRS compare event is used for synchronization

- 11110 = INT2 pin synchronizes or triggers OCx

- 11101 = INT1 pin synchronizes or triggers OCx

- 11100 = Reserved

- 11011 = CMP4 module synchronizes or triggers OCx

- 11010 = CMP3 module synchronizes or triggers OCx

- 11001 = CMP2 module synchronizes or triggers OCx

- 11000 = CMP1 module synchronizes or triggers OCx

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 input capture interrupt event synchronizes or triggers OCx

- 10010 = IC3 input capture interrupt event synchronizes or triggers OCx

- 10001 = IC2 input capture interrupt event synchronizes or triggers OCx

- 10000 = IC1 input capture interrupt event synchronizes or triggers OCx

- 01111 = Timer5 synchronizes or triggers OCx

- 01110 = Timer4 synchronizes or triggers OCx

- 01101 = Timer3 synchronizes or triggers OCx

- 01100 = Timer2 synchronizes or triggers OCx (default)

- 01011 = Timer1 synchronizes or triggers OCx

- 01010 = Reserved

- 01001 = Reserved

- 01000 = IC4 input capture event synchronizes or triggers OCx

- 00111 = IC3 input capture event synchronizes or triggers OCx

- 00110 = IC2 input capture event synchronizes or triggers OCx

- 00101 = IC1 input capture event synchronizes or triggers OCx

- 00100 = OC4 module synchronizes or triggers  $OCx^{(1,2)}$

- 00011 = OC3 module synchronizes or triggers  $OCx^{(1,2)}$

- 00010 = OC2 module synchronizes or triggers  $OCx^{(1,2)}$

- 00001 = OC1 module synchronizes or triggers  $OCx^{(1,2)}$

- 00000 = No sync or trigger source for OCx

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

### REGISTER 19-8: ADCON4H: ADC CONTROL REGISTER 4 HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0         | R/W-0 | R/W-0  | R/W-0  |

|--------|--------|--------|--------|---------------|-------|--------|--------|

| C3CHS1 | C3CHS0 | C2CHS1 | C2CHS0 | C1CHS1 C1CHS0 |       | C0CHS1 | C0CHS0 |

| bit 7  | •      |        |        |               |       |        | bit 0  |

| Legend:          |                                    |                           |                                                             |                    |  |  |  |

|------------------|------------------------------------|---------------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit |                                    | W = Writable bit          | U = Unimplemented bit                                       | , read as '0'      |  |  |  |

| -n = Value       | at POR                             | '1' = Bit is set          | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

| bit 15-8         | Unimplen                           | nented: Read as '0'       |                                                             |                    |  |  |  |

| bit 7-6          | -                                  |                           | 3 Input Channel Selection bits                              |                    |  |  |  |

|                  | 1x = Rese<br>01 = AN15<br>00 = AN3 |                           | when DIFF3 (ADMOD0L<7>)                                     | = 1)               |  |  |  |

| bit 5-4          | C2CHS<1                            | :0>: Dedicated ADC Core 2 | 2 Input Channel Selection bits                              |                    |  |  |  |

|                  |                                    | Band Gap                  | when DIFF2 (ADMOD0L<5>)                                     | = 1)               |  |  |  |

| bit 3-2          | 11 = AN1/<br>10 = PGA              | ALT<br>2                  | I Input Channel Selection bits when DIFF1 (ADMOD0L<3>)      | = 1)               |  |  |  |

| bit 1-0          | 11 = AN0/<br>10 = PGA              | ALT<br>1                  | ) Input Channel Selection bits<br>when DIFF0 (ADMOD0L<1>) = | = 1)               |  |  |  |

NOTES:

# 22.0 CONSTANT-CURRENT SOURCE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

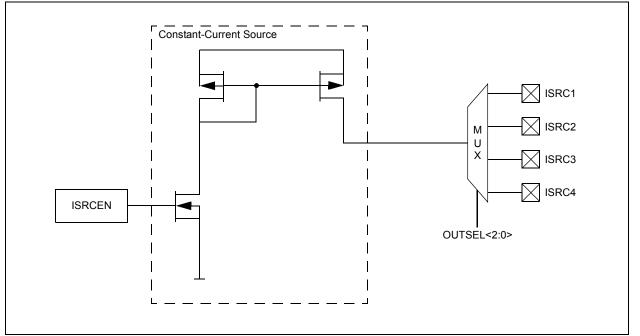

The constant-current source module is a precision current generator and is used in conjunction with the ADC module to measure the resistance of external resistors connected to device pins.

# 22.1 Features Overview

The constant-current source module offers the following major features:

- Constant-Current Generator (10 µA nominal)

- Internal Selectable Connection to One of Four Pins

- Enable/Disable Bit

# 22.2 Module Description

Figure 22-1 shows a functional block diagram of the constant-current source module. It consists of a precision current generator with a nominal value of 10  $\mu$ A. The module can be enabled and disabled using the ISRCEN bit in the ISRCCON register. The output of the current generator is internally connected to a device pin. The dsPIC33EPXXGS50X family can have up to 4 selectable current source pins. The OUTSEL<2:0> bits in the ISRCCON register allow selection of the target pin.

The current source is calibrated during testing.

### FIGURE 22-1: CONSTANT-CURRENT SOURCE MODULE BLOCK DIAGRAM

# 23.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXGS50X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXGS50X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

# 23.1 Configuration Bits

In dsPIC33EPXXGS50X family devices, the Configuration Words are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the end of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 23-1 with detailed descriptions in Table 23-2. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration Shadow registers during device Resets.

For devices operating in Dual Partition modes, the BSEQx bits (FBTSEQ<11:0>) determine which panel is the Active Partition at start-up and the Configuration Words from that panel are loaded into the Configuration Shadow registers.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Words for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled. Program code executing out of configuration space will cause a device Reset.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration Words.

# TABLE 23-1: CONFIGURATION REGISTER MAP<sup>(3)</sup> (CONTINUED)

|                      | -       |                                      | •••••      |        | -       |        | <b>\</b> |        | ,      |       |       |       |       |           |         |         |                         |          |         |

|----------------------|---------|--------------------------------------|------------|--------|---------|--------|----------|--------|--------|-------|-------|-------|-------|-----------|---------|---------|-------------------------|----------|---------|

| Name                 | Address | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-16 | Bit 15 | Bit 14  | Bit 13 | Bit 12   | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4   | Bit 3   | Bit 2                   | Bit 1    | Bit 0   |

| FDEVOPT              | 002BAC  | 16                                   |            |        |         |        |          |        |        |       |       |       |       |           |         |         |                         |          |         |

|                      | 0057AC  | 32                                   | —          | _      | _       | _      | _        | _      | _      | —     | _     | _     | DBCC  | —         | ALTI2C2 | ALTI2C1 | Reserved <sup>(1)</sup> | _        | PWMLOCK |

|                      | 00AFAC  | 64                                   |            |        |         |        |          |        |        |       |       |       |       |           |         |         |                         |          |         |

| FALTREG              | 002BB0  | 16                                   |            |        |         |        |          |        |        |       |       |       |       |           |         |         |                         |          |         |

|                      | 0057B0  | 32                                   | _          | _      | _       | —      | _        | —      | _      | _     | _     | _     |       | CTXT2<2:  | 0>      | _       | с                       | TXT1<2:0 | >       |

|                      | 00AFB0  | 64                                   |            |        |         |        |          |        |        |       |       |       |       |           |         |         |                         |          |         |

| FBTSEQ               | 002BFC  | 16                                   |            |        |         |        |          |        | •      |       |       |       |       |           |         |         |                         |          |         |

|                      | 0057FC  | 32                                   |            | IBSE   | Q<11:0> |        |          |        |        |       |       |       | E     | BSEQ<11:0 | >       |         |                         |          |         |

|                      | 00AFFC  | 64                                   | 1          |        |         |        |          |        |        |       |       |       |       |           |         |         |                         |          |         |

| FBOOT <sup>(4)</sup> | 801000  | -                                    | _          | _      |         | _      | _        | -      |        | _     |       | _     | _     | _         | _       | _       | _                       | BTMC     | DE<1:0> |

Note 1: These bits are reserved and must be programmed as '1'.

2: This bit is reserved and must be programmed as '0'.

3: When operating in Dual Partition mode, each partition will have dedicated Configuration registers. On a device Reset, the configuration values of the Active Partition are read at start-up, but during a soft swap condition, the configuration settings of the newly Active Partition are ignored.

4: FBOOT resides in configuration memory space.

### TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTI      | ERISTICS                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |      |                     |  |  |

|------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|---------------------|--|--|

| Parameter<br>No. | Тур.                      | Max. | Units                                                                                                                                                                                                                                                                                   |        |      |                     |  |  |

| Operating Curr   | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |        |      |                     |  |  |

| DC20d            | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | -40°C  |      |                     |  |  |

| DC20a            | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V | 10 MIPS             |  |  |

| DC20b            | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V |                     |  |  |

| DC20c            | 7                         | 12   | mA                                                                                                                                                                                                                                                                                      | +125°C | -    |                     |  |  |

| DC22d            | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | -40°C  |      |                     |  |  |

| DC22a            | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V | 20 MIPS             |  |  |

| DC22b            | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V | 20 101195           |  |  |

| DC22c            | 11                        | 19   | mA                                                                                                                                                                                                                                                                                      | +125°C |      |                     |  |  |

| DC24d            | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | -40°C  |      |                     |  |  |

| DC24a            | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3∨ | 40 MIPS             |  |  |

| DC24b            | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V | 40 1011-3           |  |  |

| DC24c            | 19                        | 30   | mA                                                                                                                                                                                                                                                                                      | +125°C | -    |                     |  |  |

| DC25d            | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | -40°C  |      |                     |  |  |

| DC25a            | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3∨ | 60 MIPS             |  |  |

| DC25b            | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | +85°C  | 3.3V | 00 WIF 3            |  |  |

| DC25c            | 26                        | 41   | mA                                                                                                                                                                                                                                                                                      | +125°C |      |                     |  |  |

| DC26d            | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | -40°C  |      |                     |  |  |

| DC26a            | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V | 70 MIPS             |  |  |

| DC26b            | 30                        | 46   | mA                                                                                                                                                                                                                                                                                      | +85°C  |      |                     |  |  |

| DC27d            | 51                        | 81   | mA                                                                                                                                                                                                                                                                                      | -40°C  |      | 70 14/00            |  |  |

| DC27a            | 51                        | 81   | mA                                                                                                                                                                                                                                                                                      | +25°C  | 3.3V | 70 MIPS<br>(Note 2) |  |  |

| DC27b            | 52                        | 82   | mA                                                                                                                                                                                                                                                                                      | +85°C  |      | (1010 2)            |  |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- CPU is executing while(1) statement

- JTAG is disabled

- **2:** For this specification, the following test conditions apply:

- · APLL clock is enabled

- All 5 PWMs enabled and operating at maximum speed (PTCON2<2:0> = 000), PTPER = 1000h, 50% duty cycle

- All other peripherals are disabled (corresponding PMDx bits are set)

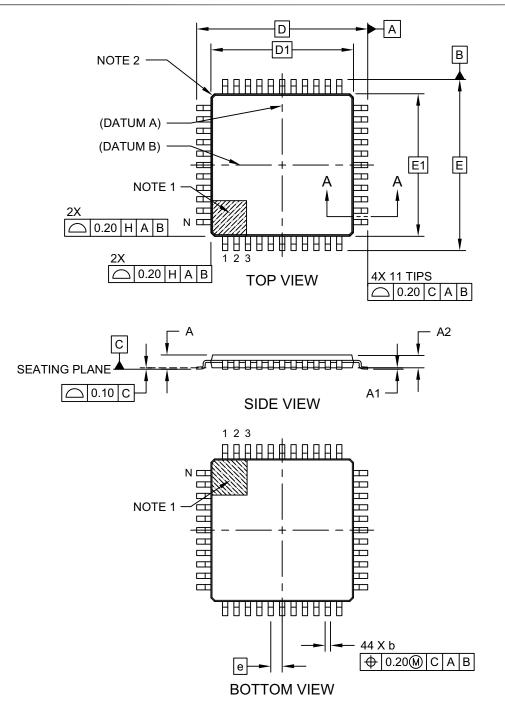

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

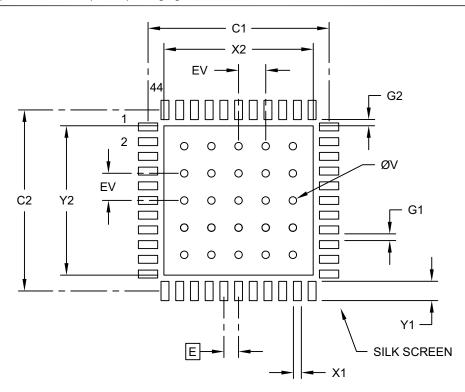

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                  | Ν      | /ILLIMETER | S        |      |  |  |

|----------------------------------|--------|------------|----------|------|--|--|

| Dimension                        | Limits | MIN        | NOM      | MAX  |  |  |

| Contact Pitch                    | E      |            | 0.65 BSC |      |  |  |

| Optional Center Pad Width        | X2     |            |          | 6.60 |  |  |

| Optional Center Pad Length       | Y2     |            |          | 6.60 |  |  |

| Contact Pad Spacing              | C1     |            | 8.00     |      |  |  |

| Contact Pad Spacing              | C2     |            | 8.00     |      |  |  |

| Contact Pad Width (X44)          | X1     |            |          | 0.35 |  |  |

| Contact Pad Length (X44)         | Y1     |            |          | 0.85 |  |  |

| Contact Pad to Contact Pad (X40) | G1     | 0.30       |          |      |  |  |

| Contact Pad to Center Pad (X44)  | G2     | 0.28       |          |      |  |  |

| Thermal Via Diameter             | V      |            | 0.33     |      |  |  |

| Thermal Via Pitch                | EV     |            | 1.20     |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C