Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gs506t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP64GS50X DEVICES

| 7                          | GOTO Instruction                                      | 0x000000                         |

|----------------------------|-------------------------------------------------------|----------------------------------|

|                            | Reset Address                                         | 0x000002                         |

| Ð                          | Interrupt Vector Table                                | 0x000004<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22,207 instructions) | 0x000200<br>0x00AF7E             |

| er Mem                     | Device Configuration                                  | 0x00AF80<br>0x00AFFE             |

| Use                        |                                                       | 0x00B000                         |

|                            | Unimplemented                                         |                                  |

|                            | (Read '0's)                                           |                                  |

|                            | Reserved                                              | 0x7FFFFE<br>0x800000<br>0x800E46 |

|                            | Calibration Data                                      | 0x800E48                         |

|                            | Reserved                                              | 0x800E78<br>0x800E7A<br>0x800EFE |

| Configuration Memory Space | UDID                                                  | 0x800F00<br>0x800F08<br>0x800F0A |

| nory S                     | Reserved                                              | 0x800F7E                         |

| n Mer                      | User OTP Memory                                       | 0x800F80<br>0x800FFC             |

| Iratio                     | Reserved                                              | 0x801000                         |

| onfigu                     | Write Latches                                         | 0xF9FFFE<br>0xFA0000             |

| ŏ                          |                                                       | 0xFA0002<br>0xFA0004             |

|                            | Reserved                                              |                                  |

|                            | DEVID                                                 | 0xFEFFFE<br>0xFF0000             |

|                            | Reserved                                              | 0xFF0002<br>0xFF0004             |

| _                          |                                                       | 0xFFFFFE                         |

Note: Memory areas are not shown to scale.

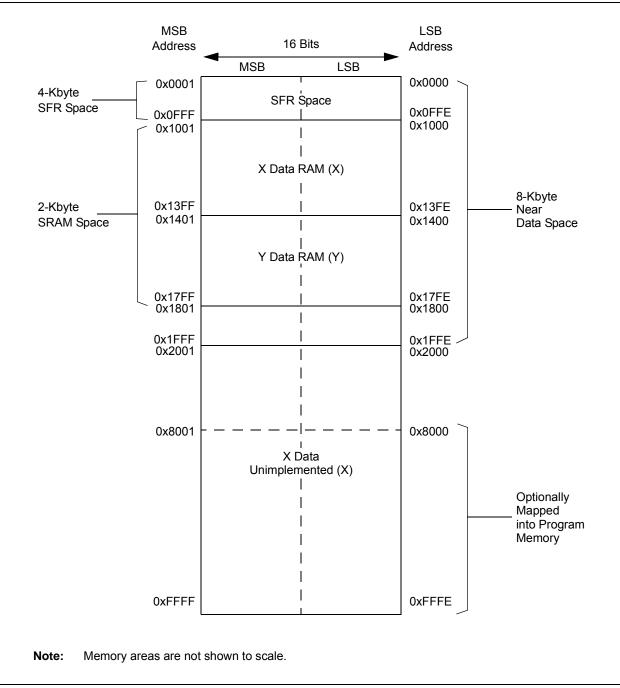

#### FIGURE 4-6: DATA MEMORY MAP FOR dsPIC33EP16GS50X DEVICES

#### TABLE 4-21: NVM REGISTER MAP

| SFR<br>Name | Addr. | Bit 15       | Bit 14                                                                       | Bit 13 | Bit 12  | Bit 11 | Bit 10      | Bit 9     | Bit 8        | Bit 7                         | Bit 6   | Bit 5    | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------------|------------------------------------------------------------------------------|--------|---------|--------|-------------|-----------|--------------|-------------------------------|---------|----------|-------|----------|-------|-------|-------|---------------|

| NVMCON      | 0728  | WR           | WREN                                                                         | WRERR  | NVMSIDL | SFTSWP | P2ACTIV     | RPDF      | URERR        | R NVMOP3 NVMOP2 NVMOP1 NVMOP0 |         |          |       |          |       | 0000  |       |               |

| NVMADR      | 072A  | NVMADR<15:0> |                                                                              |        |         |        |             |           |              |                               |         |          | 0000  |          |       |       |       |               |

| NVMADRU     | 072C  | -            | _                                                                            | _      | _       |        | _           | _         | _            | NVMADR<23:16>                 |         |          |       |          |       |       | 0000  |               |

| NVMKEY      | 072E  | -            | _                                                                            | _      | _       |        | _           | _         | _            |                               |         |          | NVMK  | (EY<7:0> |       |       |       | 0000          |

| NVMSRCADR   | 0730  |              |                                                                              |        |         | NVM S  | Source Data | Address I | Register, Lo | wer Word                      | (NVMSRC | ADR<15:0 | >)    |          |       |       |       | 0000          |

| NVMSRCADRH  | 0732  | _            | — — — — — — — NVM Source Data Address Register, Upper Byte (NVMSRCADR<23:16> |        |         |        |             |           |              |                               | 0000    |          |       |          |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9     | Bit 8       | Bit 7    | Bit 6    | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|-----------|-----------|-------------|----------|----------|--------|---------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR | _       | —      | VREGSF | _         | CM        | VREGS       | EXTR     | SWR      | SWDTEN | WDTO    | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | -      | COSC2  | COSC1   | COSC0  | _      | NOSC2     | NOSC1     | NOSC0       | CLKLOCK  | IOLOCK   | LOCK   | _       | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1   | DOZE0  | DOZEN  | FRCDIV2   | FRCDIV1   | FRCDIV0     | PLLPOST1 | PLLPOST0 | _      | PLLPRE4 | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 3040          |

| PLLFBD      | 0746  | -      |        | _       | _      | _      | _         | _         | PLLDIV<8:0> |          |          |        |         |         |         | 0030    |         |               |

| OSCTUN      | 0748  | -      |        | _       | _      | _      | _         | _         | _           | _        | _        |        |         | TUN     | <5:0>   |         |         | 0000          |

| LFSR        | 074C  | -      |        |         |        |        |           |           | LF          | SR<14:0> |          |        |         |         |         |         |         | 0000          |

| REFOCON     | 074E  | ROON   |        | ROSSLP  | ROSEL  | RODIV3 | RODIV2    | RODIV1    | RODIV0      | _        | _        | _      | _       | _       | _       | _       | _       | 0000          |

| ACLKCON     | 0750  | ENAPLL | APLLCK | SELACLK | _      | _      | APSTSCLR2 | APSTSCLR1 | APSTSCLR0   | ASRCSEL  | FRCSEL   | —      | _       | _       | _       | _       | _       | 2740          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

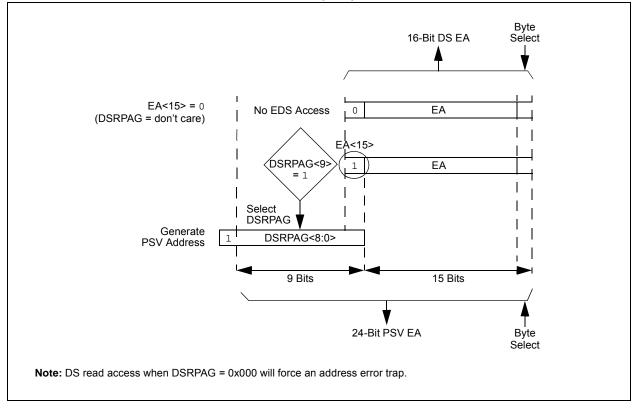

### 4.5.1 PAGED MEMORY SCHEME

The dsPIC33EPXXGS50X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the base Data Space address is used in conjunction with the Data Space Page (DSRPAG) register to form the Program Space Visibility (PSV) address.

The Data Space Page (DSRPAG) register is located in the SFR space. Construction of the PSV address is shown in Figure 4-9. When DSRPAG<9> = 1 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit PSV read address. The paged memory scheme provides access to multiple 32-Kbyte windows in the PSV memory. The Data Space Page (DSRPAG) register, in combination with the upper half of the Data Space address, can provide up to 8 Mbytes of PSV address space. The paged data memory space is shown in Figure 4-10.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG.

### FIGURE 4-9: PROGRAM SPACE VISIBILITY (PSV) READ ADDRESS GENERATION

# 4.5.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible, regardless of the contents of the Data Space Page register. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space in combination with DSRPAG = 0x00. Consequently, DSRPAG is initialized to 0x001 at Reset.

- Note 1: DSRPAG should not be used to access Page 0. An EDS access with DSRPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSRPAG in software has no effect.

The remaining PSV pages are only accessible using the DSRPAG register in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

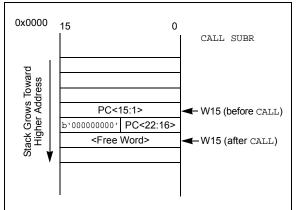

## 4.5.3 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP), and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXGS50X devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-11 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes). When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-11. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

## FIGURE 4-11: CALL STACK FRAME

| Reserved   Reserved   cillator Fail Trap Vector   dress Error Trap Vector   eneric Hard Trap Vector   tack Error Trap Vector   Math Error Trap Vector   Reserved   eneric Soft Trap Vector 0   Interrupt Vector 1   :   :   Interrupt Vector 52   Interrupt Vector 53   Interrupt Vector 54 | $\begin{array}{c} \text{BSLIM}{(12:0)}^{(1)} + 0x000000\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000002\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000004\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000006\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000A\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000C\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000C\\ \text{BSLIM}{(12:0)}^{(1)} + 0x00000C\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000010\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000012\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000014\\ \text{BSLIM}{(12:0)}^{(1)} + 0x000016\\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | See Table 7-1 for        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| cillator Fail Trap Vector<br>dress Error Trap Vector<br>eneric Hard Trap Vector<br>tack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53  | BSLIM<12:0>(1) + 0x000004<br>BSLIM<12:0>(1) + 0x000006<br>BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                 | See Table 7-1 for        |

| dress Error Trap Vector<br>eneric Hard Trap Vector<br>tack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                               | BSLIM<12:0>(1) + 0x000006<br>BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                              | See Table 7-1 for        |

| eneric Hard Trap Vector<br>tack Error Trap Vector<br>Math Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                          | BSLIM<12:0>(1) + 0x000008<br>BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C                                                                                                                                                                                                                                                                        | See Table 7-1 for        |

| tack Error Trap Vector<br>Nath Error Trap Vector<br>Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                     | BSLIM<12:0>(1) + 0x00000A<br>BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C                                                                                                                                                                                                                                                                                               | See Table 7-1 for        |

| Math Error Trap Vector   Reserved   eneric Soft Trap Vector   Reserved   Interrupt Vector 0   Interrupt Vector 1   Interrupt Vector 52   Interrupt Vector 53                                                                                                                                | BSLIM<12:0>(1) + 0x00000C<br>BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                                                                                                                                            | See Table 7-1 for        |

| Reserved<br>eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                         | BSLIM<12:0>(1) + 0x00000E<br>BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br><br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                                                                                                                                                                               | See Table 7-1 for        |

| eneric Soft Trap Vector<br>Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                     | BSLIM<12:0>(1) + 0x000010<br>BSLIM<12:0>(1) + 0x000012<br>BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                      | See Table 7-1 for        |

| Reserved<br>Interrupt Vector 0<br>Interrupt Vector 1<br>                                                                                                                                                                                                                                    | BSLIM<12:0> <sup>(1)</sup> + 0x000012<br>BSLIM<12:0> <sup>(1)</sup> + 0x000014<br>BSLIM<12:0> <sup>(1)</sup> + 0x000016<br>:<br>:<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                       | See Table 7-1 for        |

| Interrupt Vector 0<br>Interrupt Vector 1<br>:<br>:<br>Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                                            | BSLIM<12:0>(1) + 0x000014<br>BSLIM<12:0>(1) + 0x000016<br>:<br>:<br>BSLIM<12:0>(1) + 0x00007C<br>BSLIM<12:0>(1) + 0x00007C                                                                                                                                                                                                                                                                                                                                                                                                                                                | See Table 7-1 for        |

| Interrupt Vector 1                                                                                                                                                                                                                                                                          | BSLIM<12:0> <sup>(1)</sup> + 0x000016<br>:<br>:<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                         | See Table 7-1 for        |

| Interrupt Vector 52<br>Interrupt Vector 53                                                                                                                                                                                                                                                  | :<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007C<br>BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                         | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                         | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                         | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| Interrupt Vector 53                                                                                                                                                                                                                                                                         | BSLIM<12:0> <sup>(1)</sup> + 0x00007E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

|                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | See Table 7-1 for        |

| Interrupt Vector 54                                                                                                                                                                                                                                                                         | BSLIM<12:0> <sup>(1)</sup> + 0x000080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See Table 7-1 for        |

| -                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| :                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interrupt Vector Details |

| :                                                                                                                                                                                                                                                                                           | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| :                                                                                                                                                                                                                                                                                           | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Interrupt Vector 116                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x0000FC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 117                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x0000FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 118                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 119                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 120                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x000104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| :                                                                                                                                                                                                                                                                                           | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| :                                                                                                                                                                                                                                                                                           | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| :                                                                                                                                                                                                                                                                                           | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Interrupt Vector 244                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x0001FC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Interrupt Vector 245                                                                                                                                                                                                                                                                        | BSLIM<12:0> <sup>(1)</sup> + 0x0001FE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

|                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | y BSLIM<12:0>.           |

|                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

|                                   | U-0                                                                                                                                                                     | U-0                                                                                                                                                               | R/W-0                                                                | R/W-0             | R/W-0            | R/W-0              | R/W-0  |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|------------------|--------------------|--------|--|--|--|--|

| _                                 | —                                                                                                                                                                       | —                                                                                                                                                                 | PWM5MD                                                               | PWM4MD            | PWM3MD           | PWM2MD             | PWM1MD |  |  |  |  |

| bit 15                            |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    | bit 8  |  |  |  |  |

|                                   |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |  |  |  |

| U-0                               | U-0                                                                                                                                                                     | U-0                                                                                                                                                               | U-0                                                                  | U-0               | U-0              | U-0                | U-0    |  |  |  |  |

|                                   |                                                                                                                                                                         | _                                                                                                                                                                 | _                                                                    | —                 |                  |                    |        |  |  |  |  |

| bit 7                             |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    | bit C  |  |  |  |  |

|                                   |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |  |  |  |

| Legend:                           |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                                                                         |                                                                                                                                                                   | oit                                                                  | U = Unimplem      | nented bit, read | l as '0'           |        |  |  |  |  |

| -n = Value at                     | t POR                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                  |                                                                      | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |  |  |  |

|                                   |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |  |  |  |

| bit 15-13                         | Unimplement                                                                                                                                                             | ted: Read as '0                                                                                                                                                   | )'                                                                   |                   |                  |                    |        |  |  |  |  |

| bit 12                            | PWM5MD: P\                                                                                                                                                              | WM5 Module D                                                                                                                                                      | isable bit                                                           |                   |                  |                    |        |  |  |  |  |

|                                   |                                                                                                                                                                         | 1 = PWM5 module is disabled<br>0 = PWM5 module is enabled                                                                                                         |                                                                      |                   |                  |                    |        |  |  |  |  |

|                                   |                                                                                                                                                                         |                                                                                                                                                                   | -                                                                    |                   |                  |                    |        |  |  |  |  |

| bit 11                            | PWM4MD: P\                                                                                                                                                              | : PWM4 Module Disable bit                                                                                                                                         |                                                                      |                   |                  |                    |        |  |  |  |  |

|                                   |                                                                                                                                                                         |                                                                                                                                                                   |                                                                      |                   |                  |                    |        |  |  |  |  |

|                                   |                                                                                                                                                                         | odule is disable                                                                                                                                                  | -                                                                    |                   |                  |                    |        |  |  |  |  |

|                                   | 0 = PWM4 mo                                                                                                                                                             | odule is enable                                                                                                                                                   | d                                                                    |                   |                  |                    |        |  |  |  |  |

|                                   | 0 = PWM4 mo<br><b>PWM3MD:</b> P\                                                                                                                                        | odule is enable<br>VM3 Module D                                                                                                                                   | d<br>isable bit                                                      |                   |                  |                    |        |  |  |  |  |

|                                   | 0 = PWM4 mo<br>PWM3MD: P\<br>1 = PWM3 mo                                                                                                                                | odule is enable                                                                                                                                                   | d<br>isable bit<br>d                                                 |                   |                  |                    |        |  |  |  |  |

| bit 10<br>bit 9                   | 0 = PWM4 mc<br>PWM3MD: P\<br>1 = PWM3 mc<br>0 = PWM3 mc                                                                                                                 | odule is enable<br>WM3 Module D<br>odule is disable                                                                                                               | d<br>isable bit<br>d                                                 |                   |                  |                    |        |  |  |  |  |

| bit 10                            | 0 = PWM4 mc<br>PWM3MD: P\<br>1 = PWM3 mc<br>0 = PWM3 mc<br>PWM2MD: P\                                                                                                   | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable                                                                                            | d<br>isable bit<br>d<br>d<br>isable bit                              |                   |                  |                    |        |  |  |  |  |

| bit 10                            | 0 = PWM4 mo<br><b>PWM3MD</b> : PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br><b>PWM2MD</b> : PV<br>1 = PWM2 mo                                                                    | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D                                                                            | d<br>isable bit<br>d<br>d<br>isable bit<br>d                         |                   |                  |                    |        |  |  |  |  |

| bit 10                            | 0 = PWM4 mc<br><b>PWM3MD</b> : PV<br>1 = PWM3 mc<br>0 = PWM3 mc<br><b>PWM2MD</b> : PV<br>1 = PWM2 mc<br>0 = PWM2 mc                                                     | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable                                                        | d<br>isable bit<br>d<br>d<br>isable bit<br>d<br>d                    |                   |                  |                    |        |  |  |  |  |

| bit 10<br>bit 9                   | 0 = PWM4 mo<br>PWM3MD: PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br>PWM2MD: PV<br>1 = PWM2 mo<br>0 = PWM2 mo<br>0 = PWM2 mo<br>PWM1MD: PV<br>1 = PWM1 mo                         | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable<br>odule is enable<br>WM1 Module D<br>odule is disable | d<br>isable bit<br>d<br>isable bit<br>d<br>d<br>isable bit<br>d      |                   |                  |                    |        |  |  |  |  |

| bit 10<br>bit 9                   | 0 = PWM4 mo<br><b>PWM3MD</b> : PV<br>1 = PWM3 mo<br>0 = PWM3 mo<br><b>PWM2MD</b> : PV<br>1 = PWM2 mo<br>0 = PWM2 mo<br><b>PWM1MD</b> : PV<br>1 = PWM1 mo<br>0 = PWM1 mo | odule is enable<br>WM3 Module D<br>odule is disable<br>odule is enable<br>WM2 Module D<br>odule is disable<br>odule is enable<br>WM1 Module D                     | d<br>isable bit<br>d<br>isable bit<br>d<br>d<br>isable bit<br>d<br>d |                   |                  |                    |        |  |  |  |  |

| Input Name <sup>(1)</sup> | Function Name | Register | Configuration Bits |

|---------------------------|---------------|----------|--------------------|

| External Interrupt 1      | INT1          | RPINR0   | INT1R<7:0>         |

| External Interrupt 2      | INT2          | RPINR1   | INT2R<7:0>         |

| Timer1 External Clock     | T1CK          | RPINR2   | T1CKR<7:0>         |

| Timer2 External Clock     | T2CK          | RPINR3   | T2CKR<7:0>         |

| Timer3 External Clock     | T3CK          | RPINR3   | T3CKR<7:0>         |

| Input Capture 1           | IC1           | RPINR7   | IC1R<7:0>          |

| Input Capture 2           | IC2           | RPINR7   | IC2R<7:0>          |

| Input Capture 3           | IC3           | RPINR8   | IC3R<7:0>          |

| Input Capture 4           | IC4           | RPINR8   | IC4R<7:0>          |

| Output Compare Fault A    | OCFA          | RPINR11  | OCFAR<7:0>         |

| PWM Fault 1               | FLT1          | RPINR12  | FLT1R<7:0>         |

| PWM Fault 2               | FLT2          | RPINR12  | FLT2R<7:0>         |

| PWM Fault 3               | FLT3          | RPINR13  | FLT3R<7:0>         |

| PWM Fault 4               | FLT4          | RPINR13  | FLT4R<7:0>         |

| UART1 Receive             | U1RX          | RPINR18  | U1RXR<7:0>         |

| UART1 Clear-to-Send       | U1CTS         | RPINR18  | U1CTSR<7:0>        |

| UART2 Receive             | U2RX          | RPINR19  | U2RXR<7:0>         |

| UART2 Clear-to-Send       | U2CTS         | RPINR19  | U2CTSR<7:0>        |

| SPI1 Data Input           | SDI1          | RPINR20  | SDI1R<7:0>         |

| SPI1 Clock Input          | SCK1          | RPINR20  | SCK1R<7:0>         |

| SPI1 Slave Select         | SS1           | RPINR21  | SS1R<7:0>          |

| SPI2 Data Input           | SDI2          | RPINR22  | SDI2R<7:0>         |

| SPI2 Clock Input          | SCK2          | RPINR22  | SCK2R<7:0>         |

| SPI2 Slave Select         | SS2           | RPINR23  | SS2R<7:0>          |

| PWM Synch Input 1         | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |

| PWM Synch Input 2         | SYNCI2        | RPINR38  | SYNCI2R<7:0>       |

| PWM Fault 5               | FLT5          | RPINR42  | FLT5R<7:0>         |

| PWM Fault 6               | FLT6          | RPINR42  | FLT6R<7:0>         |

| PWM Fault 7               | FLT7          | RPINR43  | FLT7R<7:0>         |

| PWM Fault 8               | FLT8          | RPINR43  | FLT8R<7:0>         |

### TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

### **REGISTER 15-19: TRGCONX: PWMx TRIGGER CONTROL REGISTER (x = 1 to 5)**

| TRGDIV3<br>bit 15  | TRGDIV2                                                                                                                                                                                             | TRGDIV1                                                                                                         | TRGDIV0          | _                   |                  |                    | _          |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|--------------------|------------|--|--|--|--|--|

| bit 15             |                                                                                                                                                                                                     |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     |                                                                                                                 | L                |                     |                  | I                  | bit 8      |  |  |  |  |  |

|                    |                                                                                                                                                                                                     |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

| R/W-0              | U-0                                                                                                                                                                                                 | R/W-0                                                                                                           | R/W-0            | R/W-0               | R/W-0            | R/W-0              | R/W-0      |  |  |  |  |  |

| DTM <sup>(1)</sup> | <u> </u>                                                                                                                                                                                            | TRGSTRT5                                                                                                        | TRGSTRT4         | TRGSTRT3            | TRGSTRT2         | 2 TRGSTRT1 TRGSTR1 |            |  |  |  |  |  |

| bit 7              |                                                                                                                                                                                                     |                                                                                                                 |                  |                     |                  |                    | bit (      |  |  |  |  |  |

| Legend:            |                                                                                                                                                                                                     |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

| R = Readable       | e bit                                                                                                                                                                                               | W = Writable                                                                                                    | bit              | U = Unimplem        | nented bit, read | l as '0'           |            |  |  |  |  |  |

| -n = Value at      | POR                                                                                                                                                                                                 | '1' = Bit is set                                                                                                |                  | '0' = Bit is clea   | ared             | x = Bit is unkn    | own        |  |  |  |  |  |

|                    |                                                                                                                                                                                                     |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

| bit 15-12          | TRGDIV<3:0                                                                                                                                                                                          | Trigger # Out                                                                                                   | tput Divider bit | S                   |                  |                    |            |  |  |  |  |  |

|                    | 1111 <b>= Trigg</b> e                                                                                                                                                                               | er output for eve                                                                                               | ery 16th trigge  | revent              |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for eve                                                                                               |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 1101 = Trigger output for every 14th trigger event<br>1100 = Trigger output for every 13th trigger event                                                                                            |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for events of events output for events of the second second second second second second second second |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for even                                                                                              |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for eve                                                                                               |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for ev                                                                                                |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for eve                                                                                               |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 0110 = Trigger output for every 7th trigger event                                                                                                                                                   |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 0101 = Trigger output for every 6th trigger event                                                                                                                                                   |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 0100 = Trigger output for every 5th trigger event<br>0011 = Trigger output for every 4th trigger event                                                                                              |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 0010 = Trigger output for every 3rd trigger event                                                                                                                                                   |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 0001 = Trigger output for every 2nd trigger event                                                                                                                                                   |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    |                                                                                                                                                                                                     | er output for eve                                                                                               |                  |                     |                  |                    |            |  |  |  |  |  |

| bit 11-8           | Unimplemen                                                                                                                                                                                          | ted: Read as '0                                                                                                 | )'               |                     |                  |                    |            |  |  |  |  |  |

| bit 7              | DTM: Dual Tr                                                                                                                                                                                        | igger Mode bit <sup>(</sup>                                                                                     | 1)               |                     |                  |                    |            |  |  |  |  |  |

|                    | 1 = Secondary trigger event is combined with the primary trigger event to create a PWM trigger                                                                                                      |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

|                    | 0 = Secondary trigger event is not combined with the primary trigger event to create a PWM trigger<br>two separate PWM triggers are generated                                                       |                                                                                                                 |                  |                     |                  |                    |            |  |  |  |  |  |

| bit 6              |                                                                                                                                                                                                     | ted: Read as '                                                                                                  | •                |                     |                  |                    |            |  |  |  |  |  |

| bit 5-0            | -                                                                                                                                                                                                   |                                                                                                                 |                  | Enable Select b     | its              |                    |            |  |  |  |  |  |