Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                              |

| Core Processor             | ARM® Cortex®-M4F                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                          |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-TQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32wg942f64-qfp64 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **2 System Summary**

# **2.1 System Introduction**

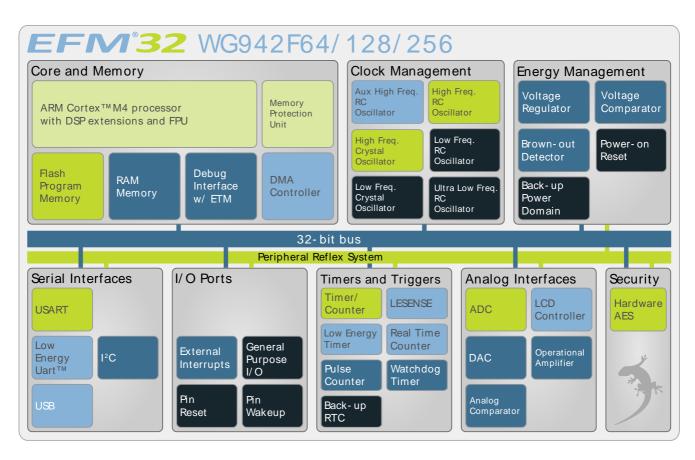

The EFM32 MCUs are the world's most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-M4, with DSP instruction support and floating-point unit, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32WG microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configuration for the EFM32WG942 devices. For a complete feature set and in-depth information on the modules, the reader is referred to the *EFM32WG Reference Manual*.

A block diagram of the EFM32WG942 is shown in Figure 2.1 (p. 3) .

#### Figure 2.1. Block Diagram

## 2.1.1 ARM Cortex-M4 Core

The ARM Cortex-M4 includes a 32-bit RISC processor, with DSP instruction support and floating-point unit, which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while the CPU is asleep. The EFM32 implementation of the Cortex-M4 is described in detail in *ARM Cortex-M4 Devices Generic User Guide*.

## 2.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface and an Embedded Trace Module (ETM) for data/instruction tracing. In addition there is also a 1-wire Serial Wire Viewer pin which can be used to output profiling information, data trace and software-generated messages.

## 2.1.18 Low Energy Timer (LETIMER)

The unique LETIMER<sup>TM</sup>, the Low Energy Timer, is a 16-bit timer that is available in energy mode EM2 in addition to EM1 and EM0. Because of this, it can be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. It is also connected to the Real Time Counter (RTC), and can be configured to start counting on compare matches from the RTC.

## 2.1.19 Pulse Counter (PCNT)

The Pulse Counter (PCNT) can be used for counting pulses on a single input or to decode quadrature encoded inputs. It runs off either the internal LFACLK or the PCNTn\_S0IN pin as external clock source. The module may operate in energy mode EM0 – EM3.

## 2.1.20 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs can either be one of the selectable internal references or from external pins. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

## 2.1.21 Voltage Comparator (VCMP)

The Voltage Supply Comparator is used to monitor the supply voltage from software. An interrupt can be generated when the supply falls below or rises above a programmable threshold. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

## 2.1.22 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to one million samples per second. The integrated input mux can select inputs from 8 external pins and 6 internal signals.

## 2.1.23 Digital to Analog Converter (DAC)

The Digital to Analog Converter (DAC) can convert a digital value to an analog output voltage. The DAC is fully differential rail-to-rail, with 12-bit resolution. It has two single ended output buffers which can be combined into one differential output. The DAC may be used for a number of different applications such as sensor interfaces or sound output.

## 2.1.24 Operational Amplifier (OPAMP)

The EFM32WG942 features 3 Operational Amplifiers. The Operational Amplifier is a versatile general purpose amplifier with rail-to-rail differential input and rail-to-rail single ended output. The input can be set to pin, DAC or OPAMP, whereas the output can be pin, OPAMP or ADC. The current is programmable and the OPAMP has various internal configurations such as unity gain, programmable gain using internal resistors etc.

## 2.1.25 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface (LESENSE<sup>TM</sup>), is a highly configurable sensor interface with support for up to 4 individually configurable sensors. By controlling the analog comparators and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable

# **3 Electrical Characteristics**

# **3.1 Test Conditions**

## **3.1.1 Typical Values**

The typical data are based on  $T_{AMB}$ =25°C and  $V_{DD}$ =3.0 V, as defined in Table 3.2 (p. 10), by simulation and/or technology characterisation unless otherwise specified.

#### 3.1.2 Minimum and Maximum Values

The minimum and maximum values represent the worst conditions of ambient temperature, supply voltage and frequencies, as defined in Table 3.2 (p. 10), by simulation and/or technology characterisation unless otherwise specified.

## **3.2 Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings, and functional operation under such conditions are not guaranteed. Stress beyond the limits specified in Table 3.1 (p. 10) may affect the device reliability or cause permanent damage to the device. Functional operating conditions are given in Table 3.2 (p. 10).

| Symbol             | Parameter                         | Condition                              | Min  | Тур | Max                  | Unit |

|--------------------|-----------------------------------|----------------------------------------|------|-----|----------------------|------|

| T <sub>STG</sub>   | Storage tempera-<br>ture range    |                                        | -40  |     | 150 <sup>1</sup>     | °C   |

| Τ <sub>S</sub>     | Maximum soldering temperature     | Latest IPC/JEDEC J-STD-020<br>Standard |      |     | 260                  | °C   |

| V <sub>DDMAX</sub> | External main sup-<br>ply voltage |                                        | 0    |     | 3.8                  | V    |

| V <sub>IOPIN</sub> | Voltage on any I/O pin            |                                        | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

#### Table 3.1. Absolute Maximum Ratings

<sup>1</sup>Based on programmed devices tested for 10000 hours at 150°C. Storage temperature affects retention of preprogrammed calibration values stored in flash. Please refer to the Flash section in the Electrical Characteristics for information on flash data retention for different temperatures.

# **3.3 General Operating Conditions**

## 3.3.1 General Operating Conditions

#### Table 3.2. General Operating Conditions

| Symbol            | Parameter                    | Min  | Тур | Max | Unit |

|-------------------|------------------------------|------|-----|-----|------|

| T <sub>AMB</sub>  | Ambient temperature range    | -40  |     | 85  | °C   |

| V <sub>DDOP</sub> | Operating supply voltage     | 1.98 |     | 3.8 | V    |

| f <sub>APB</sub>  | Internal APB clock frequency |      |     | 48  | MHz  |

| f <sub>AHB</sub>  | Internal AHB clock frequency |      |     | 48  | MHz  |

## 3.3.2 Environmental

#### Table 3.3. Environmental

| Symbol              | Parameter                            | Condition              | Min | Тур | Max  | Unit |

|---------------------|--------------------------------------|------------------------|-----|-----|------|------|

| V <sub>ESDHBM</sub> | ESD (Human Body<br>Model HBM)        | T <sub>AMB</sub> =25°C |     |     | 2000 | V    |

| V <sub>ESDCDM</sub> | ESD (Charged De-<br>vice Model, CDM) | T <sub>AMB</sub> =25°C |     |     | 750  | V    |

Latch-up sensitivity passed:  $\pm 100 \text{ mA}/1.5 \times \text{V}_{\text{SUPPLY}}(\text{max})$  according to JEDEC JESD 78 method Class II, 85°C.

# **3.4 Current Consumption**

#### Table 3.4. Current Consumption

| Symbol           | Parameter                                                                                | Condition                                                                               | Min                                                                                      | Тур | Max        | Unit       |            |

|------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|------------|------------|------------|

|                  |                                                                                          | 48 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C          |                                                                                          | 225 | 236        | μΑ/<br>MHz |            |

|                  |                                                                                          | 48 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C          |                                                                                          | 225 |            | µA/<br>MHz |            |

|                  |                                                                                          | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C         |                                                                                          | 226 | 238        | μΑ/<br>MHz |            |

|                  |                                                                                          | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C         |                                                                                          | 227 |            | µA/<br>MHz |            |

|                  |                                                                                          | 21 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C |                                                                                          | 228 | 240        | µA/<br>MHz |            |

|                  | EM0 current. No<br>prescaling. Running<br>prime number cal-                              | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C         |                                                                                          | 229 |            | µA/<br>MHz |            |

| I <sub>EMO</sub> | culation code from<br>Flash. (Production<br>test condition = 14<br>MHz)                  | 14 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C |                                                                                          | 230 | 243        | µA/<br>MHz |            |

|                  |                                                                                          | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C         |                                                                                          | 231 |            | µA/<br>MHz |            |

|                  |                                                                                          | 11 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C |                                                                                          | 232 | 245        | µA/<br>MHz |            |

|                  | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C          |                                                                                         | 233                                                                                      |     | µA/<br>MHz |            |            |

|                  |                                                                                          |                                                                                         | 6.6 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C |     | 238        | 250        | µA/<br>MHz |

|                  | 6.6 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C |                                                                                         | 238                                                                                      |     | µA/<br>MHz |            |            |

| Symbol           | Parameter         | Condition                                                                                                                | Min | Тур               | Max              | Unit       |

|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-------------------|------------------|------------|

|                  |                   | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                         |     | 271               | 286              | μΑ/<br>MHz |

|                  |                   | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{\text{DD}}\text{=}$ 3.0 V, $T_{\text{AMB}}\text{=}85^{\circ}\text{C}$ |     | 275               |                  | μΑ/<br>MHz |

|                  |                   | 48 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                           |     | 63                | 75               | μΑ/<br>MHz |

|                  |                   | 48 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C                                           |     | 65                | 76               | μΑ/<br>MHz |

|                  |                   | 28 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 64                | 75               | μΑ/<br>MHz |

|                  |                   | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C                                          |     | 65                | 77               | μΑ/<br>MHz |

|                  |                   | 21 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 65                | 76               | μΑ/<br>MHz |

|                  |                   | 21 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                  |     | 66                | 78               | μΑ/<br>MHz |

|                  | EM1 current (Pro- | 14 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 67                | 79               | μΑ/<br>MHz |

| I <sub>EM1</sub> | tion = 14 MHz)    | 14 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                  |     | 68                | 82               | μΑ/<br>MHz |

|                  |                   | 11 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 68                | 81               | µA/<br>MHz |

|                  |                   | 11 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                  |     | 70                | 83               | µA/<br>MHz |

|                  |                   | 6.6 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                 |     | 74                | 87               | µA/<br>MHz |

|                  |                   | 6.6 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                 |     | 76                | 89               | µA/<br>MHz |

|                  |                   | 1.2 MHz HFRCO. all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                    |     | 106               | 120              | µA/<br>MHz |

|                  |                   | 1.2 MHz HFRCO. all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C                                         |     | 112               | 129              | μΑ/<br>MHz |

| I <sub>EM2</sub> | EM2 current       | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                     |     | 0.95 <sup>1</sup> | 1.7 <sup>1</sup> | μA         |

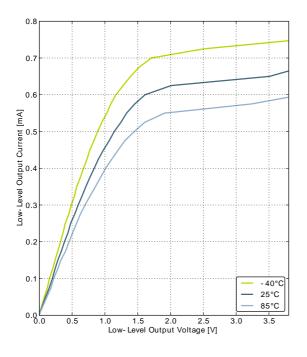

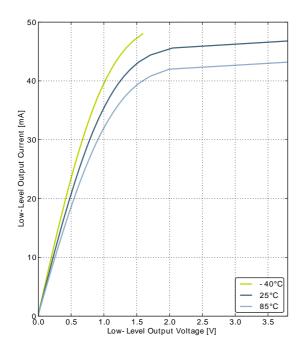

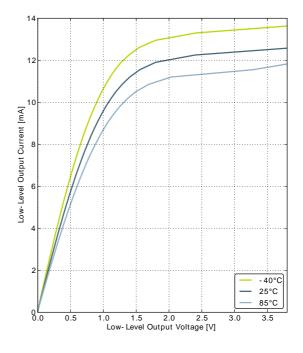

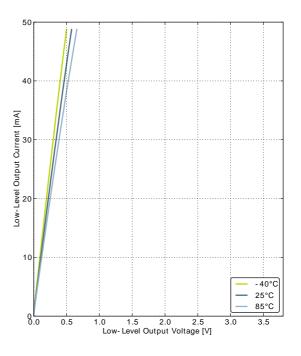

#### Figure 3.15. Typical Low-Level Output Current, 3.8V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = LOW

GPIO\_Px\_CTRL DRIVEMODE = HIGH

## 3.9.3 LFRCO

#### Table 3.11. LFRCO

| Symbol                        | Parameter                                                         | Condition | Min   | Тур    | Max   | Unit |

|-------------------------------|-------------------------------------------------------------------|-----------|-------|--------|-------|------|

| f <sub>LFRCO</sub>            | Oscillation frequen-<br>cy , $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C |           | 31.29 | 32.768 | 34.28 | kHz  |

| t <sub>LFRCO</sub>            | Startup time not in-<br>cluding software<br>calibration           |           |       | 150    |       | μs   |

| I <sub>LFRCO</sub>            | Current consump-<br>tion                                          |           |       | 300    |       | nA   |

| TUNESTEP <sub>L</sub><br>FRCO | Frequency step<br>for LSB change in<br>TUNING value               |           |       | 1.5    |       | %    |

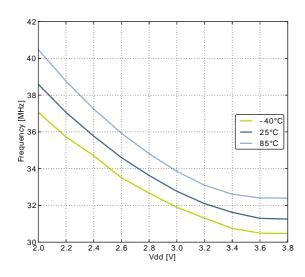

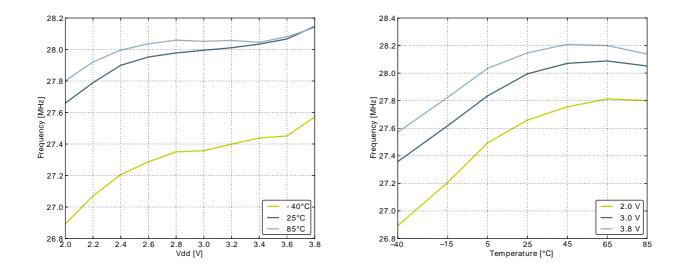

Figure 3.17. Calibrated LFRCO Frequency vs Temperature and Supply Voltage

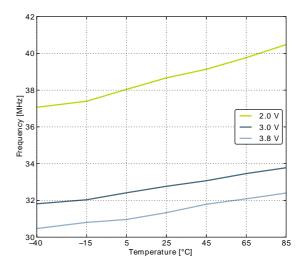

Figure 3.22. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature

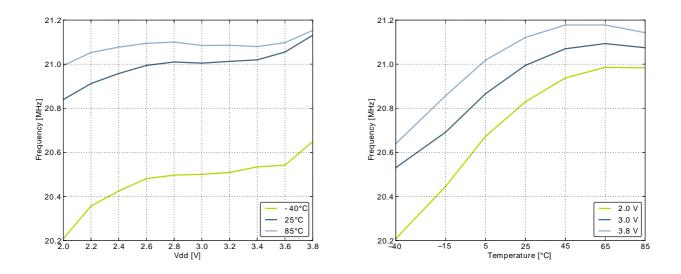

Figure 3.23. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature

## 3.10.1 Typical performance

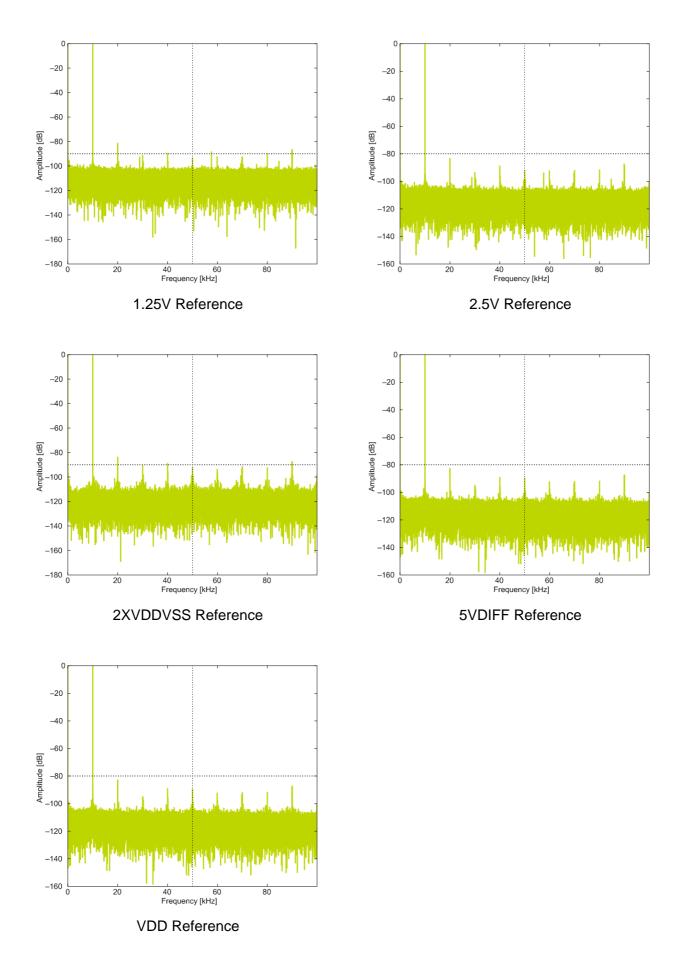

#### Figure 3.26. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C

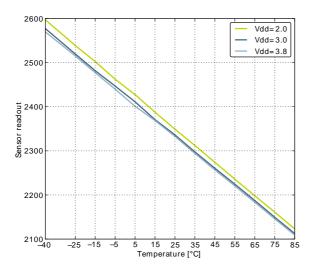

#### Figure 3.31. ADC Temperature sensor readout

# 3.11 Digital Analog Converter (DAC)

#### Table 3.16. DAC

| Symbol                 | Parameter                           | Condition                                                                | Min              | Тур              | Max             | Unit            |

|------------------------|-------------------------------------|--------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|

| М                      | Output voltage                      | VDD voltage reference, single ended                                      | 0                |                  | V <sub>DD</sub> | V               |

| V <sub>DACOUT</sub>    | range                               | VDD voltage reference, differ-<br>ential                                 | -V <sub>DD</sub> |                  | V <sub>DD</sub> | V               |

| V <sub>DACCM</sub>     | Output common<br>mode voltage range |                                                                          | 0                |                  | V <sub>DD</sub> | V               |

|                        | Active current in-                  | 500 kSamples/s, 12 bit                                                   |                  | 400 <sup>1</sup> |                 | μA              |

| I <sub>DAC</sub>       | cluding references                  | 100 kSamples/s, 12 bit                                                   |                  | 200 <sup>1</sup> |                 | μA              |

|                        | for 2 channels                      | 1 kSamples/s 12 bit NORMAL                                               |                  | 17 <sup>1</sup>  |                 | μA              |

| SR <sub>DAC</sub>      | Sample rate                         |                                                                          |                  |                  | 500             | ksam-<br>ples/s |

|                        | DAC clock frequen-<br>cy            | Continuous Mode                                                          |                  |                  | 1000            | kHz             |

| f <sub>DAC</sub>       |                                     | Sample/Hold Mode                                                         |                  |                  | 250             | kHz             |

|                        |                                     | Sample/Off Mode                                                          |                  |                  | 250             | kHz             |

| CYC <sub>DACCONV</sub> | Clock cyckles per conversion        |                                                                          |                  | 2                |                 |                 |

| t <sub>DACCONV</sub>   | Conversion time                     |                                                                          | 2                |                  |                 | μs              |

| t <sub>DACSETTLE</sub> | Settling time                       |                                                                          |                  | 5                |                 | μs              |

| SNR <sub>DAC</sub>     |                                     | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |                  | 58               |                 | dB              |

|                        | Signal to Noise Ra-<br>tio (SNR)    | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |                  | 59               |                 | dB              |

|                        |                                     | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |                  | 58               |                 | dB              |

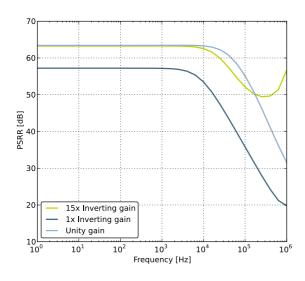

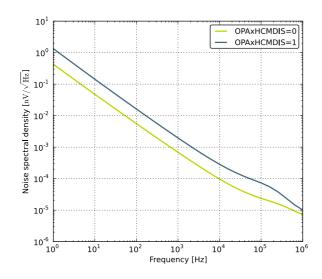

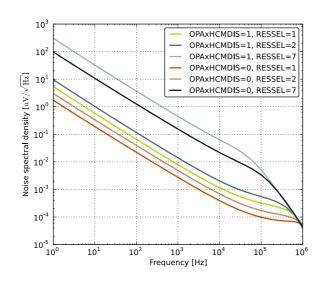

Figure 3.34. OPAMP Negative Power Supply Rejection Ratio

Figure 3.35. OPAMP Voltage Noise Spectral Density (Unity Gain) Vout=1V

Figure 3.36. OPAMP Voltage Noise Spectral Density (Non-Unity Gain)

# 3.14 Voltage Comparator (VCMP)

#### Table 3.19. VCMP

| Symbol                                 | Parameter                             | Condition                                                             | Min | Тур             | Max | Unit |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------------|-----|-----------------|-----|------|

| V <sub>VCMPIN</sub>                    | Input voltage range                   |                                                                       |     | V <sub>DD</sub> |     | V    |

| V <sub>VCMPCM</sub>                    | VCMP Common<br>Mode voltage range     |                                                                       |     | V <sub>DD</sub> |     | V    |

| 1                                      | Active current                        | BIASPROG=0b0000 and<br>HALFBIAS=1 in VCMPn_CTRL<br>register           |     | 0.3             | 0.6 | μA   |

| IVCMP                                  | Active current                        | BIASPROG=0b1111 and<br>HALFBIAS=0 in VCMPn_CTRL<br>register. LPREF=0. |     | 22              | 35  | μA   |

| t <sub>VCMPREF</sub>                   | Startup time refer-<br>ence generator | NORMAL                                                                |     | 10              |     | μs   |

| M                                      | Offect veltage                        | Single ended                                                          |     | 10              |     | mV   |

| V <sub>VCMPOFFSET</sub> Offset voltage | Differential                          |                                                                       | 10  |                 | mV  |      |

| V <sub>VCMPHYST</sub>                  | VCMP hysteresis                       |                                                                       |     | 61              | 210 | mV   |

| t <sub>VCMPSTART</sub>                 | Startup time                          |                                                                       |     |                 | 10  | μs   |

The  $V_{DD}$  trigger level can be configured by setting the TRIGLEVEL field of the VCMP\_CTRL register in accordance with the following equation:

VCMP Trigger Level as a Function of Level Setting

V<sub>DD Trigger Level</sub>=1.667V+0.034 ×TRIGLEVEL

(3.2)

## 3.15 LCD

#### Table 3.20. LCD

| Symbol                | Parameter                            | Condition                                                                                                                              | Min | Тур  | Max | Unit |

|-----------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| f <sub>LCDFR</sub>    | Frame rate                           |                                                                                                                                        | 30  |      | 200 | Hz   |

| NUM <sub>SEG</sub>    | Number of seg-<br>ments supported    |                                                                                                                                        |     | 16×8 |     | seg  |

| V <sub>LCD</sub>      | LCD supply voltage range             | Internal boost circuit enabled                                                                                                         | 2.0 |      | 3.8 | V    |

|                       |                                      | Display disconnected, stat-<br>ic mode, framerate 32 Hz, all<br>segments on.                                                           |     | 250  |     | nA   |

| I <sub>LCD</sub>      | Steady state current consumption.    | Display disconnected, quadru-<br>plex mode, framerate 32<br>Hz, all segments on, bias<br>mode to ONETHIRD in<br>LCD_DISPCTRL register. |     | 550  |     | nA   |

|                       | Steady state Cur-                    | Internal voltage boost off                                                                                                             |     | 0    |     | μA   |

| I <sub>LCDBOOST</sub> | rent contribution of internal boost. | Internal voltage boost on,<br>boosting from 2.2 V to 3.0 V.                                                                            |     | 8.4  |     | μA   |

|                       |                                      | VBLEV of LCD_DISPCTRL register to LEVEL0                                                                                               |     | 3.02 |     | V    |

|                       |                                      | VBLEV of LCD_DISPCTRL register to LEVEL1                                                                                               |     | 3.15 |     | V    |

|                       |                                      | VBLEV of LCD_DISPCTRL register to LEVEL2                                                                                               |     | 3.28 |     | V    |

| V                     | Popot Voltago                        | VBLEV of LCD_DISPCTRL register to LEVEL3                                                                                               |     | 3.41 |     | V    |

| V <sub>BOOST</sub>    | Boost Voltage                        | VBLEV of LCD_DISPCTRL register to LEVEL4                                                                                               |     | 3.54 |     | V    |

|                       |                                      | VBLEV of LCD_DISPCTRL register to LEVEL5                                                                                               |     | 3.67 |     | V    |

|                       |                                      | VBLEV of LCD_DISPCTRL register to LEVEL6                                                                                               |     | 3.73 |     | V    |

|                       |                                      | VBLEV of LCD_DISPCTRL register to LEVEL7                                                                                               |     | 3.74 |     | V    |

The total LCD current is given by Equation 3.3 (p. 50). *I*<sub>LCDBOOST</sub> is zero if internal boost is off.

#### Total LCD Current Based on Operational Mode and Internal Boost

$I_{LCDTOTAL} = I_{LCD} + I_{LCDBOOST}$

(3.3)

#### Table 3.23. I2C Fast-mode Plus (Fm+)

| Symbol              | Parameter                                               | Min  | Тур | Max               | Unit |

|---------------------|---------------------------------------------------------|------|-----|-------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                     | 0    |     | 1000 <sup>1</sup> | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                                      | 0.5  |     |                   | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                                     | 0.26 |     |                   | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                         | 50   |     |                   | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                           | 8    |     |                   | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time                    | 0.26 |     |                   | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time                    | 0.26 |     |                   | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                              | 0.26 |     |                   | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and a START condi-<br>tion | 0.5  |     |                   | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode Plus, see the I2C chapter in the EFM32WG Reference Manual.

# 3.17 USART SPI

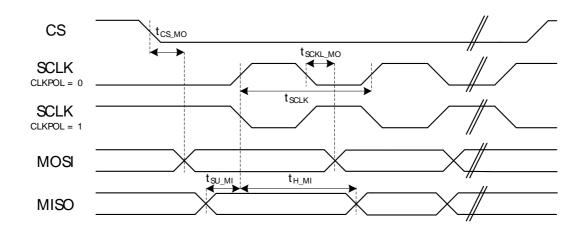

#### Figure 3.38. SPI Master Timing

#### Table 3.24. SPI Master Timing

| Symbol                            | Parameter       | Condition     | Min                            | Тур | Max  | Unit |

|-----------------------------------|-----------------|---------------|--------------------------------|-----|------|------|

| t <sub>SCLK</sub> <sup>12</sup>   | SCLK period     |               | 2 * t <sub>HFPER-</sub><br>CLK |     |      | ns   |

| t <sub>CS_MO</sub> <sup>12</sup>  | CS to MOSI      |               | -2.00                          |     | 2.00 | ns   |

| t <sub>SCLK_MO<sup>12</sup></sub> | SCLK to MOSI    |               | -1.00                          |     | 3.00 | ns   |

| t <sub>SU_MI</sub> <sup>1 2</sup> | MISO setup time | IOVDD = 3.0 V | 36.00                          |     |      | ns   |

| t <sub>H_MI</sub> <sup>1 2</sup>  | MISO hold time  |               | -6.00                          |     |      | ns   |

<sup>1</sup>Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

$^2\text{Measurement}$  done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $V_{\text{DD}})$

# **4 Pinout and Package**

#### Note

Please refer to the application note "AN0002 EFM32 Hardware Design Considerations" for guidelines on designing Printed Circuit Boards (PCB's) for the EFM32WG942.

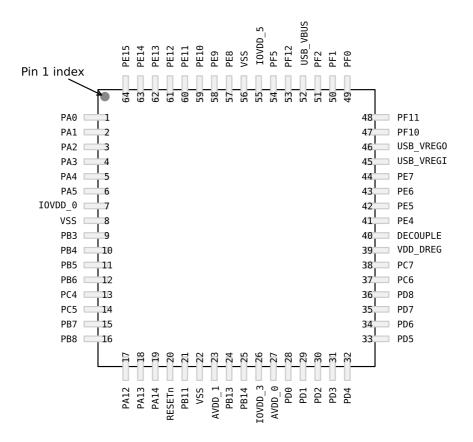

## 4.1 Pinout

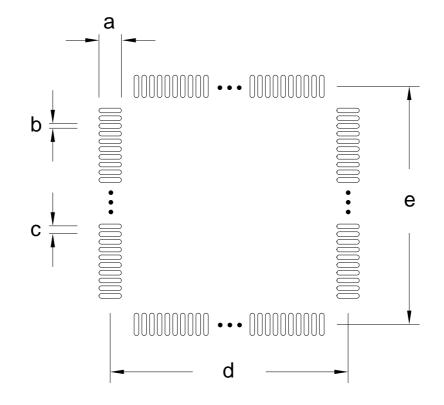

The *EFM32WG942* pinout is shown in Figure 4.1 (p. 55) and Table 4.1 (p. 55). Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

#### Figure 4.1. EFM32WG942 Pinout (top view, not to scale)

Table 4.1. Device Pinout

| QFP64 Pin#<br>and Name |          | Pin Alternate Functionality / Description |                 |                           |                           |  |  |  |  |

|------------------------|----------|-------------------------------------------|-----------------|---------------------------|---------------------------|--|--|--|--|

| Pin #                  | Pin Name | Analog                                    | Timers          | Communication             | Other                     |  |  |  |  |

| 1                      | PA0      | LCD_SEG13                                 | TIM0_CC0 #0/1/4 | LEU0_RX #4<br>I2C0_SDA #0 | PRS_CH0 #0<br>GPIO_EM4WU0 |  |  |  |  |

| 2                      | PA1      | LCD_SEG14                                 | TIM0_CC1 #0/1   | I2C0_SCL #0               | CMU_CLK1 #0<br>PRS_CH1 #0 |  |  |  |  |

| 3                      | PA2      | LCD_SEG15                                 | TIM0_CC2 #0/1   |                           | CMU_CLK0 #0               |  |  |  |  |

#### ...the world's most energy friendly microcontrollers

| Alternate                       |      |      | LOC |     |     |     |      |                                                                                                                                                                      |

|---------------------------------|------|------|-----|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality                   | 0    | 1    | 2   | 3   | 4   | 5   | 6    | Description                                                                                                                                                          |

| OPAMP_N1                        |      |      |     |     |     |     |      |                                                                                                                                                                      |

| OPAMP_N2                        | PD3  |      |     |     |     |     |      | Operational Amplifier 2 external negative input.                                                                                                                     |

| DAC0_OUT0 /<br>OPAMP_OUT0       | PB11 |      |     |     |     |     |      | Digital to Analog Converter DAC0_OUT0 /<br>OPAMP output channel number 0.                                                                                            |

| DAC0_OUT0ALT /<br>OPAMP_OUT0ALT |      |      |     |     | PD0 |     |      | Digital to Analog Converter DAC0_OUT0ALT / OPAMP alternative output for channel 0.                                                                                   |

| DAC0_OUT1ALT /<br>OPAMP_OUT1ALT |      |      |     |     | PD1 |     |      | Digital to Analog Converter DAC0_OUT1ALT /<br>OPAMP alternative output for channel 1.                                                                                |

| OPAMP_OUT2                      | PD5  | PD0  |     |     |     |     |      | Operational Amplifier 2 output.                                                                                                                                      |

| DAC0_P0 /<br>OPAMP_P0           | PC4  |      |     |     |     |     |      | Operational Amplifier 0 external positive input.                                                                                                                     |

| DAC0_P1 /<br>OPAMP_P1           | PD6  |      |     |     |     |     |      | Operational Amplifier 1 external positive input.                                                                                                                     |

| OPAMP_P2                        | PD4  |      |     |     |     |     |      | Operational Amplifier 2 external positive input.                                                                                                                     |

|                                 |      |      |     |     |     |     |      | Debug-interface Serial Wire clock input.                                                                                                                             |

| DBG_SWCLK                       | PF0  | PF0  | PF0 | PF0 |     |     |      | Note that this function is enabled to pin out of reset, and has a built-in pull down.                                                                                |

|                                 |      |      |     |     |     |     |      | Debug-interface Serial Wire data input / output.                                                                                                                     |

| DBG_SWDIO                       | PF1  | PF1  | PF1 | PF1 |     |     |      | Note that this function is enabled to pin out of reset, and has a built-in pull up.                                                                                  |

|                                 |      |      |     |     |     |     |      | Debug-interface Serial Wire viewer Output.                                                                                                                           |

| DBG_SWO                         | PF2  |      | PD1 | PD2 |     |     |      | Note that this function is not enabled after reset, and must be enabled by software to be used.                                                                      |

| ETM_TCLK                        | PD7  |      | PC6 |     |     |     |      | Embedded Trace Module ETM clock .                                                                                                                                    |

| ETM_TD0                         | PD6  |      | PC7 | PA2 |     |     |      | Embedded Trace Module ETM data 0.                                                                                                                                    |

| ETM_TD1                         | PD3  |      | PD3 | PA3 |     |     |      | Embedded Trace Module ETM data 1.                                                                                                                                    |

| ETM_TD2                         | PD4  |      | PD4 | PA4 |     |     |      | Embedded Trace Module ETM data 2.                                                                                                                                    |

| ETM_TD3                         | PD5  |      | PD5 | PA5 |     |     |      | Embedded Trace Module ETM data 3.                                                                                                                                    |

| GPIO_EM4WU0                     | PA0  |      |     |     |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                       |

| GPIO_EM4WU3                     | PF1  |      |     |     |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                       |

| GPIO_EM4WU4                     | PF2  |      |     |     |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                       |

| GPIO_EM4WU5                     | PE13 |      |     |     |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                       |

| HFXTAL_N                        | PB14 |      |     |     |     |     |      | High Frequency Crystal negative pin. Also used as exter-<br>nal optional clock input pin.                                                                            |

| HFXTAL_P                        | PB13 |      |     |     |     |     |      | High Frequency Crystal positive pin.                                                                                                                                 |

| I2C0_SCL                        | PA1  | PD7  | PC7 |     |     | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                                                                                                               |

| I2C0_SDA                        | PA0  | PD6  | PC6 |     |     | PF0 | PE12 | I2C0 Serial Data input / output.                                                                                                                                     |

| I2C1_SCL                        | PC5  |      |     |     |     |     |      | I2C1 Serial Clock Line input / output.                                                                                                                               |

| I2C1_SDA                        | PC4  | PB11 |     |     |     |     |      | I2C1 Serial Data input / output.                                                                                                                                     |

| LCD_BCAP_N                      | PA13 |      |     |     |     |     |      | LCD voltage booster (optional), boost capacitor, negative<br>pin. If using the LCD voltage booster, connect a 22 nF ca<br>pacitor between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BCAP_P                      | PA12 |      |     |     |     |     |      | LCD voltage booster (optional), boost capacitor, positive<br>pin. If using the LCD voltage booster, connect a 22 nF ca<br>pacitor between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BEXT                        | PA14 |      |     |     |     |     |      | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.                                   |

|                                 |      |      |     |     |     |     |      | An external LCD voltage may also be applied to this pin it the booster is not enabled.                                                                               |

#### ...the world's most energy friendly microcontrollers

| Alternate     |           |      | LOC | LOCATION |      |      |   |                                                                                             |

|---------------|-----------|------|-----|----------|------|------|---|---------------------------------------------------------------------------------------------|

| Functionality | 0         | 1    | 2   | 3        | 4    | 5    | 6 | Description                                                                                 |

| US0_CLK       | PE12      | PE5  |     |          | PB13 | PB13 |   | USART0 clock input / output.                                                                |

| US0_CS        | PE13      | PE4  |     |          | PB14 | PB14 |   | USART0 chip select input / output.                                                          |

|               |           |      |     |          |      |      |   | USART0 Asynchronous Receive.                                                                |

| US0_RX        | PE11      | PE6  |     | PE12     | PB8  |      |   | USART0 Synchronous mode Master Input / Slave Output (MISO).                                 |

| US0_TX        | PE10      | PE7  |     | PE13     | PB7  |      |   | USART0 Asynchronous Transmit.Also used as receive in-<br>put in half duplex communication.  |

|               |           |      |     |          |      |      |   | USART0 Synchronous mode Master Output / Slave Input (MOSI).                                 |

| US1_CLK       | PB7       | PD2  | PF0 |          |      |      |   | USART1 clock input / output.                                                                |

| US1_CS        | PB8       | PD3  | PF1 |          |      |      |   | USART1 chip select input / output.                                                          |

|               |           |      |     |          |      |      |   | USART1 Asynchronous Receive.                                                                |

| US1_RX        |           | PD1  | PD6 |          |      |      |   | USART1 Synchronous mode Master Input / Slave Output (MISO).                                 |

| US1_TX        |           | PD0  | PD7 |          |      |      |   | USART1 Asynchronous Transmit.Also used as receive in-<br>put in half duplex communication.  |

|               |           |      |     |          |      |      |   | USART1 Synchronous mode Master Output / Slave Input (MOSI).                                 |

| US2_CLK       | PC4       | PB5  |     |          |      |      |   | USART2 clock input / output.                                                                |

| US2_CS        | PC5       | PB6  |     |          |      |      |   | USART2 chip select input / output.                                                          |

|               |           |      |     |          |      |      |   | USART2 Asynchronous Receive.                                                                |

| US2_RX        |           | PB4  |     |          |      |      |   | USART2 Synchronous mode Master Input / Slave Output (MISO).                                 |

| US2_TX        |           | PB3  |     |          |      |      |   | USART2 Asynchronous Transmit. Also used as receive in-<br>put in half duplex communication. |

| 032_17        |           | F D3 |     |          |      |      |   | USART2 Synchronous mode Master Output / Slave Input (MOSI).                                 |

| USB_DM        | PF10      |      |     |          |      |      |   | USB D- pin.                                                                                 |

| USB_DMPU      | PD2       |      |     |          |      |      |   | USB D- Pullup control.                                                                      |

| USB_DP        | PF11      |      |     |          |      |      |   | USB D+ pin.                                                                                 |

| USB_ID        | PF12      |      |     |          |      |      |   | USB ID pin. Used in OTG mode.                                                               |

| USB_VBUS      | USB_VBUS  |      |     |          |      |      |   | USB 5 V VBUS input.                                                                         |

| USB_VBUSEN    | PF5       |      |     |          |      |      |   | USB 5 V VBUS enable.                                                                        |

| USB_VREGI     | USB_VREGI |      |     |          |      |      |   | USB Input to internal 3.3 V regulator                                                       |

| USB_VREGO     | USB_VREGO |      |     |          |      |      |   | USB Decoupling for internal 3.3 V USB regulator and regulator output                        |

## 4.3 GPIO Pinout Overview

The specific GPIO pins available in *EFM32WG942* is shown in Table 4.3 (p. 63). Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port in indicated by a number from 15 down to 0.

#### Figure 5.2. TQFP64 PCB Solder Mask

Table 5.2. QFP64 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.72      |

| b      | 0.42      |

| с      | 0.50      |

| d      | 11.50     |

| e      | 11.50     |

Updated the EM0 and EM1 current consumption numbers. Updated the the EM1 plots and removed the EM0 plots.

Updated Environmental information.

Updated trademark, disclaimer and contact information.

Other minor corrections.

## 7.4 Revision 1.20

June 28th, 2013

Updated power requirements in the Power Management section.

Removed minimum load capacitance figure and table. Added reference to application note.

Other minor corrections.

## 7.5 Revision 1.10

May 6th, 2013

Updated current consumption table and figures in Electrical characteristics section.

Other minor corrections.

## 7.6 Revision 1.00

September 11th, 2012

Updated the HFRCO 1 MHz band typical value to 1.2 MHz.

Updated the HFRCO 7 MHz band typical value to 6.6 MHz.

Other minor corrections.

### 7.7 Revision 0.95

May 3rd, 2012

Updated EM2/EM3 current consumption at 85°C.

## 7.8 Revision 0.90

February 27th, 2012

Initial preliminary release.

# silabs.com