Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Data ila                   |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Details                    |                                                                       |

| Product Status             | Obsolete                                                              |

| Core Processor             | CPU32                                                                 |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                             |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 18                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 7.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                         |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 160-BQFP                                                              |

| Supplier Device Package    | 160-QFP (28x28)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68336acab25 |

Table 3-1 MC68336/376 Pin Characteristics (Continued)

| Pin Mnemonic      | Output<br>Driver | Input<br>Synchronized | Input<br>Hysteresis | Discrete<br>I/O | Port<br>Designation |

|-------------------|------------------|-----------------------|---------------------|-----------------|---------------------|

| SIZ[1:0]          | В                | Yes                   | Yes                 | I/O             | PE[7:6]             |

| T2CLK             | _                | Yes                   | Yes                 | _               | _                   |

| TPUCH[15:0]       | A                | Yes                   | Yes                 | _               | _                   |

| TSTME/TSC         | _                | Yes                   | Yes                 | _               | _                   |

| TXD               | Во               | Yes <sup>1</sup>      | Yes                 | I/O             | PQS7                |

| XFC <sup>2</sup>  | _                | _                     | _                   | Special         | _                   |

| XTAL <sup>2</sup> | _                | _                     | _                   | Special         | _                   |

#### NOTES:

- 1. DATA[15:0] are synchronized during reset only. MODCLK, and the QSM and QADC pins are synchronized only when used as input port pins.

- 2. EXTAL, XFC and XTAL are clock reference connections.

# Table 3-2 MC68336/376 Output Driver Types

| Туре | Description                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α    | Output only signals that are always driven. No external pull-up required.                                                                                                                                                        |

| Ao   | Type A output that can be operated in an open-drain mode.                                                                                                                                                                        |

| Aw   | Type A output with p-channel precharge when reset.                                                                                                                                                                               |

| В    | Three-state output that includes circuitry to assert output before high impedance is established, to ensure rapid rise time. An external holding resistor is required to maintain logic level while in the high-impedance state. |

| Во   | Type B output that can be operated in an open-drain mode.                                                                                                                                                                        |

| Ва   | Three-state output that can be operated in open-drain mode only.                                                                                                                                                                 |

### Table 3-3 MC68336/376 Power Connections

| Pin                                 | Description             |

|-------------------------------------|-------------------------|

| V <sub>STBY</sub>                   | Standby RAM power       |

| V <sub>DDSYN</sub>                  | Clock synthesizer power |

| V <sub>DDA</sub> , V <sub>SSA</sub> | QADC converter power    |

| V <sub>RH,</sub> V <sub>RL</sub>    | QADC reference voltage  |

| V <sub>SS</sub> , V <sub>DD</sub>   | Microcontroller power   |

### 3.6 Internal Register Map

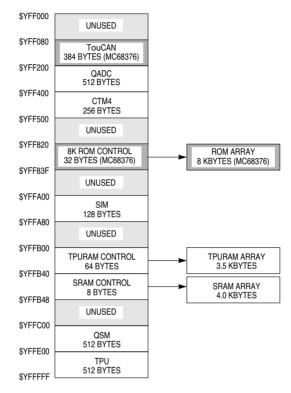

In **Figure 3-4**, IMB ADDR[23:20] are represented by the letter Y. The value represented by Y determines the base address of MCU module control registers. In the MC68336/376, Y is equal to M111, where M is the logic state of the module mapping (MM) bit in the system integration module configuration register (SIMCR).

NOTES: 1. Y=M111, WHERE M IS THE MODMAP SIGNAL STATE ON THE IMB, WHICH REFLECTS THE STATE OF THE MODMAP IN THE MODULE CONFIGURATION REGISTER OF THE SYSTEM INTEGRATION MODULE. (Y=\$7 OR \$F)

2. ATTEMPTED ACCESSES TO UNUSED LOCATIONS OR UNUSED BITS WITHIN VALID LOCATIONS RETURN ALL ZEROS.

336/376 ADDRESS MAP

Figure 3-4 MC68336/376 Address Map

MC68336/376 **OVERVIEW** MOTOROLA USER'S MANUAL 3-13

**Table 4-2 Instruction Set Summary (Continued)**

| NEO                    |                                             | 0.40.00                      | O Destination Bestination                                                                                                           |

|------------------------|---------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| NEG                    | <ea></ea>                                   | 8, 16, 32                    | 0 – Destination ⇒ Destination                                                                                                       |

| NEGX                   | <ea></ea>                                   | 8, 16, 32                    | 0 – Destination – X ⇒ Destination                                                                                                   |

| NOP                    | none                                        | none                         | PC + 2 ⇒ PC                                                                                                                         |

| NOT                    | <ea></ea>                                   | 8, 16, 32                    | Destination ⇒ Destination                                                                                                           |

| OR                     | <ea>, Dn<br/>Dn, <ea></ea></ea>             | 8, 16, 32<br>8, 16, 32       | Source + Destination ⇒ Destination                                                                                                  |

| ORI                    | # <data>, <ea></ea></data>                  | 8, 16, 32                    | Data + Destination ⇒ Destination                                                                                                    |

| ORI to CCR             | # <data>, CCR</data>                        | 16                           | Source + CCR ⇒ SR                                                                                                                   |

| ORI to SR <sup>1</sup> | # <data>, SR</data>                         | 16                           | Source ; SR ⇒ SR                                                                                                                    |

| PEA                    | <ea></ea>                                   | 32                           | $SP-4 \Rightarrow SP; \langle ea \rangle \Rightarrow SP$                                                                            |

| RESET <sup>1</sup>     | none                                        | none                         | Assert RESET line                                                                                                                   |

| ROL                    | Dn, Dn<br># <data>, Dn<br/><ea></ea></data> | 8, 16, 32<br>8, 16, 32<br>16 | C                                                                                                                                   |

| ROR                    | Dn, Dn<br># <data>, Dn<br/><ea></ea></data> | 8, 16, 32<br>8, 16, 32<br>16 | - C                                                                                                                                 |

| ROXL                   | Dn, Dn<br># <data>, Dn<br/><ea></ea></data> | 8, 16, 32<br>8, 16, 32<br>16 | C - X -                                                                                                                             |

| ROXR                   | Dn, Dn<br># <data>, Dn<br/><ea></ea></data> | 8, 16, 32<br>8, 16, 32<br>16 | X > C                                                                                                                               |

| RTD                    | #d                                          | 16                           | $(SP) \Rightarrow PC; SP + 4 + d \Rightarrow SP$                                                                                    |

| RTE <sup>1</sup>       | none                                        | none                         | $(SP) \Rightarrow SR; SP + 2 \Rightarrow SP; (SP) \Rightarrow PC;$<br>$SP + 4 \Rightarrow SP;$<br>Restore stack according to format |

| RTR                    | none                                        | none                         | $(SP) \Rightarrow CCR; SP + 2 \Rightarrow SP; (SP) \Rightarrow PC; SP + 4 \Rightarrow SP$                                           |

| RTS                    | none                                        | none                         | $(SP) \Rightarrow PC; SP + 4 \Rightarrow SP$                                                                                        |

| SBCD                   | Dn, Dn<br>- (An), - (An)                    | 8<br>8                       | Destination10 – Source10 – X ⇒ Destination                                                                                          |

| Scc                    | <ea></ea>                                   | 8                            | If condition true, then destination bits are set to one; else, destination bits are cleared to zero                                 |

| STOP <sup>1</sup>      | # <data></data>                             | 16                           | Data ⇒ SR; STOP                                                                                                                     |

| SUB                    | <ea>, Dn<br/>Dn, <ea></ea></ea>             | 8, 16, 32                    | Destination – Source ⇒ Destination                                                                                                  |

| SUBA                   | <ea>, An</ea>                               | 16, 32                       | Destination – Source ⇒ Destination                                                                                                  |

| SUBI                   | # <data>, <ea></ea></data>                  | 8, 16, 32                    | Destination – Data ⇒ Destination                                                                                                    |

| SUBQ                   | # <data>, <ea></ea></data>                  | 8, 16, 32                    | Destination – Data ⇒ Destination                                                                                                    |

| SUBX                   | Dn, Dn<br>- (An), - (An)                    | 8, 16, 32<br>8, 16, 32       | Destination – Source – X ⇒ Destination                                                                                              |

| SWAP                   | Dn                                          | 16                           | MSW LSW                                                                                                                             |

| TAS                    | <ea></ea>                                   | 8                            | Destination Tested Condition Codes bit 7 of Destination                                                                             |

| TBLS/TBLU              | <ea>, Dn<br/>Dym : Dyn, Dn</ea>             | 8, 16, 32                    | Dyn - Dym ⇒ Temp<br>(Temp * Dn [7 : 0]) ⇒ Temp<br>(Dym * 256) + Temp ⇒ Dn                                                           |

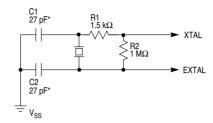

To generate a reference frequency using the crystal oscillator, a reference crystal must be connected between the EXTAL and XTAL pins. Typically, a 4.194 MHz crystal is used, but the frequency may vary between 1 and 6 MHz. **Figure 5-3** shows a typical circuit.

<sup>\*</sup> RESISTANCE AND CAPACITANCE BASED ON A TEST CIRCUIT CONSTRUCTED WITH A KDS041-18 4.194 MHz CRYSTAL. SPECIFIC COMPONENTS MUST BE BASED ON CRYSTAL TYPE. CONTACT CRYSTAL VENDOR FOR EXACT CIRCUIT.

32 OSCILLATOR 4M

Figure 5-3 System Clock Oscillator Circuit

If a fast reference frequency is provided to the PLL from a source other than a crystal, or an external system clock signal is applied through the EXTAL pin, the XTAL pin must be left floating.

When an external system clock signal is applied (MODCLK = 0 during reset), the PLL is disabled. The duty cycle of this signal is critical, especially at operating frequencies close to maximum. The relationship between clock signal duty cycle and clock signal period is expressed as follows:

Minimum External Clock Period =

Minimum External Clock High/Low Time

50% – Percentage Variation of External Clock Input Duty Cycle

# 5.3.2 Clock Synthesizer Operation

$V_{DDSYN}$  is used to power the clock circuits when the system clock is synthesized from either a crystal or an externally supplied reference frequency. A separate power source increases MCU noise immunity and can be used to run the clock when the MCU is powered down. A quiet power supply must be used as the  $V_{DDSYN}$  source. Adequate external bypass capacitors should be placed as close as possible to the  $V_{DDSYN}$  pin to assure a stable operating frequency. When an external system clock signal is applied and the PLL is disabled,  $V_{DDSYN}$  should be connected to the  $V_{DD}$  supply. Refer to the SIM Reference Manual (SIMRM/AD) for more information regarding system clock power supply conditioning.

When the clock synthesizer is used, SYNCR determines the system clock frequency and certain operating parameters. The W and Y[5:0] bits are located in the PLL feedback path, enabling frequency multiplication by a factor of up to 256. When the W or Y values change, VCO frequency changes, and there is a VCO relock delay. The SYNCR X bit controls a divide-by circuit that is not in the synthesizer feedback loop. When X=0 (reset state), a divide-by-four circuit is enabled, and the system clock frequency is one-fourth the VCO frequency ( $f_{VCO}$ ). When X=1, a divide-by-two circuit is enabled and system clock frequency is one-half the VCO frequency ( $f_{VCO}$ ). There is no relock delay when clock speed is changed by the X bit.

Clock frequency is determined by SYNCR bit settings as follows:

$$f_{sys} = \frac{f_{ref}}{128} [4(Y+1)(2^{(2W+X)})]$$

The reset state of SYNCR (\$3F00) results in a power-on  $f_{sys}$  of 8.388 MHz when  $f_{ref}$  is 4.194 MHz.

For the device to operate correctly, the clock frequency selected by the W, X, and Y bits must be within the limits specified for the MCU.

Internal VCO frequency is determined by the following equations:

$$f_{VCO} = 4f_{sys}$$

if  $X = 0$

or

$$f_{VCO} = 2f_{sys}$$

if  $X = 1$

**Table 5-2** shows clock control multipliers for all possible combinations of SYNCR bits. To obtain clock frequency, find counter modulus in the leftmost column, then multiply the reference frequency by the value in the appropriate prescaler cell. Shaded cells exceed the maximum system clock frequency at the time of manual publication; however, they may be usable in the future. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for maximum allowable clock rate.

**Table 5-3** shows clock frequencies available with a 4.194 MHz reference and a maximum specified clock frequency of 20.97 MHz. To obtain clock frequency, find counter modulus in the leftmost column, then refer to appropriate prescaler cell. Shaded cells exceed the maximum system clock frequency at the time of manual publication; however, they may be usable in the future. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for maximum system frequency (f<sub>sys</sub>).

When an external device asserts  $\overline{\text{RESET}}$  for the proper period, reset control logic clocks the signal into an internal latch. The control logic drives the  $\overline{\text{RESET}}$  pin low for an additional 512 CLKOUT cycles after it detects that the  $\overline{\text{RESET}}$  signal is no longer being externally driven to guarantee this length of reset to the entire system.

If an internal source asserts a reset signal, the reset control logic asserts the RESET pin for a minimum of 512 cycles. If the reset signal is still asserted at the end of 512 cycles, the control logic continues to assert the RESET pin until the internal reset signal is negated.

After 512 cycles have elapsed, the RESET pin goes to an inactive, high-impedance state for ten cycles. At the end of this 10-cycle period, the RESET input is tested. When the input is at logic level one, reset exception processing begins. If, however, the RESET input is at logic level zero, reset control logic drives the pin low for another 512 cycles. At the end of this period, the pin again goes to high-impedance state for ten cycles, then it is tested again. The process repeats until RESET is released.

#### 5.7.7 Power-On Reset

When the SIM clock synthesizer is used to generate system clocks, power-on reset involves special circumstances related to application of system and clock synthesizer power. Regardless of clock source, voltage must be applied to the clock synthesizer power input pin  $V_{\rm DDSYN}$  for the MCU to operate. The following discussion assumes that  $V_{\rm DDSYN}$  is applied before and during reset, which minimizes crystal start-up time. When  $V_{\rm DDSYN}$  is applied at power-on, start-up time is affected by specific crystal parameters and by oscillator circuit design.  $V_{\rm DD}$  ramp-up time also affects pin state during reset. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for voltage and timing specifications.

During power-on reset, an internal circuit in the SIM drives the IMB internal (MSTRST) and external (EXTRST) reset lines. The power-on reset circuit releases the internal reset line as  $V_{DD}$  ramps up to the minimum operating voltage, and SIM pins are initialized to the values shown in **Table 5-17**. When  $V_{DD}$  reaches the minimum operating voltage, the clock synthesizer VCO begins operation. Clock frequency ramps up to specified limp mode frequency ( $f_{limp}$ ). The external RESET line remains asserted until the clock synthesizer PLL locks and 512 CLKOUT cycles elapse.

The SIM clock synthesizer provides clock signals to the other MCU modules. After the clock is running and MSTRST is asserted for at least four clock cycles, these modules reset. V<sub>DD</sub> ramp time and VCO frequency ramp time determine how long the four cycles take. Worst case is approximately 15 milliseconds. During this period, module port pins may be in an indeterminate state. While input-only pins can be put in a known state by external pull-up resistors, external logic on input/output or output-only pins during this time must condition the lines. Active drivers require high-impedance buffers or isolation resistors to prevent conflict.

**Table 5-19 Pin Assignment Field Encoding**

| CSxPA[1:0] | Description               |

|------------|---------------------------|

| 00         | Discrete output           |

| 01         | Alternate function        |

| 10         | Chip-select (8-bit port)  |

| 11         | Chip-select (16-bit port) |

Port size determines the way in which bus transfers to an external address are allocated. Port size of eight bits or sixteen bits can be selected when a pin is assigned as a chip-select. Port size and transfer size affect how the chip-select signal is asserted. Refer to **5.9.1.3 Chip-Select Option Registers** for more information.

Out of reset, chip-select pin function is determined by the logic level on a corresponding data bus pin. The data bus pins have weak internal pull-up drivers, but can be held low by external devices. Refer to **5.7.3.1 Data Bus Mode Selection** for more information. Either 16-bit chip-select function (%11) or alternate function (%01) can be selected during reset. All pins except the boot ROM select pin (CSBOOT) are disabled out of reset. There are twelve chip-select functions and only eight associated data bus pins. There is not a one-to-one correspondence. Refer to **5.9.4 Chip-Select Reset Operation** for more detailed information.

The CSBOOT signal is enabled out of reset. The state of the DATA0 line during reset determines what port width CSBOOT uses. If DATA0 is held high (either by the weak internal pull-up driver or by an external pull-up device), 16-bit port size is selected. If DATA0 is held low, 8-bit port size is selected.

A pin programmed as a discrete output drives an external signal to the value specified in the port C register. No discrete output function is available on pins CSBOOT, BR, BG, or BGACK. ADDR23 provides the ECLK output rather than a discrete output signal.

When a pin is programmed for discrete output or alternate function, internal chip-select logic still functions and can be used to generate  $\overline{\mathsf{DSACK}}$  or  $\overline{\mathsf{AVEC}}$  internally on an address and control signal match.

# 5.9.1.2 Chip-Select Base Address Registers

Each chip-select has an associated base address register. A base address is the lowest address in the block of addresses enabled by a chip-select. Block size is the extent of the address block above the base address. Block size is determined by the value contained in BLKSZ[2:0]. Multiple chip-selects assigned to the same block of addresses must have the same number of wait states.

BLKSZ[2:0] determines which bits in the base address field are compared to corresponding bits on the address bus during an access. Provided other constraints determined by option register fields are also satisfied, when a match occurs, the associated chip-select signal is asserted. **Table 5-20** shows BLKSZ[2:0] encoding.

### 8.4.1.1 Port A Analog Input Pins

When used as analog inputs, the eight port A pins are referred to as AN[59:52]. Due to the digital output drivers associated with port A, the analog characteristics of port A are different from those of port B. All of the analog signal input pins may be used for at least one other purpose.

# 8.4.1.2 Port A Digital Input/Output Pins

Port A pins are referred to as PQA[7:0] when used as a bidirectional 8-bit digital input/output port. These eight pins may be used for general-purpose digital input signals or digital open drain pull-down output signals.

Port A pins are connected to a digital input synchronizer during reads and may be used as general purpose digital inputs.

Each port A pin is configured as an input or output by programming the port data direction register (DDRQA). Digital input signal states are read from the PORTQA data register when DDRQA specifies that the pins are inputs. Digital data in PORTQA is driven onto the port A pins when the corresponding bits in DDRQA specify outputs. Refer to **D.5.5 Port Data Direction Register** for more information. Since the outputs are open drain drivers (so as to minimize the effects to the analog function of the pins), external pull-up resistors must be used when port A pins are used to drive another device.

#### 8.4.2 Port B Pin Functions

The eight port B pins can be used as analog inputs, or as an 8-bit digital input only port. Refer to the following paragraphs for more information.

# 8.4.2.1 Port B Analog Input Pins

When used as analog inputs, the eight port B pins are referred to as AN[51:48]/ AN[3:0]. Since port B functions as analog and digital input only, the analog characteristics are different from those of port A. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information on analog signal characteristics. All of the analog signal input pins may be used for at least one other purpose.

### 8.4.2.2 Port B Digital Input Pins

Port B pins are referred to as PQB[7:0] when used as an 8-bit digital input only port. In addition to functioning as analog input pins, the port B pins are also connected to the input of a synchronizer during reads and may be used as general-purpose digital inputs.

Since port B pins are input only, there is no associated data direction register. Digital input signal states are read from the PORTQB data register. Refer to **D.5.5 Port Data Direction Register** for more information.

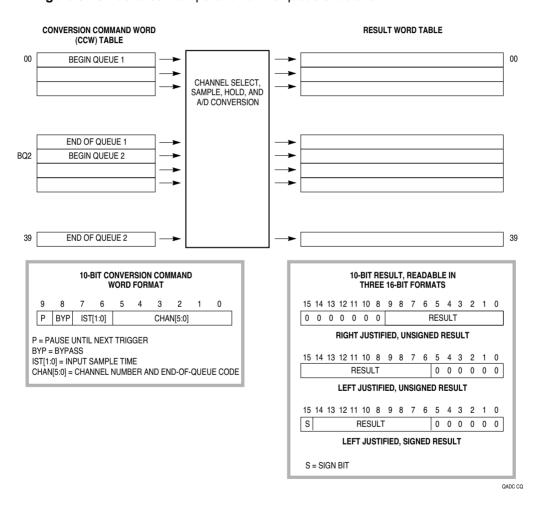

The ten implemented bits of the CCW word can be read and written. Unimplemented bits are read as zeros, and write operations have no effect. Each location in the CCW table corresponds to a location in the result word table. When a conversion is completed for a CCW entry, the 10-bit result is written in the corresponding result word entry.

The beginning of queue 1 is the first location in the CCW table. The first location of queue 2 is specified by the beginning of queue 2 pointer BQ2 in QACR2. To dedicate the entire CCW table to queue 1, queue 2 is disabled, and BQ2 is programmed to any value greater than 39. To dedicate the entire CCW table to queue 2, queue 1 is disabled, and BQ2 is specified as the first location in the CCW table.

**Figure 8-10** illustrates the operation of the queue structure.

Figure 8-10 QADC Conversion Queue Operation

#### 10.9.9 PWM Pulse Width

The shortest output pulse width (t<sub>PWMIN</sub>) that can be obtained is given by the following equation:

$$t_{PWMIN} = \frac{N_{CLOCK}}{f_{sys}}$$

The maximum output pulse width (t<sub>PWMAX</sub>) that can be obtained is given by the following equation:

$$t_{PWMAX} = \frac{N_{CLOCK} \cdot (N_{PERIOD} - 1)}{f_{svs}}$$

### 10.9.10 PWM Period and Pulse Width Register Values

The value loaded into PWMA1 to obtain a given period is:

$$PWMA1 = \frac{f_{sys}}{N_{CLOCK} \cdot f_{PWM}}$$

The value loaded into PWMB1 to obtain a given duty cycle is:

$$PWMB1 = \frac{1}{t_{PWMIN} \cdot f_{PWM}} = \frac{Duty \ Cycle \ \%}{100} \cdot PWMA1$$

### 10.9.10.1 PWM Duty Cycle Boundary Cases

PWM duty cycles 0% and 100% are special boundary cases (zero pulse width and infinite pulse width) that are defined by the "always clear" and "always set" states of the output flip-flop.

A zero width pulse is generated by setting PWMB2 to \$0000. The output is a true steady state signal. An infinite width pulse is generated by setting PWMB2 equal to or greater than the period value in PWMA2. In both cases, the state of the output pin will remain unchanged at the polarity defined by the POL bit in PWMSIC.

#### NOTE

A duty cycle of 100% is not possible when the output period is set to 65536 PWM clock periods (which occurs when PWMB2 is set to 0000). In this case, the maximum duty cycle is 99.998% ( $100 \times 65535/65536$ ).

Even when the duty cycle is 0% or 100%, the PWMSM counter continues to count.

# 10.9.11 PWMSM Registers

The PWMSM contains a status/interrupt/control register, a period register, a pulse width register, and a counter register. All unused bits and reserved address locations return zero when read. Writes to unused bits and reserved address locations have no effect. The CTM4 contains four PWMSMs, each with its own set of registers. Refer to

### 11.4.6 Period Measurement with Additional Transition Detect (PMA)

This function and the following function are used primarily in toothed-wheel speedsensing applications, such as monitoring rotational speed of an engine. The period measurement with additional transition detect function allows for a special-purpose 23-bit period measurement. It can detect the occurrence of an additional transition (caused by an extra tooth on the sensed wheel) indicated by a period measurement that is less than a programmable ratio of the previous period measurement.

Once detected, this condition can be counted and compared to a programmable number of additional transitions detected before TCR2 is reset to \$FFFF. Alternatively, a byte at an address specified by a channel parameter can be read and used as a flag. A non-zero value of the flag indicates that TCR2 is to be reset to \$FFFF once the next additional transition is detected.

Refer to TPU programming note *Period Measurement, Additional Transition Detect (PMA) TPU Function* (TPUPN15A/D) for more information.

### 11.4.7 Period Measurement with Missing Transition Detect (PMM)

Period measurement with missing transition detect allows a special-purpose 23-bit period measurement. It detects the occurrence of a missing transition (caused by a missing tooth on the sensed wheel), indicated by a period measurement that is greater than a programmable ratio of the previous period measurement. Once detected, this condition can be counted and compared to a programmable number of additional transitions detected before TCR2 is reset to \$FFFF. In addition, one byte at an address specified by a channel parameter can be read and used as a flag. A non-zero value of the flag indicates that TCR2 is to be reset to \$FFFF once the next missing transition is detected.

Refer to TPU programming note *Period Measurement, Missing Transition Detect (PMM) TPU Function* (TPUPN15B/D) for more information.

# 11.4.8 Position-Synchronized Pulse Generator (PSP)

Any channel of the TPU can generate an output transition or pulse, which is a projection in time based on a reference period previously calculated on another channel. Both TCRs are used in this algorithm: TCR1 is internally clocked, and TCR2 is clocked by a position indicator in the user's device. An example of a TCR2 clock source is a sensor that detects special teeth on the flywheel of an automobile using PMA or PMM. The teeth are placed at known degrees of engine rotation; hence, TCR2 is a coarse representation of engine degrees. For example, each count represents some number of degrees.

Up to 15 position-synchronized pulse generator function channels can operate with a single input reference channel executing a PMA or PMM input function. The input channel measures and stores the time period between the flywheel teeth and resets TCR2 when the engine reaches a reference position. The output channel uses the period calculated by the input channel to project output transitions at specific engine degrees. Because the flywheel teeth might be 30 or more degrees apart, a fractional

Table 13-7 Mask Examples for Normal/Extended Messages

| Message Buffer (MB)<br>/Mask | Base ID<br>ID[28:18] | IDE | Extended ID<br>ID[17:0] | Match           |

|------------------------------|----------------------|-----|-------------------------|-----------------|

| MB2                          | 11111111000          | 0   | _                       | _               |

| MB3                          | 11111111000          | 1   | 010101010101010101      | _               |

| MB4                          | 00000011111          | 0   | _                       | _               |

| MB5                          | 00000011101          | 1   | 010101010101010101      | _               |

| MB14                         | 11111111000          | 1   | 010101010101010101      | _               |

| RX Global Mask               | 11111111110          |     | 1111111000000000001     | _               |

| RX Message In                | 11111111001          | 1   | 010101010101010101      | 3 <sup>1</sup>  |

|                              | 11111111001          | 0   | _                       | 2 <sup>2</sup>  |

|                              | 11111111001          | 1   | 010101010101010100      | 3               |

|                              | 01111111000          | 0   | _                       | 4               |

|                              | 01111111000          | 1   | 010101010101010101      | 5               |

| RX 14 Mask                   | 01111111111          |     | 1111111000000000000     | _               |

| RX Message In                | 10111111000          | 1   | 010101010101010101      | 6               |

|                              | 01111111000          | 1   | 010101010101010101      | 14 <sup>7</sup> |

#### NOTES:

- 1. Match for extended format (MB3).

- 2. Match for standard format (MB2).

- 3. No match for MB3 because of ID0.

- 4. No match for MB2 because of ID28.

- 5. No match for MB3 because of ID28, match for MB14.

- 6. No match for MB14 because of ID27.

- 7. Match for MB14.

### 13.4.3 Bit Timing

The TouCAN module uses three 8-bit registers to set-up the bit timing parameters required by the CAN protocol. Control registers 1 and 2 (CANCTRL1, CANCTRL2) contain the PROPSEG, PSEG1, PSEG2, and the RJW fields which allow the user to configure the bit timing parameters. The prescaler divide register (PRESDIV) allows the user to select the ratio used to derive the S-clock from the system clock. The time quanta clock operates at the S-clock frequency. **Table 13-8** provides examples of system clock, CAN bit rate, and S-clock bit timing parameters. Refer to **APPENDIX D REGISTER SUMMARY** for more information on the bit timing registers.

At the end of a successful transmission, the value of the free-running timer (which was captured at the beginning of the identifier field on the CAN bus), is written into the time stamp field in the message buffer. The code field in the control/status word of the message buffer is updated and a status flag is set in the IFLAG register.

### 13.5.3.1 Transmit Message Buffer Deactivation

Any write access to the control/status word of a transmit message buffer during the process of selecting a message buffer for transmission immediately deactivates that message buffer, removing it from the transmission process.

While a message is being transferred from a transmit message buffer to a serial message buffer, if the user deactivates that transmit message buffer, the message will not be transmitted.

If the user deactivates the transmit message buffer after the message is transferred to the serial message buffer, the message will be transmitted, but no interrupt will be requested and the transmit code will not be updated.

If a message buffer containing the lowest ID is deactivated while that message is undergoing the internal arbitration process to determine which message should be sent, then that message may not be transmitted.

### 13.5.3.2 Reception of Transmitted Frames

The TouCAN will receive a frame it has transmitted if an empty message buffer with a matching identifier exists.

#### 13.5.4 Receive Process

The receive process includes configuring message buffers for reception, the transfer of received messages by the TouCAN from the serial message buffers to the receive message buffers with matching IDs, and the retrieval of these messages by the user.

The user should prepare/change a message buffer for frame reception by executing the following steps.

- 1. Write the control/status word to hold the receive buffer inactive (code = %0000).

- 2. Write the ID\_HIGH and ID\_LOW words.

- 3. Write the control/status word to mark the receive message buffer as active and empty.

### **NOTE**

Steps 1 and 3 are mandatory for data coherency while preparing a message buffer for reception.

Once these steps are performed, the message buffer functions as an active receive buffer and participates in the internal matching process, which takes place every time the TouCAN receives an error-free frame. In this process, all active receive buffers compare their ID value to the newly received one. If a match is detected, the following actions occur:

### Table A-6 AC Timing (Continued)

$(V_{DD} \text{ and } V_{DDSYN} = 5.0 \text{ Vdc} \pm 5\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num | Characteristic                     | Symbol            | Min | Max | Unit             |

|-----|------------------------------------|-------------------|-----|-----|------------------|

| 76  | Mode Select Hold Time              | t <sub>MSH</sub>  | 0   | _   | ns               |

| 77  | RESET Assertion Time <sup>13</sup> | t <sub>RSTA</sub> | 4   | _   | t <sub>cyc</sub> |

| 78  | RESET Rise Time <sup>14, 15</sup>  | t <sub>RSTR</sub> | _   | 10  | t <sub>cyc</sub> |

#### NOTES:

- 1. All AC timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub> levels unless otherwise noted.

- 2. The base configuration of the MC68336/376 requires a 20.97 MHz crystal reference.

- 3. When an external clock is used, minimum high and low times are based on a 50% duty cycle. The minimum allowable t<sub>Xcyc</sub> period is reduced when the duty cycle of the external clock signal varies. The relationship between external clock input duty cycle and minimum t<sub>Xcyc</sub> is expressed:

Minimum  $t_{XCVC}$  period = minimum  $t_{XCHL}$  / (50% –external clock input duty cycle tolerance).

- 4. Parameters for an external clock signal applied while the internal PLL is disabled (MODCLK pin held low during reset). Does not pertain to an external VCO reference applied while the PLL is enabled (MODCLK pin held high during reset). When the PLL is enabled, the clock synthesizer detects successive transitions of the reference signal. If transitions occur within the correct clock period, rise/fall times and duty cycle are not critical.

- Address access time = (2.5 + WS) t<sub>cyc</sub> t<sub>CHAV</sub> t<sub>DICL</sub>

Chip select access time = (2 + WS) t<sub>cyc</sub> t<sub>LSA</sub> t<sub>DICL</sub>

Where: WS = number of wait states. When fast termination is used (2 clock bus) WS = -1.

- 6. Specification 9A is the worst-case skew between  $\overline{AS}$  and  $\overline{DS}$  or  $\overline{CS}$ . The amount of skew depends on the relative loading of these signals. When loads are kept within specified limits, skew will not cause  $\overline{AS}$  and  $\overline{DS}$  to fall outside the limits shown in specification 9.

- 7. If multiple chip selects are used,  $\overline{CS}$  width negated (specification 15) applies to the time from the negation of a heavily loaded chip select to the assertion of a lightly loaded chip select. The  $\overline{CS}$  width negated specification between multiple chip selects does not apply to chip selects being used for synchronous ECLK cycles.

- 8. Hold times are specified with respect to  $\overline{DS}$  or  $\overline{CS}$  on asynchronous reads and with respect to CLKOUT on fast cycle reads. The user is free to use either hold time.

- 9. Maximum value is equal to  $(t_{cvc}/2) + 25$  ns.

- 10. If the asynchronous setup time (specification 47A) requirements are satisfied, the DSACK[1:0] low to data setup time (specification 31) and DSACK[1:0] low to BERR low setup time (specification 48) can be ignored. The data must only satisfy the data-in to clock low setup time (specification 27) for the following clock cycle. BERR must satisfy only the late BERR low to clock low setup time (specification 27A) for the following clock cycle.

- 11. To ensure coherency during every operand transfer,  $\overline{BG}$  will not be asserted in response to  $\overline{BR}$  until after all cycles of the current operand transfer are complete and  $\overline{RMC}$  is negated.

- 12. In the absence of DSACK[1:0], BERR is an asynchronous input using the asynchronous setup time (specification 47A).

- 13. After external RESET negation is detected, a short transition period (approximately 2 t<sub>cyc</sub>) elapses, then the SIM drives RESET low for 512 t<sub>cyc</sub>.

- 14. External assertion of the RESET input can overlap internally-generated resets. To insure that an external reset is recognized in all cases, RESET must be asserted for at least 590 CLKOUT cycles.

- 15. External logic must pull RESET high during this period in order for normal MCU operation to begin.

### S — Supervisor/User State

0 = CPU operates at user privilege level

1 = CPU operates at supervisor privilege level

## IP[2:0] — Interrupt Priority Mask

The priority value in this field (0 to 7) is used to mask interrupts.

### X — Extend Flag

Used in multiple-precision arithmetic operations. In many instructions, it is set to the same value as the C bit.

### N — Negative Flag

Set when the MSB of a result register is set.

### Z — Zero Flag

Set when all bits of a result register are zero.

### V — Overflow Flag

Set when two's complement overflow occurs as the result of an operation.

### C — Carry Flag

Set when a carry or borrow occurs during an arithmetic operation. Also used during shift and rotate instructions to facilitate multiple word operations.

This field only affects the response of chip-selects and does not affect interrupt recognition by the CPU32.

### AVEC — Autovector Enable

This field selects one of two methods of acquiring an interrupt vector during an interrupt acknowledge cycle. It is not usually used with a chip-select pin.

- 0 = External interrupt vector enabled

- 1 = Autovector enabled

If the chip select is configured to trigger on an interrupt acknowledge cycle (SPACE[1:0] = %00) and the  $\overline{\text{AVEC}}$  field is set to one, the chip-select automatically generates  $\overline{\text{AVEC}}$  in response to the interrupt acknowledge cycle. Otherwise, the vector must be supplied by the requesting device.

## **D.2.22 Master Shift Registers**

**TSTMSRA** — Master Shift Register A **\$YFFA30**Used for factory test only.

# D.2.23 Test Module Shift Count Register

**TSTSC** — Test Module Shift Count

Used for factory test only.

\$YFFA34

# **D.2.24 Test Module Repetition Count Register**

**TSTRC** — Test Module Repetition Count

Used for factory test only.

\$YFFA36

# **D.2.25 Test Submodule Control Register**

**CREG** — Test Submodule Control Register

Used for factory test only.

\$YFFA38

# **D.2.26 Distributed Register**

DREG — Distributed Register \$YFFA3A Used for factory test only.

# SCBR[12:0] — SCI Baud Rate

SCI baud rate is programmed by writing a 13-bit value to this field. Writing a value of zero to SCBR disables the baud rate generator. Baud clock rate is calculated as follows:

SCI Baud Rate =

$$\frac{f_{sys}}{32 \times SCBR[12:0]}$$

or

$$SCBR[12:0] = \frac{f_{sys}}{32 \times SCI \text{ Baud Rate Desired}}$$

where SCBR[12:0] is in the range of 1 to 8191.

## D.6.6 SCI Control Register 1

## **SCCR1** — SCI Control Register 1

**\$YFFC0A**

|   | 15     | 14    | 13   | 12  | 11 | 10 | 9 | 8    | 7   | 6    | 5   | 4    | 3  | 2  | 1   | 0   |

|---|--------|-------|------|-----|----|----|---|------|-----|------|-----|------|----|----|-----|-----|

|   | 0      | LOOPS | WOMS | ILT | PT | PE | М | WAKE | TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

| _ | RESET: |       |      |     |    |    |   |      |     |      |     |      |    |    |     |     |

|   | 0      | 0     | 0    | 0   | 0  | 0  | 0 | 0    | 0   | 0    | 0   | 0    | 0  | 0  | 0   | 0   |

SCCR1 contains SCI configuration parameters, including transmitter and receiver enable bits, interrupt enable bits, and operating mode enable bits. SCCR0 can be read or written at any time. The SCI can modify the RWU bit under certain circumstances. Changing the value of SCCR1 bits during a transfer operation can disrupt the transfer.

Bit 15 — Not Implemented

LOOPS — Loop Mode

0 = Normal SCI operation, no looping, feedback path disabled.

1 = Test SCI operation, looping, feedback path enabled.

WOMS — Wired-OR Mode for SCI Pins

0 = If configured as an output, TXD is a normal CMOS output.

1 = If configured as an output, TXD is an open-drain output.

ILT — Idle-Line Detect Type

0 = Short idle-line detect (start count on first one).

1 = Long idle-line detect (start count on first one after stop bit(s)).

PT — Parity Type

0 = Even parity

1 = Odd parity

PE — Parity Enable

0 = SCI parity disabled.

1 = SCI parity enabled.

| Q3IVI 9-3, D-41                             | <b>-I-</b>                                  |

|---------------------------------------------|---------------------------------------------|

| SIM 5-3                                     |                                             |

| TouCAN D-85                                 | I/O port operation 8-8                      |

| TPU D-75                                    |                                             |

| bus monitor (FRZBM) 5-3, D-7                | IARB                                        |

| software enable (FRZSW) 5-3, D-7            | BIUSM D-58                                  |

|                                             | QADC 8-8, D-29                              |

| Frequency                                   | QSM D-41                                    |

| control                                     | SIM 5-2, 5-3, 5-52, D-7                     |

| counter (Y) D-8                             | TouCAN D-88                                 |

| prescaler (X) D-8                           | TPU 11-5, D-75                              |

| VCO (W) D-8                                 |                                             |

| measurement (FQM) 11-13                     | IARB3 D-60, D-61, D-64, D-69                |

|                                             | IC D-67, D-68                               |

| FRZ 8-7, 13-11, D-29, D-41, D-75, D-85      | ICD16/ICD32 C-1                             |

| FRZACK 13-11, D-87                          | ID                                          |

| FRZBM 5-3, D-7                              | Extended (IDE) field 13-5                   |

| FRZSW 5-3, D-7                              | HIGH field 13-5                             |

| f <sub>svs</sub> 8-25, 10-16, D-8           |                                             |

| F-term encoding 5-30                        | LOW field 13-5                              |

| FULL 13-4                                   | I <sub>DD</sub> 5-46                        |

|                                             | IDE 13-5                                    |

| Function                                    | Identifier (ID) 13-1                        |

| code (FC) signals 5-22, 5-30                | bit field 13-6                              |

| library for TPU 11-5                        | IDLE 9-28, D-45, D-95                       |

|                                             |                                             |

| -G-                                         | Idle                                        |

| -9-                                         | CAN status (IDLE) D-95                      |

|                                             | frame 9-25                                  |

| Global registers 8-2                        | -line                                       |

| · ·                                         | detect type (ILT) D-43                      |

| ш                                           | detected (IDLE) 9-28, D-45                  |

| -H-                                         | detection process 9-28                      |

|                                             | ·                                           |

| Hall effect decode (HALLD) 11-13            | interrupt enable (ILIE) 9-29, D-44          |

| HALLD 11-13                                 | type (ILT) bit 9-29                         |

| HALT 13-11, D-52, D-86                      | IFLAG D-96                                  |

|                                             | IL D-60, D-61, D-64, D-69                   |

| HALT 5-15, 5-23, 5-27, 5-37                 | ILIE 9-29, D-44                             |

| assertion results 5-35                      | ILQSPI D-42                                 |

| Halt                                        | ILSCI D-42                                  |

| acknowledge flag (HALTA) D-53               |                                             |

| monitor                                     | ILT 9-29, D-43                              |

| enable (HME) 5-15, D-13                     | IMASK D-96                                  |

|                                             | IMB 8-1, 10-1                               |

| reset (HLT) D-9                             | IN D-60, D-64                               |

| operation 5-37                              | IN1 D-62                                    |

| negating/reasserting 5-37                   | IN2 D-62                                    |

| QSPI (HALT) D-52                            | In-circuit debugger (ICD16/ICD32) C-1       |

| TouCAN S-clock (HALT) D-86                  |                                             |

| HALTA D-53                                  | Information processing time (IPT) 13-9      |

| HALTA/MODF interrupt enable (HMIE) bit D-52 | Initial sample time 8-13                    |

| Handshaking 5-26                            | Input                                       |

| •                                           | capture/input transition counter (ITC) 11-6 |

| Hang on T4 (HOT4) D-75                      | pin status (IN)                             |

| Hardware breakpoints 5-31                   | DASM D-64                                   |

| HLT D-9                                     | sample time (IST) 8-26, D-37                |

| HME 5-15, D-13                              |                                             |

| HMIE D-52                                   | Interchannel communication 11-4             |

| Host                                        | Intermission 13-16                          |

| sequence registers 11-16                    | Intermodule bus (IMB) 3-3, 8-1, 10-1        |

| . •                                         | Internal                                    |

| service registers 11-17                     | bus                                         |

| HOT4 D-75                                   | error (BERR) 5-14, 5-15                     |

| HSQR D-78                                   | monitor 5-14                                |

| HSSR D-79                                   | clock signals (PCLK) D-62                   |

| Hysteresis 5-51                             | <b>3</b>                                    |

| •                                           | register map 3-13                           |

|                                             | Interrupt                                   |

MOTOROLA MC68336/376 I-6 USER'S MANUAL

| end queue pointer (ENDQP) 9-8             | data                                                     |

|-------------------------------------------|----------------------------------------------------------|

| new queue pointer (NEWQP) 9-8             | (RXD) pin 9-24                                           |

| status (QS) D-36                          | register full (RDRF) D-45                                |

| Queue 1                                   | error status flag (RXWARN) D-95                          |

| completion                                | pin configuration control (RXMODE) D-89                  |

| flag (CF1) D-35                           | RAM 9-7                                                  |

| interrupt enable (CIE1) D-32              | time sample clock (RT) 9-26, 9-28                        |

| interrupt level (IRLQ1) D-29              | Receiver                                                 |

| operating mode (MQ1) D-32                 | active (RAF) D-45                                        |

| pause                                     | data register (RDRF) flag 9-28                           |

| flag (PF1) D-35                           | enable (RE) 9-28, D-44                                   |

| interrupt enable (PIE1) D-32              | interrupt enable (RIE) D-44                              |

| single-scan enable (SSE1) D-32            | wakeup (RWU) 9-29, D-44                                  |

| trigger overrun (TOR1) D-35               | Reception of transmitted frames 13-13                    |

| Queue 2                                   | Remote                                                   |

| completion                                | frames 13-15                                             |

| flag (CF2) D-35                           | transmission request (RTR) 13-4, 13-5                    |

| interrupt enable (CIE2) D-33              | RES 8-31, D-34                                           |

| interrupt level (IRLQ2) D-29              | Reserved                                                 |

| operating mode (MQ2) D-33                 | channel number D-37                                      |

| pause                                     | mode 8-20                                                |

| flag (PF2) D-35                           | RESET 4-19, 5-40, 5-42, 5-46, 5-47                       |

| interrupt enable (PIE2) D-33              | Reset                                                    |

| resume (RES) D-34                         | control logic in SIM 5-40                                |

| single-scan enable bit (SSE2) D-33        | exception processing 5-40                                |

| trigger overrun (TOR2) D-36               | mode selection                                           |

| Queued                                    | timing diagram A-18                                      |

| analog-to-digital converter. See QADC 8-1 | use in determining SIM configuration 5-41                |

| output match (QOM) 11-11                  | module pin function out of reset 5-45                    |

| serial                                    | operation in SIM 5-40                                    |

| module (QSM). See QSM 9-1                 | power-on 5-48                                            |

| peripheral interface (QSPI) 9-1, 9-5      | processing summary 5-50                                  |

|                                           | source summary in SIM 5-41                               |

| -R-                                       | states of pins assigned to other MCU modules 5-47        |

|                                           | status register (RSR) 5-14, 5-50, D-9                    |

| R/W 5-22, 5-27                            | timing 5-47                                              |

| field 5-59, D-19                          | Resistor-divider chain 8-15                              |

| RAF D-45                                  | Resolution time 8-13                                     |

| RAM                                       | Result word table 8-1, 8-16, 8-31                        |

| array                                     | Resynchronization jump width (RJW) bit field D-91        |

| disable (RAMDS) D-83                      | Retry operation 5-37                                     |

| space (RASP) D-22                         | RIE D-44                                                 |

| base address lock (RLCK) bit D-22         | Right justified, unsigned result word table (RJURR) D-39 |

| RAMBAH 6-1, D-23                          | RJURR D-39                                               |

| RAMBAL 6-1, D-23                          | RJW 13-11, D-91                                          |

| RAMDS 12-1, D-83                          | RLCK 6-1, D-22                                           |

| RAMMCR 6-1, D-22                          | RMC 3-7, 3-10, 3-12, 5-38                                |

| RAMTST 6-1, D-23                          | ROM array space (ASPC) D-25                              |

| RASP 6-1, D-22, D-82                      | ROMBAH 7-1, D-26                                         |

| encoding D-22                             | ROMBAL 7-1, D-26                                         |

| RDR 9-24                                  | ROMBS 7-1                                                |

| RDRF 9-28, D-45                           | ROMBS0-3 D-27                                            |

| RE 9-28, D-44                             | RPC 4-22                                                 |

| Read                                      | RR D-53                                                  |

| /write signal (R/W) 5-22                  | RS-232C terminal C-2                                     |

| cycle 5-28                                | RSIGHI 7-1, 7-3, D-26                                    |

| flowchart 5-28                            | RSIGLO 7-1, 7-3, D-26                                    |

| timing diagram A-11                       | RSR 5-14, D-9                                            |

| system register command (RSREG) 4-20      | RSREG 4-20                                               |

| Receive                                   | RT 9-28                                                  |

MOTOROLA MC68336/376

I-12 USER'S MANUAL