#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | CPU32                                                                 |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                             |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 18                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 7.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                         |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 160-BQFP                                                              |

| Supplier Device Package    | 160-QFP (28x28)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68336gcab25 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS (Continued) Title

# Paragraph

Page

| 10.1     | General10                                     | -1 |

|----------|-----------------------------------------------|----|

| 10.2     | Address Map10                                 | -2 |

| 10.3     | Time Base Bus System10                        |    |

| 10.4     | Bus Interface Unit Submodule (BIUSM)10        | -3 |

| 10.4.1   | STOP Effect On the BIUSM                      |    |

| 10.4.2   | Freeze Effect On the BIUSM10                  |    |

| 10.4.3   | LPSTOP Effect on the BIUSM10                  |    |

| 10.4.4   | BIUSM Registers10                             | -4 |

| 10.5     | Counter Prescaler Submodule (CPSM)10          | -4 |

| 10.5.1   | CPSM Registers10                              | -5 |

| 10.6     | Free-Running Counter Submodule (FCSM)10       |    |

| 10.6.1   | FCSM Counter10                                | -6 |

| 10.6.2   | FCSM Clock Sources10                          |    |

| 10.6.3   | FCSM External Event Counting10                | -6 |

| 10.6.4   | FCSM Time Base Bus Driver                     | -6 |

| 10.6.5   | FCSM Interrupts10                             |    |

| 10.6.6   | FCSM Registers10                              |    |

| 10.7     | Modulus Counter Submodule (MCSM)10            | -7 |

| 10.7.1   | MCSM Modulus Latch                            | -8 |

| 10.7.2   | MCSM Counter10                                | -8 |

| 10.7.2.1 | Loading the MCSM Counter Register             | -8 |

| 10.7.2.2 | Using the MCSM as a Free-Running Counter      | -9 |

| 10.7.3   | MCSM Clock Sources10                          | -9 |

| 10.7.4   | MCSM External Event Counting10                | -9 |

| 10.7.5   | MCSM Time Base Bus Driver                     |    |

| 10.7.6   | MCSM Interrupts10                             | -9 |

| 10.7.7   | MCSM Registers10-7                            | 10 |

| 10.8     | Double-Action Submodule (DASM)                | 10 |

| 10.8.1   | DASM Interrupts10-7                           | 12 |

| 10.8.2   | DASM Registers10-7                            |    |

| 10.9     | Pulse-Width Modulation Submodule (PWMSM) 10-7 |    |

| 10.9.1   | Output Flip-Flop and Pin                      | 13 |

| 10.9.2   | Clock Selection10-                            | 13 |

| 10.9.3   | PWMSM Counter10-                              |    |

| 10.9.4   | PWMSM Period Registers and Comparator10-7     |    |

| 10.9.5   | PWMSM Pulse-Width Registers and Comparator    |    |

| 10.9.6   | PWMSM Coherency10-7                           |    |

| 10.9.7   | PWMSM Interrupts10-                           |    |

| 10.9.8   | PWM Frequency10-                              |    |

| 10.9.9   | PWM Pulse Width10-                            |    |

| 10.9.10  | PWM Period and Pulse Width Register Values    | 17 |

# LIST OF ILLUSTRATIONS

# Figure

# Title

| 3-1  | MC68336/376 Block Diagram                               |      |

|------|---------------------------------------------------------|------|

| 3-2  | MC68336 Pin Assignments for 160-Pin Package             |      |

| 3-3  | MC68376 Pin Assignments for 160-Pin Package             |      |

| 3-4  | MC68336/376 Address Map                                 |      |

| 3-5  | Overall Memory Map                                      |      |

| 3-6  | Separate Supervisor and User Space Map                  | 3-16 |

| 3-7  | Supervisor Space (Separate Program/Data Space) Map      | 3-17 |

| 3-8  | User Space (Separate Program/Data Space) Map            |      |

| 4-1  | CPU32 Block Diagram                                     |      |

| 4-2  | User Programming Model                                  | 4-3  |

| 4-3  | Supervisor Programming Model Supplement                 | 4-4  |

| 4-4  | Data Organization in Data Registers                     | 4-5  |

| 4-5  | Address Organization in Address Registers               | 4-6  |

| 4-6  | Memory Operand Addressing                               | 4-8  |

| 4-7  | Loop Mode Instruction Sequence                          | 4-15 |

| 4-8  | Common In-Circuit Emulator Diagram                      | 4-19 |

| 4-9  | Bus State Analyzer Configuration                        | 4-19 |

| 4-10 | Debug Serial I/O Block Diagram                          |      |

| 4-11 | BDM Serial Data Word                                    |      |

| 4-12 | BDM Connector Pinout                                    |      |

| 5-1  | System Integration Module Block Diagram                 | 5-2  |

| 5-2  | System Clock Block Diagram                              |      |

| 5-3  | System Clock Oscillator Circuit                         |      |

| 5-4  | System Clock Filter Networks                            |      |

| 5-5  | LPSTOP Flowchart                                        | 5-13 |

| 5-6  | System Protection Block                                 |      |

| 5-7  | Periodic Interrupt Timer and Software Watchdog Timer    |      |

| 5-8  | MCU Basic System                                        |      |

| 5-9  | Operand Byte Order                                      |      |

| 5-10 | Word Read Cycle Flowchart                               |      |

| 5-11 | Write Cycle Flowchart                                   |      |

| 5-12 | CPU Space Address Encoding                              |      |

| 5-13 | Breakpoint Operation Flowchart                          |      |

| 5-14 | LPSTOP Interrupt Mask Level                             |      |

| 5-15 | Bus Arbitration Flowchart for Single Request            |      |

| 5-16 | Preferred Circuit for Data Bus Mode Select Conditioning | 5-43 |

| 5-17 | Alternate Circuit for Data Bus Mode Select Conditioning |      |

| 5-18 | Power-On Reset                                          |      |

| 5-19 | Basic MCU System                                        |      |

| 5-20 | Chip-Select Circuit Block Diagram                       |      |

| 5-21 | CPU Space Encoding for Interrupt Acknowledge            | 5-61 |

MOTOROLA

# 5.10 Parallel Input/Output Ports

Sixteen SIM pins can be configured for general-purpose discrete input and output. Although these pins are organized into two ports, port E and port F, function assignment is by individual pin. Pin assignment registers, data direction registers, and data registers are used to implement discrete I/O.

## 5.10.1 Pin Assignment Registers

Bits in the port E and port F pin assignment registers (PEPAR and PFPAR) control the functions of the pins on each port. Any bit set to one defines the corresponding pin as a bus control signal. Any bit cleared to zero defines the corresponding pin as an I/O pin.

## 5.10.2 Data Direction Registers

Bits in the port E and port F data direction registers (DDRE and DDRF) control the direction of the pin drivers when the pins are configured as I/O. Any bit in a register set to one configures the corresponding pin as an output. Any bit in a register cleared to zero configures the corresponding pin as an input. These registers can be read or written at any time.

## 5.10.3 Data Registers

A write to the port E and port F data registers (PORTE[0:1] and PORTF[0:1]) is stored in an internal data latch, and if any pin in the corresponding port is configured as an output, the value stored for that bit is driven out on the pin. A read of a data register returns the value at the pin only if the pin is configured as a discrete input. Otherwise, the value read is the value stored in the port data register. Both data registers can be accessed in two locations and can be read or written at any time.

## 5.11 Factory Test

The test submodule supports scan-based testing of the various MCU modules. It is integrated into the SIM to support production test. Test submodule registers are intended for Motorola use only. Register names and addresses are provided in **D.2.2 System Integration Test Register** and **D.2.5 System Integration Test Register (ECLK)** to show the user that these addresses are occupied. The QUOT pin is also used for factory test.

# **SECTION 6 STANDBY RAM MODULE**

The standby RAM (SRAM) module consists of a control register block and a 4-Kbyte array of fast (two bus cycle) static RAM. The SRAM is especially useful for system stacks and variable storage. The SRAM can be mapped to any address that is a multiple of the array size so long as SRAM boundaries do not overlap the module control registers (overlap makes the registers inaccessible). Data can be read/written in bytes, words or long words. SRAM is powered by V<sub>DD</sub> in normal operation. During power-down, SRAM contents can be maintained by power from the V<sub>STBY</sub> input. Power switching between sources is automatic.

# 6.1 SRAM Register Block

There are four SRAM control registers: the RAM module configuration register (RAM-MCR), the RAM test register (RAMTST), and the RAM array base address registers (RAMBAH/RAMBAL). To protect these registers from accidental modification, they are always mapped to supervisor data space.

The module mapping bit (MM) in the SIM configuration register defines the most significant bit (ADDR23) of the IMB address for each MC68336/376 module. Refer to **5.2.1 Module Mapping** for information on how the state of MM affects the system.

The SRAM control register consists of eight bytes, but not all locations are implemented. Unimplemented register addresses are read as zeros, and writes have no effect. Refer to **D.3 Standby RAM Module** for register block address map and register bit/field definitions.

# 6.2 SRAM Array Address Mapping

Base address registers RAMBAH and RAMBAL are used to specify the SRAM array base address in the memory map. RAMBAH and RAMBAL can only be written while the SRAM is in low-power stop mode (RAMMCR STOP = 1) and the base address lock (RAMMCR RLCK = 0) is disabled. RLCK can be written once only to a value of one. This prevents accidental remapping of the array.

# 6.3 SRAM Array Address Space Type

RASP[1:0] in RAMMCR determine the SRAM array address space type. The SRAM module can respond to both program and data space accesses or to program space accesses only. This allows code to be executed from RAM, and permits use of program counter relative addressing mode for operand fetches from the array.

In addition, RASP[1:0] specify whether access to the SRAM module can be made in supervisor mode only, or in either user or supervisor mode. If supervisor-only access is specified, accesses in user mode are ignored by the SRAM control logic and can be decoded externally.

6. Calculate the QCLK frequency ( $f_{QCLK}$ ).

$$\frac{(f_{QCLK} \text{ (in MHz)} = 1000)}{QCLK \text{ high time (in ns)} + QCLK \text{ low time (in ns)}}$$

- 7. Choose the number of input sample cycles (2, 4, 8, or 16) for a typical input channel.

- 8. If the calculated conversion times are not sufficient, return to step 3. Conversion time is determined by the following equation:

$Conversion \ time \ (in \ \mu s \ ) \ = \ \frac{16 + Number \ of \ input \ sample \ cycles}{f_{QCLK}(in \ MHz)}$

9. Code the selected PSH, PSL, and PSA values into the prescaler fields of QACR0.

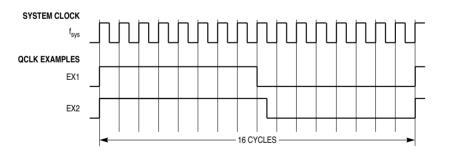

**Figure 8-9** and **Table 8-4** show examples of QCLK programmability. The examples include conversion times based on the following assumptions:

- f<sub>svs</sub> = 20.97 MHz.

- Input sample time is as fast as possible (IST[1:0] = %00, 2 QCLK cycles).

**Figure 8-9** and **Table 8-4** also show the conversion time calculated for a single conversion in a queue. For other MCU system clock frequencies and other input sample times, the same calculations can be made.

QADC QCLK EX

Figure 8-9 QADC Clock Programmability Examples

- If both STOP and SELFWAKE are set and a recessive to dominant edge immediately occurs on the CAN bus, the TouCAN may never set the STOPACK bit, and the STOP bit will be cleared.

- To prevent old frames from being sent when the TouCAN awakes from low-power stop mode via the self-wake mechanism, disable all transmit sources, including transmit buffers configured for remote request responses, before placing the TouCAN in low-power stop mode.

- If the TouCAN is in debug mode when the STOP bit is set, the TouCAN will assume that debug mode should be exited. As a result, it will try to synchronize with the CAN bus, and only then will it await the conditions required for entry into low-power stop mode.

- Unlike other modules, the TouCAN does not come out of reset in low-power stop mode. The basic TouCAN initialization procedure (see **13.5.2 TouCAN Initialization**) should be executed before placing the module in low-power stop mode.

- If the TouCAN is in low-power stop mode with the self-wake mechanism engaged and is operating with a single system clock per time quantum, there can be extreme cases in which TouCAN wake-up on recessive to dominant edge may not conform to the CAN protocol. TouCAN synchronization will be shifted one time quantum from the wake-up event. This shift lasts until the next recessive to dominant edge, which resynchronizes the TouCAN to be in conformance with the CAN protocol. The same holds true when the TouCAN is in auto power save mode and awakens on a recessive to dominant edge.

# 13.6.3 Auto Power Save Mode

Auto power save mode enables normal operation with optimized power savings. Once the auto power save (APS) bit in CANMCR is set, the TouCAN looks for a set of conditions in which there is no need for the clocks to be running. If these conditions are met, the TouCAN stops its clocks, thus saving power. The following conditions will activate auto power save mode.

- No RX/TX frame in progress.

- No transfer of RX/TX frames to and from a serial message buffer, and no TX frame awaiting transmission in any message buffer.

- No CPU32 access to the TouCAN module.

- The TouCAN is not in debug mode, low-power stop mode, or the bus off state.

While its clocks are stopped, if the TouCAN senses that any one of the aforementioned conditions is no longer true, it restarts its clocks. The TouCAN then continues to monitor these conditions and stops/restarts its clocks accordingly.

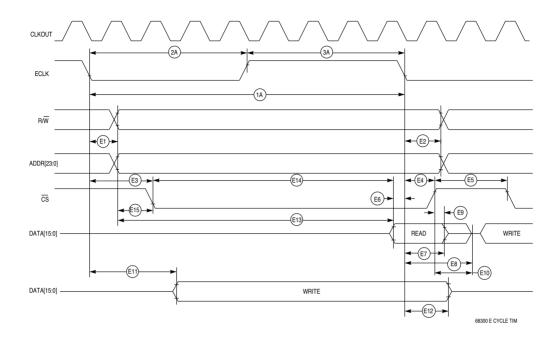

Figure A-15 ECLK Timing Diagram

# **D.2.3 Clock Synthesizer Control Register**

| SYNC | SYNCR — Clock Synthesizer Control Register |    |    |    |      |   |   |      |   |   |                   |       | \$YFF             | A04   |       |

|------|--------------------------------------------|----|----|----|------|---|---|------|---|---|-------------------|-------|-------------------|-------|-------|

| 15   | 14                                         | 13 | 12 | 11 | 10   | 9 | 8 | 7    | 6 | 5 | 4                 | 3     | 2                 | 1     | 0     |

| W    | Х                                          |    |    | Y[ | 5:0] |   |   | EDIV | 0 | 0 | RSVD <sup>1</sup> | SLOCK | RSVD <sup>1</sup> | STSIM | STEXT |

| RES  | SET:                                       |    |    |    |      |   |   |      |   |   |                   |       |                   |       |       |

| 0    | 0                                          | 1  | 1  | 1  | 1    | 1 | 1 | 0    | 0 | 0 | 0                 | U     | 0                 | 0     | 0     |

NOTES:

1. Ensure that initialization software does not change the value of these bits. They should always be zero.

SYNCR determines system clock operating frequency and operation during low-power stop mode. Clock frequency is determined by SYNCR bit settings as follows:

$$f_{sys} = \frac{f_{ref}}{128} [4(Y+1)(2^{(2W+X)})]$$

W — Frequency Control (VCO)

This bit controls a prescaler tap in the synthesizer feedback loop. Setting this bit increases the VCO speed by a factor of four. VCO relock delay is required.

X — Frequency Control (Prescaler)

This bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting the bit doubles clock speed without changing the VCO speed. No VCO relock delay is required.

Y[5:0] — Frequency Control (Counter)

The Y field controls the modulus down counter in the synthesizer feedback loop, causing it to divide by a value of Y + 1. VCO relock delay is required.

EDIV — E Clock Divide Rate

0 = ECLK frequency is system clock divided by 8.

1 = ECLK frequency is system clock divided by 16.

ECLK is an external M6800 bus clock available on ADDR23.

SLOCK — Synthesizer Lock Flag

0 = VCO is enabled, but has not locked.

1 = VCO has locked on the desired frequency or VCO is disabled.

The MCU remains in reset until the synthesizer locks, but SLOCK does not indicate synthesizer lock status until after the user writes to SYNCR.

- STSIM Stop Mode SIM Clock

- 0 = When LPSTOP is executed, the SIM clock is driven from the crystal oscillator and the VCO is turned off to conserve power.

- 1 = When LPSTOP is executed, the SIM clock is driven from the VCO.

## **D.4.6 ROM Bootstrap Words**

| ROMBS0 — ROM Bootstrap Word 0 | \$YFF830 |

|-------------------------------|----------|

| ROMBS1 — ROM Bootstrap Word 1 | \$YFF832 |

| ROMBS2 — ROM Bootstrap Word 2 | \$YFF834 |

#### **ROMBS3** — ROM Bootstrap Word 3

Typically, CPU32 reset vectors reside in non-volatile memory and are only fetched when the CPU32 comes out of reset. These four words can be used as reset vectors with the contents specified at mask time. The content of these words cannot be changed. On generic (blank ROM) MC68376 devices, ROMBS[0:3] are masked to 0000. When the ROM on the MC68376 is masked with customer specific code, ROMBS[0:3] respond to system addresses 00000 to 00000 only during the reset vector fetch if  $\overline{BOOT} = 0$ .

**\$YFF836**

# D.5 QADC Module

**Table D-24** shows the QADC address map. The column labeled "Access" indicates the privilege level at which the CPU32 must be operating to access the register. A designation of "S" indicates that supervisor mode is required. A designation of "S/U" indicates that the register can be programmed for either supervisor mode access or unrestricted access.

| Access | Address <sup>1</sup> | 15 8                                                                | 7 0                                                                   |  |  |  |  |  |  |

|--------|----------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| S      | \$YFF200             | Module Configuration Register (QADCMCR)                             |                                                                       |  |  |  |  |  |  |

| S      | \$YFF202             | Test Register                                                       | (QADCTEST)                                                            |  |  |  |  |  |  |

| S      | \$YFF204             | Interrupt Regis                                                     | iter (QADCINT)                                                        |  |  |  |  |  |  |

| S/U    | \$YFF206             | Port A Data (PORTQA)                                                | Port B Data (PORTQB)                                                  |  |  |  |  |  |  |

| S/U    | \$YFF208             | Port Data Direction                                                 | Register (DDRQA)                                                      |  |  |  |  |  |  |

| S/U    | \$YFF20A             | Control Regis                                                       | ter 0 (QACR0)                                                         |  |  |  |  |  |  |

| S/U    | \$YFF20C             | Control Regis                                                       | ter 1 (QACR1)                                                         |  |  |  |  |  |  |

| S/U    | \$YFF20E             | Control Register 2 (QACR2)                                          |                                                                       |  |  |  |  |  |  |

| S/U    | \$YFF210             | Status Register (QASR)                                              |                                                                       |  |  |  |  |  |  |

| —      | \$YFF212 – \$YFF22E  | Reserved                                                            |                                                                       |  |  |  |  |  |  |

| S/U    | \$YFF230 – \$YFF27E  | Conversion Comman                                                   | nd Word (CCW) Table                                                   |  |  |  |  |  |  |

| —      | \$YFF280 – \$YFF2AE  | Rese                                                                | erved                                                                 |  |  |  |  |  |  |

| S/U    | \$YFF2B0 – \$YFF2FE  |                                                                     | 'ord Table<br>Result Register (RJURR)                                 |  |  |  |  |  |  |

| —      | \$YFF300 - \$YFF32E  | Rese                                                                | erved                                                                 |  |  |  |  |  |  |

| S/U    | \$YFF330 – \$YFF37E  | Result Word Table<br>Left Justified, Signed Result Register (LJSRR) |                                                                       |  |  |  |  |  |  |

| —      | \$YFF380 – \$YFF3AE  | Rese                                                                | erved                                                                 |  |  |  |  |  |  |

| S/U    | \$YFF3B0 – \$YFF3FE  |                                                                     | Result Word Table<br>Left Justified, Unsigned Result Register (LJURR) |  |  |  |  |  |  |

#### Table D-24 QADC Address Map

NOTES:

1. Y = M111, where M is the logic state of the module mapping (MM) bit in SIMCR.

# **D.5.1 QADC Module Configuration Register**

#### **QADCMCR** — Module Configuration Register

#### \$YFF200

| 15     | 14  | 13 | 12 | 11  | 10   | 9 | 8 | 7    | 6 | 5        | 4 | 3 | 2    | 1      | 0 |

|--------|-----|----|----|-----|------|---|---|------|---|----------|---|---|------|--------|---|

| STOP   | FRZ |    |    | NOT | USED |   |   | SUPV | 1 | NOT USED | ) |   | IARE | 8[3:0] |   |

| RESET: |     |    |    |     |      |   |   |      |   |          |   |   |      |        |   |

| 0      | 0   |    |    |     |      |   |   | 1    |   |          |   | 0 | 0    | 0      | 0 |

STOP — Low-Power Stop Mode Enable

When the STOP bit is set, the clock signal to the QADC is disabled, effectively turning off the analog circuitry.

0 = Enable QADC clock.

1 = Disable QADC clock.

| QACR1 — Control Register 1 |      |      |     |      |    |          |   |   |   |   |      | \$YFF | 20C |   |   |

|----------------------------|------|------|-----|------|----|----------|---|---|---|---|------|-------|-----|---|---|

| 15                         | 14   | 13   | 12  | 11   | 10 | 9        | 8 | 7 | 6 | 5 | 4    | 3     | 2   | 1 | 0 |

| CIE1                       | PIE1 | SSE1 | NOT | USED |    | MQ1[2:0] |   |   |   |   | RESE | RVED  |     |   |   |

| RESET:                     |      |      |     |      |    |          |   |   |   |   |      |       |     |   |   |

| 0                          | 0    | 0    |     |      | 0  | 0        | 0 |   |   |   |      |       |     |   |   |

CIE1 — Queue 1 Completion Interrupt Enable

CIE1 enables completion interrupts for queue 1. The interrupt request is generated when the conversion is complete for the last CCW in queue 1.

- 0 =Queue 1 completion interrupts disabled.

- 1 = Generate an interrupt request after completing the last CCW in queue 1.

- PIE1 Queue 1 Pause Interrupt Enable

PIE1 enables pause interrupts for queue 1. The interrupt request is generated when the conversion is complete for a CCW that has the pause bit set.

- 0 = Queue 1 pause interrupts disabled.

- 1 = Generate an interrupt request after completing a CCW in queue 1 which has the pause bit set.

#### SSE1 — Queue 1 Single-Scan Enable

SSE1 enables a single-scan of queue 1 after a trigger event occurs. The SSE1 bit may be set to a one during the same write cycle that sets the MQ1[2:0] bits for the single-scan queue operating mode. The single-scan enable bit can be written as a one or a zero, but is always read as a zero.

The SSE1 bit allows a trigger event to initiate queue execution for any single-scan operation on queue 1. The QADC clears SSE1 when the single-scan is complete.

#### MQ1[2:0] — Queue 1 Operating Mode

The MQ1 field selects the queue operating mode for queue 1. **Table D-25** shows the different queue 1 operating modes.

| MQ1[2:0] | Queue 1 Operating Mode                                             |

|----------|--------------------------------------------------------------------|

| 000      | Disabled mode, conversions do not occur                            |

| 001      | Software triggered single-scan mode (started with SSE1)            |

| 010      | External trigger rising edge single-scan mode (on ETRIG1 pin)      |

| 011      | External trigger falling edge single-scan mode (on ETRIG1 pin)     |

| 100      | Reserved mode, conversions do not occur                            |

| 101      | Software triggered continuous-scan mode (started with SSE1)        |

| 110      | External trigger rising edge continuous-scan mode (on ETRIG1 pin)  |

| 111      | External trigger falling edge continuous-scan mode (on ETRIG1 pin) |

#### Table D-25 Queue 1 Operating Modes

# Table D-44 DASM Mode Flag Status Bit States

| Mode | Flag Status Bit State                                                                |

|------|--------------------------------------------------------------------------------------|

| DIS  | FLAG bit is reset                                                                    |

| IPWM | FLAG bit is set each time there is a capture on channel A                            |

| IPM  | FLAG bit is set each time there is a capture on channel A, except for the first time |

| IC   | FLAG bit is set each time there is a capture on channel A                            |

| OCB  | FLAG bit is set each time there is a successful comparison on channel B              |

| OCAB | FLAG bit is set each time there is a successful comparison on either channel A or B  |

| OPWM | FLAG bit is set each time there is a successful comparison on channel A              |

The FLAG bit is set by hardware and cleared by software, or by system reset. Clear the FLAG bit either by writing a zero to it, having first read the bit as a one, or by selecting the DIS mode.

# IL[2:0] — Interrupt Level

When the DASM generates an interrupt request, IL[2:0] determines which of the interrupt request signals is asserted. When a request is acknowledged, the CTM4 compares IL[2:0] to a mask value supplied by the CPU32 to determine whether to respond. IL[2:0] must have a value in the range of \$0 (interrupts disabled) to \$7 (highest priority).

# IARB3 — Interrupt Arbitration Bit 3

This bit and the IARB[2:0] field in BIUMCR are concatenated to determine the interrupt arbitration number for the submodule requesting interrupt service. Refer to **D.7.1 BIU Module Configuration Register** for more information on IARB[2:0].

## WOR — Wired-OR Mode

In the DIS, IPWM, IPM and IC modes, the WOR bit is not used. Reading this bit returns the value that was previously written.

In the OCB, OCAB and OPWM modes, the WOR bit selects whether the output buffer is configured for open-drain or normal operation.

0 = Output buffer operates in normal mode.

1 = Output buffer operates in open-drain mode.

## BSL — Bus Select

This bit selects the time base bus connected to the DASM.

- 0 = DASM is connected to time base bus A.

- 1 = DASM is connected to time base bus B.

## IN — Input Pin Status

In the DIS, IPWM, IPM and IC modes, this read-only status bit reflects the logic level on the input pin.

In the OCB, OCAB and OPWM modes, reading this bit returns the value latched on the output flip-flop, after EDPOL polarity selection.

Writing to this bit has no effect.

| POL | EN | Output Pin State | Periodic Edge | Variable Edge | <b>Optional Interrupt On</b> |

|-----|----|------------------|---------------|---------------|------------------------------|

| 0   | 0  | Always low       | —             | —             | —                            |

| 1   | 0  | Always high      | —             | —             | —                            |

| 0   | 1  | High pulse       | Rising edge   | Falling edge  | Rising edge                  |

| 1   | 1  | Low pulse        | Falling edge  | Rising edge   | Falling edge                 |

# Table D-49 PWMSM Output Pin Polarity Selection

## EN — PWMSM Enable

This control bit enables and disables the PWMSM.

- 0 = Disable the PWMSM.

- 1 = Enable the PWMSM.

While the PWMSM is disabled (EN = 0):

- The output flip-flop is held in reset and the level on the output pin is set to one or zero according to the state of the POL bit.

- The PWMSM divide-by-256 prescaler is held in reset.

- The counter stops incrementing and is at \$0001.

- The comparators are disabled.

- The PWMA1 and PWMB1 registers permanently transfer their contents to the buffer registers PWMA2 and PWMB2, respectively.

When the EN bit is changed from zero to one:

- The output flip-flop is set to start the first pulse.

- The PWMSM divide-by-256 prescaler is released.

- The counter is released and starts to increment from \$0001.

- The FLAG bit is set to indicate that PWMA1 and PWMB1 can be updated with new values.

While EN is set, the PWMSM continuously generates a pulse width modulated output signal based on the data in PWMA2 and PWMB2 which are updated via PWMA1 and PWMB2 each time a period is completed.

#### NOTE

To prevent unwanted output waveform glitches when disabling the PWMSM, first write to PWMB1 to generate one period of 0% duty cycle, then clear EN.

CLK[2:0] — Clock Rate Selection

The CLK[2:0] bits select one of the eight counter clock sources coming from the PWMSM prescaler. These bits can be changed at any time. **Table D-50** shows the counter clock sources and rates in detail.

| CLK2 | CLK1 | CLK0 | PCLK1 = $f_{sys} \div 2$<br>(CPCR DIV23 = 0) | PCLK1 = $f_{sys} \div 2$<br>(CPCR DIV23 = 0) |

|------|------|------|----------------------------------------------|----------------------------------------------|

| 0    | 0    | 0    | f <sub>sys</sub> ÷2                          | f <sub>sys</sub> ÷3                          |

| 0    | 0    | 1    | f <sub>sys</sub> ÷4                          | f <sub>sys</sub> ÷ 6                         |

| 0    | 1    | 0    | f <sub>sys</sub> ÷8                          | f <sub>sys</sub> ÷12                         |

| 0    | 1    | 1    | f <sub>sys</sub> ÷16                         | f <sub>sys</sub> ÷24                         |

| 1    | 0    | 0    | f <sub>sys</sub> ÷32                         | f <sub>sys</sub> ÷48                         |

| 1    | 0    | 1    | f <sub>sys</sub> ÷64                         | f <sub>sys</sub> ÷96                         |

| 1    | 1    | 0    | f <sub>sys</sub> ÷128                        | f <sub>sys</sub> ÷ 192                       |

| 1    | 1    | 1    | f <sub>sys</sub> ÷ 512                       | f <sub>sys</sub> ÷ 768                       |

## Table D-50 PWMSM Divide By Options

#### **D.7.15 PWM Period Register**

| PV<br>PV | VM(<br>VM) | 6A1 -<br>7A1 - | — PW<br>— PW<br>— PW<br>— PW | /M6A<br>/M7A | Perio<br>Perio | d Reg<br>d Reg | jister<br>jister |   |   |   |   |   |   |   | \$YFF<br>\$YFF<br>\$YFF<br>\$YFF | 432<br>43A |

|----------|------------|----------------|------------------------------|--------------|----------------|----------------|------------------|---|---|---|---|---|---|---|----------------------------------|------------|

| 1        | 5          | 14             | 13                           | 12           | 11             | 10             | 9                | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1                                | 0          |

|          |            |                |                              |              |                |                |                  |   |   |   |   |   |   |   |                                  |            |

|          | RES        | ET:            |                              |              |                |                |                  |   |   |   |   |   |   |   |                                  |            |

|          |            |                |                              |              |                |                |                  |   |   |   |   |   | U | U |                                  |            |

The PWMA1 register contains the period value for the next cycle of the PWM output waveform. When the PWMSM is enabled, a period value written to PWMA1 is loaded into PWMA2 at the end of the current period or when the LOAD bit in PWMSIC is written to one. If the PWMSM is disabled, a period value written to PWMA1 is loaded into PWMA2 on the next half cycle of the MCU system clock. PWMA2 is a temporary register that is used to smoothly update the PWM period value; it is not user-accessible. The PWMSM hardware does not modify the contents of PWMA1 at any time.

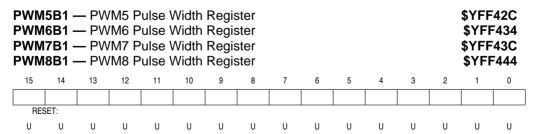

## D.7.16 PWM Pulse Width Register

# Table D-54 FRZ[1:0] Encoding

| FRZ[1:0] | TPU Response                        |

|----------|-------------------------------------|

| 00       | Ignore freeze                       |

| 01       | Reserved                            |

| 10       | Freeze at end of current microcycle |

| 11       | Freeze at next time-slot boundary   |

CCL — Channel Conditions Latch

CCL controls the latching of channel conditions (MRL and TDL) when the CHAN register is written.

- 0 = Only the pin state condition of the new channel is latched as a result of the write CHAN register microinstruction.

- 1 = Pin state, MRL, and TDL conditions of the new channel are latched as a result of a write CHAN register microinstruction.

# BP, BC, BH, BL, BM, and BT — Breakpoint Enable Bits

These bits are TPU breakpoint enables. Setting a bit enables a breakpoint condition. **Table D-55** shows the different breakpoint enable bits.

| Enable Bit | Function                                                                                                                  |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| BP         | Break if µPC equals µPC breakpoint register                                                                               |

| BC         | Break if CHAN register equals channel breakpoint register at beginning of state or when CHAN is changed through microcode |

| BH         | Break if host service latch is asserted at beginning of state                                                             |

| BL         | Break if link service latch is asserted at beginning of state                                                             |

| BM         | Break if MRL is asserted at beginning of state                                                                            |

| BT         | Break if TDL is asserted at beginning of state                                                                            |

# D.8.4 Development Support Status Register

| DSSR — Development Support Status Register\$YF |      |    |    |    |    |   |   |      |      |      |      |      |   |   | E06 |

|------------------------------------------------|------|----|----|----|----|---|---|------|------|------|------|------|---|---|-----|

| 15                                             | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2 | 1 | 0   |

| 0                                              | 0    | 0  | 0  | 0  | 0  | 0 | 0 | BKPT | PCBK | CHBK | SRBK | TPUF | 0 | 0 | 0   |

| RES                                            | SET: |    |    |    |    |   |   |      |      |      |      |      |   |   |     |

| 0                                              | 0    | 0  | 0  | 0  | 0  | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0 | 0 | 0   |

# BKPT — Breakpoint Asserted Flag

If an internal breakpoint caused the TPU to enter the halted state, the TPU asserts the BKPT signal on the IMB and sets the BKPT flag. BKPT remains set until the TPU recognizes a breakpoint acknowledge cycle, or until the IMB FREEZE signal is asserted.

## PCBK — $\mu$ PC Breakpoint Flag

PCBK is asserted if a breakpoint occurs because of a  $\mu$ PC (microprogram counter) register match with the  $\mu$ PC breakpoint register. PCBK is negated when the BKPT flag is cleared.

#### CHBK — Channel Register Breakpoint Flag

CHBK is asserted if a breakpoint occurs because of a CHAN register match with the CHAN register breakpoint register. CHBK is negated when the BKPT flag is cleared.

## SRBK — Service Request Breakpoint Flag

SRBK is asserted if a breakpoint occurs because of any of the service request latches being asserted along with their corresponding enable flag in the development support control register. SRBK is negated when the BKPT flag is cleared.

## TPUF — TPU FREEZE Flag

TPUF is set whenever the TPU is in a halted state as a result of FREEZE being asserted. This flag is automatically negated when the TPU exits the halted state because of FREEZE being negated.

#### D.8.5 TPU Interrupt Configuration Register

| Т | ICR — TPU Interrupt Conf | TPU Interrupt Configuration Register         \$YFFE08           10         9         8         7         6         5         4         3         0           NOT USED         CIRL[2:0]         CIBV[3:0]         NOT USED         NOT USED |           |   |   |      |       |   |  |          |  |  |  |  |  |

|---|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|---|------|-------|---|--|----------|--|--|--|--|--|

|   | 15                       | 10 9 8 7 6 5 4 3                                                                                                                                                                                                                            |           |   |   |      |       |   |  |          |  |  |  |  |  |

|   | NOT USED                 |                                                                                                                                                                                                                                             | CIRL[2:0] |   |   | CIBV | [3:0] |   |  | NOT USED |  |  |  |  |  |

|   | RESET:                   |                                                                                                                                                                                                                                             |           |   |   |      |       |   |  |          |  |  |  |  |  |

|   |                          | 0                                                                                                                                                                                                                                           | 0         | 0 | 0 | 0    | 0     | 0 |  |          |  |  |  |  |  |

#### CIRL[2:0] — Channel Interrupt Request Level

This three-bit field specifies the interrupt request level for all channels. Level seven for this field indicates a non-maskable interrupt; level zero indicates that all channel interrupts are disabled.

## CIBV[3:0] — Channel Interrupt Base Vector

The TPU is assigned 16 unique interrupt vector numbers, one vector number for each channel. The CIBV field specifies the most significant nibble of all 16 TPU channel interrupt vector numbers. The lower nibble of the TPU interrupt vector number is determined by the channel number on which the interrupt occurs.

## **D.8.6 Channel Interrupt Enable Register**

| CIER — Channel Interrupt Enable Register \$ |       |       |       |       |       |      |      |      |      |      |      |      |      |      | E0A  |

|---------------------------------------------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 15                                          | 14    | 13    | 12    | 11    | 10    | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| CH 15                                       | CH 14 | CH 13 | CH 12 | CH 11 | CH 10 | CH 9 | CH 8 | CH 7 | CH 6 | CH 5 | CH 4 | CH 3 | CH 2 | CH 1 | CH 0 |

| RES                                         | SET:  |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0                                           | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### CH[15:0] — Channel Interrupt Enable/Disable

0 = Channel interrupts disabled

1 = Channel interrupts enabled

# D.9 Standby RAM Module with TPU Emulation Capability (TPURAM)

**Table D-58** is the TPURAM address map. TPURAM responds to both program and data space accesses. The RASP bit in TRAMMCR determines whether the processor must be operating in supervisor mode to access the array. TPURAM control registers are accessible in supervisor mode only.

#### Table D-58 TPURAM Address Map

| Address <sup>1</sup> | 15                                                | 0 |

|----------------------|---------------------------------------------------|---|

| \$YFFB00             | TPURAM Module Configuration Register (TRAMMCR)    |   |

| \$YFFB02             | TPURAM Test Register (TRAMTST)                    |   |

| \$YFFB04             | TPURAM Base Address and Status Register (TRAMBAR) |   |

| \$YFFB06-\$YFFB3F    | Not Used                                          |   |

NOTES:

1. Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

# **D.9.1 TPURAM Module Configuration Register**

| <b>TRAMMCR</b> — TPURAM Module Configuration Register | \$YFFB00 |

|-------------------------------------------------------|----------|

|                                                       |          |

| 15   | 14  | 13 | 12 | 11 | 10 | 9 | 8    | 7 |          | 0 |

|------|-----|----|----|----|----|---|------|---|----------|---|

| STOP | 0   | 0  | 0  | 0  | 0  | 0 | RASP |   | NOT USED |   |

| RES  | ET: |    |    |    |    |   |      |   |          |   |

| 0    | 0   | 0  | 0  | 0  | 0  | 0 | 1    |   |          |   |

STOP — Low-Power Stop Mode Enable

0 = TPURAM operates normally.

1 = TPURAM enters low-power stop mode.

This bit controls whether TPURAM operates normally or enters low-power stop mode. In low-power stop mode, the array retains its contents, but cannot be read or written.

#### RASP — TPURAM Array Space

0 = TPURAM is accessible in supervisor or user space.

1 = TPURAM is accessible in supervisor space only.

#### D.9.2 TPURAM Test Register

#### TRAMTST — TPURAM Test Register

Used for factory test only.

## **D.9.3 TPURAM Module Configuration Register**

| TRAN       | <b>IBA</b> F | <b>х</b> — Т | PURA       | AM Ba      | ase Ao     | ddres      | s and      | Statu      | ıs Reg     | gister     |            |   |   | \$YFI | FB04  |

|------------|--------------|--------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---|---|-------|-------|

| 15         | 14           | 13           | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3 | 2 | 1     | 0     |

| ADDR<br>23 | ADDR<br>22   | ADDR<br>21   | ADDR<br>20 | ADDR<br>19 | ADDR<br>18 | ADDR<br>17 | ADDR<br>16 | ADDR<br>15 | ADDR<br>14 | ADDR<br>13 | ADDR<br>12 | 0 | 0 | 0     | RAMDS |

| RES        | SET:         |              |            |            |            |            |            |            |            |            |            |   |   |       |       |

| 0          | 0            | 0            | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0 | 0 | 0     | 0     |

#### **REGISTER SUMMARY**

**\$YFFB02**

# D.10.5 Control Register 1

| ( | CANC | TRL | 1 — 0 | Contro | l Reg | jister <sup>-</sup> | 1 |   |      |      |       |      |      | \$           | YFF | )87 |  |

|---|------|-----|-------|--------|-------|---------------------|---|---|------|------|-------|------|------|--------------|-----|-----|--|

|   | 15   | 14  | 13    | 12     | 11    | 10                  | 9 | 8 | 7    | 6    | 5     | 4    | 3    | 2            | 1   | 0   |  |

| ſ |      |     |       | CANC   | TRL0  |                     |   |   | SAMP | LOOP | TSYNC | LBUF | RSVD | PROPSEG[2:0] |     |     |  |

|   | RES  | ET: |       |        |       |                     |   |   |      |      |       |      |      |              |     |     |  |

|   | 0    | 0   | 0     | 0      | 0     | 0                   | 0 | 0 | 0    | 0    | 0     | 0    | 0    | 0            | 0   | 0   |  |

|   |      |     |       |        |       |                     |   |   |      |      |       |      |      |              |     |     |  |

## SAMP — Sampling Mode

The SAMP bit determines whether the TouCAN module will sample each received bit one time or three times to determine its value.

- 0 = One sample, taken at the end of phase buffer segment 1, is used to determine the value of the received bit.

- 1 = Three samples are used to determine the value of the received bit. The samples are taken at the normal sample point, and at the two preceding periods of the S-clock.

# LOOP — TouCAN Loop Back

The LOOP bit configures the TouCAN to perform internal loop back. The bit stream output of the transmitter is fed back to the receiver. The receiver ignores the CANRX0 and CANRX1 pins. The CANTX0 and CANTX1 pins output a recessive state. In this state, the TouCAN ignores the ACK bit to ensure proper reception of its own messages.

0 = Internal loop back disabled.

1 = Internal loop back enabled.

## TSYNC — Timer Synchronize Mode

The TSYNC bit enables the mechanism that resets the free-running timer each time a message is received in message buffer 0. This feature provides the means to synchronize multiple TouCAN stations with a special "SYNC" message (global network time).

- 0 = Timer synchronization disabled.

- 1 = Timer synchronization enabled.

# NOTE

There can be a bit clock skew of four to five counts between different TouCAN modules that are using this feature on the same network.

LBUF — Lowest Buffer Transmitted First

The LBUF bit defines the transmit-first scheme.

- 0 = Message buffer with lowest ID is transmitted first.

- 1 = Lowest numbered buffer is transmitted first.

PROPSEG[2:0] — Propagation Segment Time

PROPSEG defines the length of the propagation segment in the bit time. The valid programmed values are 0 to 7. The propagation segment time is calculated as follows:

RTE 5-36 RTR 13-4, 13-5, 13-15 RWU 9-29, D-44 RX Length 13-4 RX14MSKHI D-93 RX15MSKHI D-93 RX15MSKLO D-93 RXD 9-24 RXECTR D-97 RXGMSKHI D-93 RXGMSKHI D-93 RXGMSKLO D-93 RXMODE D-89 RXMODE D-89 RXWARN D-95

#### -S-

S D-4 SAMP D-90 Sample amplifier bypass (BYP) D-37 Sampling mode (SAMP) D-90 SAR 8-1, 8-16 SASM timing (electricals) A-32 SBK 9-27, D-44 Scan modes SCBR D-43 SCCR 9-21 SCCR0 D-42 SCCR1 D-43 SCDR 9-24, D-46 SCI 9-1, 9-2, 9-16, 9-21 baud clock 9-25 rate (SCBR) D-43 equation D-43 idle-line detection 9-28 internal loop 9-30 operation 9-24 parity checking 9-26 pins 9-24 receiver block diagram 9-23 operation 9-28 wakeup 9-29 registers 9-21 control registers (SCCR) 9-21 data register (SCDR) 9-24 status register (SCSR) 9-24 transmitter block diagram 9-22 operation 9-26 SCK 9-16. 9-19 actual delay before SCK (equation) 9-17 baud rate (equation) 9-17 S-clock 13-8 SCSR 9-24, D-45 Self wake enable (SELFWAKE) D-87 Send break (SBK) 9-27, D-44

Serial clock baud rate (SPBR) D-49 communication interface (SCI) 9-1, 9-21 formats 9-25 interface 4-23 mode (M) bit 9-25 shifter 9-24. 9-26 Service request breakpoint flag (SRBK) D-77 Set (definition) 2-8 SFC 4-7 SGLR D-80 SHEN 5-39, D-7 Show cycle enable (SHEN) 5-3, 5-39, D-7 operation 5-39 timing diagram A-17 Signal characteristics 3-9 functions 3-11 Signature registers (RSIGHI/LO) 7-1 SIM 5-1 address map D-5 block diagram 5-2 bus operation 5-26 chip-selects 5-54 external bus interface (EBI) 5-19 features 3-1 functional blocks 5-1 halt monitor 5-15 interrupt arbitration 5-3 interrupts 5-50 low-power stop operation 5-19 module configuration register (SIMCR) D-6 parallel I/O ports 5-64 periodic interrupt timer 5-17 block diagram (with software watchdog) 5-17 register access 5-3 registers chip-select base address register boot ROM (CSBARBT) D-17 registers (CSBAR) 5-57, 5-58, D-17 option register boot ROM (CSORBT) D-18 registers (CSOR) 5-57, 5-59, D-18 pin assignment registers (CSPAR) 5-57, D-15 clock synthesizer control register (SYNCR) D-8 distributed register (DREG) D-21 master shift register A/B (TSTMSRA/B) D-21 module configuration register (SIMCR) 5-2 periodic interrupt control register (PICR) D-13 timer register (PITR) 5-17, D-14 port C data register (PORTC) 5-60, D-15 port E data direction register (DDRE) 5-64, D-10 data register (PORTE) 5-64, D-10 pin assignment register (PEPAR) 5-64,

MC68336/376 USER'S MANUAL