Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | CPU32                                                                  |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 20MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 18                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 7.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                          |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 160-BQFP                                                               |

| Supplier Device Package    | 160-QFP (28x28)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68376bgcab20 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **SECTION 1 INTRODUCTION**

The MC68336 and the MC68376 are highly-integrated 32-bit microcontrollers, combining high-performance data manipulation capabilities with powerful peripheral subsystems.

MC68300 microcontrollers are built up from standard modules that interface through a common intermodule bus (IMB). Standardization facilitates rapid development of devices tailored for specific applications.

The MC68336 incorporates a 32-bit CPU (CPU32), a system integration module (SIM), a time processor unit (TPU), a configurable timer module (CTM4), a queued serial module (QSM), a 10-bit queued analog-to-digital converter module (QADC), a 3.5-Kbyte TPU emulation RAM module (TPURAM), and a 4-Kbyte standby RAM module (SRAM).

The MC68376 includes all of the aforementioned modules, plus a CAN 2.0B protocol controller module (TouCAN<sup>™</sup>) and an 8-Kbyte masked ROM (MRM).

The MC68336/376 can either synthesize the system clock signal from a fast reference or use an external clock input directly. Operation with a 4.194 MHz reference frequency is standard. The maximum system clock speed is 20.97 MHz. System hardware and software allow changes in clock rate during operation. Because MCU operation is fully static, register and memory contents are not affected by clock rate changes.

High-density complementary metal-oxide semiconductor (HCMOS) architecture makes the basic power consumption of the MCU low. Power consumption can be minimized by stopping the system clock. The CPU32 instruction set includes a low-power stop (LPSTOP) instruction that efficiently implements this capability.

Documentation for the Modular Microcontroller Family follows the modular construction of the devices in the product line. Each microcontroller has a comprehensive user's manual that provides sufficient information for normal operation of the device. The user's manual is supplemented by module reference manuals that provide detailed information about module operation and applications. Refer to Motorola publication *Advanced Microcontroller Unit (AMCU) Literature* (BR1116/D) for a complete listing of documentation.

## 2.2 CPU32 Registers

- A6–A0 Address registers (index registers)

- A7 (SSP) Supervisor stack pointer

- A7 (USP) User stack pointer

- CCR Condition code register (user portion of SR)

- D7–D0 Data registers (index registers)

- DFC Alternate function code register

- PC Program counter

- SFC Alternate function code register

- SR Status register

- VBR Vector base register

- X Extend indicator

- N Negative indicator

- Z Zero indicator

- V Two's complement overflow indicator

- C Carry/borrow indicator

## 2.3 Pin and Signal Mnemonics

ADDR[23:0] — Address Bus

- AN[59:48]/[3:0] QADC Analog Input

- AN[w, x, y, z] QADC Analog Input

- AS Address Strobe

- AVEC Autovector

- BERR Bus Error

- BG Bus Grant

- BGACK Bus Grant Acknowledge

- BKPT Breakpoint

- BR Bus Request

- CANRX0 TouCAN Receive Data

- CANTX0 TouCAN Transmit Data

- CLKOUT System Clock

- CS[10:0] Chip Selects

- CSBOOT Boot ROM Chip Select

- CPWM[8:5] CTM Pulse Width Modulation Channel

- CTD[10:9]/[4:3] CTM Double Action Channel

- CTM2C CTM Modulus Clock

- DATA[15:0] Data Bus

- DS Data Strobe

- DSACK[1:0] Data and Size Acknowledge

- DSCLK Development Serial Clock

- DSI Development Serial Input

- DSO Development Serial Output

- ECLK MC6800 Devices and Peripherals Bus Clock

- ETRIG[2:1] QADC External Trigger

- EXTAL Crystal Oscillator Input

- FC[2:0] Function Codes

- FREEZE Freeze

- HALT Halt

- IFETCH Instruction Fetch

- **IPIPE** Instruction Pipeline

- IRQ[7:1] Interrupt Request

- MA[2:0] QADC Multiplexed Address

- MISO QSM Master In Slave Out

- MODCLK Clock Mode Select

- MOSI QSM Master Out Slave In

- PCS[3:0] QSM Peripheral Chip-Selects

- PQA[7:0] QADC Port A

- PQB[7:0] QADC Port B

- PC[6:0] SIM Port C

- PE[7:0] SIM Port E

- PF[7:0] SIM Port F

- QUOT Quotient Out

- $R/\overline{W}$  Read/Write

- RESET Reset

- RMC Read-Modify-Write Cycle

- RXD SCI Receive Data

- SCK QSPI Serial Clock

- SIZ[1:0] Size

- $\overline{\rm SS}$  Slave Select

- T2CLK TPU Clock In

- TPUCH[15:0] TPU Channel Signals

- TSC Three-State Control

- TSTME Test Mode Enable

- V<sub>RH</sub> \_\_\_\_ QADC High Reference Voltage

- V<sub>RI</sub> \_\_\_\_ QADC Low Reference Voltage

- XFC External Filter Capacitor

- XTAL Crystal Oscillator Output

# **3.5 Signal Descriptions**

The following tables define the MC68336/376 signals. **Table 3-4** shows signal origin, type, and active state. **Table 3-5** describes signal functions. Both tables are sorted alphabetically by mnemonic. MCU pins often have multiple functions. More than one description can apply to a pin.

| Signal Name           | MCU Module | Signal Type  | Active State |

|-----------------------|------------|--------------|--------------|

| ADDR[23:0]            | SIM        | Bus          | —            |

| AN[59:48]/[3:0]       | QADC       | Input        | _            |

| AN[w, x, y, z]        | QADC       | Input        | —            |

| AS                    | SIM        | Output       | 0            |

| AVEC                  | SIM        | Input        | 0            |

| BERR                  | SIM        | Input        | 0            |

| BG                    | SIM        | Output       | 0            |

| BGACK                 | SIM        | Input        | 0            |

| BKPT                  | CPU32      | Input        | 0            |

| BR                    | SIM        | Input        | 0            |

| CLKOUT                | SIM        | Output       | _            |

| CANRX0 (MC68376 Only) | TouCAN     | Input        | —            |

| CANTX0 (MC68376 Only) | TouCAN     | Output       | —            |

| CS[10:0]              | SIM        | Output       | 0            |

| CSBOOT                | SIM        | Output       | 0            |

| CPWM[8:5]             | CTM4       | Output       | _            |

| CTD[10:9]/[4:3]       | CTM4       | Input/Output | —            |

| CTM2C                 | CTM4       | Input        | —            |

| DATA[15:0]            | SIM        | Bus          | —            |

| DS                    | SIM        | Output       | 0            |

| DSACK[1:0]            | SIM        | Input        | 0            |

| DSCLK                 | CPU32      | Input        | Serial Clock |

| DSI                   | CPU32      | Input        | Serial Data  |

| DSO                   | CPU32      | Output       | Serial Data  |

| ECLK                  | SIM        | Output       | —            |

| ETRIG[2:1]            | QADC       | Input        | —            |

| EXTAL                 | SIM        | Input        | —            |

| FC[2:0]               | SIM        | Output       | —            |

| FREEZE                | SIM        | Output       | 1            |

| HALT                  | SIM        | Input/Output | 0            |

| IFETCH                | CPU32      | Output       | 0            |

| IPIPE                 | CPU32      | Output       | 0            |

| IRQ[7:1]              | SIM        | Input        | 0            |

| MA[2:0]               | QADC       | Output       | 1            |

| MISO                  | QSM        | Input/Output | _            |

| MODCLK                | SIM        | Input        | —            |

| MOSI                  | QSM        | Input/Output |              |

| PC[6:0]               | SIM        | Output       |              |

| PCS[3:0]              | QSM        | Input/Output |              |

| PE[7:0]               | SIM        | Input/Output | —            |

| PF[7:0]               | SIM        | Input/Output | —            |

# Table 3-4 MC68336/376 Signal Characteristics

## 4.2.4.2 Alternate Function Code Registers

Alternate function code registers (SFC and DFC) contain 3-bit function codes. Function codes can be considered extensions of the 24-bit linear address that optionally provide as many as eight 16-Mbyte address spaces. The processor automatically generates function codes to select address spaces for data and programs at the user and supervisor privilege levels and to select a CPU address space used for processor functions (such as breakpoint and interrupt acknowledge cycles).

Registers SFC and DFC are used by the MOVES instruction to specify explicitly the function codes of the memory address. The MOVEC instruction is used to transfer values to and from the alternate function code registers. This is a long-word transfer; the upper 29 bits are read as zeros and are ignored when written.

### 4.2.5 Vector Base Register (VBR)

The VBR contains the base address of the 1024-byte exception vector table, consisting of 256 exception vectors. Exception vectors contain the memory addresses of routines that begin execution at the completion of exception processing. More information on the VBR and exception processing can be found in **4.9 Exception Processing**.

### 4.3 Memory Organization

Memory is organized on a byte-addressable basis in which lower addresses correspond to higher order bytes. For example, the address N of a long-word data item corresponds to the address of the most significant byte of the highest order word. The address of the most significant byte of the low-order word is N + 2, and the address of the least significant byte of the long word is N + 3. The CPU32 requires long-word and word data and all instructions to be aligned on word boundaries. Refer to **Figure 4-6**. If this does not happen, an exception will occur when the CPU32 accesses the misaligned instruction or data. Data misalignment is not supported.

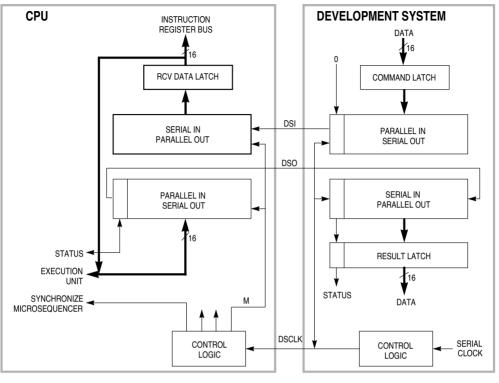

32 DEBUG I/O BLOCK

Figure 4-10 Debug Serial I/O Block Diagram

The serial interface uses a full-duplex synchronous protocol similar to the serial peripheral interface (SPI) protocol. The development system serves as the master of the serial link since it is responsible for the generation of DSCLK. If DSCLK is derived from the CPU32 system clock, development system serial logic is unhindered by the operating frequency of the target processor. Operable frequency range of the serial clock is from DC to one-half the processor system clock frequency.

The serial interface operates in full-duplex mode — data is transmitted and received simultaneously by both master and slave devices. In general, data transitions occur on the falling edge of DSCLK and are stable by the following rising edge of DSCLK. Data is transmitted MSB first, and is latched on the rising edge of DSCLK.

The serial data word is 17 bits wide, including 16 data bits and a status/control bit (refer to **Figure 4-11**). Bit 16 indicates the status of CPU-generated messages. **Table 4-7** shows the CPU-generated message types.

**CENTRAL PROCESSOR UNIT**

| Modulus | Prescalers |            |            |            |  |  |  |  |  |

|---------|------------|------------|------------|------------|--|--|--|--|--|

| Y       | [W:X] = 00 | [W:X] = 01 | [W:X] = 10 | [W:X] = 11 |  |  |  |  |  |

| 000000  | .03125     | .625       | .125       | .25        |  |  |  |  |  |

| 000001  | .0625      | .125       | .25        | .5         |  |  |  |  |  |

| 000010  | .09375     | .1875      | .375       | .75        |  |  |  |  |  |

| 000011  | .125       | .25        | .5         | 1          |  |  |  |  |  |

| 000100  | .15625     | .3125      | .625       | 1.25       |  |  |  |  |  |

| 000101  | .1875      | .375       | .75        | 1.5        |  |  |  |  |  |

| 000110  | .21875     | .4375      | .875       | 1.75       |  |  |  |  |  |

| 000111  | .25        | .5         | 1          | 2          |  |  |  |  |  |

| 001000  | .21825     | .5625      | 1.125      | 2.25       |  |  |  |  |  |

| 001001  | .3125      | .625       | 1.25       | 2.5        |  |  |  |  |  |

| 001010  | .34375     | .6875      | 1.375      | 2.75       |  |  |  |  |  |

| 001011  | .375       | .75        | 1.5        | 3          |  |  |  |  |  |

| 001100  | .40625     | .8125      | 1.625      | 3.25       |  |  |  |  |  |

| 001101  | .4375      | .875       | 1.75       | 3.5        |  |  |  |  |  |

| 001110  | .46875     | .9375      | 1.875      | 3.75       |  |  |  |  |  |

| 001111  | .5         | 1          | 2          | 4          |  |  |  |  |  |

| 010000  | .53125     | 1.0625     | 2.125      | 4.25       |  |  |  |  |  |

| 010001  | .5625      | 1.125      | 2.25       | 4.5        |  |  |  |  |  |

| 010010  | .59375     | 1.1875     | 2.375      | 4.75       |  |  |  |  |  |

| 010011  | .625       | 1.25       | 2.5        | 5          |  |  |  |  |  |

| 010100  | .65625     | 1.3125     | 2.625      | 5.25       |  |  |  |  |  |

| 010101  | .6875      | 1.375      | 2.75       | 5.5        |  |  |  |  |  |

| 010110  | .71875     | 1.4375     | 2.875      | 5.75       |  |  |  |  |  |

| 010111  | .75        | 1.5        | 3          | 6          |  |  |  |  |  |

| 011000  | .78125     | 1.5625     | 3.125      | 6.25       |  |  |  |  |  |

| 011001  | .8125      | 1.625      | 3.25       | 6.5        |  |  |  |  |  |

| 011010  | .84375     | 1.6875     | 3.375      | 6.75       |  |  |  |  |  |

| 011011  | .875       | 1.75       | 3.5        | 7          |  |  |  |  |  |

| 011100  | .90625     | 1.8125     | 3.625      | 7.25       |  |  |  |  |  |

| 011101  | .9375      | 1.875      | 3.75       | 7.5        |  |  |  |  |  |

| 011110  | .96875     | 1.9375     | 3.875      | 7.75       |  |  |  |  |  |

| 011111  | 1          | 2          | 4          | 8          |  |  |  |  |  |

# **Table 5-2 Clock Control Multipliers**

If bus termination signals remain unasserted, the MCU will continue to insert wait states, and the bus cycle will never end. If no peripheral responds to an access, or if an access is invalid, external logic should assert the BERR or HALT signals to abort the bus cycle (when BERR and HALT are asserted simultaneously, the CPU32 acts as though only BERR is asserted). When enabled, the SIM bus monitor asserts BERR when DSACK response time exceeds a predetermined limit. The bus monitor timeout period is determined by the BMT[1:0] field in SYPCR. The maximum bus monitor timeout period is 64 system clock cycles.

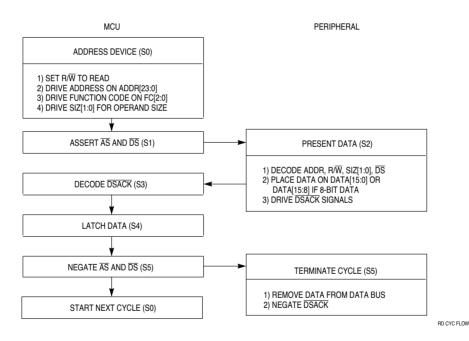

# 5.6.2.1 Read Cycle

During a read cycle, the MCU transfers data from an external memory or peripheral device. If the instruction specifies a long-word or word operation, the MCU attempts to read two bytes at once. For a byte operation, the MCU reads one byte. The portion of the data bus from which each byte is read depends on operand size, peripheral address, and peripheral port size. **Figure 5-10** is a flowchart of a word read cycle. Refer to **5.5.2 Dynamic Bus Sizing**, **5.5.4 Misaligned Operands**, and the *SIM Reference Manual* (SIMRM/AD) for more information.

Figure 5-10 Word Read Cycle Flowchart

# 5.6.3 Fast Termination Cycles

When an external device has a fast access time, the chip-select circuit fast termination option can provide a two-cycle external bus transfer. Because the chip-select circuits are driven from the system clock, the bus cycle termination is inherently synchronized with the system clock.

If multiple chip-selects are to be used to provide control signals to a single device and match conditions occur simultaneously, all MODE, STRB, and associated  $\overline{DSACK}$  fields must be programmed to the same value. This prevents a conflict on the internal bus when the wait states are loaded into the  $\overline{DSACK}$  counter shared by all chip-selects.

Fast termination cycles use internal handshaking signals generated by the chip-select logic. To initiate a transfer, the MCU asserts an address and the SIZ[1:0] signals. When  $\overline{AS}$ ,  $\overline{DS}$ , and R/W are valid, a peripheral device either places data on the bus (read cycle) or latches data from the bus (write cycle). At the appropriate time, chip-select logic asserts data and size acknowledge signals.

The DSACK option fields in the chip-select option registers determine whether internally generated DSACK or externally generated DSACK is used. The external DSACK lines are always active, regardless of the setting of the DSACK field in the chip-select option registers. Thus, an external DSACK can always terminate a bus cycle. Holding a DSACK line low will cause all external bus cycles to be three-cycle (zero wait states) accesses unless the chip-select option register specifies fast accesses.

For fast termination cycles, the fast termination encoding (%1110) must be used. Refer to **5.9.1 Chip-Select Registers** for information about fast termination setup.

To use fast termination, an external device must be fast enough to have data ready within the specified setup time (for example, by the falling edge of S4). Refer to **Table A-6** and **Figures A-6** and **A-7** for information about fast termination timing.

When fast termination is in use,  $\overline{DS}$  is asserted during read cycles but not during write cycles. The STRB field in the chip-select option register used must be programmed with the address strobe encoding to assert the chip-select signal for a fast termination write.

### 5.6.4 CPU Space Cycles

Function code signals FC[2:0] designate which of eight external address spaces is accessed during a bus cycle. Address space 7 is designated CPU space. CPU space is used for control information not normally associated with read or write bus cycles. Function codes are valid only while  $\overline{AS}$  is asserted. Refer to **5.5.1.7 Function Codes** for more information on codes and encoding.

During a CPU space access, ADDR[19:16] are encoded to reflect the type of access being made. **Figure 5-12** shows the three encodings used by 68300 family microcontrollers. These encodings represent breakpoint acknowledge (Type \$0) cycles, low power stop broadcast (Type \$3) cycles, and interrupt acknowledge (Type \$F) cycles. Refer to **5.8 Interrupts** for information about interrupt acknowledge bus cycles.

SYSTEM INTEGRATION MODULE

| Module                | Pin Mnemonic                    | Function        |  |  |

|-----------------------|---------------------------------|-----------------|--|--|

|                       | DSI/IFETCH                      | DSI/IFETCH      |  |  |

| CPU32                 | DSO/IPIPE                       | DSO/IPIPE       |  |  |

|                       | BKPT/DSCLK                      | BKPT/DSCLK      |  |  |

|                       | CPWM[8:5]                       | Discrete output |  |  |

| CTM4                  | CTD[10:9]/[4:3]                 | Discrete input  |  |  |

|                       | CTM4C                           | Discrete input  |  |  |

|                       | PQA[7:5]/AN[59:57]              | Discrete input  |  |  |

|                       | PQA[4:3]/AN[56:55]/ETRIG[2:1]   | Discrete input  |  |  |

| QADC                  | PQA[2:0]/AN[54:52]/MA[2:0]      | Discrete input  |  |  |

|                       | PQB[7:4]/AN[51:48]              | Discrete input  |  |  |

|                       | PQB[3:0]/AN[z, y, x, w]/AN[3:0] | Discrete input  |  |  |

|                       | PQS0/MISO                       | Discrete input  |  |  |

|                       | PQS1/MOSI                       | Discrete input  |  |  |

|                       | PQS2/SCK                        | Discrete input  |  |  |

| QSM                   | PQS3/PCS0/SS                    | Discrete input  |  |  |

|                       | PQS[6:4]/PCS[3:1]               | RXD             |  |  |

|                       | PQS7/TXD                        | Discrete input  |  |  |

|                       | RXD                             | Discrete input  |  |  |

| TouCAN (MC68376 only) | CANRX0                          | TouCAN receive  |  |  |

|                       | CANTX0                          | TouCAN transmit |  |  |

| TPU                   | TPUCH[15:0]                     | TPU input       |  |  |

| IFU                   | T2CLK                           | TCR2 clock      |  |  |

# Table 5-16 Module Pin Functions During Reset

# 5.7.5 Pin States During Reset

It is important to keep the distinction between pin function and pin electrical state clear. Although control register values and mode select inputs determine pin function, a pin driver can be active, inactive or in high-impedance state while reset occurs. During power-on reset, pin state is subject to the constraints discussed in **5.7.7 Power-On Reset**.

### NOTE

Pins that are not used should either be configured as outputs, or (if configured as inputs) pulled to the appropriate inactive state. This decreases additional  $I_{DD}$  caused by digital inputs floating near mid-supply level.

### 5.7.5.1 Reset States of SIM Pins

Generally, while RESET is asserted, SIM pins either go to an inactive high-impedance state or are driven to their inactive states. After RESET is released, mode selection occurs and reset exception processing begins. Pins configured as inputs must be driven to the desired active state. Pull-up or pull-down circuitry may be necessary. Pins configured as outputs begin to function after RESET is released. **Table 5-17** is a summary of SIM pin states during reset.

## 9.4.3.6 Receiver Operation

The RE bit in SCCR1 enables (RE = 1) and disables (RE = 0) the receiver. The receiver contains a receive serial shifter and a parallel receive data register (RDR) located in the SCI data register (SCDR). The serial shifter cannot be directly accessed by the CPU32. The receiver is double-buffered, allowing data to be held in the RDR while other data is shifted in.

Receiver bit processor logic drives a state machine that determines the logic level for each bit-time. This state machine controls when the bit processor logic is to sample the RXD pin and also controls when data is to be passed to the receive serial shifter. A receive time clock is used to control sampling and synchronization. Data is shifted into the receive serial shifter according to the most recent synchronization of the receive time clock with the incoming data stream. From this point on, data movement is synchronized with the MCU system clock. Operation of the receiver state machine is detailed in the *QSM Reference Manual* (QSMRM/AD).

The number of bits shifted in by the receiver depends on the serial format. However, all frames must end with at least one stop bit. When the stop bit is received, the frame is considered to be complete, and the received data in the serial shifter is transferred to the RDR. The receiver data register flag (RDRF) is set when the data is transferred.

Noise errors, parity errors, and framing errors can be detected while a data stream is being received. Although error conditions are detected as bits are received, the noise flag (NF), the parity flag (PF), and the framing error (FE) flag in SCSR are not set until data is transferred from the serial shifter to the RDR.

RDRF must be cleared before the next transfer from the shifter can take place. If RDRF is set when the shifter is full, transfers are inhibited and the overrun error (OR) flag in SCSR is set. OR indicates that the RDR needs to be serviced faster. When OR is set, the data in the RDR is preserved, but the data in the serial shifter is lost. Because framing, noise, and parity errors are detected while data is in the serial shifter, FE, NF, and PF cannot occur at the same time as OR.

When the CPU32 reads SCSR and SCDR in sequence, it acquires status and data, and also clears the status flags. Reading SCSR acquires status and arms the clearing mechanism. Reading SCDR acquires data and clears SCSR.

When RIE in SCCR1 is set, an interrupt request is generated whenever RDRF is set. Because receiver status flags are set at the same time as RDRF, they do not have separate interrupt enables.

### 9.4.3.7 Idle-Line Detection

During a typical serial transmission, frames are transmitted isochronally and no idle time occurs between frames. Even when all the data bits in a frame are logic ones, the start bit provides one logic zero bit-time during the frame. An idle line is a sequence of contiguous ones equal to the current frame size. Frame size is determined by the state of the M bit in SCCR1.

When any of the end-of-queue conditions is recognized, a queue completion flag is set, and if enabled, an interrupt request is generated. The following situations prematurely terminate queue execution:

- Since queue 1 is higher in priority than queue 2, when a trigger event occurs on queue 1 during queue 2 execution, the execution of queue 2 is suspended by aborting execution of the CCW in progress, and queue 1 execution begins. When queue 1 execution is complete, queue 2 conversions restart with the first CCW entry in queue 2 or the first CCW of the queue 2 subqueue being executed when queue 2 was suspended. Alternately, conversions can restart with the aborted queue 2 CCW entry. The resume RES bit in QACR2 allows software to select where queue 2 begins after suspension. By choosing to re-execute all of the suspended queue 2 and subqueue CCWs, all of the samples are guaranteed to have been taken during the same scan pass. However, a high trigger event rate for queue 1 can prohibit the completion of queue 2. If this occurs, execution of queue 2 may begin with the aborted CCW entry.

- When a queue is disabled, any conversion taking place for that queue is aborted. Putting a queue into disabled mode does not power down the converter.

- When the operating mode of a queue is changed to another valid mode, any conversion taking place for that queue is aborted. The queue operating restarts at the beginning of the queue, once an appropriate trigger event occurs.

- When placed in low-power stop mode, the QADC aborts any conversion in progress.

- When the FRZ bit in the QADCMCR is set and the IMB FREEZE line is asserted, the QADC freezes at the end of the current conversion. When FREEZE is negated, the QADC resumes queue execution beginning with the next CCW entry.

# 8.12.8 Result Word Table

The result word table is a 40-word long, 10-bit wide RAM. The QADC writes a result word after completing an analog conversion specified by the corresponding CCW. The result word table can be read or written, but in normal operation, software reads the result word table to obtain analog conversions from the QADC. Unimplemented bits are read as zeros, and write operations have no effect. Refer to **D.5.9 Result Word Table** for register descriptions.

While there is only one result word table, the data can be accessed in three different alignment formats:

- 1. Right justified, with zeros in the higher order unused bits.

- 2. Left justified, with the most significant bit inverted to form a sign bit, and zeros in the unused lower order bits.

- 3. Left justified, with zeros in the unused lower order bits.

The left justified, signed format corresponds to a half-scale, offset binary, two's complement data format. The data is routed onto the IMB according to the selected format. The address used to access the table determines the data alignment format. All write operations to the result word table are right justified.

| Message Buffer (MB)<br>/Mask | Base ID<br>ID[28:18] | IDE | Extended ID<br>ID[17:0] | Match           |

|------------------------------|----------------------|-----|-------------------------|-----------------|

| MB2                          | 11111111000          | 0   | _                       | _               |

| MB3                          | 11111111000          | 1   | 01010101010101010101    | _               |

| MB4                          | 00000011111          | 0   | _                       | _               |

| MB5                          | 00000011101          | 1   | 0101010101010101010101  | _               |

| MB14                         | 11111111000          | 1   | 0101010101010101010101  | _               |

| RX Global Mask               | 11111111110          |     | 11111100000000000       | —               |

| RX Message In                | 11111111001          | 1   | 01010101010101010101    | 3 <sup>1</sup>  |

|                              | 1111111001           | 0   | —                       | 2 <sup>2</sup>  |

|                              | 1111111001           | 1   | 01010101010101010100    | _3              |

|                              | 0111111000           | 0   | _                       | 4               |

|                              | 0111111000           | 1   | 01010101010101010101    | 5               |

| RX 14 Mask                   | 01111111111          |     | 11111110000000000000    | —               |

| RX Message In                | 10111111000          | 1   | 01010101010101010101    | 6               |

|                              | 0111111000           | 1   | 01010101010101010101    | 14 <sup>7</sup> |

#### Table 13-7 Mask Examples for Normal/Extended Messages

NOTES:

1. Match for extended format (MB3).

- 2. Match for standard format (MB2).

- 3. No match for MB3 because of ID0.

- 4. No match for MB2 because of ID28.

5. No match for MB3 because of ID28, match for MB14.

- 6. No match for MB14 because of ID27.

- 7. Match for MB14.

# 13.4.3 Bit Timing

The TouCAN module uses three 8-bit registers to set-up the bit timing parameters required by the CAN protocol. Control registers 1 and 2 (CANCTRL1, CANCTRL2) contain the PROPSEG, PSEG1, PSEG2, and the RJW fields which allow the user to configure the bit timing parameters. The prescaler divide register (PRESDIV) allows the user to select the ratio used to derive the S-clock from the system clock. The time quanta clock operates at the S-clock frequency. **Table 13-8** provides examples of system clock, CAN bit rate, and S-clock bit timing parameters. Refer to **APPENDIX D REGISTER SUMMARY** for more information on the bit timing registers.

# **Table A-5 DC Characteristics**

$(V_{DD} \text{ and } V_{DDSYN} = 5.0 \text{ Vdc} \pm 5\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)$

| Num | Characteristic                                                                                                                                                                                                                                         | Symbol                                                                                | Min                    | Max                    | Unit                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|------------------------|----------------------|

| 1   | Input High Voltage                                                                                                                                                                                                                                     | V <sub>IH</sub>                                                                       | 0.7 (V <sub>DD</sub> ) | V <sub>DD</sub> + 0.3  | V                    |

| 2   | Input Low Voltage                                                                                                                                                                                                                                      | V <sub>IL</sub>                                                                       | V <sub>SS</sub> - 0.3  | 0.2 (V <sub>DD</sub> ) | V                    |

| 3   | Input Hysteresis <sup>1</sup>                                                                                                                                                                                                                          | V <sub>HYS</sub>                                                                      | 0.5                    | —                      | V                    |

| 4   | Input Leakage Current <sup>2</sup><br>$V_{in} = V_{DD}$ or $V_{SS}$ Input-only pins                                                                                                                                                                    | l <sub>in</sub>                                                                       | -2.5                   | 2.5                    | μA                   |

| 5   | High Impedance (Off-State) Leakage Current <sup>2</sup><br>$V_{in} = V_{DD}$ or $V_{SS}$ All input/output and output pins                                                                                                                              | I <sub>oz</sub>                                                                       | -2.5                   | 2.5                    | μА                   |

| 6   | CMOS Output High Voltage <sup>2, 3</sup><br>$I_{OH} = -10.0 \mu A$ Group 1, 2, 4 input/output and all output pins                                                                                                                                      | V <sub>OH</sub>                                                                       | V <sub>DD</sub> - 0.2  | _                      | v                    |

| 7   | CMOS Output Low Voltage <sup>2</sup><br>$I_{OL} = 10.0 \ \mu A$ Group 1, 2, 4 input/output and all output pins                                                                                                                                         | V <sub>OL</sub>                                                                       | _                      | 0.2                    | v                    |

| 8   | Output High Voltage <sup>2, 3</sup><br>$I_{OH} = -0.8 \text{ mA}$ Group 1, 2, 4 input/output and all output pins                                                                                                                                       | V <sub>OH</sub>                                                                       | V <sub>DD</sub> – 0.8  | _                      | v                    |

| 9   | Output Low Voltage2 $I_{OL} = 1.6 \text{ mA}$ Group 1 I/O Pins, CLKOUT, FREEZE/QUOT, IPIPE $I_{OL} = 5.3 \text{ mA}$ Group 2 and Group 4 I/O Pins, CSBOOT, BG/CS $I_{OL} = 12 \text{ mA}$ Group 3                                                      | V <sub>ol</sub>                                                                       | <br>                   | 0.4<br>0.4<br>0.4      | V                    |

| 10  | Three State Control Input High Voltage                                                                                                                                                                                                                 | V <sub>IHTSC</sub>                                                                    | 1.6 (V <sub>DD</sub> ) | 9.1                    | V                    |

| 11  | Data Bus Mode Select Pull-up Current4 $V_{in} = V_{IL}$ DATA[15:0] $V_{in} = V_{IH}$ DATA[15:0]                                                                                                                                                        | I <sub>MSP</sub>                                                                      | —<br>–15               | -120<br>               | μΑ                   |

| 12A | MC68336 V <sub>DD</sub> Supply Current <sup>5</sup><br>RUN <sup>6</sup><br>RUN, TPU emulation mode<br>LPSTOP, 4.194 MHz crystal, VCO Off (STSIM = 0)<br>LPSTOP (External clock input frequency = maximum f <sub>sys</sub> )                            | I <sub>DD</sub><br>I <sub>DD</sub><br>S <sub>IDD</sub><br>S <sub>IDD</sub>            | <br>                   | 140<br>150<br>3<br>7   | mA<br>mA<br>mA<br>mA |

| 12B | MC68376 V <sub>DD</sub> Supply Current <sup>5</sup><br>RUN <sup>6</sup><br>RUN, TPU emulation mode<br>LPSTOP, 4.194 MHz crystal, VCO Off (STSIM = 0)<br>LPSTOP (External clock input frequency = maximum f <sub>sys</sub> )                            | I <sub>DD</sub><br>I <sub>DD</sub><br>S <sub>IDD</sub><br>S <sub>IDD</sub>            | <br>                   | 150<br>160<br>3<br>7   | mA<br>mA<br>mA<br>mA |

| 13  | Clock Synthesizer Operating Voltage                                                                                                                                                                                                                    | VDDSYN                                                                                | 4.75                   | 5.25                   | V                    |

| 14  | V <sub>DDSYN</sub> Supply Current <sup>5</sup><br>4.194 MHz crystal, VCO on, maximum f <sub>sys</sub><br>External Clock, maximum f <sub>sys</sub><br>LPSTOP, 4.194 MHz crystal, VCO off (STSIM = 0)<br>4.194 MHz crystal, V <sub>DD</sub> powered down | I <sub>ddsyn</sub><br>I <sub>ddsyn</sub><br>S <sub>iddsyn</sub><br>I <sub>ddsyn</sub> | <br>                   | 3<br>5<br>3<br>3       | mA<br>mA<br>mA<br>mA |

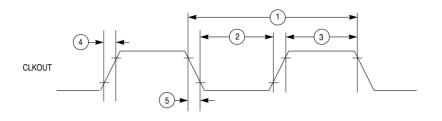

68300 CLKOUT TIM

Figure A-1 CLKOUT Output Timing Diagram

NOTE: TIMING SHOWN WITH RESPECT TO 20% AND 70%  $V_{DD}.$  PULSE WIDTH SHOWN WITH RESPECT TO 50%  $V_{DD}.$

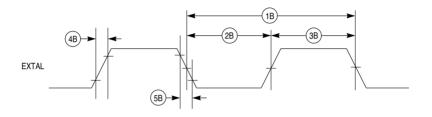

68300 EXT CLK INPUT TIM

NOTE: TIMING SHOWN WITH RESPECT TO 20% AND 70% VDD.

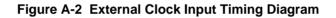

68300 ECLK OUTPUT TIM

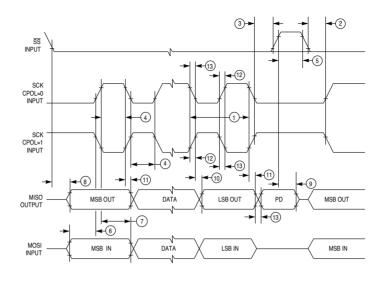

QSPI SLV CPHA0

Figure A-18 QSPI Timing — Slave, CPHA = 0

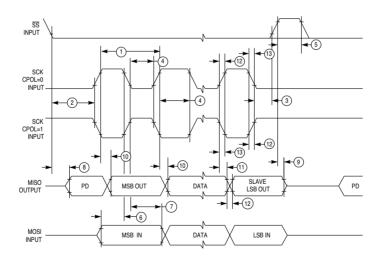

QSPI SLV CPHA1

Figure A-19 QSPI Timing — Slave, CPHA = 1

MC68336/376 USER'S MANUAL

#### **ELECTRICAL CHARACTERISTICS**

MOTOROLA A-25

#### IVB[7:0] — Interrupt Vector Base

Only the upper six bits of IVB[7:0] can be initialized. During interrupt arbitration, the vector provided by the QADC is made up of IVB[7:2], plus two low-order bits that identify one of the four QADC interrupt sources. Once IVB is written, the two low-order bits always read as zeros.

# D.5.4 Port A/B Data Register

|                                                            | PORTQA — Port QA Data Register\$YFF206PORTQB — Port QB Data Register\$YFF207 |          |          |        |        |      |      |      |      |      |      |      |      |      |      |      |

|------------------------------------------------------------|------------------------------------------------------------------------------|----------|----------|--------|--------|------|------|------|------|------|------|------|------|------|------|------|

|                                                            | 15                                                                           | 14       | 13       | 12     | 11     | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| P                                                          | QA7                                                                          | PQA6     | PQA5     | PQA4   | PQA3   | PQA2 | PQA1 | PQA0 | PQB7 | PQB6 | PQB5 | PQB4 | PQB3 | PQB2 | PQB1 | PQB0 |

|                                                            | RES                                                                          | SET:     |          |        |        |      |      |      |      |      |      |      |      |      |      |      |

|                                                            | U                                                                            | U        | U        | U      | U      | U    | U    | U    | U    | U    | U    | U    | U    | U    | U    | U    |

|                                                            | ANALOG CHANNEL:                                                              |          |          |        |        |      |      |      |      |      |      |      |      |      |      |      |

| A                                                          | N59                                                                          | AN58     | AN57     | AN56   | AN55   | AN54 | AN53 | AN52 | AN51 | AN50 | AN49 | AN48 | AN3  | AN2  | AN1  | AN0  |

|                                                            | EXTE                                                                         | RNAL TRI | IGGER IN | PUTS:  |        |      |      |      |      |      |      |      |      |      |      |      |

|                                                            |                                                                              |          |          | ETRIG2 | ETRIG1 |      |      |      |      |      |      |      |      |      |      |      |

| MULTIPLEXED ADDRESS OUTPUTS:<br>MULTIPLEXED ANALOG INPUTS: |                                                                              |          |          |        | UTS:   |      |      |      |      |      |      |      |      |      |      |      |

|                                                            |                                                                              |          |          |        | MA2    | MA1  | MA0  |      |      |      |      |      |      |      |      |      |

|                                                            |                                                                              |          |          |        |        |      |      |      |      |      |      |      |      |      |      |      |

|                                                            |                                                                              |          |          |        |        |      |      |      |      |      |      |      | ANz  | ANy  | ANx  | ANw  |

QADC ports A and B are accessed through two 8-bit port data registers (PORTQA and PORTQB). Port A pins are referred to as PQA[7:0] when used as an 8-bit input/output port. Port A can also be used for analog inputs (AN[59:52]), external trigger inputs (ETRIG[2:1]), and external multiplexer address outputs (MA[2:0]).

Port B pins are referred to as PQB[7:0] when used as an 8-bit input only port. Port B can also be used for non-multiplexed (AN[51:48])/AN[3:0]) and multiplexed (ANz, ANy, ANx, ANw) analog inputs.

# D.5.5 Port Data Direction Register

| <b>DDRQA</b> — Port QA Data Direction Register\$YFF208 |       |                                                  |    |    |    |   |   |   |   |   |   |   | 208 |   |   |

|--------------------------------------------------------|-------|--------------------------------------------------|----|----|----|---|---|---|---|---|---|---|-----|---|---|

| 15                                                     | 14    | 13                                               | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

| DDQA7                                                  | DDQA6 | QA6 DDQA5 DDQA4 DDQA3 DDQA2 DDQA1 DDQA0 RESERVED |    |    |    |   |   |   |   |   |   |   |     |   |   |

| RESET:                                                 |       |                                                  |    |    |    |   |   |   |   |   |   |   |     |   |   |

| 0                                                      | 0     | 0                                                | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 |

Bits in this register control the direction of the port QA pin drivers when pins are configured for I/O. Setting a bit configures the corresponding pin as an output; clearing a bit configures the corresponding pin as an input. This register can be read or written at any time.

**FDGEN D-62** FDGFP D-62 EDIV 5-12. D-8 EDPOL D-65 **EMPTY 13-4** EMU 11-5. 11-15. D-74 EMUL D-25 Emulation control (EMU) 11-15, D-74 mode control (EMUL) D-25 support 11-5 EN D-70 Encoded one of three channel priority levels (CH) D-80 time function for each channel (CHANNEL) D-78 type of host service (CH) D-79 Ending queue pointer (ENDQP) D-52 End-offrame (EOF) 13-16 queue condition 8-30 ENDQP 9-8, D-52 EOF 13-16 ERRINT D-96 ERRMSK D-89 Error conditions 9-28 counters 13-9 detection circuitry 9-2 interrupt (ERRINT) D-96 interrupt mask (ERRMSK) D-89 ESTAT D-94 ETRIG 8-5 Event flag (FLAG) D-63 Event timing 11-3 Exception instruction (RTE) 5-36 processing 4-15, 5-40 sequence 4-17 types of exceptions 4-17 vectors 4-15 exception vector assignments 4-16 vector 5-40, 11-6 EXOFF D-6 EXT D-9 Extended message format 13-1 frames 13-4 External bus arbitration 5-38 clock division (EDIV) D-8 division bit (EDIV) 5-12 operation during LPSTOP 5-12 signal (ECLK) 5-12 interface (EBI) 5-19 control signals 5-21 clock input timing diagram A-10 clock off (EXOFF) D-6 digital supply pin 8-6 multiplexing 8-10

reset (EXT) D-9 trigger pins 8-5 Externally input clock frequency D-14 multiplexed mode (MUX) D-31 EXTRST (external reset) 5-48

#### -F-

Factory test 5-64 FAR 4-22 Fast quadrature decode (FQD) 11-12 reference 5-4 circuit 5-5 termination cycles 5-26, 5-30 read cycle timing diagram A-13 write cvcle timing diagram A-14 Fast reference frequency D-14 Fault confinement state (FCS) 13-10, D-95 FC 5-22 FCS 13-10. D-95 FCSM 10-5 block diagram 10-5 clock sources 10-6 counter 10-6 external event counting 10-6 interrupts 10-6 registers 10-7 counter register (FCSMCNT) D-61 status/interrupt/control register (FCSMSIC) D-59 time base bus drivers 10-6 timing (electricals) A-31 FCSMCNT D-61 FCSMSIC D-59 FE 9-28, D-46 Final sample time 8-13 FLAG D-63, D-68 FORCA D-65 FORCB D-65 Force (FORCA/B) D-65 FORMERR D-94 f<sub>PWM</sub> 10-16 f<sub>OCLK</sub> 8-24 FQD 11-12 FQM 11-13 Frame 9-25 size 9-28 Frames overload 13-16 remote 13-15 Framing error (FE) flag 9-28, D-46 Free-running counter submodule. See FCSM 10-5 FREEZ ACK 13-16 FREEZE assertion response (FRZ) BIUSM 10-3, D-57 QADC 8-7, D-29

LR D-80 LSB 2-8, 4-4, 8-15 LSW 2-8

#### -M-

M 9-25, D-44 M68000 family compatibility 4-14 development support 4-18 M68MEVB1632 C-1 modular evaluation board (MEVB) C-1 M68MMDS1632 C-1 Mask examples for normal/extended messages 13-8 registers (RX) 13-7 Masked ROM module (MRM). See MRM 7-1 Master /slave mode select (MSTR) D-48 shift registers (TSTMSR) D-21 Maximum ratings (electrical) A-1 MC68010 4-14 MC68020 4-10, 4-14 MCSM 10-5, 10-7 block diagram 10-8 clock sources 10-9 counter 10-8 external event counting 10-9 interrupts 10-9 modulus latch 10-8 registers 10-10 counter register (MCSMCNT) D-63 modulus latch register (MCSMML) D-63 status/interrupt/control register (MCSMSIC) D-61 time base bus drivers 10-9 timing (electricals) A-31 MCSMCNT D-63 MCSMML D-63 MCSMSIC D-61 MCU basic system 5-20 block diagram 3-4 features 3-1 personality board (MPB) C-1 pin assignment package MC68336 160-pin package 3-5, B-1 MC68376 160-pin package 3-6. B-2 Mechanical information B-4 Memory CPU32 organization 4-7 maps overall memory 3-15 separate supervisor and user space 3-16 supervisor space (separate program/data space) 3-17 user space (separate program/data space) 3-18 virtual 4-9 Message

buffer address map D-85 code for RX/TX buffers 13-4 deactivation 13-13 structure 13-3 format error (FORMERR) D-94 Mid-analog supply voltage 8-15 Misaligned operand 5-25 MISO 9-16, 9-19 MM 6-1, 7-1, 9-2, D-7 MMDS C-1 Mnemonics pin and signal 2-2 range (definition) 2-8 register 2-4 specific (definition) 2-8 MODCLK 5-49 MODE 5-59, D-18, D-66 Mode fault flag (MODF) 9-9, D-53 select (M) D-44 Modes disabled 8-20 reserved 8-20 scan. See Scan modes MODE 9-9, D-53 Modular platform board C-1 Module mapping (MM) bit 5-2, 6-1, 7-1, 9-2, D-6, D-7 pin functions 5-45 Modulus counter 9-25 counter submodule (MCSM). See MCSM 10-5, 10-7 load edge sensitivity (EDGEN, EDGEP) bits D-62 input pin status (IN1) D-62 MOSI 9-16, 9-19 Most significant bit (MSB) 8-15 Motorola Microcontroller Development Tools Directorv (MCUDEVTLDIR/D Rev. 3) C-1 modular development system (MMDS) C-1 MPB C-1 MQ1 D-32 MQ2 D-33 **MRM 7-1** address map D-24 array address mapping 7-1 features 3-1 low-power stop operation 7-3 normal access 7-2 registers module configuration register (MRMCR) 7-1, D-24 ROM array base address registers (ROM-BAH/BAL) 7-1, D-26 bootstrap words (ROMBS) 7-1, D-27 signature registers (RSIGHI/LO) 7-1, D-26 reset 7-3