Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | CPU32                                                                  |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 20MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 18                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 7.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                          |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 160-BQFP                                                               |

| Supplier Device Package    | 160-QFP (28x28)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68376bgmab20 |

# TABLE OF CONTENTS (Continued)

| Paragraph                                                                   |                                                                                                                  | itle Page                              |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5.10.2<br>5.10.3<br>5.11                                                    | Data Registers                                                                                                   |                                        |

|                                                                             | SECTION 6 STAND                                                                                                  | BY RAM MODULE                          |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                      | SRAM Array Address Mapping<br>SRAM Array Address Space Type<br>Normal Access<br>Standby and Low-Power Stop Oper  |                                        |

|                                                                             | SECTION 7 MASK                                                                                                   | ED ROM MODULE                          |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7                               | MRM Array Address Mapping MRM Array Address Space Type Normal Access Low-Power Stop Mode Operation ROM Signature | 7-1 7-1 7-2 7-2 7-3 7-3 7-3            |

|                                                                             | SECTION 8 QUEUED ANALOG-TO                                                                                       | D-DIGITAL CONVERTER MODULE             |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.4.1<br>8.4.1.1<br>8.4.1.2<br>8.4.2<br>8.4.2.1 | QADC Address Map                                                                                                 | 8-1 8-2 8-2 8-2 8-3 8-3 1 Pins 8-4 8-4 |

| 8.4.2.2<br>8.4.3<br>8.4.4<br>8.4.5                                          | Port B Digital Input Pins<br>External Trigger Input Pins<br>Multiplexed Address Output Pi                        |                                        |

| 8.4.6<br>8.4.7<br>8.4.8<br>8.4.9                                            | Voltage Reference Pins Dedicated Analog Supply Pins External Digital Supply Pin                                  | 8-5<br>8-6<br>8-6<br>8-6               |

# LIST OF TABLES (Continued)

| Table | Title                                  | Page |

|-------|----------------------------------------|------|

| D-35  | CTM4 Address Map                       | D-56 |

| D-36  | Interrupt Vector Base Number Bit Field | D-57 |

| D-37  | Time Base Register Bus Select Bits     | D-58 |

| D-38  | Prescaler Division Ratio Select Field  | D-59 |

| D-39  | Drive Time Base Bus Field              | D-60 |

| D-40  | Counter Clock Select Field             | D-60 |

| D-41  | Drive Time Base Bus Field              | D-62 |

| D-42  | Modulus Load Edge Sensitivity Bits     | D-62 |

| D-43  | Counter Clock Select Field             | D-62 |

| D-44  | DASM Mode Flag Status Bit States       | D-64 |

| D-45  | Edge Polarity                          | D-65 |

| D-46  | DASM Mode Select Field                 | D-66 |

| D-47  | DASMA Operations                       | D-67 |

| D-48  | DASMB Operations                       | D-68 |

| D-49  | PWMSM Output Pin Polarity Selection    | D-70 |

| D-50  | PWMSM Divide By Options                | D-71 |

| D-51  | TPU Register Map                       | D-73 |

| D-52  | TCR1 Prescaler Control Bits            | D-74 |

| D-53  | TCR2 Prescaler Control Bits            | D-74 |

| D-54  | FRZ[1:0] Encoding                      | D-76 |

| D-55  | Breakpoint Enable Bits                 | D-76 |

| D-56  | Channel Priorities                     | D-80 |

| D-57  | Parameter RAM Address Map              | D-81 |

| D-58  | TPURAM Address Map                     | D-82 |

| D-59  | TouCAN Address Map                     | D-84 |

| D-60  | RX MODE[1:0] Configuration             | D-89 |

| D-61  | Transmit Pin Configuration             | D-89 |

| D-62  | Transmit Bit Error Status              | D-94 |

| D-63  | Fault Confinement State Encoding       | D-95 |

**Table 4-4** summarizes the processing of each source for both enabled and disabled cases. As shown in **Table 4-4**, the BKPT instruction never causes a transition into BDM.

**Table 4-4 BDM Source Summary**

| Source           | BDM Enabled                                 | BDM Disabled                                |

|------------------|---------------------------------------------|---------------------------------------------|

| BKPT             | Background                                  | Breakpoint Exception                        |

| Double Bus Fault | Background                                  | Halted                                      |

| BGND Instruction | Background                                  | Illegal Instruction                         |

| BKPT Instruction | Opcode Substitution/<br>Illegal Instruction | Opcode Substitution/<br>Illegal Instruction |

# 4.10.4.1 External BKPT Signal

Once enabled, BDM is initiated whenever assertion of BKPT is acknowledged. If BDM is disabled, a breakpoint exception (vector \$0C) is acknowledged. The BKPT input has the same timing relationship to the data strobe trailing edge as does read cycle data. There is no breakpoint acknowledge bus cycle when BDM is entered.

## 4.10.4.2 BGND Instruction

An illegal instruction, \$4AFA, is reserved for use by development tools. The CPU32 defines \$4AFA (BGND) to be a BDM entry point when BDM is enabled. If BDM is disabled, an illegal instruction trap is acknowledged.

#### 4.10.4.3 Double Bus Fault

The CPU32 normally treats a double bus fault, or two bus faults in succession, as a catastrophic system error, and halts. When this condition occurs during initial system debug (a fault in the reset logic), further debugging is impossible until the problem is corrected. In BDM, the fault can be temporarily bypassed, so that the origin of the fault can be isolated and eliminated.

## 4.10.4.4 Peripheral Breakpoints

CPU32 peripheral breakpoints are implemented in the same way as external breakpoints — peripherals request breakpoints by asserting the BKPT signal. Consult the appropriate peripheral user's manual for additional details on the generation of peripheral breakpoints.

# 4.10.5 Entering BDM

When the processor detects a breakpoint or a double bus fault, or decodes a BGND instruction, it suspends instruction execution and asserts the FREEZE output. This is the first indication that the processor has entered BDM. Once FREEZE has been asserted, the CPU enables the serial communication hardware and awaits a command.

The CPU writes a unique value indicating the source of BDM transition into temporary register A (ATEMP) as part of the process of entering BDM. A user can poll ATEMP and determine the source (refer to **Table 4-5**) by issuing a read system register command (RSREG). ATEMP is used in most debugger commands for temporary storage

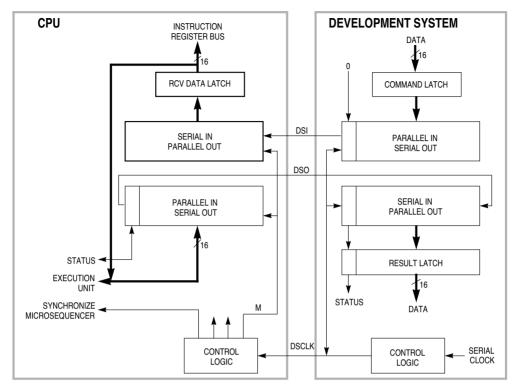

32 DEBUG I/O BLOCK

Figure 4-10 Debug Serial I/O Block Diagram

The serial interface uses a full-duplex synchronous protocol similar to the serial peripheral interface (SPI) protocol. The development system serves as the master of the serial link since it is responsible for the generation of DSCLK. If DSCLK is derived from the CPU32 system clock, development system serial logic is unhindered by the operating frequency of the target processor. Operable frequency range of the serial clock is from DC to one-half the processor system clock frequency.

The serial interface operates in full-duplex mode — data is transmitted and received simultaneously by both master and slave devices. In general, data transitions occur on the falling edge of DSCLK and are stable by the following rising edge of DSCLK. Data is transmitted MSB first, and is latched on the rising edge of DSCLK.

The serial data word is 17 bits wide, including 16 data bits and a status/control bit (refer to **Figure 4-11**). Bit 16 indicates the status of CPU-generated messages. **Table 4-7** shows the CPU-generated message types.

Because the SIM routes external interrupt requests to the CPU32, the SIM IARB field value is used for arbitration between internal and external interrupts of the same priority. The reset value of IARB for the SIM is %1111, and the reset IARB value for all other modules is %0000, which prevents SIM interrupts from being discarded during initialization. Refer to **5.8 Interrupts** for a discussion of interrupt arbitration.

# 5.2.3 Show Internal Cycles

A show cycle allows internal bus transfers to be monitored externally. The SHEN field in SIMCR determines what the external bus interface does during internal transfer operations. **Table 5-1** shows whether data is driven externally, and whether external bus arbitration can occur. Refer to **5.6.6.1 Show Cycles** for more information.

| rabio o i onon oyolo Inabio Bito |                                                                                               |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| SHEN[1:0]                        | Action                                                                                        |  |  |

| 00                               | Show cycles disabled, external arbitration enabled                                            |  |  |

| 01                               | Show cycles enabled, external arbitration disabled                                            |  |  |

| 10                               | Show cycles enabled, external arbitration enabled                                             |  |  |

| 11                               | Show cycles enabled, external arbitration enabled; internal activity is halted by a bus grant |  |  |

**Table 5-1 Show Cycle Enable Bits**

# 5.2.4 Register Access

The CPU32 can operate at one of two privilege levels. Supervisor level is more privileged than user level — all instructions and system resources are available at supervisor level, but access is restricted at user level. Effective use of privilege level can protect system resources from uncontrolled access. The state of the S bit in the CPU status register determines access level, and whether the user or supervisor stack pointer is used for stacking operations. The SUPV bit places SIM global registers in either supervisor or user data space. When SUPV = 0, registers with controlled access are accessible from either the user or supervisor privilege level; when SUPV = 1, registers with controlled access are restricted to supervisor access only.

# 5.2.5 Freeze Operation

The FREEZE signal halts MCU operations during debugging. FREEZE is asserted internally by the CPU32 if a breakpoint occurs while background mode is enabled. When FREEZE is asserted, only the bus monitor, software watchdog, and periodic interrupt timer are affected. The halt monitor and spurious interrupt monitor continue to operate normally. Setting the freeze bus monitor (FRZBM) bit in SIMCR disables the bus monitor when FREEZE is asserted. Setting the freeze software watchdog (FRZSW) bit disables the software watchdog and the periodic interrupt timer when FREEZE is asserted.

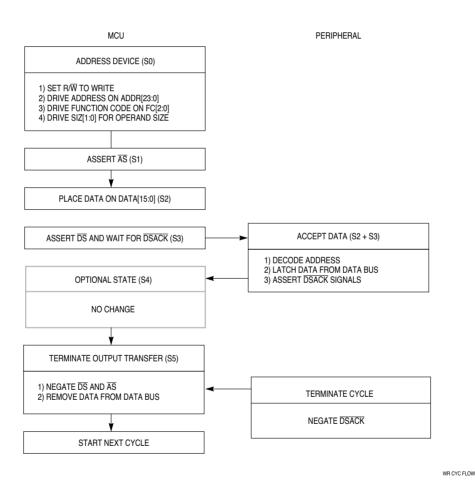

## 5.6.2.2 Write Cycle

During a write cycle, the MCU transfers data to an external memory or peripheral device. If the instruction specifies a long-word or word operation, the MCU attempts to write two bytes at once. For a byte operation, the MCU writes one byte. The portion of the data bus upon which each byte is written depends on operand size, peripheral address, and peripheral port size.

Refer to **5.5.2 Dynamic Bus Sizing** and **5.5.4 Misaligned Operands** for more information. **Figure 5-11** is a flowchart of a write-cycle operation for a word transfer. Refer to the *SIM Reference Manual* (SIMRM/AD) for more information.

Figure 5-11 Write Cycle Flowchart

tion to restart at the designated location. Reads of SPCR2 return the current value of the register, not of the buffer. Writing the same value into any control register except SPCR2 while the QSPI is enabled has no effect on QSPI operation.

## 9.3.1.2 Status Register

SPSR contains information concerning the current serial transmission. Only the QSPI can set the bits in this register. The CPU32 reads SPSR to obtain QSPI status information and writes SPSR to clear status flags.

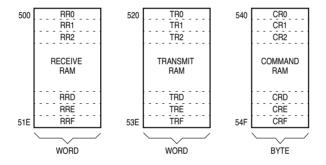

## **9.3.2 QSPI RAM**

The QSPI contains an 80-byte block of dual-port access static RAM that can be accessed by both the QSPI and the CPU32. The RAM is divided into three segments: receive data RAM, transmit data RAM, and command data RAM. Receive data is information received from a serial device external to the MCU. Transmit data is information stored for transmission to an external device. Command control data defines transfer parameters. Refer to **Figure 9-3**, which shows RAM organization.

Figure 9-3 QSPI RAM

#### 9.3.2.1 Receive RAM

Data received by the QSPI is stored in this segment. The CPU32 reads this segment to retrieve data from the QSPI. Data stored in the receive RAM is right-justified. Unused bits in a receive queue entry are set to zero by the QSPI upon completion of the individual queue entry. The CPU32 can access the data using byte, word, or long-word addressing.

The CPTQP value in SPSR shows which queue entries have been executed. The CPU32 uses this information to determine which locations in receive RAM contain valid data before reading them.

#### 9.3.2.2 Transmit RAM

Data that is to be transmitted by the QSPI is stored in this segment and must be written to transmit RAM in a right-justified format. The QSPI cannot modify information in the transmit RAM. The QSPI copies the information to its data serializer for transmission. Information remains in transmit RAM until overwritten.

OSPI RAM MAP

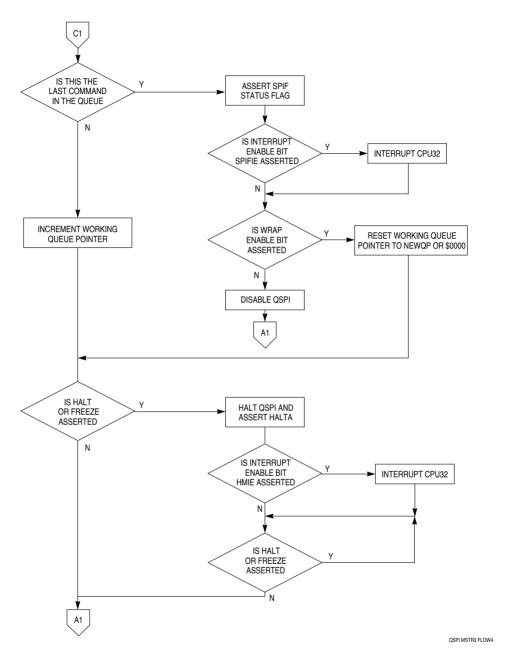

Figure 9-7 Flowchart of QSPI Master Operation (Part 3)

## 9.3.5.2 Master Wrap-Around Mode

Wrap-around mode is enabled by setting the WREN bit in SPCR2. The queue can wrap to pointer address \$0 or to the address pointed to by NEWQP, depending on the state of the WRTO bit in SPCR2.

In wrap-around mode, the QSPI cycles through the queue continuously, even while the QSPI is requesting interrupt service. SPE is not cleared when the last command in the queue is executed. New receive data overwrites previously received data in receive RAM. Each time the end of the queue is reached, the SPIF flag is set. SPIF is not automatically reset. If interrupt-driven QSPI service is used, the service routine must clear the SPIF bit to end the current interrupt request. Additional interrupt requests during servicing can be prevented by clearing SPIFIE, but SPIFIE is buffered. Clearing it does not end the current request.

Wrap-around mode is exited by clearing the WREN bit or by setting the HALT bit in SPCR3. Exiting wrap-around mode by clearing SPE is not recommended, as clearing SPE may abort a serial transfer in progress. The QSPI sets SPIF, clears SPE, and stops the first time it reaches the end of the queue after WREN is cleared. After HALT is set, the QSPI finishes the current transfer, then stops executing commands. After the QSPI stops, SPE can be cleared.

#### 9.3.5.3 Slave Mode

Clearing the MSTR bit in SPCR0 selects slave mode operation. In slave mode, the QSPI is unable to initiate serial transfers. Transfers are initiated by an external SPI bus master. Slave mode is typically used on a multi-master SPI bus. Only one device can be bus master (operate in master mode) at any given time.

Before QSPI operation is initiated, QSM register PQSPAR must be written to assign necessary pins to the QSPI. The pins necessary for slave mode operation are MISO and MOSI, SCK, and PCS0/ $\overline{SS}$ . MISO is used for serial data output in slave mode, and MOSI is used for serial data input. Either or both may be necessary, depending on the particular application. SCK is the serial clock input in slave mode. Assertion of the active-low slave select signal  $\overline{SS}$  initiates slave mode operation.

Before slave mode operation is initiated, DDRQS must be written to direct data flow on the QSPI pins used. Configure the MOSI, SCK and PCS0/SS pins as inputs. The MISO pin must be configured as an output.

After pins are assigned and configured, write data to be transmitted into transmit RAM. Command RAM is not used in slave mode, and does not need to be initialized. Set the queue pointers, as appropriate.

When SPE is set and MSTR is clear, a low state on the slave select PCS0/SS pin begins slave mode operation at the address indicated by NEWQP. Data that is received is stored at the pointer address in receive RAM. Data is simultaneously loaded into the data serializer from the pointer address in transmit RAM and transmitted. Transfer is synchronized with the externally generated SCK. The CPHA and CPOL bits determine upon which SCK edge to latch incoming data from the MISO pin and to drive outgoing data from the MOSI pin.

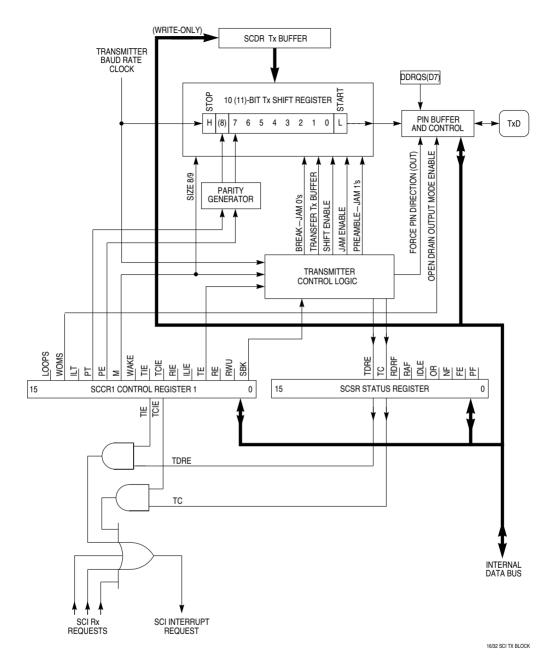

Figure 9-10 SCI Transmitter Block Diagram

The SCI receiver has both short and long idle-line detection capability. Idle-line detection is always enabled. The idle line type (ILT) bit in SCCR1 determines which type of detection is used. When an idle line condition is detected, the IDLE flag in SCSR is set.

For short idle-line detection, the receiver bit processor counts contiguous logic one bittimes whenever they occur. Short detection provides the earliest possible recognition of an idle line condition, because the stop bit and contiguous logic ones before and after it are counted. For long idle-line detection, the receiver counts logic ones after the stop bit is received. Only a complete idle frame causes the IDLE flag to be set.

In some applications, software overhead can cause a bit-time of logic level one to occur between frames. This bit-time does not affect content, but if it occurs after a frame of ones when short detection is enabled, the receiver flags an idle line.

When the ILIE bit in SCCR1 is set, an interrupt request is generated when the IDLE flag is set. The flag is cleared by reading SCSR and SCDR in sequence. IDLE is not set again until after at least one frame has been received (RDRF = 1). This prevents an extended idle interval from causing more than one interrupt.

## 9.4.3.8 Receiver Wake-Up

The receiver wake-up function allows a transmitting device to direct a transmission to a single receiver or to a group of receivers by sending an address frame at the start of a message. Hardware activates each receiver in a system under certain conditions. Resident software must process address information and enable or disable receiver operation.

A receiver is placed in wake-up mode by setting the RWU bit in SCCR1. While RWU is set, receiver status flags and interrupts are disabled. Although the CPU32 can clear RWU, it is normally cleared by hardware during wake-up.

The WAKE bit in SCCR1 determines which type of wake-up is used. When WAKE = 0, idle-line wake-up is selected. When WAKE = 1, address-mark wake-up is selected. Both types require a software-based device addressing and recognition scheme.

Idle-line wake-up allows a receiver to sleep until an idle line is detected. When an idle-line is detected, the receiver clears RWU and wakes up. The receiver waits for the first frame of the next transmission. The byte is received normally, transferred to the RDR, and the RDRF flag is set. If software does not recognize the address, it can set RWU and put the receiver back to sleep. For idle-line wake-up to work, there must be a minimum of one frame of idle line between transmissions. There must be no idle time between frames within a transmission.

Address-mark wake-up uses a special frame format to wake up the receiver. When the MSB of an address-mark frame is set, that frame contains address information. The first frame of each transmission must be an address frame. When the MSB of a frame is set, the receiver clears RWU and wakes up. The byte is received normally, transferred to the RDR, and the RDRF flag is set. If software does not recognize the address, it can set RWU and put the receiver back to sleep. Address-mark wake-up allows idle time between frames and eliminates idle time between transmissions. However, there is a loss of efficiency because of an additional bit-time per frame.

# 8.12.4 QADC Clock (QCLK) Generation

**Figure 8-8** is a block diagram of the clock subsystem. QCLK provides the timing for the A/D converter state machine which controls the timing of conversions. QCLK is also the input to a 17-stage binary divider which implements the periodic/interval timer. To obtain the specified analog conversion accuracy, the QCLK frequency (f<sub>QCLK</sub>) must be within the tolerance specified in **Table A-13**.

Before using the QADC, software must initialize the prescaler with values that put QCLK within a specified range. Though most applications initialize the prescaler once and do not change it, write operations to the prescaler fields are permitted.

#### **CAUTION**

A change in the prescaler value while a conversion is in progress is likely to corrupt the conversion result. Therefore, any prescaler write operation should be done only when both queues are disabled.

Figure 8-8 QADC Clock Subsystem Functions

To accommodate wide variations of the main MCU clock frequency  $f_{sys}$ , QCLK is generated by a programmable prescaler which divides the MCU system clock to a frequency within the specified QCLK tolerance range. The prescaler also allows the duty cycle of the QCLK waveform to be programmable.

The basic high phase of the QCLK waveform is selected with the PSH (prescaler clock high time) field in QACR0, and the basic low phase of QCLK with the PSL (prescaler clock low time) field. The duty cycle of QCLK can be further modified with the PSA (prescaler add a clock tick) bit in QACR0. The combination of the PSH and PSL parameters establishes the frequency of QCLK.

**Figure 8-8** shows that the prescaler is essentially a variable pulse width signal generator. A 5-bit down counter, clocked at the system clock rate, is used to create both the high phase and the low phase of the QCLK signal. At the beginning of the high phase, the 5-bit counter is loaded with the 5-bit PSH value. When the zero detector finds that the high phase is finished, QCLK is reset. A 3-bit comparator looks for a one's complement match with the 3-bit PSL value, which is the end of the low phase of QCLK. The PSA bit allows the QCLK high-to-low transition to be delayed by a half cycle of the input clock.

The following sequence summarizes the process of determining what values are to be put into the prescaler fields in QACR0:

- 1. Choose the system clock frequency  $f_{sys}$ .

- 2. Choose first-try values for PSH, PSL, and PSA, then skip to step 4.

- 3. Choose different values for PSH, PSL, and PSA.

- 4. If the QCLK high time is less than  $t_{PSH}$  (QADC clock duty cycle Minimum high phase time), return to step 3. Refer to **Table A-13** for more information on  $t_{PSH}$ . QCLK high time is determined by the following equation:

QCLK high time (in ns) =

$$\frac{1000 (1 + PSH + 0.5 PSA)}{f_{sys}(in MHz)}$$

where PSH = 0 to 31 and PSA = 0 or 1.

If QCLK low time is less than t<sub>PSL</sub> (QADC clock duty cycle – Minimum low phase time), return to step 3. Refer to **Table A-13** for more information on t<sub>PSL</sub>. QCLK low time is determined by the following equation:

QCLK low time (in ns) =

$$\frac{1000 (1 + PSL - 0.5 PSA)}{f_{SVS}(in MHz)}$$

where PSL = 0 to 7 and PSA = 0 or 1.

**Table 13-3 Message Buffer Codes for Transmit Buffers**

| RTR | Initial TX Code   | Description                                                                                                   | Code After<br>Successful<br>Transmission |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Х   | 1000              | Message buffer not ready for transmit.                                                                        | _                                        |

| 0   | 1100              | Data frame to be transmitted once, unconditionally.                                                           | 1000                                     |

| 1   | 1100              | Remote frame to be transmitted once, and message buffer becomes an RX message buffer for data frames.         | 0100                                     |

| 0   | 1010 <sup>1</sup> | Data frame to be transmitted only as a response to a remote frame, always.                                    | 1010                                     |

| 0   | 1110              | Data frame to be transmitted only once, unconditionally, and then only as a response to remote frame, always. | 1010                                     |

#### NOTES:

### 13.4.1.2 Fields for Extended Format Frames

**Table 13-4** describes the message buffer fields used only for extended identifier format frames.

## **Table 13-4 Extended Format Frames**

| Field                                   | Description                                                                                                                                                                 |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ID[28:18]/[17:15]                       | Contains the 14 most significant bits of the extended identifier, located in the ID HIGH word of the message buffer.                                                        |  |  |

| Substitute<br>Remote Request<br>(SRR)   | Contains a fixed recessive bit, used only in extended format. Should be set to one by the user for TX buffers. It will be stored as received on the CAN bus for RX buffers. |  |  |

| ID Extended<br>(IDE)                    | If extended format frame is used, this field should be set to one. If zero, standard format frame should be used.                                                           |  |  |

| ID[14:0]                                | Bits [14:0] of the extended identifier, located in the ID LOW word of the message buffer.                                                                                   |  |  |

| Remote<br>Transmission<br>Request (RTR) | This bit is located in the least significant bit of the ID LOW word of the message buffer; 0 = Data Frame, 1 = Remote Frame.                                                |  |  |

### 13.4.1.3 Fields for Standard Format Frames

**Table 13-5** describes the message buffer fields used only for standard identifier format frames.

<sup>1.</sup> When a matching remote request frame is detected, the code for such a message buffer is changed to be 1110

- If both STOP and SELFWAKE are set and a recessive to dominant edge immediately occurs on the CAN bus, the TouCAN may never set the STOPACK bit, and the STOP bit will be cleared.

- To prevent old frames from being sent when the TouCAN awakes from low-power stop mode via the self-wake mechanism, disable all transmit sources, including transmit buffers configured for remote request responses, before placing the TouCAN in low-power stop mode.

- If the TouCAN is in debug mode when the STOP bit is set, the TouCAN will assume that debug mode should be exited. As a result, it will try to synchronize with the CAN bus, and only then will it await the conditions required for entry into low-power stop mode.

- Unlike other modules, the TouCAN does not come out of reset in low-power stop mode. The basic TouCAN initialization procedure (see 13.5.2 TouCAN Initialization) should be executed before placing the module in low-power stop mode.

- If the TouCAN is in low-power stop mode with the self-wake mechanism engaged and is operating with a single system clock per time quantum, there can be extreme cases in which TouCAN wake-up on recessive to dominant edge may not conform to the CAN protocol. TouCAN synchronization will be shifted one time quantum from the wake-up event. This shift lasts until the next recessive to dominant edge, which resynchronizes the TouCAN to be in conformance with the CAN protocol. The same holds true when the TouCAN is in auto power save mode and awakens on a recessive to dominant edge.

#### 13.6.3 Auto Power Save Mode

Auto power save mode enables normal operation with optimized power savings. Once the auto power save (APS) bit in CANMCR is set, the TouCAN looks for a set of conditions in which there is no need for the clocks to be running. If these conditions are met, the TouCAN stops its clocks, thus saving power. The following conditions will activate auto power save mode.

- No RX/TX frame in progress.

- No transfer of RX/TX frames to and from a serial message buffer, and no TX frame awaiting transmission in any message buffer.

- No CPU32 access to the TouCAN module.

- The TouCAN is not in debug mode, low-power stop mode, or the bus off state.

While its clocks are stopped, if the TouCAN senses that any one of the aforementioned conditions is no longer true, it restarts its clocks. The TouCAN then continues to monitor these conditions and stops/restarts its clocks accordingly.

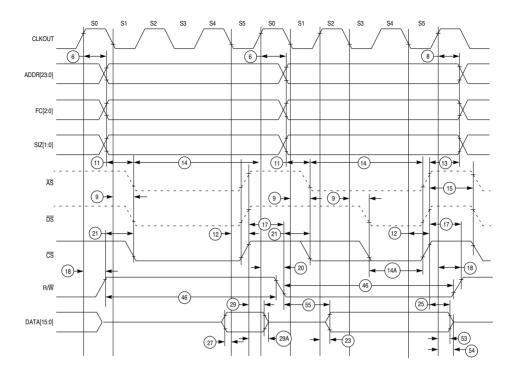

68300 CHIP SEL TIM

Figure A-11 Chip-Select Timing Diagram

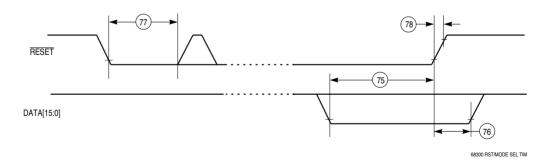

Figure A-12 Reset and Mode Select Timing Diagram

# Table A-13 QADC AC Electrical Characteristics (Operating)

(V<sub>DDI</sub> and V<sub>DDA</sub> = 5.0 Vdc  $\pm$  5%, V<sub>SSI</sub> and V<sub>SSA</sub> = 0Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>)

| Num | Parameter                                                                                                                                                                                                                                                                                          | Symbol            | Min          | Max         | Unit        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|-------------|-------------|

| 1   | QADC Clock (QCLK) Frequency <sup>1</sup>                                                                                                                                                                                                                                                           | f <sub>QCLK</sub> | 0.5          | 2.1         | MHz         |

| 2   | QADC Clock Duty Cycle <sup>2, 3</sup><br>High Phase Time ( $t_{PSL} \le t_{PSH}$ )                                                                                                                                                                                                                 | t <sub>PSH</sub>  | 500          | _           | ns          |

| 3   | Conversion Cycles <sup>4</sup>                                                                                                                                                                                                                                                                     | СС                | 18           | 32          | QCLK cycles |

| 4   | $\begin{aligned} & \text{Conversion Time}^{2,4,5} \\ & \text{f}_{QCLK} = 0.999 \text{ MHz}^6 \\ & \text{Min = CCW/IST = } \%00 \\ & \text{Max = CCW/IST = } \%11 \\ & \text{f}_{QCLK} = 2.097 \text{ MHz}^{1,7} \\ & \text{Min = CCW/IST = } \%00 \\ & \text{Max = CCW/IST = } \%11 \end{aligned}$ | <sup>t</sup> CONV | 18.0<br>8.58 | 32<br>15.24 | μѕ          |

| 5   | Stop Mode Recovery Time                                                                                                                                                                                                                                                                            | t <sub>SR</sub>   | _            | 10          | μs          |

#### NOTES:

- 1. Conversion characteristics vary with  $f_{QCLK}$  rate. Reduced conversion accuracy occurs at max  $f_{QCLK}$  rate.

- 2. Duty cycle must be as close as possible to 75% to achieve optimum performance.

- 3. Minimum applies to 1.0 MHz operation.

- 4. Assumes that short input sample time has been selected (IST = 0).

- 5. Assumes that  $f_{sys} = 20.97 \text{ MHz}$ .

- 6. Assumes f<sub>QCLK</sub> = 0.999 MHz, with clock prescaler values of:

QACR0: PSH = %01111, PSA = %1, PSL = 100)

CCW: BYP = %0

7. Assumes f<sub>xxxx</sub> = 2.097 MHz, with clock prescaler values of:

- 7. Assumes f<sub>QCLK</sub> = 2.097 MHz, with clock prescaler values of: QACR0: PSH = %00110, PSA = %1, PSL = 010)

# Table D-14 BYTE Field Bit Encoding

| BYTE[1:0] | Description |  |

|-----------|-------------|--|

| 00        | Disable     |  |

| 01        | Lower byte  |  |

| 10        | Upper byte  |  |

| 11        | Both bytes  |  |

# R/W[1:0]— Read/Write

This field causes a chip-select to be asserted only for a read, only for a write, or for both read and write. **Table D-15** shows the options.

Table D-15 Read/Write Field Bit Encoding

| R/W[1:0] | Description |  |

|----------|-------------|--|

| 00       | Disable     |  |

| 01       | Read only   |  |

| 10       | Write only  |  |

| 11       | Read/Write  |  |

#### STRB — Address Strobe/Data Strobe

This bit controls the timing for assertion of a chip-select in asynchronous mode. Selecting address strobe causes the chip-select to be asserted synchronized with address strobe. Selecting data strobe causes the chip-select to be asserted synchronized with data strobe.

0 = Address strobe

1 = Data strobe

# DSACK[3:0] — Data Strobe Acknowledge

This field specifies the source of  $\overline{DSACK}$  in asynchronous mode. It also allows the user to adjust bus timing with internal  $\overline{DSACK}$  generation by controlling the number of wait states that are inserted to optimize bus speed in a particular application. **Table D-16** shows the  $\overline{DSACK}[3:0]$  field encoding. The fast termination encoding (%1110) effectively corresponds to -1 wait states.

| Clock (QCLK) 8-14                            | test register (QTEST) 9-2                  |

|----------------------------------------------|--------------------------------------------|

| conversion characteristics (operating) A-30  | module configuration register (QSMCR) D-40 |

| electrical characteristics (operating)       | pin control registers 9-4                  |

| AC A-29                                      | port QS                                    |

| DC A-28                                      | data direction register (DDRQS) 9-4,       |

| features 3-2                                 | D-47                                       |

| maximum ratings A-27                         | data register (PORTQS) 9-4, D-46           |

| ~                                            | • , , ,                                    |

| pin functions diagram 8-3                    | pin assignment register (PQSPAR)           |

| registers                                    | D-47                                       |

| control register 0 (QACR0) 8-2, 8-28, D-31   | QSPI                                       |

| control register 1 (QACR0) 8-2, 8-28         | control register 0 (SPCR0) D-48            |

| control register 1 (QACR1) D-32              | control register 1 (SPCR1) D-50            |

| control register 2 (QACR0) 8-2, 8-28         | control register 2 (SPCR2) D-51            |

| control register 2 (QACR2) D-33              | control register 3 (SPCR3) D-52            |

| conversion command word table (CCW) D-37     | status register (SPSR) D-52                |

| interrupt register (QADCINT) 8-2, D-29       | receive data RAM (RR) D-53                 |

| module configuration register (QADCMCR) 8-2, | SCI                                        |

| 8-6, D-28                                    | control register 0 (SCCR0) D-42            |

|                                              | g , ,                                      |

| port                                         | control register 1 (SCCR1) D-43            |

| A data register (PORTQA) 8-2                 | data register (SCDR) D-46                  |

| B data register (PORTQB) 8-2                 | status register (SCSR) D-45                |

| data direction register (DDRQA) 8-2          | test register (QTEST) D-41                 |

| QA data direction register (DDRQA) D-30      | transmit data RAM (TR) D-54                |

| QA data register (PORTQA) D-30               | types 9-2                                  |

| QB data register (PORTQB) D-30               | SCI 9-21                                   |

| result word table D-39                       | operation 9-24                             |

| status register (QASR) 8-2, 8-28, D-35       | pins 9-24                                  |

| test register (QADCTEST) 8-2, D-29           | registers 9-21                             |

| QADCINT 8-2, D-29                            | QSMCR D-40                                 |

| QADCMCR 8-2, 8-6, D-28                       | QSPI 9-1, 9-5                              |

|                                              |                                            |

| QADCTEST 8-2, D-29                           | block diagram 9-5                          |

| QASR 8-2, 8-28, D-35                         | enable (SPE) D-50                          |

| QCLK 8-14, 8-23                              | finished flag (SPIF) D-53                  |

| frequency 8-24                               | initialization operation 9-10              |

| QDEC 11-10                                   | loop mode (LOOPQ) D-52                     |

| QILR 9-2, D-41                               | master operation flow 9-11                 |

| QIVR 9-2, D-41                               | operating modes 9-9                        |

| QOM 11-11                                    | master mode 9-9, 9-16                      |

| QS D-36                                      | wraparound mode 9-19                       |

| QSM                                          | slave mode 9-9, 9-19                       |

| address map 9-2, D-40                        | wraparound mode 9-20                       |

| block diagram 9-1                            | operation 9-8                              |

| features 3-2                                 | peripheral chip-selects 9-20               |

| general 9-1                                  | pins 9-8                                   |

| 9                                            | ·                                          |

| initialization sequence 9-30                 | RAM 9-7                                    |

| interrupts 9-3                               | command RAM 9-8                            |

| pin function 9-4, D-48                       | receive RAM 9-7                            |

| QSPI 9-5                                     | transmit RAM 9-7                           |

| operating modes 9-9                          | registers 9-6                              |

| operation 9-8                                | control registers 9-6                      |

| pins 9-8                                     | status register 9-7                        |

| RAM 9-7                                      | timing A-23                                |

| registers 9-6                                | master A-24                                |

| reference manual 9-1                         | slave A-25                                 |

| registers                                    | QTEST 9-2, D-41                            |

| command RAM (CR) D-54                        | Quadrature decode (QDEC) 11-10             |

| global registers 9-2                         | Quad-word data 4-4                         |

|                                              |                                            |

| interrupt                                    | Queue 8-16                                 |

| level register (QILR) 9-2, D-41              | pointers                                   |

| vector register (QIVR) 9-2, D-41             | completed queue pointer (CPTQP) 9-8        |

MC68336/376 USER'S MANUAL