Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | CPU32                                                                  |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 20MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 18                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | ·                                                                      |

| RAM Size                   | 7.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                          |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 160-BQFP                                                               |

| Supplier Device Package    | 160-QFP (28x28)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/sc68376bacab20 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE OF CONTENTS (Continued) Title

# Paragraph

Page

| 5.10.2 | Data Direction Registers | 5-64 |

|--------|--------------------------|------|

| 5.10.3 | Data Registers           | 5-64 |

| 5.11   | Factory Test             | 5-64 |

# SECTION 6 STANDBY RAM MODULE

| 6.1 | SRAM Register Block                  | 6-1 |

|-----|--------------------------------------|-----|

| 6.2 | SRAM Array Address Mapping           | 6-1 |

| 6.3 | SRAM Array Address Space Type        |     |

| 6.4 | Normal Access                        |     |

| 6.5 | Standby and Low-Power Stop Operation | 6-2 |

| 6.6 | Reset                                |     |

# SECTION 7 MASKED ROM MODULE

| 7.1 | MRM Register Block            | 7-1 |

|-----|-------------------------------|-----|

| 7.2 | MRM Array Address Mapping     |     |

| 7.3 | MRM Array Address Space Type  | 7-2 |

| 7.4 | Normal Access                 |     |

| 7.5 | Low-Power Stop Mode Operation | 7-3 |

| 7.6 | ROM Signature                 | 7-3 |

| 7.7 | Reset                         | 7-3 |

|     |                               |     |

# SECTION 8 QUEUED ANALOG-TO-DIGITAL CONVERTER MODULE

| 8.1     | General                         | 8-1 |

|---------|---------------------------------|-----|

| 8.2     | QADC Address Map                | 8-2 |

| 8.3     | QADC Registers                  | 8-2 |

| 8.4     | QADC Pin Functions              | 8-2 |

| 8.4.1   | Port A Pin Functions            | 8-3 |

| 8.4.1.1 | Port A Analog Input Pins        | 8-4 |

| 8.4.1.2 |                                 |     |

| 8.4.2   | Port B Pin Functions            | 8-4 |

| 8.4.2.1 | Port B Analog Input Pins        |     |

| 8.4.2.2 | Port B Digital Input Pins       | 8-4 |

| 8.4.3   | External Trigger Input Pins     | 8-5 |

| 8.4.4   | Multiplexed Address Output Pins | 8-5 |

| 8.4.5   | Multiplexed Analog Input Pins   | 8-5 |

| 8.4.6   | Voltage Reference Pins          | 8-5 |

| 8.4.7   | Dedicated Analog Supply Pins    | 8-6 |

| 8.4.8   | External Digital Supply Pin     | 8-6 |

| 8.4.9   | Digital Supply Pins             | 8-6 |

|         |                                 |     |

# LIST OF TABLES

# Table

# Title

Page

| 3-1  | MC68336/376 Pin Characteristics                   |      |

|------|---------------------------------------------------|------|

| 3-2  | MC68336/376 Output Driver Types                   | 3-8  |

| 3-3  | MC68336/376 Power Connections                     | 3-8  |

| 3-4  | MC68336/376 Signal Characteristics                | 3-9  |

| 3-5  | MC68336/376 Signal Functions                      | 3-11 |

| 4-1  | Unimplemented MC68020 Instructions                | 4-10 |

| 4-2  | Instruction Set Summary                           | 4-11 |

| 4-3  | Exception Vector Assignments                      | 4-16 |

| 4-4  | BDM Source Summary                                | 4-20 |

| 4-5  | Polling the BDM Entry Source                      |      |

| 4-6  | Background Mode Command Summary                   | 4-22 |

| 4-7  | CPU Generated Message Encoding                    | 4-25 |

| 5-1  | Show Cycle Enable Bits                            | 5-3  |

| 5-2  | Clock Control Multipliers                         |      |

| 5-3  | System Frequencies from 4.194 MHz Reference       | 5-10 |

| 5-4  | Bus Monitor Period                                |      |

| 5-5  | MODCLK Pin and SWP Bit During Reset               |      |

| 5-6  | Software Watchdog Ratio                           | 5-16 |

| 5-7  | MODCLK Pin and PTP Bit at Reset                   | 5-17 |

| 5-8  | Periodic Interrupt Priority                       | 5-18 |

| 5-9  | Size Signal Encoding                              | 5-22 |

| 5-10 | Address Space Encoding                            |      |

| 5-11 | Effect of DSACK Signals                           | 5-24 |

| 5-12 | Operand Alignment                                 | 5-26 |

| 5-13 | DSACK, BERR, and HALT Assertion Results           | 5-35 |

| 5-14 | Reset Source Summary                              | 5-41 |

| 5-15 | Reset Mode Selection                              |      |

| 5-16 | Module Pin Functions During Reset                 |      |

| 5-17 | SIM Pin Reset States                              | 5-47 |

| 5-18 | Chip-Select Pin Functions                         |      |

| 5-19 | Pin Assignment Field Encoding                     | 5-58 |

| 5-20 | Block Size Encoding                               | 5-59 |

| 5-21 | Chip-Select Base and Option Register Reset Values |      |

| 5-22 | CSBOOT Base and Option Register Reset Values      | 5-63 |

| 6-1  | SRAM Array Address Space Type                     | 6-2  |

| 7-1  | ROM Array Space Type                              |      |

| 7-2  | Wait States Field                                 | 7-2  |

| 8-1  | Multiplexed Analog Input Channels                 |      |

| 8-2  | Analog Input Channels                             |      |

| 8-3  | Queue 1 Priority Assertion                        |      |

| 8-4  | QADC Clock Programmability                        | 8-27 |

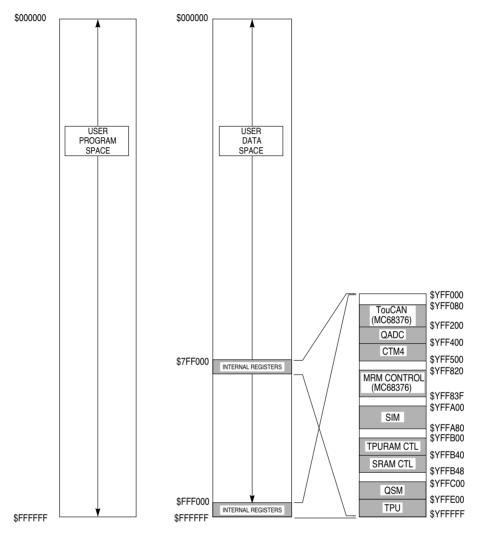

NOTES:

1. LOCATION OF THE MODULE CONTROL REGISTERS IS DETERMINED BY THE STATE OF THE MODULE MAPPING (MM) BIT IN THE SIM CONFIGURATION REGISTER. Y = M111, WHERE M IS THE STATE OF THE MM BIT.

2. UNUSED ADDRESSES WITHIN THE INTERNAL REGISTER BLOCK ARE MAPPED EXTERNALLY. "RESERVED" BLOCKS ARE NOT MAPPED EXTERNALLY.

3. SOME INTERNAL REGISTERS ARE NOT AVAILABLE IN USER SPACE.

336/376 USER P/D MAP

# 4.4 Virtual Memory

The full addressing range of the CPU32 on the MC68336/376 is 16 Mbytes in each of eight address spaces. Even though most systems implement a smaller physical memory, the system can be made to appear to have a full 16 Mbytes of memory available to each user program by using virtual memory techniques.

A system that supports virtual memory has a limited amount of high-speed physical memory that can be accessed directly by the processor and maintains an image of a much larger virtual memory on a secondary storage device. When the processor attempts to access a location in the virtual memory map that is not resident in physical memory, a page fault occurs. The access to that location is temporarily suspended while the necessary data is fetched from secondary storage and placed in physical memory. The suspended access is then restarted or continued.

The CPU32 uses instruction restart, which requires that only a small portion of the internal machine state be saved. After correcting the fault, the machine state is restored, and the instruction is fetched and started again. This process is completely transparent to the application program.

# 4.5 Addressing Modes

Addressing in the CPU32 is register-oriented. Most instructions allow the results of the specified operation to be placed either in a register or directly in memory. There is no need for extra instructions to store register contents in memory.

There are seven basic addressing modes:

- Register Direct

- Register Indirect

- Register Indirect with Index

- Program Counter Indirect with Displacement

- Program Counter Indirect with Index

- Absolute

- Immediate

The register indirect addressing modes include postincrement, predecrement, and offset capability. The program counter indirect mode also has index and offset capabilities. In addition to these addressing modes, many instructions implicitly specify the use of the status register, stack pointer, and/or program counter.

# 4.6 Processing States

The processor is always in one of four processing states: normal, exception, halted, or background. The normal processing state is associated with instruction execution; the bus is used to fetch instructions and operands and to store results.

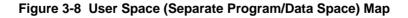

This additional  $\overline{BG}$  assertion allows external arbitration circuitry to select the next bus master before the current master has released the bus.

Refer to **Figure 5-15**, which shows bus arbitration for a single device. The flowchart shows BR negated at the same time BGACK is asserted.

Figure 5-15 Bus Arbitration Flowchart for Single Request

# 5.6.6.1 Show Cycles

The MCU normally performs internal data transfers without affecting the external bus, but it is possible to show these transfers during debugging.  $\overline{AS}$  is not asserted externally during show cycles.

Show cycles are controlled by SHEN[1:0] in SIMCR. This field is set to %00 by reset. When show cycles are disabled, the address bus, function codes, size, and read/write signals reflect internal bus activity, but  $\overline{AS}$  and  $\overline{DS}$  are not asserted externally and external data bus pins are in high-impedance state during internal accesses. Refer to **5.2.3 Show Internal Cycles** and the *SIM Reference Manual* (SIMRM/AD) for more information.

When show cycles are enabled,  $\overline{\text{DS}}$  is asserted externally during internal cycles, and internal data is driven out on the external data bus. Because internal cycles normally continue to run when the external bus is granted, one SHEN encoding halts internal bus activity while there is an external master.

- E. After arbitration, the interrupt acknowledge cycle is completed in one of the following ways:

- 1. When there is no contention (IARB = %0000), the spurious interrupt monitor asserts BERR, and the CPU32 generates the spurious interrupt vector number.

- 2. The dominant interrupt source (external or internal) supplies a vector number and DSACK signals appropriate to the access. The CPU32 acquires the vector number.

- 3. The AVEC signal is asserted (the signal can be asserted by the dominant external interrupt source or the pin can be tied low), and the CPU32 generates an autovector number corresponding to interrupt priority.

- 4. The bus monitor asserts BERR and the CPU32 generates the spurious interrupt vector number.

- F. The vector number is converted to a vector address.

- G. The content of the vector address is loaded into the PC and the processor transfers control to the exception handler routine.

# 5.8.5 Interrupt Acknowledge Bus Cycles

Interrupt acknowledge bus cycles are CPU32 space cycles that are generated during exception processing. For further information about the types of interrupt acknowledge bus cycles determined by AVEC or DSACK, refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** and the *SIM Reference Manual* (SIMRM/AD).

# 5.9 Chip-Selects

Typical microcontrollers require additional hardware to provide external chip-select and address decode signals. The MCU includes 12 programmable chip-select circuits that can provide 2 to 16 clock-cycle access to external memory and peripherals. Address block sizes of two Kbytes to one Mbyte can be selected. **Figure 5-19** is a diagram of a basic system that uses chip-selects.

tion to restart at the designated location. Reads of SPCR2 return the current value of the register, not of the buffer. Writing the same value into any control register except SPCR2 while the QSPI is enabled has no effect on QSPI operation.

# 9.3.1.2 Status Register

SPSR contains information concerning the current serial transmission. Only the QSPI can set the bits in this register. The CPU32 reads SPSR to obtain QSPI status information and writes SPSR to clear status flags.

# 9.3.2 QSPI RAM

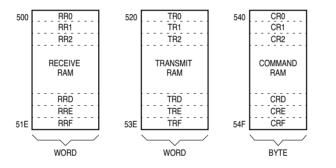

The QSPI contains an 80-byte block of dual-port access static RAM that can be accessed by both the QSPI and the CPU32. The RAM is divided into three segments: receive data RAM, transmit data RAM, and command data RAM. Receive data is information received from a serial device external to the MCU. Transmit data is information stored for transmission to an external device. Command control data defines transfer parameters. Refer to **Figure 9-3**, which shows RAM organization.

QSPI RAM MAP

Figure 9-3 QSPI RAM

# 9.3.2.1 Receive RAM

Data received by the QSPI is stored in this segment. The CPU32 reads this segment to retrieve data from the QSPI. Data stored in the receive RAM is right-justified. Unused bits in a receive queue entry are set to zero by the QSPI upon completion of the individual queue entry. The CPU32 can access the data using byte, word, or long-word addressing.

The CPTQP value in SPSR shows which queue entries have been executed. The CPU32 uses this information to determine which locations in receive RAM contain valid data before reading them.

# 9.3.2.2 Transmit RAM

Data that is to be transmitted by the QSPI is stored in this segment and must be written to transmit RAM in a right-justified format. The QSPI cannot modify information in the transmit RAM. The QSPI copies the information to its data serializer for transmission. Information remains in transmit RAM until overwritten.

MC68336/376 USER'S MANUAL QUEUED SERIAL MODULE

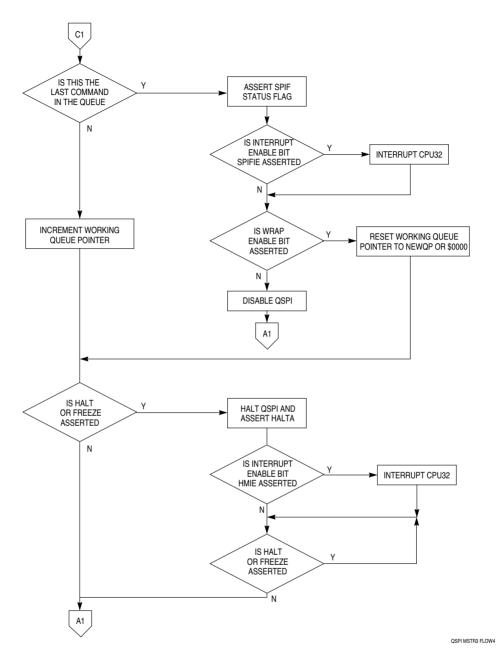

Figure 9-7 Flowchart of QSPI Master Operation (Part 3)

# 9.3.5.2 Master Wrap-Around Mode

Wrap-around mode is enabled by setting the WREN bit in SPCR2. The queue can wrap to pointer address \$0 or to the address pointed to by NEWQP, depending on the state of the WRTO bit in SPCR2.

In wrap-around mode, the QSPI cycles through the queue continuously, even while the QSPI is requesting interrupt service. SPE is not cleared when the last command in the queue is executed. New receive data overwrites previously received data in receive RAM. Each time the end of the queue is reached, the SPIF flag is set. SPIF is not automatically reset. If interrupt-driven QSPI service is used, the service routine must clear the SPIF bit to end the current interrupt request. Additional interrupt requests during servicing can be prevented by clearing SPIFIE, but SPIFIE is buffered. Clearing it does not end the current request.

Wrap-around mode is exited by clearing the WREN bit or by setting the HALT bit in SPCR3. Exiting wrap-around mode by clearing SPE is not recommended, as clearing SPE may abort a serial transfer in progress. The QSPI sets SPIF, clears SPE, and stops the first time it reaches the end of the queue after WREN is cleared. After HALT is set, the QSPI finishes the current transfer, then stops executing commands. After the QSPI stops, SPE can be cleared.

# 9.3.5.3 Slave Mode

Clearing the MSTR bit in SPCR0 selects slave mode operation. In slave mode, the QSPI is unable to initiate serial transfers. Transfers are initiated by an external SPI bus master. Slave mode is typically used on a multi-master SPI bus. Only one device can be bus master (operate in master mode) at any given time.

Before QSPI operation is initiated, QSM register PQSPAR must be written to assign necessary pins to the QSPI. The pins necessary for slave mode operation are MISO and MOSI, SCK, and PCS0/SS. MISO is used for serial data output in slave mode, and MOSI is used for serial data input. Either or both may be necessary, depending on the particular application. SCK is the serial clock input in slave mode. Assertion of the active-low slave select signal SS initiates slave mode operation.

Before slave mode operation is initiated, DDRQS must be written to direct data flow on the QSPI pins used. Configure the MOSI, SCK and PCS0/SS pins as inputs. The MISO pin must be configured as an output.

After pins are assigned and configured, write data to be transmitted into transmit RAM. Command RAM is not used in slave mode, and does not need to be initialized. Set the queue pointers, as appropriate.

When SPE is set and MSTR is clear, a low state on the slave select PCS0/SS pin begins slave mode operation at the address indicated by NEWQP. Data that is received is stored at the pointer address in receive RAM. Data is simultaneously loaded into the data serializer from the pointer address in transmit RAM and transmitted. Transfer is synchronized with the externally generated SCK. The CPHA and CPOL bits determine upon which SCK edge to latch incoming data from the MISO pin and to drive outgoing data from the MOSI pin.

data space accesses. The SUPV bit in QADCMCR designates the assignable space as supervisor or unrestricted.

Attempts to read supervisor-only data space when the CPU32 is not in supervisor mode causes a value of \$0000 to be returned. Attempts to read assignable data space when the CPU32 is not in supervisor mode and when the space is programmed as supervisor space, causes a value of \$FFFF to be returned. Attempts to write supervisor-only or supervisor-assigned data space when the CPU32 is in user mode has no effect.

The supervisor-only data space segment contains the QADC global registers, which include QADCMCR, QADCTEST, and QADCINT. The supervisor/unrestricted space designation for the CCW table, the result word table, and the remaining QADC registers is programmable. Refer to **D.5.1 QADC Module Configuration Register** for more information.

# 8.6.4 Interrupt Arbitration Priority

Each module that can request interrupts, including the QADC, has an interrupt arbitration number (IARB) field in its module configuration register. Each IARB field must have a different non-zero value. During an interrupt acknowledge cycle, IARB permits arbitration among simultaneous interrupts of the same priority level.

The reset value of IARB in the QADCMCR is \$0. Initialization software must set the IARB field to a non-zero value in order for QADC interrupts to be arbitrated. Refer to **D.5.1 QADC Module Configuration Register** for more information.

# 8.7 Test Register

The QADC test register (QADCTEST) is used only during factory testing of the MCU.

# 8.8 General-Purpose I/O Port Operation

QADC port pins, when used as general-purpose input, are conditioned by a synchronizer with an enable feature. The synchronizer is not enabled until the QADC decodes an IMB bus cycle which addresses the port data register to minimize the high-current effect of mid-level signals on the inputs used for analog signals. Digital input signals must meet the input low voltage ( $V_{IL}$ ) or input high voltage ( $V_{IH}$ ) specifications in **AP-PENDIX A ELECTRICAL CHARACTERISTICS**. If an analog input pin does not meet the digital input pin specifications when a digital port read operation occurs, an indeterminate state is read.

During a port data register read, the actual value of the pin is reported when its corresponding bit in the data direction register defines the pin to be an input (port A only). When the data direction bit specifies the pin to be an output, the content of the port data register is read. By reading the latch which drives the output pin, software instructions that read data, modify it, and write the result, like bit manipulation instructions, work correctly.

effect at the same time. Parameter RAM hardware supports coherent access of two adjacent 16-bit parameters. The host CPU must use a long-word operation to guarantee coherency.

# 11.3.6 Emulation Support

Although factory-programmed time functions can perform a wide variety of control tasks, they may not be ideal for all applications. The TPU provides emulation capability that allows the user to develop new time functions. Emulation mode is entered by setting the EMU bit in TPUMCR. In emulation mode, an auxiliary bus connection is made between TPURAM and the TPU, and access to TPURAM via the intermodule bus is disabled. A 9-bit address bus, a 32-bit data bus, and control lines transfer information between the modules. To ensure exact emulation, RAM module access timing remains consistent with access timing of the TPU microcode ROM control store.

To support changing TPU application requirements, Motorola has established a TPU function library. The function library is a collection of TPU functions written for easy assembly in combination with each other or with custom functions. Refer to Motorola Programming Note TPUPN00/D, *Using the TPU Function Library and TPU Emulation Mode* for information about developing custom functions and accessing the TPU function library. Refer to the *TPU Reference Manual* (TPURM/AD) and the Motorola TPU Literature Package (TPULITPAK/D) for more information about specific functions.

# 11.3.7 TPU Interrupts

Each of the TPU channels can generate an interrupt service request. Interrupts for each channel must be enabled by writing to the appropriate control bit in the channel interrupt enable register (CIER). The channel interrupt status register (CISR) contains one interrupt status flag per channel. Time functions set the flags. Setting a flag bit causes the TPU to make an interrupt service request if the corresponding channel interrupt enable bit is set and the interrupt request level is non-zero.

The value of the channel interrupt request level (CIRL) field in the TPU interrupt configuration register (TICR) determines the priority of all TPU interrupt service requests. CIRL values correspond to MCU interrupt request signals IRQ[7:1]. IRQ7 is the highest-priority request signal; IRQ1 has the lowest priority. Assigning a value of %111 to CIRL causes IRQ7 to be asserted when a TPU interrupt request is made; lower field values cause corresponding lower-priority interrupt request signals to be asserted. Assigning CIRL a value of %000 disables all interrupts.

The CPU32 recognizes only interrupt requests of a priority greater than the value contained in the interrupt priority (IP) mask in the status register. When the CPU32 acknowledges an interrupt request, the priority of the acknowledged interrupt is written to the IP mask and is driven out onto the IMB address lines.

When the IP mask value driven out on the address lines is the same as the CIRL value, the TPU contends for arbitration priority. The IARB field in TPUMCR contains the TPU arbitration number. Each module that can make an interrupt service request must be assigned a unique non-zero IARB value in order to implement an arbitration scheme.

# Table A-9 QSPI Timing

$(V_{DD} \text{ and } V_{DDSYN} = 5.0 \text{ Vdc} \pm 5\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H 200 \text{ pF load on all QSPI pins})^1$

| Num       | Function                                                                 | Symbol                             | Min                                               | Max                  | Unit                                 |

|-----------|--------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|----------------------|--------------------------------------|

| 1         | Operating Frequency<br>Master<br>Slave                                   | f <sub>QSPI</sub>                  | DC<br>DC                                          | 1/4<br>1/4           | f <sub>sys</sub><br>f <sub>sys</sub> |

| 2         | Cycle Time<br>Master<br>Slave                                            | t <sub>qcyc</sub>                  | 4 4                                               | 510<br>—             | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 3         | Enable Lead Time<br>Master<br>Slave                                      | t <sub>lead</sub>                  | 2<br>2                                            | 128<br>—             | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 4         | Enable Lag Time<br>Master<br>Slave                                       | t <sub>lag</sub>                   | 2                                                 | 1/2                  | SCK<br>t <sub>cyc</sub>              |

| 5         | Clock (SCK) High or Low Time<br>Master<br>Slave <sup>2</sup>             | t <sub>sw</sub>                    | 2 t <sub>cyc</sub> – 60<br>2 t <sub>cyc</sub> – n | 255 t <sub>cyc</sub> | ns<br>ns                             |

| 6         | Sequential Transfer Delay<br>Master<br>Slave (Does Not Require Deselect) | t <sub>td</sub>                    | 17<br>13                                          | 8192<br>—            | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 7         | Data Setup Time (Inputs)<br>Master<br>Slave                              | t <sub>su</sub>                    | 30<br>20                                          | _                    | ns<br>ns                             |

| 8         | Data Hold Time (Inputs)<br>Master<br>Slave                               | t <sub>hi</sub>                    | 0<br>20                                           |                      | ns<br>ns                             |

| 9         | Slave Access Time                                                        | ta                                 | -                                                 | 1                    | t <sub>cyc</sub>                     |

| 10        | Slave MISO Disable Time                                                  | t <sub>dis</sub>                   | —                                                 | 2                    | t <sub>cyc</sub>                     |

| 11        | Data Valid (after SCK Edge)<br>Master<br>Slave                           | t <sub>v</sub>                     |                                                   | 50<br>50             | ns<br>ns                             |

| 12        | Data Hold Time (Outputs)<br>Master<br>Slave                              | t <sub>ho</sub>                    | 0<br>0                                            |                      | ns<br>ns                             |

| 13        | Rise Time<br>Input<br>Output                                             | t <sub>ri</sub><br>t <sub>ro</sub> | _                                                 | 2<br>30              | μs<br>ns                             |

| 14<br>NOT | Fall Time<br>Input<br>Output                                             | t <sub>fi</sub><br>t <sub>fo</sub> | _                                                 | 2<br>30              | μs<br>ns                             |

NOTES:

1. All AC timing is shown with respect to 20%  $V_{\text{DD}}$  and 70%  $V_{\text{DD}}$  levels unless otherwise noted.

2. For high time, n = External SCK rise time; for low time, n = External SCK fall time.

| Part<br>Number | Package<br>Type | Frequency<br>(MHz) | TPU | Mask<br>ROM | Temperature    | Package<br>Order<br>Quantity | Order Number     |

|----------------|-----------------|--------------------|-----|-------------|----------------|------------------------------|------------------|

| MC68376        | 160-pin QFP     | 20.97 MHz          | А   | Blank       | –40 to +85 °C  | 2                            | SPMC68376BACFT20 |

|                |                 |                    |     |             |                | 24                           | MC68376BACFT20   |

|                |                 |                    |     |             |                | 120                          | MC68376BACFT20B1 |

|                |                 |                    |     |             | –40 to +105 °C | 2                            | SPMC68376BAVFT20 |

|                |                 |                    |     |             |                | 24                           | MC68376BAVFT20   |

|                |                 |                    |     |             |                | 120                          | MC68376BAVFT20B1 |

|                |                 |                    |     |             | –40 to +125 °C | 2                            | SPMC68376BAMFT20 |

|                |                 |                    |     |             |                | 24                           | MC68376BAMFT20   |

|                |                 |                    |     |             |                | 120                          | MC68376BAMFT20B1 |

|                |                 |                    | G   | Blank       | -40 to +85 °C  | 2                            | SPMC68376BGCFT20 |

|                |                 |                    |     |             |                | 24                           | MC68376BGCFT20   |

|                |                 |                    |     |             |                | 120                          | MC68376BGCFT20B1 |

|                |                 |                    |     |             | –40 to +105 °C | 2                            | SPMC68376BGVFT20 |

|                |                 |                    |     |             |                | 24                           | MC68376BGVFT20   |

|                |                 |                    |     |             |                | 120                          | MC68376BGVFT20B1 |

|                |                 |                    |     |             | –40 to +125 °C | 2                            | SPMC68376BGMFT20 |

|                |                 |                    |     |             |                | 24                           | MC68376BGMFT20   |

|                |                 |                    |     |             |                | 120                          | MC68376BGMFT20B1 |

# Table B-2 MC68376 Ordering Information

# **D.2.3 Clock Synthesizer Control Register**

| SYNC | CR — | Cloc | k Syr | thesi | zer C | ontro | l Reg | gister |   |   |                   |       |                   | \$YFF | A04   |

|------|------|------|-------|-------|-------|-------|-------|--------|---|---|-------------------|-------|-------------------|-------|-------|

| 15   | 14   | 13   | 12    | 11    | 10    | 9     | 8     | 7      | 6 | 5 | 4                 | 3     | 2                 | 1     | 0     |

| W    | Х    |      |       | Y[    | 5:0]  |       |       | EDIV   | 0 | 0 | RSVD <sup>1</sup> | SLOCK | RSVD <sup>1</sup> | STSIM | STEXT |

| RES  | SET: |      |       |       |       |       |       |        |   |   |                   |       |                   |       |       |

| 0    | 0    | 1    | 1     | 1     | 1     | 1     | 1     | 0      | 0 | 0 | 0                 | U     | 0                 | 0     | 0     |

NOTES:

1. Ensure that initialization software does not change the value of these bits. They should always be zero.

SYNCR determines system clock operating frequency and operation during low-power stop mode. Clock frequency is determined by SYNCR bit settings as follows:

$$f_{sys} = \frac{f_{ref}}{128} [4(Y+1)(2^{(2W+X)})]$$

W — Frequency Control (VCO)

This bit controls a prescaler tap in the synthesizer feedback loop. Setting this bit increases the VCO speed by a factor of four. VCO relock delay is required.

X — Frequency Control (Prescaler)

This bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting the bit doubles clock speed without changing the VCO speed. No VCO relock delay is required.

Y[5:0] — Frequency Control (Counter)

The Y field controls the modulus down counter in the synthesizer feedback loop, causing it to divide by a value of Y + 1. VCO relock delay is required.

EDIV — E Clock Divide Rate

0 = ECLK frequency is system clock divided by 8.

1 = ECLK frequency is system clock divided by 16.

ECLK is an external M6800 bus clock available on ADDR23.

SLOCK — Synthesizer Lock Flag

0 = VCO is enabled, but has not locked.

1 = VCO has locked on the desired frequency or VCO is disabled.

The MCU remains in reset until the synthesizer locks, but SLOCK does not indicate synthesizer lock status until after the user writes to SYNCR.

- STSIM Stop Mode SIM Clock

- 0 = When LPSTOP is executed, the SIM clock is driven from the crystal oscillator and the VCO is turned off to conserve power.

- 1 = When LPSTOP is executed, the SIM clock is driven from the VCO.

#### CH[15:0] — Encoded Host Sequence

The host sequence field selects the mode of operation for the time function selected on a given channel. The meaning of the host sequence bits depends on the time function specified.

### **D.8.9 Host Service Request Registers**

| HSSF       | HSSR0 — Host Service Request Register 0\$YFFE18  |      |        |       |       |       |                        |         |    |         |    |         |    |              |                 |

|------------|--------------------------------------------------|------|--------|-------|-------|-------|------------------------|---------|----|---------|----|---------|----|--------------|-----------------|

| 15         | 14                                               | 13   | 12     | 11    | 10    | 9     | 8                      | 7       | 6  | 5       | 4  | 3       | 2  | 1            | 0               |

| CH         | 15                                               | CH   | 14     | CH    | 13    | СН    | 12                     | CH      | 11 | СН      | 10 | CH      | 19 | CI           | 18              |

| RES        | SET:                                             |      |        |       |       |       |                        |         |    |         |    |         |    |              |                 |

| 0          | 0                                                | 0    | 0      | 0     | 0     | 0     | 0                      | 0       | 0  | 0       | 0  | 0       | 0  | 0            | 0               |

|            | HSSR1 — Host Service Request Register 1 \$YFFE1A |      |        |       |       |       |                        |         |    |         |    |         |    |              |                 |

| HSSF       | २१ —                                             | Host | Servi  | ce Re | quest | Regi  | ster 1                 |         |    |         |    |         |    | \$YFF        | E1A             |

| HSSF<br>15 | <b>R1 —</b>                                      | Host | Servie | ce Re | quest | Regis | ster 1<br><sup>8</sup> | 7       | 6  | 5       | 4  | 3       | 2  | <b>\$YFF</b> | <b>E1A</b><br>0 |

| 15         |                                                  | 13   |        | 11    | •     | 9     |                        | 7<br>Cł |    | 5<br>Cł |    | 3<br>Cł | 2  | 1            |                 |

| 15<br>Cł   | 14                                               | 13   | 12     | 11    | 10    | 9     | 8                      |         |    | -       |    | -       | 2  | 1            | 0               |

#### CH[15:0] — Encoded Type of Host Service

The host service request field selects the type of host service request for the time function selected on a given channel. The meaning of the host service request bits depends on the time function specified.

A host service request field cleared to %00 signals the host that service is completed by the microengine on that channel. The host can request service on a channel by writing the corresponding host service request field to one of three non-zero states. The CPU32 should monitor the host service request register until the TPU clears the service request to %00 before any parameters are changed or a new service request is issued to the channel

# **D.8.10 Channel Priority Registers**

| CPR                                        | <b>)</b> — C      | hann       | el Pric | ority R  | egist    | er O      |          |         |    |    |    |         |   | \$YFF           | E1C             |

|--------------------------------------------|-------------------|------------|---------|----------|----------|-----------|----------|---------|----|----|----|---------|---|-----------------|-----------------|

| 15                                         | 14                | 13         | 12      | 11       | 10       | 9         | 8        | 7       | 6  | 5  | 4  | 3       | 2 | 1               | 0               |

| CH                                         | CH 15 CH 14 CH 13 |            | СН      | 12       | СН       | 11        | СН       | 10      | Cł | 19 | CH | 18      |   |                 |                 |

| RES                                        | SET:              |            |         |          |          |           |          |         |    |    |    |         |   |                 |                 |

| 0                                          | 0                 | 0          | 0       | 0        | 0        | 0         | 0        | 0       | 0  | 0  | 0  | 0       | 0 | 0               | 0               |

|                                            |                   |            |         |          |          |           |          |         |    |    |    |         |   |                 |                 |

| CPR1 — Channel Priority Register 1 \$YFFE1 |                   |            |         |          |          |           |          |         |    |    |    |         |   |                 |                 |

|                                            |                   | nann       | el Pric | ority R  | egist    | er 1      |          |         |    |    |    |         |   | \$YFF           | E1E             |

| 15                                         | 14                | nann<br>13 |         | 11<br>11 | 10<br>10 | er 1<br>9 | 8        | 7       | 6  | 5  | 4  | 3       | 2 | <b>\$YFF</b>    | <b>Е1Е</b><br>0 |

| 15<br>Cł                                   | 14                | 13         |         | 11       | •        | 9         | 8<br>H 4 | 7<br>Cł | -  | -  | 4  | 3<br>Cł | 2 | \$YFF<br>1<br>ि | 0               |

| CI                                         | 14                | 13         | 12      | 11       | 10       | 9         | -        |         | -  | -  |    | -       | 2 | 1               | 0               |

# D.9 Standby RAM Module with TPU Emulation Capability (TPURAM)

**Table D-58** is the TPURAM address map. TPURAM responds to both program and data space accesses. The RASP bit in TRAMMCR determines whether the processor must be operating in supervisor mode to access the array. TPURAM control registers are accessible in supervisor mode only.

### Table D-58 TPURAM Address Map

| Address <sup>1</sup> | 15                                                | 0 |

|----------------------|---------------------------------------------------|---|

| \$YFFB00             | TPURAM Module Configuration Register (TRAMMCR)    |   |

| \$YFFB02             | TPURAM Test Register (TRAMTST)                    |   |

| \$YFFB04             | TPURAM Base Address and Status Register (TRAMBAR) |   |

| \$YFFB06-\$YFFB3F    | Not Used                                          |   |

NOTES:

1. Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

# **D.9.1 TPURAM Module Configuration Register**

| <b>TRAMMCR</b> — TPURAM Module Configuration Register | \$YFFB00 |

|-------------------------------------------------------|----------|

|                                                       |          |

| 15   | 14  | 13 | 12 | 11 | 10 | 9 | 8    | 7 |          | 0 |

|------|-----|----|----|----|----|---|------|---|----------|---|

| STOP | 0   | 0  | 0  | 0  | 0  | 0 | RASP |   | NOT USED |   |

| RES  | ET: |    |    |    |    |   |      |   |          |   |

| 0    | 0   | 0  | 0  | 0  | 0  | 0 | 1    |   |          |   |

STOP — Low-Power Stop Mode Enable

0 = TPURAM operates normally.

1 = TPURAM enters low-power stop mode.

This bit controls whether TPURAM operates normally or enters low-power stop mode. In low-power stop mode, the array retains its contents, but cannot be read or written.

#### RASP — TPURAM Array Space

0 = TPURAM is accessible in supervisor or user space.

1 = TPURAM is accessible in supervisor space only.

#### D.9.2 TPURAM Test Register

#### TRAMTST — TPURAM Test Register

Used for factory test only.

# **D.9.3 TPURAM Module Configuration Register**

|        | <b>TRAMBAR</b> — TPURAM Base Address and Status Register |            |            |            |            |            |            |            |            |            |            |            |   |   | \$YFFB04 |       |  |

|--------|----------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---|---|----------|-------|--|

|        | 15                                                       | 14         | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3 | 2 | 1        | 0     |  |

|        | ADDR<br>23                                               | ADDR<br>22 | ADDR<br>21 | ADDR<br>20 | ADDR<br>19 | ADDR<br>18 | ADDR<br>17 | ADDR<br>16 | ADDR<br>15 | ADDR<br>14 | ADDR<br>13 | ADDR<br>12 | 0 | 0 | 0        | RAMDS |  |

| RESET: |                                                          |            |            |            |            |            |            |            |            |            |            |            |   |   |          |       |  |

|        | 0                                                        | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0 | 0 | 0        | 0     |  |

#### **REGISTER SUMMARY**

**\$YFFB02**

**FDGEN D-62** FDGFP D-62 EDIV 5-12. D-8 EDPOL D-65 **EMPTY 13-4** EMU 11-5. 11-15. D-74 EMUL D-25 Emulation control (EMU) 11-15, D-74 mode control (EMUL) D-25 support 11-5 EN D-70 Encoded one of three channel priority levels (CH) D-80 time function for each channel (CHANNEL) D-78 type of host service (CH) D-79 Ending queue pointer (ENDQP) D-52 End-offrame (EOF) 13-16 queue condition 8-30 ENDQP 9-8, D-52 EOF 13-16 ERRINT D-96 ERRMSK D-89 Error conditions 9-28 counters 13-9 detection circuitry 9-2 interrupt (ERRINT) D-96 interrupt mask (ERRMSK) D-89 ESTAT D-94 ETRIG 8-5 Event flag (FLAG) D-63 Event timing 11-3 Exception instruction (RTE) 5-36 processing 4-15, 5-40 sequence 4-17 types of exceptions 4-17 vectors 4-15 exception vector assignments 4-16 vector 5-40, 11-6 EXOFF D-6 EXT D-9 Extended message format 13-1 frames 13-4 External bus arbitration 5-38 clock division (EDIV) D-8 division bit (EDIV) 5-12 operation during LPSTOP 5-12 signal (ECLK) 5-12 interface (EBI) 5-19 control signals 5-21 clock input timing diagram A-10 clock off (EXOFF) D-6 digital supply pin 8-6 multiplexing 8-10

reset (EXT) D-9 trigger pins 8-5 Externally input clock frequency D-14 multiplexed mode (MUX) D-31 EXTRST (external reset) 5-48

#### -F-

Factory test 5-64 FAR 4-22 Fast quadrature decode (FQD) 11-12 reference 5-4 circuit 5-5 termination cycles 5-26, 5-30 read cycle timing diagram A-13 write cvcle timing diagram A-14 Fast reference frequency D-14 Fault confinement state (FCS) 13-10, D-95 FC 5-22 FCS 13-10. D-95 FCSM 10-5 block diagram 10-5 clock sources 10-6 counter 10-6 external event counting 10-6 interrupts 10-6 registers 10-7 counter register (FCSMCNT) D-61 status/interrupt/control register (FCSMSIC) D-59 time base bus drivers 10-6 timing (electricals) A-31 FCSMCNT D-61 FCSMSIC D-59 FE 9-28, D-46 Final sample time 8-13 FLAG D-63, D-68 FORCA D-65 FORCB D-65 Force (FORCA/B) D-65 FORMERR D-94 f<sub>PWM</sub> 10-16 f<sub>OCLK</sub> 8-24 FQD 11-12 FQM 11-13 Frame 9-25 size 9-28 Frames overload 13-16 remote 13-15 Framing error (FE) flag 9-28, D-46 Free-running counter submodule. See FCSM 10-5 FREEZ ACK 13-16 FREEZE assertion response (FRZ) BIUSM 10-3, D-57 QADC 8-7, D-29

mask register (IMASK) D-96 module configuration register (CANMCR) D-85 receive buffer 14 mask registers (RX14MSKHI/LO) D-93 buffer 15 mask registers (RX15MSKHI/LO) D-93 global mask registers (RXGMSKLO/HI D-93 RX/TX error counter registers (RXECTR/TXEC-TR) D-97 test configuration register (CANTCR) D-88 special operating modes 13-16 auto power save mode 13-18 debug mode 13-16 low-power stop mode 13-17 transmit process 13-12 TPU A mask functions 11-6 discrete input/output (DIO) 11-6 input capture/input transition counter (ITC) 11-6 output compare (OC) 11-7 period /pw accumulator (PPWA) 11-9 measurement add transition detect (PMA) 11-8 missing transition detect (PMM) 11-8 position-synch pulse generator (PSP) 11-8 pulse width modulation (PWM) 11-7 quadrature decode (QDEC) 11-10 stepper motor (SM) 11-9 synch pw modulation (SPWM) 11-7 address map D-73 block diagram 11-1 components 11-2 features 3-2 FREEZE flag (TPUF) D-77 function library 11-5 G mask functions 11-10 brushless motor commutation (COMM) 11-12 fast quadrature decode (FQD) 11-12 frequency measurement (FQM) 11-13 hall effect decode (HALLD) 11-13 multichannel pulse width modulation (PCPWM) 11-11 new input capture/transition counter (NITC) 11-11 programmable time accumulator (PTA) 11-11 queued output match (QOM) 11-11 table stepper motor (TSM) 11-10 universal asynchronous receiver/transmitter (UART) 11-12 host interface 11-3 interrupts 11-5 microengine 11-3 operation 11-3 coherency 11-4 emulation support 11-5 event timing 11-3 interchannel communication 11-4

programmable channel service priority 11-4 overview 11-1 parameter RAM 11-3, D-80 address map D-81 registers channel function select registers (CFSR) D-78 interrupt enable register (CIER) 11-5, D-77 status register (CISR) 11-5, D-80 priority registers (CPR) D-79 decoded channel number register (DCNR) D-80 development support control register (DSCR) D-75 support status register (DSSR) D-76 host sequence registers (HSQR) D-78 service request registers (HSSR) D-79 link register (LR) D-80 module configuration register (TPUMCR) D-73 service grant latch register (SGLR) D-80 test configuration register (TCR) D-75 TPU interrupt configuration register (TICR) D-77 scheduler 11-3 time bases 11-2 timer channels 11-2 timing (electricals) A-26 TPU Reference Manual 11-3, 11-16, 11-17 TPUF D-77 TPUMCR 11-13, D-73 TPURAM address map D-82 array address mapping 12-1 base address (ADDR) D-83 space (RASP) D-82 features 3-2 general 12-1 operation normal 12-2 standby 12-2 privilege level 12-2 register block 12-1 registers base address and status register (TRAMBAR) D-82 module configuration register (TRAMMCR) D-82 test register (TRAMTST) D-82 reset 12-3 TPU microcode emulation 12-3 t<sub>PWMAX</sub> 10-17 t<sub>PWMIN</sub> 10-17 TR D-54 Trace enable field (T) D-3 on instruction execution 4-18 TRAMBAR 12-1, D-82 TRAMMCR 12-1. D-82

TRAMTST 12-1. D-82 Transfer length options 9-17 time 8-13 Transistion-sensitivity 5-51 Transmission complete (TC) flag 9-27 interrupt enable (TCIE) 9-27 Transmit /receive status (TX/RX) D-95 bit error (BITERR) D-94 complete bit (TC) D-45 interrupt enable (TCIE) D-44 data (TXD) pin 9-24 register empty (TDRE) flag 9-27, D-45 error status flag (TXWARN) D-95 interrupt enable (TIE) 9-27, D-44 pin configuration control (TXMODE) D-89 **RAM 9-7** Transmitter enable (TE) 9-26, D-44 Trigger event 8-30 TSC 5-49 TSM 11-10 T<sub>SR</sub> 8-6 TST D-9 TSTME 3-8, 3-10, 3-12 TSTMSR D-21 TSTRC D-21 TSTSC D-21 TSYNC D-90 TΧ Lenath 13-4 TX/RX D-95 TXD 9-24 **TXECTR D-97 TXMODE D-89 TXWARN D-95** Typical ratings (electrical) A-2

#### -U-

UART 11-12 Unimplemented instruction emulation 4-18 Universal asynchronous receiver/transmitter (UART) 11-12 User stack pointer (USP) 4-10 Using the TPU Function Library and TPU Emulation Mode 11-5 USP 4-10

#### -V-

V (overflow) flag 4-6, D-4 Variable pulse width signal generator (prescaler) 8-25 VBR 4-7, 4-15 V<sub>DD</sub> 3-8, 5-48, 6-1, 8-6, 12-1

ramp time 5-48 V<sub>DDA</sub> 3-8, 8-6 VDDA/2 8-15 V<sub>DDSYN</sub> 3-8, 5-48 VECT D-57 Vector base register (VBR) 3-14, 4-7, 4-15, 5-50 VIH 8-8 VIL 8-8 Virtual memory 4-9 Voltage controlled oscillator (VCO) frequency ramp time 5-48 reference pins 8-5 Vpd C-2 V<sub>RH</sub> 3-8, 8-5, 8-15, D-37 V<sub>RI</sub> 3-8, 8-5, 8-15, D-37 V<sub>SS</sub> 3-8, 8-6, 12-2 V<sub>SSA</sub> 3-8, 8-6 V<sub>STBY</sub> 3-8, 6-2, 12-1, 12-2

#### -W-

W bit D-8 WAIT 7-3. D-25 Wait states (WAIT) D-25 WAKE 9-29, D-44 Wake interrupt (WAKEINT) D-96 WAKEINT 13-17, D-96 WAKEMSK 13-17, D-86 Wakeup address mark (WAKE) 9-29, D-44 functions 9-2 interrupt mask (WAKEMSK) D-86 Wired-OR mode for QSPI pins (WOMQ) D-48 for SCI pins (WOMS) 9-26, D-43 mode (WOR) D-64 WOMQ D-48 WOMS 9-26, D-43 WOR D-64 Wrap enable (WREN) D-51 to (WRTO) D-51 Wraparound mode 9-6 master 9-19 slave 9-20 WREN D-51 Write cycle 5-29 flowchart 5-29 timing diagram A-12 WRTO D-51

#### -X-

X (extend) flag 4-6, D-4 bit in SYNCR D-8 XTRST (external reset) 5-41

MC68336/376 USER'S MANUAL MOTOROLA I-17