Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | CPU32                                                                  |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 18                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 7.5K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                          |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 160-BQFP                                                               |

| Supplier Device Package    | 160-QFP (28x28)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/sc68376bgvab25 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE OF CONTENTS (Continued) Title

# Paragraph

Page

| 9.1     | General                            | 9-1   |

|---------|------------------------------------|-------|

| 9.2     | QSM Registers and Address Map      | 9-2   |

| 9.2.1   | QSM Global Registers               |       |

| 9.2.1.1 | Low-Power Stop Operation           | 9-2   |

| 9.2.1.2 | Freeze Operation                   |       |

| 9.2.1.3 | QSM Interrupts                     |       |

| 9.2.2   | QSM Pin Control Registers          | 9-4   |

| 9.3     | Queued Serial Peripheral Interface |       |

| 9.3.1   | QSPI Registers                     |       |

| 9.3.1.1 | Control Registers                  |       |

| 9.3.1.2 | Status Register                    |       |

| 9.3.2   | QSPI RAM                           | 9-7   |

| 9.3.2.1 | Receive RAM                        | 9-7   |

| 9.3.2.2 | Transmit RAM                       | 9-7   |

| 9.3.2.3 | Command RAM                        | 9-8   |

| 9.3.3   | QSPI Pins                          | 9-8   |

| 9.3.4   | QSPI Operation                     | 9-8   |

| 9.3.5   | QSPI Operating Modes               |       |

| 9.3.5.1 | Master Mode                        |       |

| 9.3.5.2 | Master Wrap-Around Mode            | .9-19 |

| 9.3.5.3 | Slave Mode                         | .9-19 |

| 9.3.5.4 | Slave Wrap-Around Mode             | .9-20 |

| 9.3.6   | Peripheral Chip Selects            |       |

| 9.4     | Serial Communication Interface     | .9-21 |

| 9.4.1   | SCI Registers                      | .9-21 |

| 9.4.1.1 | Control Registers                  | .9-21 |

| 9.4.1.2 | Status Register                    | .9-24 |

| 9.4.1.3 | Data Register                      | .9-24 |

| 9.4.2   | SCI Pins                           | .9-24 |

| 9.4.3   | SCI Operation                      | .9-24 |

| 9.4.3.1 | Definition of Terms                | 9-25  |

| 9.4.3.2 | Serial Formats                     | 9-25  |

| 9.4.3.3 | Baud Clock                         | 9-25  |

| 9.4.3.4 | Parity Checking                    | .9-26 |

| 9.4.3.5 | Transmitter Operation              | .9-26 |

| 9.4.3.6 | Receiver Operation                 | .9-28 |

| 9.4.3.7 | Idle-Line Detection                | .9-28 |

| 9.4.3.8 | Receiver Wake-Up                   | 9-29  |

| 9.4.3.9 | Internal Loop                      |       |

| 9.5     | QSM Initialization                 | .9-30 |

# **SECTION 10 CONFIGURABLE TIMER MODULE 4**

MOTOROLA

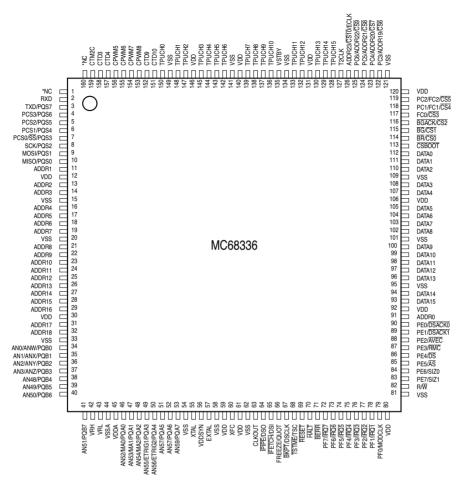

\*NOTE: MC68336 REVISION D AND LATER (F60K AND LATER MASK SETS) HAVE ASSIGNED PINS 1 AND 160 AS "NO CONNECT", TO ALLOW PIN COMPATIBILITY WITH THE MC68376. FOR REVISION C (D65J MASK SET) DEVICES, PIN 1 IS V<sub>SS</sub> AND PIN 160 IS V<sub>DD</sub>.

336 160-PIN QFP

### Figure 3-2 MC68336 Pin Assignments for 160-Pin Package

| Pin Mnemonic           | Output<br>Driver | Input<br>Synchronized | Input<br>Hysteresis | Discrete<br>I/O | Port<br>Designation |  |

|------------------------|------------------|-----------------------|---------------------|-----------------|---------------------|--|

| ADDR23/CS10/ECLK       | А                | Yes                   | No                  | 0               | _                   |  |

| ADDR[22:19]/CS[9:6]    | А                | Yes                   | No                  | 0               | PC[6:3]             |  |

| ADDR[18:0]             | А                | Yes                   | No                  | _               | _                   |  |

| AN[51:48]              | _                | Yes <sup>1</sup>      | Yes                 | I               | PQB[7:4]            |  |

| AN[3:0]/AN[w, x, y, z] | _                | Yes <sup>1</sup>      | Yes                 | I               | PQB[3:0]            |  |

| AN[59:57]              | Ba               | Yes                   | Yes                 | I/O             | PQA[7:5]            |  |

| AN[56:55]/ETRIG[2:1]   | Ba               | Yes                   | Yes                 | I/O             | PQA[4:3]            |  |

| AN[54:52]/MA[2:0]      | Ва               | Yes                   | Yes                 | I/O             | PQA[2:0]            |  |

| ĀS                     | В                | Yes                   | Yes                 | I/O             | PE5                 |  |

| AVEC                   | В                | Yes                   | No                  | I/O             | PE2                 |  |

| BERR                   | В                | Yes                   | No                  | —               | _                   |  |

| BG/CS1                 | В                | —                     | —                   | —               | —                   |  |

| BGACK/CS2              | В                | Yes                   | No                  | —               | —                   |  |

| BKPT/DSCLK             | _                | Yes                   | Yes                 | —               | —                   |  |

| BR/CS0                 | В                | Yes                   | No                  | 0               | —                   |  |

| CLKOUT                 | А                | —                     | —                   | _               | _                   |  |

| CANRX0 (MC68376 Only)  | _                | Yes                   | Yes                 | _               | _                   |  |

| CANTX0 (MC68376 Only)  | Во               | —                     | —                   | <u> </u>        | _                   |  |

| CSBOOT                 | В                | —                     | —                   | _               | _                   |  |

| CTD[10:9]/[4:3]        | А                | Yes                   | Yes                 | I/O             | _                   |  |

| CPWM[8:5]              | A                |                       | _                   | 0               |                     |  |

| CTM2C                  |                  | Yes                   | Yes                 | I               |                     |  |

| DATA[15:0]             | Aw               | Yes <sup>1</sup>      | No                  | _               | _                   |  |

| DS                     | В                | Yes                   | Yes                 | I/O             | PE4                 |  |

| DSACK[1:0]             | В                | Yes                   | No                  | I/O             | PE[1:0]             |  |

| EXTAL <sup>2</sup>     | _                | —                     | Special             | _               | _                   |  |

| FC[2:0]/CS[5:3]        | А                | Yes                   | No                  | 0               | PC[2:0]             |  |

| FREEZE/QUOT            | А                | —                     | —                   | —               | —                   |  |

| IPIPE/DSO              | А                | —                     | —                   | 0               | —                   |  |

| IFETCH/DSI             | А                | Yes                   | Yes                 | _               | —                   |  |

| HALT                   | Во               | Yes                   | No                  | _               | _                   |  |

| IRQ[7:1]               | В                | Yes                   | Yes                 | I/O             | PF[7:1]             |  |

| MISO                   | Во               | Yes <sup>1</sup>      | Yes                 | I/O             | PQS0                |  |

| MODCLK                 | В                | Yes <sup>1</sup>      | Yes                 | I/O             | PF0                 |  |

| MOSI                   | Во               | Yes <sup>1</sup>      | Yes                 | I/O             | PQS1                |  |

| PCS0/SS                | Во               | Yes <sup>1</sup>      | Yes                 | I/O             | PQS3                |  |

| PCS[3:1]               | Во               | Yes <sup>1</sup>      | Yes                 | I/O             | PQS[6:4]            |  |

| R/W                    | А                | Yes                   | No                  | _               | —                   |  |

| RESET                  | Во               | Yes                   | Yes                 | _               | _                   |  |

| RMC                    | В                | Yes                   | Yes                 | I/O             | PE3                 |  |

| RXD                    | _                | No                    | Yes                 | _               | —                   |  |

| SCK                    | Во               | Yes <sup>1</sup>      | Yes                 | I/O             | PQS2                |  |

### Table 3-1 MC68336/376 Pin Characteristics

# **3.5 Signal Descriptions**

The following tables define the MC68336/376 signals. **Table 3-4** shows signal origin, type, and active state. **Table 3-5** describes signal functions. Both tables are sorted alphabetically by mnemonic. MCU pins often have multiple functions. More than one description can apply to a pin.

| Signal Name           | MCU Module | Signal Type  | Active State |

|-----------------------|------------|--------------|--------------|

| ADDR[23:0]            | SIM        | Bus          | —            |

| AN[59:48]/[3:0]       | QADC       | Input        | _            |

| AN[w, x, y, z]        | QADC       | Input        | —            |

| ĀS                    | SIM        | Output       | 0            |

| AVEC                  | SIM        | Input        | 0            |

| BERR                  | SIM        | Input        | 0            |

| BG                    | SIM        | Output       | 0            |

| BGACK                 | SIM        | Input        | 0            |

| BKPT                  | CPU32      | Input        | 0            |

| BR                    | SIM        | Input        | 0            |

| CLKOUT                | SIM        | Output       | _            |

| CANRX0 (MC68376 Only) | TouCAN     | Input        | —            |

| CANTX0 (MC68376 Only) | TouCAN     | Output       | —            |

| CS[10:0]              | SIM        | Output       | 0            |

| CSBOOT                | SIM        | Output       | 0            |

| CPWM[8:5]             | CTM4       | Output       | _            |

| CTD[10:9]/[4:3]       | CTM4       | Input/Output | —            |

| CTM2C                 | CTM4       | Input        | —            |

| DATA[15:0]            | SIM        | Bus          | —            |

| DS                    | SIM        | Output       | 0            |

| DSACK[1:0]            | SIM        | Input        | 0            |

| DSCLK                 | CPU32      | Input        | Serial Clock |

| DSI                   | CPU32      | Input        | Serial Data  |

| DSO                   | CPU32      | Output       | Serial Data  |

| ECLK                  | SIM        | Output       | _            |

| ETRIG[2:1]            | QADC       | Input        | —            |

| EXTAL                 | SIM        | Input        | —            |

| FC[2:0]               | SIM        | Output       | —            |

| FREEZE                | SIM        | Output       | 1            |

| HALT                  | SIM        | Input/Output | 0            |

| IFETCH                | CPU32      | Output       | 0            |

| IPIPE                 | CPU32      | Output       | 0            |

| IRQ[7:1]              | SIM        | Input        | 0            |

| MA[2:0]               | QADC       | Output       | 1            |

| MISO                  | QSM        | Input/Output | _            |

| MODCLK                | SIM        | Input        | —            |

| MOSI                  | QSM        | Input/Output |              |

| PC[6:0]               | SIM        | Output       |              |

| PCS[3:0]              | QSM        | Input/Output |              |

| PE[7:0]               | SIM        | Input/Output | —            |

| PF[7:0]               | SIM        | Input/Output | —            |

# Table 3-4 MC68336/376 Signal Characteristics

1128A

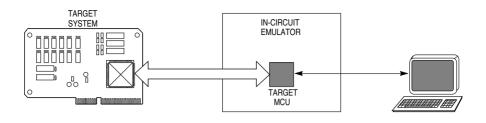

Figure 4-8 Common In-Circuit Emulator Diagram

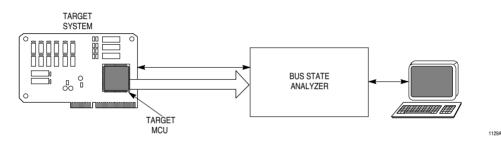

Figure 4-9 Bus State Analyzer Configuration

### 4.10.3 Enabling BDM

Accidentally entering BDM in a non-development environment can lock up the CPU32 when the serial command interface is not available. For this reason, BDM is enabled during reset via the breakpoint (BKPT) signal.

BDM operation is enabled when  $\overline{\text{BKPT}}$  is asserted (low), at the rising edge of  $\overline{\text{RESET}}$ . BDM remains enabled until the next system reset. A high  $\overline{\text{BKPT}}$  signal on the trailing edge of  $\overline{\text{RESET}}$  disables BDM.  $\overline{\text{BKPT}}$  is latched again on each rising transition of  $\overline{\text{RESET}}$ .  $\overline{\text{BKPT}}$  is synchronized internally, and must be held low for at least two clock cycles prior to negation of  $\overline{\text{RESET}}$ .

BDM enable logic must be designed with special care. If hold time on  $\overline{\text{BKPT}}$  (after the trailing edge of  $\overline{\text{RESET}}$ ) extends into the first bus cycle following reset, the bus cycle could inadvertently be tagged with a breakpoint. Refer to the *SIM Reference Manual* (SIMRM/AD) for timing information.

### 4.10.4 BDM Sources

When BDM is enabled, any of several sources can cause the transition from normal mode to BDM. These sources include external breakpoint hardware, the BGND instruction, a double bus fault, and internal peripheral breakpoints. If BDM is not enabled when an exception condition occurs, the exception is processed normally.

MC68336/376 USER'S MANUAL CENTRAL PROCESSOR UNIT

| BLKSZ[2:0] | Block Size | Address Lines Compared |

|------------|------------|------------------------|

| 000        | 2 Kbytes   | ADDR[23:11]            |

| 001        | 8 Kbytes   | ADDR[23:13]            |

| 010        | 16 Kbytes  | ADDR[23:14]            |

| 011        | 64 Kbytes  | ADDR[23:16]            |

| 100        | 128 Kbytes | ADDR[23:17]            |

| 101        | 256 Kbytes | ADDR[23:18]            |

| 110        | 512 Kbytes | ADDR[23:19]            |

| 111        | 1 Mbyte    | ADDR[23:20]            |

### Table 5-20 Block Size Encoding

The chip-select address compare logic uses only the most significant bits to match an address within a block. The value of the base address must be an integer multiple of the block size.

After reset, the MCU fetches the initialization routine from the address contained in the reset vector, located beginning at address \$000000 of program space. To support bootstrap operation from reset, the base address field in the boot chip-select base address register (CSBARBT) has a reset value of \$000, which corresponds to a base address of \$000000 and a block size of one Mbyte. A memory device containing the reset vector and initialization routine can be automatically enabled by CSBOOT after a reset. Refer to **5.9.4 Chip-Select Reset Operation** for more information.

### 5.9.1.3 Chip-Select Option Registers

Option register fields determine timing of and conditions for assertion of chip-select signals. To assert a chip-select signal, and to provide DSACK or autovector support, other constraints set by fields in the option register and in the base address register must also be satisfied. The following paragraphs summarize option register functions. Refer to **D.2.21 Chip-Select Option Registers** for register and bit field information.

The MODE bit determines whether chip-select assertion simulates an asynchronous bus cycle, or is synchronized to the M6800-type bus clock signal ECLK available on ADDR23. Refer to **5.3 System Clock** for more information on ECLK.

BYTE[1:0] controls bus allocation for chip-select transfers. Port size, set when a chipselect is enabled by a pin assignment register, affects signal assertion. When an 8-bit port is assigned, any BYTE field value other than %00 enables the chip-select signal. When a 16-bit port is assigned, however, BYTE field value determines when the chipselect is enabled. The BYTE fields for  $\overline{CS[10:0]}$  are cleared during reset. However, both bits in the boot ROM chip-select option register (CSORBT) BYTE field are set (%11) when the  $\overline{RESET}$  signal is released.

R/W[1:0] causes a chip-select signal to be asserted only for a read, only for a write, or for both read and write. Use this field in conjunction with the STRB bit to generate asynchronous control signals for external devices.

### 6.6 Reset

Reset places the SRAM in low-power stop mode, enables program space access, and clears the base address registers and the register lock bit. These actions make it possible to write a new base address into the registers.

When a synchronous reset occurs while a byte or word SRAM access is in progress, the access is completed. If reset occurs during the first word access of a long-word operation, only the first word access is completed. If reset occurs during the second word access of a long-word operation, the entire access is completed. Data being read from or written to the RAM may be corrupted by asynchronous reset. Refer to **5.7 Reset** for more information about resets.

### 9.2.2 QSM Pin Control Registers

The QSM uses nine pins. Eight of the pins can be used for serial communication or for parallel I/O. Clearing a bit in the port QS pin assignment register (PQSPAR) assigns the corresponding pin to general-purpose I/O; setting a bit assigns the pin to the QSPI. PQSPAR does not select I/O. In master mode, PQSPAR causes a bit to be assigned to the QSPI when SPE is set. In slave mode, the MISO pin, if assigned to the QSPI, remains under the control of the QSPI, regardless of the SPE bit. PQSPAR does not affect operation of the SCI.

The port QS data direction register (DDRQS) determines whether pins are inputs or outputs. Clearing a bit makes the corresponding pin an input; setting a bit makes the pin an output. DDRQS affects both QSPI function and I/O function. DDQS7 determines the direction of the TXD pin only when the SCI transmitter is disabled. When the SCI transmitter is enabled, the TXD pin is an output. PQSPAR and DDRQS are 8-bit registers located at the same word address. **Table 9-1** is a summary of QSM pin functions.

The port QS data register (PORTQS) latches I/O data. PORTQS writes drive pins defined as outputs. PORTQS reads return data present on the pins. To avoid driving undefined data, first write PORTQS, then configure DDRQS.

| QSM Pin           | Mode   | DDRQS Bit | Bit State                 | Pin Function                 |

|-------------------|--------|-----------|---------------------------|------------------------------|

| MISO Master DDQS0 |        | 0         | Serial data input to QSPI |                              |

|                   |        |           | 1                         | Disables data input          |

|                   | Slave  |           | 0                         | Disables data output         |

|                   |        |           | 1                         | Serial data output from QSPI |

| MOSI              | Master | DDQS1     | 0                         | Disables data output         |

|                   |        |           | 1                         | Serial data output from QSPI |

|                   | Slave  |           | 0                         | Serial data input to QSPI    |

|                   |        |           | 1                         | Disables data input          |

| SCK <sup>1</sup>  | Master | DDQS2     | _                         | Clock output from QSPI       |

|                   | Slave  |           | _                         | Clock input to QSPI          |

| PCS0/SS           | Master | DDQS3     | 0                         | Assertion causes mode fault  |

|                   |        |           | 1                         | Chip-select output           |

|                   | Slave  |           | 0                         | QSPI slave select input      |

|                   |        |           | 1                         | Disables slave select input  |

| PCS[1:3]          | Master | DDQS[4:6] | 0                         | Disables chip-select output  |

|                   |        |           | 1                         | Chip-select output           |

|                   | Slave  |           | 0                         | Inactive                     |

|                   |        |           | 1                         | Inactive                     |

| TXD <sup>2</sup>  | —      | DDQS7     | Х                         | Serial data output from SCI  |

| RXD               | —      | None      | NA                        | Serial data input to SCI     |

Table 9-1 Effect of DDRQS on QSM Pin Function

NOTES:

1. PQS2 is a digital I/O pin unless the SPI is enabled (SPE set in SPCR1), in which case it becomes the QSPI serial clock SCK.

2. PQS7 is a digital I/O pin unless the SCI transmitter is enabled (TE set in SCCR1), in which case it becomes the SCI serial data output TXD.

Normally, the SPI bus performs synchronous bidirectional transfers. The serial clock on the SPI bus master supplies the clock signal SCK to time the transfer of data. Four possible combinations of clock phase and polarity can be specified by the CPHA and CPOL bits in SPCR0.

Data is transferred with the most significant bit first. The number of bits transferred per command defaults to eight, but can be set to any value from eight to sixteen bits by writing a value into the BITSE field in command RAM.

Typically, SPI bus outputs are not open-drain unless multiple SPI masters are in the system. If needed, the WOMQ bit in SPCR0 can be set to provide wired-OR, opendrain outputs. An external pull-up resistor should be used on each output line. WOMQ affects all QSPI pins regardless of whether they are assigned to the QSPI or used as general-purpose I/O.

### 9.3.5.1 Master Mode

Setting the MSTR bit in SPCR0 selects master mode operation. In master mode, the QSPI can initiate serial transfers, but cannot respond to externally initiated transfers. When the slave select input of a device configured for master mode is asserted, a mode fault occurs.

Before QSPI operation begins, QSM register PQSPAR must be written to assign the necessary pins to the QSPI. The pins necessary for master mode operation are MISO and MOSI, SCK, and one or more of the chip-select pins. MISO is used for serial data input in master mode, and MOSI is used for serial data output. Either or both may be necessary, depending on the particular application. SCK is the serial clock output in master mode.

The PORTQS data register must next be written with values that make the PQS2/SCK and PQS[6:3]/PCS[3:0] outputs inactive when the QSPI completes a series of transfers. Pins allocated to the QSPI by PQSPAR are controlled by PORTQS when the QSPI is inactive. PORTQS I/O pins driven to states opposite those of the inactive QSPI signals can generate glitches that momentarily enable or partially clock a slave device. Thus, if a slave device operates with an inactive SCK state of logic one (CPOL = 1) and uses active low peripheral chip-select PCS0, the PQS[3:2] bits in PORTQS must be set to %11. If PQS[3:2] = %00, falling edges will appear on PQS2/SCK and PQS3/PCS0 as the QSPI relinquishes control of these pins and PORTQS drives them to logic zero from the inactive SCK and PCS0 states of logic one.

Before master mode operation is initiated, QSM register DDRQS is written last to direct the data flow on the QSPI pins used. Configure the SCK, MOSI and appropriate chip-select pins PCS[3:0] as outputs. The MISO pin must be configured as an input.

After pins are assigned and configured, write appropriate data to the command queue. If data is to be transmitted, write the data to transmit RAM. Initialize the queue pointers as appropriate.

Data transfer is synchronized with the internally-generated serial clock SCK. Control bits, CPHA and CPOL, in SPCR0, control clock phase and polarity. Combinations of CPHA and CPOL determine upon which SCK edge to drive outgoing data from the MOSI pin and to latch incoming data from the MISO pin.

QUEUED SERIAL MODULE

### 9.4.1.2 Status Register

SCSR contains flags that show SCI operating conditions. These flags are cleared either by SCI hardware or by reading SCSR, then reading or writing SCDR. A long-word read can consecutively access both SCSR and SCDR. This action clears receiver status flag bits that were set at the time of the read, but does not clear TDRE or TC flags.

If an internal SCI signal for setting a status bit comes after reading the asserted status bits, but before reading or writing SCDR, the newly set status bit is not cleared. SCSR must be read again with the bit set, and SCDR must be read or written before the status bit is cleared.

Reading either byte of SCSR causes all 16 bits to be accessed, and any status bit already set in either byte is cleared on a subsequent read or write of SCDR.

### 9.4.1.3 Data Register

SCDR contains two data registers at the same address. The receive data register (RDR) is a read-only register that contains data received by the SCI serial interface. Data enters the receive serial shifter and is transferred to RDR. The transmit data register (TDR) is a write-only register that contains data to be transmitted. Data is first written to TDR, then transferred to the transmit serial shifter, where additional format bits are added before transmission. R[7:0]/T[7:0] contain either the first eight data bits received when SCDR is read, or the first eight data bits to be transmitted when SCDR is written. R8/T8 are used when the SCI is configured for 9-bit operation. When it is configured for 8-bit operation, they have no meaning or effect.

### 9.4.2 SCI Pins

Two unidirectional pins, TXD (transmit data) and RXD (receive data), are associated with the SCI. TXD can be used by the SCI or for general-purpose I/O. Function is assigned by the port QS pin assignment register (PQSPAR). The receive data (RXD) pin is dedicated to the SCI. **Table 9-4** shows SCI pin function.

| Pin Names     | Mnemonics | Mode                                        | Function                                           |

|---------------|-----------|---------------------------------------------|----------------------------------------------------|

| Receive Data  | RXD       | Receiver disabled<br>Receiver enabled       | Not used<br>Serial data input to SCI               |

| Transmit Data | TXD       | Transmitter disabled<br>Transmitter enabled | General-purpose I/O<br>Serial data output from SCI |

### Table 9-4 SCI Pins

### 9.4.3 SCI Operation

SCI operation can be polled by means of status flags in SCSR, or interrupt-driven operation can be employed by the interrupt enable bits in SCCR1.

### 8.4.3 External Trigger Input Pins

The QADC has two external trigger pins (ETRIG[2:1]). The external trigger pins share two multifunction port A pins (PQA[4:3]), which are normally used as analog channel input pins. Each of the two external trigger pins is associated with one of the scan queues. When a queue is in external trigger mode, the corresponding external trigger pin is configured as a digital input and the software programmed input/output direction for that pin is ignored. Refer to **D.5.5 Port Data Direction Register** for more information.

### 8.4.4 Multiplexed Address Output Pins

In non-multiplexed mode, the 16 channel pins are connected to an internal multiplexer which routes the analog signals into the A/D converter.

In externally multiplexed mode, the QADC allows automatic channel selection through up to four external 1-of-8 multiplexer chips. The QADC provides a 3-bit multiplexed address output to the external mux chips to allow selection of one of eight inputs. The multiplexed address output signals MA[2:0] can be used as multiplex address output bits or as general-purpose I/O.

MA[2:0] are used as the address inputs for up to four 1-of-8 multiplexer chips (for example, the MC14051 and the MC74HC4051). Since MA[2:0] are digital outputs in multiplexed mode, the software programmed input/output direction for these pins in DDRQA is ignored.

### 8.4.5 Multiplexed Analog Input Pins

In externally multiplexed mode, four of the port B pins are redefined to each represent a group of eight input channels. Refer to **Table 8-1**.

The analog output of each external multiplexer chip is connected to one of the AN[w, x, y, z] inputs in order to convert a channel selected by the MA[2:0] multiplexed address outputs.

| Multiplexed Analog Input | Channels                            |

|--------------------------|-------------------------------------|

| ANw                      | Even numbered channels from 0 to 14 |

| ANx                      | Odd numbered channels from 1 to 15  |

| ANy                      | Even channels from 16 to 30         |

| ANz                      | Odd channels from 17 to 31          |

Table 8-1 Multiplexed Analog Input Channels

### 8.4.6 Voltage Reference Pins

$V_{RH}$  and  $V_{RL}$  are the dedicated input pins for the high and low reference voltages. Separating the reference inputs from the power supply pins allows for additional external filtering, which increases reference voltage precision and stability, and subsequently contributes to a higher degree of conversion accuracy. Refer to **Tables A-11** and **A-12** for more information.

When the QADC encounters a CCW with the pause bit set, the queue enters the paused state after completing the conversion specified in the CCW with the pause bit. The pause flag is set and a pause software interrupt may optionally be issued. The status of the queue is shown to be paused, indicating completion of a subqueue. The QADC then waits for another trigger event to again begin execution of the next subqueue.

### 8.12.2 Queue Boundary Conditions

A queue boundary condition occurs when one or more of the queue operating parameters is configured in a way that will inhibit queue execution. One such boundary condition is when the first CCW in a queue specified channel 63, the end-of-queue (EOQ) code. In this case, the queue becomes active and the first CCW is read. The EOQ code is recognized, the completion flag is set, and the queue becomes idle. A conversion is not performed.

A similar situation occurs when BQ2 (beginning of queue 2 pointer) is set beyond the end of the CCW table (between \$28 and \$3F) and a trigger event occurs for queue 2. The EOQ condition is recognized immediately, the completion flag is set, and the queue becomes idle. A conversion is not performed.

The QADC behaves the same way when BQ2 is set to CCW0 and a trigger event occurs for queue 1. After reading CCW0, the EOQ condition is recognized, the completion flag is set, and the queue becomes idle. A conversion is not performed.

Multiple EOQ conditions may be recognized simultaneously, but the QADC will not behave differently. One example is when BQ2 is set to CCW0, CCW0 contains the EOQ code, and a trigger event occurs for queue 1. The QADC will read CCW0 and recognize the queue 1 trigger event, detecting both as EOQ conditions. The completion flag will be set and queue 1 will become idle.

Boundary conditions also exist for combinations of pause and end-of-queue. One case is when a pause bit is in one CCW and an end-of-queue condition is in the next CCW. The conversion specified by the CCW with the pause bit set completes normally. The pause flag is set. However, since the end-of-queue condition is recognized, the completion flag is also set and the queue status becomes idle, not paused. Examples of this situation include:

- The pause bit is set in CCW5 and the channel 63 (EOQ) code is in CCW6.

- The pause bit is set in CCW27.

- During queue 1 operation, the pause bit is set in CCW14 and BQ2 points to CCW15.

Another pause and end-of-queue boundary condition occurs when the pause and an end-of-queue condition occur in the same CCW. Both the pause and end-of-queue conditions are recognized simultaneously. The end-of-queue condition has precedence so a conversion is not performed for the CCW and the pause flag is not set. The QADC sets the completion flag and the queue status becomes idle. Examples of this situation are:

### **Table 13-5 Standard Format Frames**

| Field                    | Description                                                                                                                                                                                                                                                                                                                         |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Bit Time<br>Stamp     | The ID LOW word, which is not needed for standard format, is used in a standard format buffer to store the 16-bit value of the free-running timer which is captured at the beginning of the identifier field of the frame on the CAN bus.                                                                                           |

| ID[28:18]                | Contains bits [28:18] of the identifier, located in the ID HIGH word of the message buffer. The four least significant bits in this register (corresponding to the IDE bit and ID[17:15] for an extended identifier message) must all be written as logic zeros to ensure proper operation of the TouCAN.                           |

| RTR                      | This bit is located in the ID HIGH word of the message buffer;<br>0 = data frame, 1 = remote frame.                                                                                                                                                                                                                                 |

| RTR/SRR Bit<br>Treatment | If the TouCAN transmits this bit as a one and receives it as a zero, an "arbitration loss" is indicat-<br>ed. If the TouCAN transmits this bit as a zero and is receives it as a one, a bit error is indicated.<br>If the TouCAN transmits a value and receives a matching response, a successful bit transmission<br>is indicated. |

### 13.4.1.4 Serial Message Buffers

To allow double buffering of messages, the TouCAN has two shadow buffers called serial message buffers. These two buffers are used by the TouCAN for buffering both received messages and messages to be transmitted. Only one serial message buffer is active at a time, and its function depends upon the operation of the TouCAN at that time. At no time does the user have access to or visibility of these two buffers.

### 13.4.1.5 Message Buffer Activation/Deactivation Mechanism

Each message buffer must be activated once it is configured for the desired operation by the user. A buffer is activated by writing the appropriate code to the control/status word for that buffer. Once the buffer is activated, it will begin participating in the normal transmit and receive processes.

Likewise, a buffer is deactivated by writing the appropriate deactivation code to the control/status word for that buffer. Deactivation of a buffer is typically done when the user desires to reconfigure the buffer, for example to change the buffer's function (RX to TX or TX to RX). Deactivation should also be done before changing a receive buffer's message identifier or before loading a new message to be transmitted into a transmit buffer.

For more details on activation and deactivation of message buffers, and the effects on message buffer operation, refer to **13.5 TouCAN Operation**.

### 13.4.1.6 Message Buffer Lock/Release/Busy Mechanism

In addition to the activation/deactivation mechanism, the TouCAN also utilizes a lock/ release/busy mechanism to assure data coherency during the receive process. The mechanism includes a lock status for each message buffer, and utilizes the two serial message buffers to facilitate frame transfers within the TouCAN.

Reading the control/status word of a receive message buffer triggers the lock for that buffer. While locked, a received message cannot be transferred into that buffer from one of the SMBs.

# Table A-6 AC Timing (Continued)

| Num | Characteristic                                                           | Symbol             | Min | Max | Unit             |

|-----|--------------------------------------------------------------------------|--------------------|-----|-----|------------------|

| 26  | Data Out Valid to DS, CS Asserted (Write)                                | t <sub>DVSA</sub>  | 10  | —   | ns               |

| 27  | Data In Valid to Clock Low (Data Setup) <sup>5</sup>                     | t <sub>DICL</sub>  | 5   | _   | ns               |

| 27A | Late BERR, HALT Asserted to Clock Low (Setup Time)                       | t <sub>BELCL</sub> | 15  | _   | ns               |

| 28  | AS, DS Negated to DSACK[1:0], BERR, HALT, AVEC Negated                   | t <sub>SNDN</sub>  | 0   | 60  | ns               |

| 29  | DS, CS Negated to Data In Invalid (Data In Hold) <sup>8</sup>            | t <sub>SNDI</sub>  | 0   | —   | ns               |

| 29A | DS, CS Negated to Data In High Impedance <sup>8, 9</sup>                 | t <sub>SHDI</sub>  | —   | 48  | ns               |

| 30  | CLKOUT Low to Data In Invalid (Fast Cycle Hold) <sup>8</sup>             | t <sub>CLDI</sub>  | 10  | _   | ns               |

| 30A | CLKOUT Low to Data In High Impedance <sup>8</sup>                        | t <sub>CLDH</sub>  | —   | 72  | ns               |

| 31  | DSACK[1:0] Asserted to Data In Valid <sup>10</sup>                       | t <sub>DADI</sub>  | —   | 46  | ns               |

| 33  | Clock Low to BG Asserted/Negated                                         | t <sub>CLBAN</sub> | —   | 23  | ns               |

| 35  | BR Asserted to BG Asserted (RMC Not Asserted) <sup>11</sup>              | t <sub>BRAGA</sub> | 1   | _   | t <sub>cyc</sub> |

| 37  | BGACK Asserted to BG Negated                                             | t <sub>GAGN</sub>  | 1   | 2   | t <sub>cyc</sub> |

| 39  | BG Width Negated                                                         | t <sub>GH</sub>    | 2   | _   | t <sub>cyc</sub> |

| 39A | BG Width Asserted                                                        | t <sub>GA</sub>    | 1   | _   | t <sub>cyc</sub> |

| 46  | R/W Width Asserted (Write or Read)                                       | t <sub>RWA</sub>   | 115 | —   | ns               |

| 46A | R/W Width Asserted (Fast Write or Read Cycle)                            | t <sub>RWAS</sub>  | 70  | —   | ns               |

| 47A | Asynchronous Input Setup Time<br>BR, BGACK, DSACK[1:0], BERR, AVEC, HALT | t <sub>AIST</sub>  | 5   | _   | ns               |

| 47B | Asynchronous Input Hold Time                                             | t <sub>AIHT</sub>  | 12  | —   | ns               |

| 48  | DSACK[1:0] Asserted to BERR, HALT Asserted <sup>12</sup>                 | t <sub>DABA</sub>  | —   | 30  | ns               |

| 53  | Data Out Hold from Clock High                                            | t <sub>DOCH</sub>  | 0   | —   | ns               |

| 54  | Clock High to Data Out High Impedance                                    | t <sub>CHDH</sub>  | —   | 23  | ns               |

| 55  | R/W Asserted to Data Bus Impedance Change                                | t <sub>RADC</sub>  | 32  | _   | ns               |

| 56  | RESET Pulse Width (Reset Instruction)                                    | t <sub>HRPW</sub>  | 512 | _   | t <sub>cyc</sub> |

| 57  | BERR Negated to HALT Negated (Rerun)                                     | t <sub>BNHN</sub>  | 0   | _   | ns               |

| 70  | Clock Low to Data Bus Driven (Show)                                      | t <sub>SCLDD</sub> | 0   | 23  | ns               |

| 71  | Data Setup Time to Clock Low (Show)                                      | t <sub>SCLDS</sub> | 10  | —   | ns               |

| 72  | Data Hold from Clock Low (Show)                                          | t <sub>SCLDH</sub> | 10  | —   | ns               |

| 73  | BKPT Input Setup Time                                                    | t <sub>BKST</sub>  | 10  | _   | ns               |

| 74  | BKPT Input Hold Time                                                     | t <sub>BKHT</sub>  | 10  | _   | ns               |

| 75  | Mode Select Setup Time                                                   | t <sub>MSS</sub>   | 20  | _   | t <sub>cyc</sub> |

$(V_{DD} \text{ and } V_{DDSYN} = 5.0 \text{ Vdc} \pm 5\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

This field only affects the response of chip-selects and does not affect interrupt recognition by the CPU32.

### AVEC — Autovector Enable

This field selects one of two methods of acquiring an interrupt vector during an interrupt acknowledge cycle. It is not usually used with a chip-select pin.

0 = External interrupt vector enabled

1 = Autovector enabled

If the chip select is configured to trigger on an interrupt acknowledge cycle (SPACE[1:0] = %00) and the  $\overline{AVEC}$  field is set to one, the chip-select automatically generates  $\overline{AVEC}$  in response to the interrupt acknowledge cycle. Otherwise, the vector must be supplied by the requesting device.

### **D.2.22 Master Shift Registers**

| <b>TSTMSRA</b> — Master Shift Register A<br>Used for factory test only.      | \$YFFA30 |

|------------------------------------------------------------------------------|----------|

| <b>TSTMSRB</b> — Master Shift Register B<br>Used for factory test only.      | \$YFFA32 |

| D.2.23 Test Module Shift Count Register                                      |          |

| <b>TSTSC</b> — Test Module Shift Count<br>Used for factory test only.        | \$YFFA34 |

| D.2.24 Test Module Repetition Count Register                                 |          |

| <b>TSTRC</b> — Test Module Repetition Count<br>Used for factory test only.   | \$YFFA36 |

| D.2.25 Test Submodule Control Register                                       |          |

| <b>CREG</b> — Test Submodule Control Register<br>Used for factory test only. | \$YFFA38 |

| D.2.26 Distributed Register                                                  |          |

| <b>DREG</b> — Distributed Register<br>Used for factory test only.            | \$YFFA3A |

### SCBR[12:0] - SCI Baud Rate

SCI baud rate is programmed by writing a 13-bit value to this field. Writing a value of zero to SCBR disables the baud rate generator. Baud clock rate is calculated as follows:

SCI Baud Rate =

$$\frac{f_{sys}}{32 \times SCBR[12:0]}$$

$$SCBR[12:0] = \frac{f_{sys}}{32 \times SCI Baud Rate Desired}$$

where SCBR[12:0] is in the range of 1 to 8191.

### D.6.6 SCI Control Register 1

| SCCR1 - | SCI Control | Register 1 |

|---------|-------------|------------|

|---------|-------------|------------|

# \$YFFC0A

| 15     | 14    | 13   | 12  | 11 | 10 | 9 | 8    | 7   | 6    | 5   | 4    | 3  | 2  | 1   | 0   |

|--------|-------|------|-----|----|----|---|------|-----|------|-----|------|----|----|-----|-----|

| 0      | LOOPS | WOMS | ILT | PT | PE | М | WAKE | TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

| RESET: |       |      |     |    |    | • |      |     |      |     |      |    |    |     |     |

| 0      | 0     | 0    | 0   | 0  | 0  | 0 | 0    | 0   | 0    | 0   | 0    | 0  | 0  | 0   | 0   |

SCCR1 contains SCI configuration parameters, including transmitter and receiver enable bits, interrupt enable bits, and operating mode enable bits. SCCR0 can be read or written at any time. The SCI can modify the RWU bit under certain circumstances. Changing the value of SCCR1 bits during a transfer operation can disrupt the transfer.

Bit 15 — Not Implemented

- LOOPS Loop Mode

- 0 = Normal SCI operation, no looping, feedback path disabled.

- 1 = Test SCI operation, looping, feedback path enabled.

### WOMS — Wired-OR Mode for SCI Pins

- 0 = If configured as an output, TXD is a normal CMOS output.

- 1 = If configured as an output, TXD is an open-drain output.

### ILT — Idle-Line Detect Type

0 = Short idle-line detect (start count on first one).

- 1 = Long idle-line detect (start count on first one after stop bit(s)).

- PT Parity Type

- 0 = Even parity

- 1 = Odd parity

- PE Parity Enable

- 0 = SCI parity disabled.

- 1 = SCI parity enabled.

MC68336/376 USER'S MANUAL **REGISTER SUMMARY**

### BITS[3:0] — Bits Per Transfer

In master mode, when BITSE is set in a command RAM byte, BITS[3:0] determines the number of data bits transferred. When BITSE is cleared, eight bits are transferred. Reserved values default to eight bits. In slave mode, the command RAM is not used and the setting of BITSE has no effect on QSPI transfers. Instead, the BITS[3:0] field determines the number of bits the QSPI will receive during each transfer before storing the received data.

Table D-34 shows the number of bits per transfer.

| BITS[3:0] | Bits per Transfer |

|-----------|-------------------|

| 0000      | 16                |

| 0001      | Reserved          |

| 0010      | Reserved          |

| 0011      | Reserved          |

| 0100      | Reserved          |

| 0101      | Reserved          |

| 0110      | Reserved          |

| 0111      | Reserved          |

| 1000      | 8                 |

| 1001      | 9                 |

| 1010      | 10                |

| 1011      | 11                |

| 1100      | 12                |

| 1101      | 13                |

| 1110      | 14                |

| 1111      | 15                |

### Table D-34 Bits Per Transfer

CPOL — Clock Polarity

0 = The inactive state of SCK is logic zero.

1 = The inactive state of SCK is logic one.

CPOL is used to determine the inactive state of the serial clock (SCK). It is used with CPHA to produce a desired clock/data relationship between master and slave devices.

### CPHA — Clock Phase

- 0 = Data is captured on the leading edge of SCK and changed on the trailing edge of SCK.

- 1 = Data is changed on the leading edge of SCK and captured on the trailing edge of SCK

CPHA determines which edge of SCK causes data to change and which edge causes data to be captured. CPHA is used with CPOL to produce a desired clock/data relationship between master and slave devices.

### SPBR[7:0] — Serial Clock Baud Rate

The QSPI uses a modulus counter to derive the SCK baud rate from the MCU system clock. Baud rate is selected by writing a value from 2 to 255 into SPBR[7:0]. The following equation determines the SCK baud rate:

#### CHBK — Channel Register Breakpoint Flag

CHBK is asserted if a breakpoint occurs because of a CHAN register match with the CHAN register breakpoint register. CHBK is negated when the BKPT flag is cleared.

### SRBK — Service Request Breakpoint Flag

SRBK is asserted if a breakpoint occurs because of any of the service request latches being asserted along with their corresponding enable flag in the development support control register. SRBK is negated when the BKPT flag is cleared.

### TPUF — TPU FREEZE Flag

TPUF is set whenever the TPU is in a halted state as a result of FREEZE being asserted. This flag is automatically negated when the TPU exits the halted state because of FREEZE being negated.

#### D.8.5 TPU Interrupt Configuration Register

| <b>TICR</b> — TPU Interrupt Configuration Register\$YFFE08 |          |    |           |   |   |      |        |   |          |   |  |  |

|------------------------------------------------------------|----------|----|-----------|---|---|------|--------|---|----------|---|--|--|

|                                                            | 15       | 10 | 9         | 8 | 7 | 6    | 5      | 4 | 3        | 3 |  |  |

|                                                            | NOT USED |    | CIRL[2:0] |   |   | CIBV | /[3:0] |   | NOT USED |   |  |  |

| _                                                          | RESET:   |    |           |   |   |      |        |   |          |   |  |  |

|                                                            |          | 0  | 0         | 0 | 0 | 0    | 0      | 0 |          |   |  |  |

#### CIRL[2:0] — Channel Interrupt Request Level

This three-bit field specifies the interrupt request level for all channels. Level seven for this field indicates a non-maskable interrupt; level zero indicates that all channel interrupts are disabled.

### CIBV[3:0] — Channel Interrupt Base Vector

The TPU is assigned 16 unique interrupt vector numbers, one vector number for each channel. The CIBV field specifies the most significant nibble of all 16 TPU channel interrupt vector numbers. The lower nibble of the TPU interrupt vector number is determined by the channel number on which the interrupt occurs.

### **D.8.6 Channel Interrupt Enable Register**

| CIER — Channel Interrupt Enable Register\$YFFE0A |       |       |       |       |       |      |      |      |      |      |      |      |      | E0A  |      |

|--------------------------------------------------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 15                                               | 14    | 13    | 12    | 11    | 10    | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| CH 15                                            | CH 14 | CH 13 | CH 12 | CH 11 | CH 10 | CH 9 | CH 8 | CH 7 | CH 6 | CH 5 | CH 4 | CH 3 | CH 2 | CH 1 | CH 0 |

| RES                                              | SET:  |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0                                                | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### CH[15:0] — Channel Interrupt Enable/Disable

0 = Channel interrupts disabled

1 = Channel interrupts enabled

register boot ROM (CSORBT) D-18 registers (CSOR) 5-57, 5-59, D-18 reset values 5-63 pin assignment registers (CSPAR) 5-57, D-15 field encoding 5-58. D-16 pin assignments D-16 reset operation 5-62 signals for interrupt acknowledge 5-61 timing diagram A-18 CIBV D-77 **CIE1 D-32 CIE2 D-33** CIER 11-15, D-77 CIRL D-77 CISR 11-13, 11-15, D-80 Clear (definition) 2-8 CLK D-60, D-62, D-70 CLKOUT 5-26, 5-41 output timing diagram A-10 CLKRST (clock reset) 5-41 CLKS D-75 Clock block diagram 8-24 control multipliers 5-8 timing (electricals) A-3 generation 8-24 input pin status (FCSM) D-60 input pin status (MCSM) D-62 mode pin (MODCLK) 5-44 selection 5-44 output (CLKOUT) 5-26 phase (CPHA) D-49 polarity (CPOL) D-49 rate selection (CLK) field D-70 synthesizer control register (SYNCR) D-8 operation 5-5 Code 13-4 COF D-59. D-61 Coherency 8-6, 8-22, 11-4 COMM 11-12 Command RAM 9-8 word pointer (CWP) D-36 Common in-circuit emulator 4-19 Comparator 8-16 Completed queue pointer (CPTQP) D-53 Condition code register (CCR) 4-6, 11-5 CONT D-54 Contention 5-52 Continue (CONT) D-54 Continuous transfer mode 9-6 Conventions 2-8 Conversion command word table (CCW) 8-1, 8-16, 8-28 cycle times 8-13

stages 8-30 Counter clock select (CLK) field FCSM D-60 MCSM D-62 overflow flag (COF) bit D-59. D-61 prescaler submodule. See CPSM 10-4 CPCR D-58 CPHA 9-16, D-49 CPOL 9-16, D-49 **CPR D-79 CPSM 10-4** block diagram 10-4 registers 10-5 control register (CPCR) D-58 test register (CPTR) D-59 CPTQP 9-8, D-53 CPTR D-59 CPU space address encoding 5-31 cycles 5-30 encoding for interrupt acknowledge 5-61 CPU32 5-40 address registers/address organization in 4-5 addressing modes 4-9 block diagram 4-2 data registers 4-4 data organization 4-5 development support 4-17 exception processing 4-15 features 3-1 generated message encoding 4-25 instructions 4-10 LPSTOP 4-14 MOVEC 4-7 MOVES 4-7 RESET 5-41 special control instructions 4-14 table lookup and interpolate (TBL) 4-14 umimplemented MC68020 instructions 4-10 loop mode 4-15 memory organization 4-7 processing states 4-9 register mnemonics 2-2 model 4-3, D-2 registers 4-2 alternate function code registers (SFC/DFC) 4-7 condition code register (CCR) 4-6, D-3 control registers 4-6 program counter (PC) 4-1 stack pointer (SP) 4-1 status register (SR) 4-6, D-3 vector base register (VBR) 4-7 virtual memory 4-9 CPU32 Reference Manual 4-1 CR D-54 CRCERR D-94 CREG D-21

end queue pointer (ENDQP) 9-8 new queue pointer (NEWQP) 9-8 status (QS) D-36 Queue 1 completion flag (CF1) D-35 interrupt enable (CIE1) D-32 interrupt level (IRLQ1) D-29 operating mode (MQ1) D-32 pause flag (PF1) D-35 interrupt enable (PIE1) D-32 single-scan enable (SSE1) D-32 trigger overrun (TOR1) D-35 Queue 2 completion flag (CF2) D-35 interrupt enable (CIE2) D-33 interrupt level (IRLQ2) D-29 operating mode (MQ2) D-33 pause flag (PF2) D-35 interrupt enable (PIE2) D-33 resume (RES) D-34 single-scan enable bit (SSE2) D-33 trigger overrun (TOR2) D-36 Queued analog-to-digital converter. See QADC 8-1 output match (QOM) 11-11 serial module (QSM). See QSM 9-1 peripheral interface (QSPI) 9-1, 9-5

#### -R-

R/W 5-22, 5-27 field 5-59, D-19 RAF D-45 RAM array disable (RAMDS) D-83 space (RASP) D-22 base address lock (RLCK) bit D-22 RAMBAH 6-1. D-23 RAMBAL 6-1, D-23 RAMDS 12-1. D-83 RAMMCR 6-1. D-22 RAMTST 6-1. D-23 RASP 6-1, D-22, D-82 encoding D-22 RDR 9-24 RDRF 9-28. D-45 RE 9-28, D-44 Read /write signal (R/W) 5-22 cycle 5-28 flowchart 5-28 timing diagram A-11 system register command (RSREG) 4-20 Receive

data (RXD) pin 9-24 register full (RDRF) D-45 error status flag (RXWARN) D-95 pin configuration control (RXMODE) D-89 RAM 9-7 time sample clock (RT) 9-26, 9-28 Receiver active (RAF) D-45 data register (RDRF) flag 9-28 enable (RE) 9-28, D-44 interrupt enable (RIE) D-44 wakeup (RWU) 9-29, D-44 Reception of transmitted frames 13-13 Remote frames 13-15 transmission request (RTR) 13-4, 13-5 RES 8-31, D-34 Reserved channel number D-37 mode 8-20 RESET 4-19, 5-40, 5-42, 5-46, 5-47 Reset control logic in SIM 5-40 exception processing 5-40 mode selection timing diagram A-18 use in determining SIM configuration 5-41 module pin function out of reset 5-45 operation in SIM 5-40 power-on 5-48 processing summary 5-50 source summary in SIM 5-41 states of pins assigned to other MCU modules 5-47 status register (RSR) 5-14, 5-50, D-9 timina 5-47 Resistor-divider chain 8-15 Resolution time 8-13 Result word table 8-1, 8-16, 8-31 Resynchronization jump width (RJW) bit field D-91 Retry operation 5-37 RIE D-44 Right justified, unsigned result word table (RJURR) D-39 **RJURR D-39** RJW 13-11, D-91 RLCK 6-1, D-22 RMC 3-7, 3-10, 3-12, 5-38 ROM array space (ASPC) D-25 ROMBAH 7-1, D-26 ROMBAL 7-1, D-26 ROMBS 7-1 ROMBS0-3 D-27 **RPC 4-22 RR D-53** RS-232C terminal C-2 RSIGHI 7-1, 7-3, D-26 RSIGLO 7-1, 7-3, D-26 RSR 5-14, D-9 **RSREG 4-20** RT 9-28