Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | CPU32                                                                   |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                               |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 7.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                           |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 160-BQFP                                                                |

| Supplier Device Package    | 160-QFP (28x28)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/sc68376bgvab25r |

DSACK[1:0] — Data and Size Acknowledge

DSCLK — Development Serial Clock

DSI — Development Serial Input

DSO — Development Serial Output

ECLK — MC6800 Devices and Peripherals Bus Clock

ETRIG[2:1] — QADC External Trigger

EXTAL — Crystal Oscillator Input

FC[2:0] — Function Codes

FREEZE — Freeze

HALT — Halt

IFETCH — Instruction Fetch

IPIPE — Instruction Pipeline

IRQ[7:1] — Interrupt Request

MA[2:0] — QADC Multiplexed Address

MISO — QSM Master In Slave Out

MODCLK — Clock Mode Select

MOSI — QSM Master Out Slave In

PCS[3:0] — QSM Peripheral Chip-Selects

PQA[7:0] — QADC Port A

PQB[7:0] — QADC Port B

PC[6:0] — SIM Port C

PE[7:0] — SIM Port E

PF[7:0] — SIM Port F

QUOT - Quotient Out

R/W — Read/Write

RESET — Reset

RMC — Read-Modify-Write Cycle

RXD — SCI Receive Data

SCK — QSPI Serial Clock

SIZ[1:0] — Size

SS - Slave Select

T2CLK — TPU Clock In

TPUCH[15:0] — TPU Channel Signals

TSC — Three-State Control

TSTME — Test Mode Enable

V<sub>PH</sub> — QADC High Reference Voltage

V<sub>RI</sub> — QADC Low Reference Voltage

XFC — External Filter Capacitor

XTAL — Crystal Oscillator Output

# 4.4 Virtual Memory

The full addressing range of the CPU32 on the MC68336/376 is 16 Mbytes in each of eight address spaces. Even though most systems implement a smaller physical memory, the system can be made to appear to have a full 16 Mbytes of memory available to each user program by using virtual memory techniques.

A system that supports virtual memory has a limited amount of high-speed physical memory that can be accessed directly by the processor and maintains an image of a much larger virtual memory on a secondary storage device. When the processor attempts to access a location in the virtual memory map that is not resident in physical memory, a page fault occurs. The access to that location is temporarily suspended while the necessary data is fetched from secondary storage and placed in physical memory. The suspended access is then restarted or continued.

The CPU32 uses instruction restart, which requires that only a small portion of the internal machine state be saved. After correcting the fault, the machine state is restored, and the instruction is fetched and started again. This process is completely transparent to the application program.

### 4.5 Addressing Modes

Addressing in the CPU32 is register-oriented. Most instructions allow the results of the specified operation to be placed either in a register or directly in memory. There is no need for extra instructions to store register contents in memory.

There are seven basic addressing modes:

- Register Direct

- Register Indirect

- Register Indirect with Index

- Program Counter Indirect with Displacement

- Program Counter Indirect with Index

- Absolute

- Immediate

The register indirect addressing modes include postincrement, predecrement, and offset capability. The program counter indirect mode also has index and offset capabilities. In addition to these addressing modes, many instructions implicitly specify the use of the status register, stack pointer, and/or program counter.

# 4.6 Processing States

The processor is always in one of four processing states: normal, exception, halted, or background. The normal processing state is associated with instruction execution; the bus is used to fetch instructions and operands and to store results.

## 4.10.1 M68000 Family Development Support

All M68000 Family members include features to facilitate applications development. These features include the following:

Trace on Instruction Execution — M68000 Family processors include an instruction-by-instruction tracing facility as an aid to program development. The MC68020, MC68030, MC68040, and CPU32 also allow tracing only of those instructions causing a change in program flow. In the trace mode, a trace exception is generated after an instruction is executed, allowing a debugger program to monitor the execution of a program under test.

Breakpoint Instruction — An emulator may insert software breakpoints into the target code to indicate when a breakpoint has occurred. On the MC68010, MC68020, MC68030, and CPU32, this function is provided via illegal instructions, \$4848–\$484F, to serve as breakpoint instructions.

Unimplemented Instruction Emulation — During instruction execution, when an attempt is made to execute an illegal instruction, an illegal instruction exception occurs. Unimplemented instructions (F-line, A-line, . . .) utilize separate exception vectors to permit efficient emulation of unimplemented instructions in software.

## 4.10.2 Background Debug Mode

Microcomputer systems generally provide a debugger, implemented in software, for system analysis at the lowest level. The background debug mode (BDM) on the CPU32 is unique in that the debugger has been implemented in CPU microcode.

BDM incorporates a full set of debugging options: registers can be viewed or altered, memory can be read or written to, and test features can be invoked.

A resident debugger simplifies implementation of an in-circuit emulator. In a common setup (refer to **Figure 4-8**), emulator hardware replaces the target system processor. A complex, expensive pod-and-cable interface provides a communication path between the target system and the emulator.

By contrast, an integrated debugger supports use of a bus state analyzer (BSA) for incircuit emulation. The processor remains in the target system (refer to **Figure 4-9**) and the interface is simplified. The BSA monitors target processor operation and the on-chip debugger controls the operating environment. Emulation is much "closer" to target hardware, and many interfacing problems (for example, limitations on high-frequency operation, AC and DC parametric mismatches, and restrictions on cable length) are minimized.

**Table 4-6 Background Mode Command Summary**

| Command                     | Mnemonic    | Description                                                                                                                                                                                                                               |

|-----------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read D/A Register           | RDREG/RAREG | Read the selected address or data register and return the results via the serial interface.                                                                                                                                               |

| Write D/A Register          | WDREG/WAREG | The data operand is written to the specified address or data register.                                                                                                                                                                    |

| Read System Register        | RSREG       | The specified system control register is read. All registers that can be read in supervisor mode can be read in background mode.                                                                                                          |

| Write System Register       | WSREG       | The operand data is written into the specified system control register.                                                                                                                                                                   |

| Read Memory Location        | READ        | Read the sized data at the memory location specified by the long-word address. The source function code register (SFC) determines the address space accessed.                                                                             |

| Write Memory Location WRITE |             | Write the operand data to the memory location specified by the long-word address. The destination function code (DFC) register determines the address space accessed.                                                                     |

| Dump Memory Block DUMP      |             | Used in conjunction with the READ command to dump large blocks of memory. An initial READ is executed to set up the starting address of the block and retrieve the first result. Subsequent operands are retrieved with the DUMP command. |

| Fill Memory Block           | FILL        | Used in conjunction with the WRITE command to fill large blocks of memory. An initial WRITE is executed to set up the starting address of the block and supply the first operand. Subsequent operands are written with the FILL command.  |

| Resume Execution            | GO          | The pipe is flushed and re-filled before resuming instruction execution at the current PC.                                                                                                                                                |

| Patch User Code             | CALL        | Current program counter is stacked at the location of the current stack pointer. Instruction execution begins at user patch code.                                                                                                         |

| Reset Peripherals           | RST         | Asserts RESET for 512 clock cycles. The CPU is not reset by this command. Synonymous with the CPU RESET instruction.                                                                                                                      |

| No Operation NOP            |             | NOP performs no operation and may be used as a null command.                                                                                                                                                                              |

# 4.10.7 Background Mode Registers

BDM processing uses three special purpose registers to keep track of program context during development. A description of each follows.

# 4.10.7.1 Fault Address Register (FAR)

The FAR contains the address of the faulting bus cycle immediately following a bus or address error. This address remains available until overwritten by a subsequent bus cycle. Following a double bus fault, the FAR contains the address of the last bus cycle. The address of the first fault (if there was one) is not visible to the user.

# 4.10.7.2 Return Program Counter (RPC)

The RPC points to the location where fetching will commence after transition from background mode to normal mode. This register should be accessed to change the flow of a program under development. Changing the RPC to an odd value will cause an address error when normal mode prefetching begins.

SIZ[1:0] signals reflect bus allocation during show cycles. Only the appropriate portion of the data bus is valid during the cycle. During a byte write to an internal address, the portion of the bus that represents the byte that is not written reflects internal bus conditions, and is indeterminate. During a byte write to an external address, the data multiplexer in the SIM causes the value of the byte that is written to be driven out on both bytes of the data bus.

#### 5.7 Reset

Reset occurs when an active low logic level on the  $\overline{\text{RESET}}$  pin is clocked into the SIM. The  $\overline{\text{RESET}}$  input is synchronized to the system clock. If there is no clock when  $\overline{\text{RESET}}$  is asserted, reset does not occur until the clock starts. Resets are clocked to allow completion of write cycles in progress at the time  $\overline{\text{RESET}}$  is asserted.

Reset procedures handle system initialization and recovery from catastrophic failure. The MCU performs resets with a combination of hardware and software. The SIM determines whether a reset is valid, asserts control signals, performs basic system configuration and boot ROM selection based on hardware mode-select inputs, then passes control to the CPU32.

#### 5.7.1 Reset Exception Processing

The CPU32 processes resets as a type of asynchronous exception. An exception is an event that preempts normal processing, and can be caused by internal or external events. Exception processing makes the transition from normal instruction execution to execution of a routine that deals with an exception. Each exception has an assigned vector that points to an associated handler routine. These vectors are stored in the exception vector table. The exception vector table consists of 256 four-byte vectors and occupies 1024 bytes of address space. The exception vector table can be relocated in memory by changing its base address in the vector base register (VBR). The CPU32 uses vector numbers to calculate displacement into the table. Refer to **4.9 Exception Processing** for more information.

Reset is the highest-priority CPU32 exception. Unlike all other exceptions, a reset occurs at the end of a bus cycle, and not at an instruction boundary. Handling resets in this way prevents write cycles in progress at the time the reset signal is asserted from being corrupted. However, any processing in progress is aborted by the reset exception and cannot be restarted. Only essential reset tasks are performed during exception processing. Other initialization tasks must be accomplished by the exception handler routine. Refer to **5.7.9 Reset Processing Summary** for details on exception processing.

# 5.7.2 Reset Control Logic

SIM reset control logic determines the cause of a reset, synchronizes reset assertion if necessary to the completion of the current bus cycle, and asserts the appropriate reset lines. Reset control logic can drive four different internal signals:

- E. After arbitration, the interrupt acknowledge cycle is completed in one of the following ways:

- When there is no contention (IARB = %0000), the spurious interrupt monitor asserts BERR, and the CPU32 generates the spurious interrupt vector number

- 2. The dominant interrupt source (external or internal) supplies a vector number and DSACK signals appropriate to the access. The CPU32 acquires the vector number.

- 3. The AVEC signal is asserted (the signal can be asserted by the dominant external interrupt source or the pin can be tied low), and the CPU32 generates an autovector number corresponding to interrupt priority.

- 4. The bus monitor asserts BERR and the CPU32 generates the spurious interrupt vector number.

- F. The vector number is converted to a vector address.

- G. The content of the vector address is loaded into the PC and the processor transfers control to the exception handler routine.

## 5.8.5 Interrupt Acknowledge Bus Cycles

Interrupt acknowledge bus cycles are CPU32 space cycles that are generated during exception processing. For further information about the types of interrupt acknowledge bus cycles determined by  $\overline{\text{AVEC}}$  or  $\overline{\text{DSACK}}$ , refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** and the *SIM Reference Manual* (SIMRM/AD).

## 5.9 Chip-Selects

Typical microcontrollers require additional hardware to provide external chip-select and address decode signals. The MCU includes 12 programmable chip-select circuits that can provide 2 to 16 clock-cycle access to external memory and peripherals. Address block sizes of two Kbytes to one Mbyte can be selected. **Figure 5-19** is a diagram of a basic system that uses chip-selects.

#### **SECTION 9 QUEUED SERIAL MODULE**

This section is an overview of the queued serial module (QSM). Refer to the *QSM Reference Manual* (QSMRM/AD) for complete information about the QSM.

#### 9.1 General

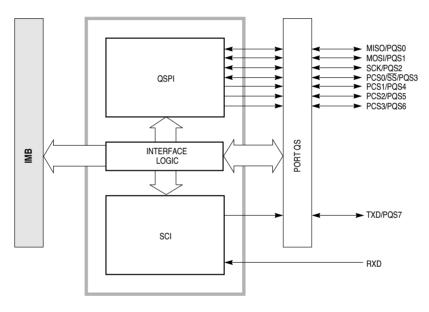

The QSM contains two serial interfaces, the queued serial peripheral interface (QSPI) and the serial communication interface (SCI). **Figure 9-1** is a block diagram of the QSM.

Figure 9-1 QSM Block Diagram

The QSPI provides peripheral expansion or interprocessor communication through a full-duplex, synchronous, three-line bus. Four programmable peripheral chip-selects can select up to sixteen peripheral devices by using an external one of sixteen line selector. A self-contained RAM queue allows up to sixteen serial transfers of eight to sixteen bits each or continuous transmission of up to a 256-bit data stream without CPU32 intervention. A special wrap-around mode supports continuous transmission/reception modes.

OSM BLOCK

QSPI MSTR2 FLOW 3

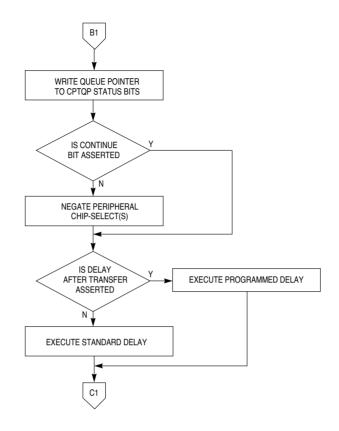

Figure 9-6 Flowchart of QSPI Master Operation (Part 2)

#### **Table 8-4 QADC Clock Programmability**

|                   | Control Registe | er 0 Information | f <sub>s</sub><br>Input Samp | <sub>ys</sub> = 20.97<br>le Time (IST) = %00 |      |  |

|-------------------|-----------------|------------------|------------------------------|----------------------------------------------|------|--|

| Example<br>Number | PSH[4:0]        | PSA              | PSL[2:0]                     | QCLK (MHz) Conversion Time (μs               |      |  |

| 1                 | 7               | 0                | 7                            | 1.0                                          | 18.0 |  |

| 2                 | 7               | 1                | 7                            | 1.0                                          | 18.0 |  |

The MCU system clock frequency is the basis of QADC timing. The QADC requires that the system clock frequency be at least twice the QCLK frequency. Refer to **Table A-13** for information on the minimum and maximum allowable QCLK frequencies.

Example 1 in **Figure 8-9** shows that when PSH = 3, the QCLK remains high for four system clock cycles. It also shows that when PSL = 3, the QCLK remains low for four system clock cycles.

In order to tune QCLK for the fastest possible conversion time for any given system clock frequency, the QADC permits one more programmable control of the QCLK high and low time. The PSA bit in QACR0 allows the QCLK high phase to be stretched for a half cycle of the system clock, and correspondingly, the QCLK low phase is shortened by a half cycle of the system clock.

Example 2 in **Figure 8-9** is the same as Example 1, except that the PSA bit is set. The QCLK high phase has 4.5 system clock cycles; the QCLK low phase has 3.5 system clock cycles.

#### 8.12.5 Periodic/Interval Timer

The QADC periodic/interval timer can be used to generate trigger events at programmable intervals to initiate scans of queue 2. The periodic/interval timer is held in reset under the following conditions:

- Queue 2 is programmed to any queue operating mode which does not use the periodic/interval timer

- Interval timer single-scan mode is selected, but the single-scan enable bit is cleared to zero

- IMB system reset or the master reset is asserted

- The QADC is placed in low-power stop mode with the STOP bit

- The IMB FREEZE line is asserted and the QADC FRZ bit is set to one

Two other conditions which cause a pulsed reset of the timer are:

- Rollover of the timer counter

- A queue operating mode change from one periodic/interval timer mode to another periodic/interval timer mode

During the low-power stop mode, the periodic/interval timer is held in reset. Since low-power stop mode initializes QACR2 to zero, a valid periodic or interval timer mode must be written to QACR2 when exiting low-power stop mode to release the timer from reset.

### 8.13.3 Interrupt Vectors

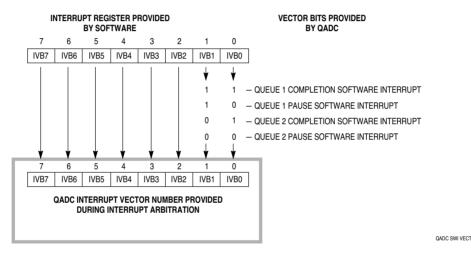

When the QADC is the only module with an interrupt request pending at the level being acknowledged, or when the QADC IARB value is higher than that of other modules with requests pending at the acknowledged IRQ level, the QADC responds to the interrupt acknowledge cycle with an 8-bit interrupt vector number. The CPU32 uses the vector number to calculate a displacement into the exception vector table, then uses the vector at that location to jump to an interrupt service routine.

The interrupt vector base field IVB[7:2] specifies the six high-order bits of the 8-bit interrupt vector number, and the QADC provides two low-order bits which correspond to one of the four QADC interrupt sources.

**Figure 8-11** shows the format of the interrupt vector, and lists the binary coding of the two low-order bits for the four QADC interrupt sources.

Figure 8-11 QADC Interrupt Vector Format

The IVB field has a reset value of \$0F, which corresponds to the uninitialized interrupt exception vector.

Multiple PWMs generated by MCPWM have two types of high time alignment: edge aligned and center aligned. Edge aligned mode uses n + 1 TPU channels for n PWMs; center aligned mode uses 2n + 1 channels. Center aligned mode allows a user-defined "dead time" to be specified so that two PWMs can be used to drive an H-bridge without destructive current spikes. This feature is important for motor control applications.

Refer to TPU programming note *Multichannel Pulse-Width Modulation (MCPWM) TPU Function* (TPUPN05/D) for more information.

## 11.5.6 Fast Quadrature Decode (FQD)

FQD is a position feedback function for motor control. It decodes the two signals from a slotted encoder to provide the CPU32 with a 16-bit free running position counter. FQD incorporates a "speed switch" which disables one of the channels at high speed, allowing faster signals to be decoded. A time stamp is provided on every counter update to allow position interpolation and better velocity determination at low speed or when low resolution encoders are used. The third index channel provided by some encoders is handled by the NITC function.

Refer to TPU programming note *Fast Quadrature Decode (FQD) TPU Function* (TPUPN02/D) for more information.

### 11.5.7 Universal Asynchronous Receiver/Transmitter (UART)

The UART function uses one or two TPU channels to provide asynchronous serial communication. Data word length is programmable from one to 14 bits. The function supports detection or generation of even, odd, and no parity. Baud rate is freely programmable and can be higher than 100 Kbaud. Eight bidirectional UART channels running in excess of 9600 baud can be implemented.

Refer to TPU programming note *Universal Asynchronous Receiver/Transmitter* (UART) TPU Function (TPUPN07/D) for more information.

# 11.5.8 Brushless Motor Commutation (COMM)

This function generates the phase commutation signals for a variety of brushless motors, including three-phase brushless DC motors. It derives the commutation state directly from the position decoded in FQD, thus eliminating the need for hall effect sensors.

The state sequence is implemented as a user-configurable state machine, thus providing a flexible approach with other general applications. An offset parameter is provided to allow all the switching angles to be advanced or retarded on the fly by the CPU32. This feature is useful for torque maintenance at high speeds.

Refer to TPU programming note *Brushless Motor Commutation (COMM) TPU Function* (TPUPN09/D) for more information.

Table 13-7 Mask Examples for Normal/Extended Messages

| Message Buffer (MB)<br>/Mask | Base ID<br>ID[28:18] | IDE | Extended ID<br>ID[17:0] | Match           |

|------------------------------|----------------------|-----|-------------------------|-----------------|

| MB2                          | 11111111000          | 0   | _                       | _               |

| MB3                          | 11111111000          | 1   | 010101010101010101      | _               |

| MB4                          | 00000011111          | 0   | _                       | _               |

| MB5                          | 00000011101          | 1   | 010101010101010101      | _               |

| MB14                         | 11111111000          | 1   | 010101010101010101      | _               |

| RX Global Mask               | 11111111110          |     | 1111111000000000001     | _               |

| RX Message In                | 11111111001          | 1   | 010101010101010101      | 3 <sup>1</sup>  |

|                              | 11111111001          | 0   | _                       | 2 <sup>2</sup>  |

|                              | 11111111001          | 1   | 010101010101010100      | 3               |

|                              | 01111111000          | 0   | _                       | 4               |

|                              | 01111111000          | 1   | 010101010101010101      | 5               |

| RX 14 Mask                   | 01111111111          |     | 1111111000000000000     | _               |

| RX Message In                | 10111111000          | 1   | 010101010101010101      | 6               |

|                              | 01111111000          | 1   | 010101010101010101      | 14 <sup>7</sup> |

#### NOTES:

- 1. Match for extended format (MB3).

- 2. Match for standard format (MB2).

- 3. No match for MB3 because of ID0.

- 4. No match for MB2 because of ID28.

- 5. No match for MB3 because of ID28, match for MB14.

- 6. No match for MB14 because of ID27.

- 7. Match for MB14.

### 13.4.3 Bit Timing

The TouCAN module uses three 8-bit registers to set-up the bit timing parameters required by the CAN protocol. Control registers 1 and 2 (CANCTRL1, CANCTRL2) contain the PROPSEG, PSEG1, PSEG2, and the RJW fields which allow the user to configure the bit timing parameters. The prescaler divide register (PRESDIV) allows the user to select the ratio used to derive the S-clock from the system clock. The time quanta clock operates at the S-clock frequency. **Table 13-8** provides examples of system clock, CAN bit rate, and S-clock bit timing parameters. Refer to **APPENDIX D REGISTER SUMMARY** for more information on the bit timing registers.

# **Table A-5 DC Characteristics**

$(V_{DD} \text{ and } V_{DDSYN} = 5.0 \text{ Vdc } \pm 5\%, V_{SS} = 0 \text{ Vdc, } T_A = T_L \text{ to } T_H)$

| Num | Characteristic                                                                                                                                                                                                                             | Symbol                                                                       | Min                    | Max                    | Unit           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------|------------------------|----------------|

| 1   | Input High Voltage                                                                                                                                                                                                                         | V <sub>IH</sub>                                                              | 0.7 (V <sub>DD</sub> ) | V <sub>DD</sub> + 0.3  | V              |

| 2   | Input Low Voltage                                                                                                                                                                                                                          | V <sub>IL</sub>                                                              | V <sub>SS</sub> - 0.3  | 0.2 (V <sub>DD</sub> ) | ٧              |

| 3   | Input Hysteresis <sup>1</sup>                                                                                                                                                                                                              | V <sub>HYS</sub>                                                             | 0.5                    | _                      | V              |

| 4   | Input Leakage Current <sup>2</sup> $V_{in} = V_{DD}$ or $V_{SS}$ Input-only pins                                                                                                                                                           | I <sub>in</sub>                                                              | -2.5                   | 2.5                    | μА             |

| 5   | High Impedance (Off-State) Leakage Current <sup>2</sup><br>$V_{in} = V_{DD}$ or $V_{SS}$ All input/output and output pins                                                                                                                  | l <sub>oz</sub>                                                              | -2.5                   | 2.5                    | μА             |

| 6   | CMOS Output High Voltage <sup>2, 3</sup> $I_{OH}$ = -10.0 $\mu$ A Group 1, 2, 4 input/output and all output pins                                                                                                                           | V <sub>OH</sub>                                                              | V <sub>DD</sub> - 0.2  | _                      | V              |

| 7   | CMOS Output Low Voltage <sup>2</sup> $I_{OL}$ = 10.0 $\mu A$ Group 1, 2, 4 input/output and all output pins                                                                                                                                | V <sub>OL</sub>                                                              | _                      | 0.2                    | ٧              |

| 8   | Output High Voltage <sup>2, 3</sup> $I_{OH} = -0.8 \text{ mA}$ Group 1, 2, 4 input/output and all output pins                                                                                                                              | V <sub>OH</sub>                                                              | V <sub>DD</sub> - 0.8  | -                      | V              |

| 9   | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                      | V <sub>OL</sub>                                                              | _<br>_<br>_            | 0.4<br>0.4<br>0.4      | V              |

| 10  | Three State Control Input High Voltage                                                                                                                                                                                                     | V <sub>IHTSC</sub>                                                           | 1.6 (V <sub>DD</sub> ) | 9.1                    | ٧              |

| 11  | Data Bus Mode Select Pull-up Current <sup>4</sup> $V_{in} = V_{IL} \qquad DATA[15:0]$ $V_{in} = V_{IH} \qquad DATA[15:0]$                                                                                                                  | I <sub>MSP</sub>                                                             | _<br>_15               | –120<br>—              | μА             |

| 12A | MC68336 V <sub>DD</sub> Supply Current <sup>5</sup> RUN <sup>6</sup> RUN, TPU emulation mode  LPSTOP, 4.194 MHz crystal, VCO Off (STSIM = 0)  LPSTOP (External clock input frequency = maximum f <sub>sys</sub> )                          | I <sub>DD</sub> I <sub>DD</sub> S <sub>IDD</sub> S <sub>IDD</sub>            | _<br>_<br>_<br>_       | 140<br>150<br>3<br>7   | mA<br>mA<br>mA |

| 12B | MC68376 V <sub>DD</sub> Supply Current <sup>5</sup> RUN <sup>6</sup> RUN, TPU emulation mode  LPSTOP, 4.194 MHz crystal, VCO Off (STSIM = 0)  LPSTOP (External clock input frequency = maximum f <sub>sys</sub> )                          | I <sub>DD</sub><br>I <sub>DD</sub><br>S <sub>IDD</sub><br>S <sub>IDD</sub>   | _<br>_<br>_            | 150<br>160<br>3<br>7   | mA<br>mA<br>mA |

| 13  | Clock Synthesizer Operating Voltage                                                                                                                                                                                                        | V <sub>DDSYN</sub>                                                           | 4.75                   | 5.25                   | ٧              |

| 14  | V <sub>DDSYN</sub> Supply Current <sup>5</sup> 4.194 MHz crystal, VCO on, maximum f <sub>sys</sub> External Clock, maximum f <sub>sys</sub> LPSTOP, 4.194 MHz crystal, VCO off (STSIM = 0) 4.194 MHz crystal, V <sub>DD</sub> powered down | I <sub>DDSYN</sub> I <sub>DDSYN</sub> S <sub>IDDSYN</sub> I <sub>DDSYN</sub> |                        | 3<br>5<br>3<br>3       | mA<br>mA<br>mA |

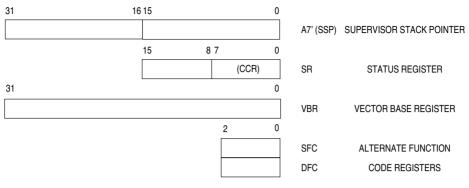

CPU32 SUPV PROG MODEL

Figure D-2 Supervisor Programming Model Supplement

### **D.1.2 Status Register**

### **SR** — Status Register

| 15  | 14   | 13 | 12 | 11 | 10 | 9       | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|------|----|----|----|----|---------|---|---|---|---|---|---|---|---|---|

| T[1 | :0]  | S  | 0  | 0  |    | IP[2:0] |   | 0 | 0 | 0 | Х | N | Z | V | С |

| RES | SET: |    |    |    |    |         |   |   |   |   |   |   |   | • |   |

| 0   | 0    | 1  | 0  | 0  | 1  | 1       | 1 | 0 | 0 | 0 | U | U | U | U | U |

The status register (SR) contains condition codes, an interrupt priority mask, and three control bits. The condition codes are contained in the condition code register (CCR), the lower byte of the SR. (The lower and upper bytes of the status register are also referred to as the user and system bytes, respectively.) In user mode, only the CCR is available. In supervisor mode, software can access the full status register.

### T[1:0] — Trace Enable

This field places the processor in one of two tracing modes or disables tracing. Refer to **Table D-2**.

Table D-2 T[1:0] Encoding

| T[1:0] | Response                       |

|--------|--------------------------------|

| 00     | No tracing                     |

| 01     | Trace on change of flow        |

| 10     | Trace on instruction execution |

| 11     | Undefined; reserved            |

### **D.2 System Integration Module**

**Table D-3** shows the SIM address map. The column labeled "Access" indicates the privilege level at which the CPU32 must be operating to access the register. A designation of "S" indicates that supervisor mode is required. A designation of "S/U" indicates that the register can be programmed for either supervisor mode access or unrestricted access.

**Table D-3 SIM Address Map**

| Access | Address <sup>1</sup> | 15 8 7                                     |                                   |  |  |  |  |  |

|--------|----------------------|--------------------------------------------|-----------------------------------|--|--|--|--|--|

| S      | \$YFFA00             | SIM Module Configu                         | ration Register (SIMCR)           |  |  |  |  |  |

| S      | \$YFFA02             | SIM Test Ro                                | SIM Test Register (SIMTR)         |  |  |  |  |  |

| S      | \$YFFA04             | Clock Synthesizer C                        | ontrol Register (SYNCR)           |  |  |  |  |  |

| S      | \$YFFA06             | Not Used                                   | Reset Status Register (RSR)       |  |  |  |  |  |

| S      | \$YFFA08             | SIM Test Reg                               | pister E (SIMTRE)                 |  |  |  |  |  |

| S      | \$YFFA0A             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA0C             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA0E             | No                                         | t Used                            |  |  |  |  |  |

| S/U    | \$YFFA10             | Not Used                                   | Port E Data (PORTE0)              |  |  |  |  |  |

| S/U    | \$YFFA12             | Not Used                                   | Port E Data (PORTE1)              |  |  |  |  |  |

| S/U    | \$YFFA14             | Not Used                                   | Port E Data Direction (DDRE)      |  |  |  |  |  |

| S      | \$YFFA16             | Not Used                                   | Port E Pin Assignment (PEPAR)     |  |  |  |  |  |

| S/U    | \$YFFA18             | Not Used                                   | Port F Data (PORTF0)              |  |  |  |  |  |

| S/U    | \$YFFA1A             | Not Used                                   | Port F Data (PORTF1)              |  |  |  |  |  |

| S/U    | \$YFFA1C             | Not Used                                   | Port F Data Direction (DDRF)      |  |  |  |  |  |

| S      | \$YFFA1E             | Not Used                                   | Port F Pin Assignment (PFPAR)     |  |  |  |  |  |

| S      | \$YFFA20             | Not Used                                   | System Protection Control (SYPCR) |  |  |  |  |  |

| S      | \$YFFA22             | Periodic Interrupt Control Register (PICR) |                                   |  |  |  |  |  |

| S      | \$YFFA24             | Periodic Interrupt                         | Fiming Register (PITR)            |  |  |  |  |  |

| S      | \$YFFA26             | Not Used                                   | Software Service (SWSR)           |  |  |  |  |  |

| S      | \$YFFA28             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA2A             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA2C             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA2E             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA30             | Test Module Mast                           | er Shift A (TSTMSRA)              |  |  |  |  |  |

| S      | \$YFFA32             | Test Module Mast                           | er Shift B (TSTMSRB)              |  |  |  |  |  |

| S      | \$YFFA34             | Test Module Si                             | hift Count (TSTSC)                |  |  |  |  |  |

| S      | \$YFFA36             | Test Module Repet                          | tition Counter (TSTRC)            |  |  |  |  |  |

| S      | \$YFFA38             | Test Module                                | Control (CREG)                    |  |  |  |  |  |

| S/U    | \$YFFA3A             | Test Module D                              | Distributed (DREG)                |  |  |  |  |  |

|        | \$YFFA3C             | No                                         | t Used                            |  |  |  |  |  |

|        | \$YFFA3E             | No                                         | t Used                            |  |  |  |  |  |

| S/U    | \$YFFA40             | Not Used                                   | Port C Data (PORTC)               |  |  |  |  |  |

|        | \$YFFA42             | No                                         | t Used                            |  |  |  |  |  |

| S      | \$YFFA44             | Chip-Select Pin A                          | ssignment (CSPAR0)                |  |  |  |  |  |

| S      | \$YFFA46             | ·                                          | ssignment (CSPAR1)                |  |  |  |  |  |

| S      | \$YFFA48             |                                            | se Boot (CSBARBT)                 |  |  |  |  |  |

| S      | \$YFFA4A             |                                            | Chip-Select Option Boot (CSORBT)  |  |  |  |  |  |

| S      | \$YFFA4C             |                                            | Chip-Select Base 0 (CSBAR0)       |  |  |  |  |  |

| S      | \$YFFA4E             | Chip-Select Option 0 (CSOR0)               |                                   |  |  |  |  |  |

This field only affects the response of chip-selects and does not affect interrupt recognition by the CPU32.

#### AVEC — Autovector Enable

This field selects one of two methods of acquiring an interrupt vector during an interrupt acknowledge cycle. It is not usually used with a chip-select pin.

- 0 = External interrupt vector enabled

- 1 = Autovector enabled

If the chip select is configured to trigger on an interrupt acknowledge cycle (SPACE[1:0] = %00) and the  $\overline{\text{AVEC}}$  field is set to one, the chip-select automatically generates  $\overline{\text{AVEC}}$  in response to the interrupt acknowledge cycle. Otherwise, the vector must be supplied by the requesting device.

## **D.2.22 Master Shift Registers**

**TSTMSRA** — Master Shift Register A **\$YFFA30**Used for factory test only.

# **D.2.23 Test Module Shift Count Register**

**TSTSC** — Test Module Shift Count

Used for factory test only.

\$YFFA34

# **D.2.24 Test Module Repetition Count Register**

**TSTRC** — Test Module Repetition Count

Used for factory test only.

\$YFFA36

# **D.2.25 Test Submodule Control Register**

**CREG** — Test Submodule Control Register

Used for factory test only.

\$YFFA38

# **D.2.26 Distributed Register**

DREG — Distributed Register \$YFFA3A Used for factory test only.

### D.6.10 Port QS Pin Assignment Register/Data Direction Register

|   |    |        |        |        |        |    |        |        |       |       | YFF(<br>YFF( |       |       |       |       |       |

|---|----|--------|--------|--------|--------|----|--------|--------|-------|-------|--------------|-------|-------|-------|-------|-------|

| 1 | 5  | 14     | 13     | 12     | 11     | 10 | 9      | 8      | 7     | 6     | 5            | 4     | 3     | 2     | 1     | 0     |

| ( | )  | PQSPA6 | PQSPA5 | PQSPA4 | PQSPA3 | 0  | PQSPA1 | PQSPA0 | DDQS7 | DDQS6 | DDQS5        | DDQS4 | DDQS3 | DDQS2 | DDQS1 | DDQS0 |

|   | RE | SET:   |        |        |        |    |        |        |       |       |              |       |       |       |       |       |

| - | ١  | Λ      | Λ      | Λ      | Λ      | Λ  | Λ      | Λ      | Λ     | Λ     | Λ            | Λ     | Λ     | Λ     | Λ     | Λ     |

Clearing a bit in PQSPAR assigns the corresponding pin to general-purpose I/O; setting a bit assigns the pin to the QSPI. PQSPAR does not affect operation of the SCI. **Table D-32** displays PQSPAR pin assignments.

**Table D-32 PQSPAR Pin Assignments**

| PQSPAR Field | PQSPAR Bit | Pin Function      |

|--------------|------------|-------------------|

| PQSPA0       | 0          | PQS0              |

| PQSPAU       | 1          | MISO              |

| PQSPA1       | 0          | PQS1              |

| PQSPAT       | 1          | MOSI              |

|              | _          | PQS2 <sup>1</sup> |

| _            | _          | SCK               |

| PQSPA3       | 0          | PQS3              |

| FQSFAS       | 1          | PCS0/SS           |

| PQSPA4       | 0          | PQS4              |

| FQ3FA4       | 1          | PCS1              |

| PQSPA5       | 0          | PQS5              |

| PQSPAS       | 1          | PCS2              |

| PQSPA6       | 0          | PQS6              |

| FQSFA0       | 1          | PCS3              |

|              | _          | PQS7 <sup>2</sup> |

| _            | _          | TXD               |

#### NOTES:

- PQS2 is a digital I/O pin unless the SPI is enabled (SPE in SPCR1 set), in which case it becomes the QSPI serial clock SCK.

- 2. PQS7 is a digital I/O pin unless the SCI transmitter is enabled (TE in SCCR1 = 1), in which case it becomes the SCI serial output TXD.

DDRQS determines whether pins configured for general purpose I/O are inputs or outputs. Clearing a bit makes the corresponding pin an input; setting a bit makes the pin an output. DDRQS affects both QSPI function and I/O function. **Table D-33** shows the effect of DDRQS on QSM pin function.

# **D.7 Configurable Timer Module 4**

**Table D-35** shows the CTM4 address map. All CTM4 control registers reside in supervisor space only.

# Table D-35 CTM4 Address Map

| Address <sup>1</sup> | 15                                                   | 0 |

|----------------------|------------------------------------------------------|---|

| \$YFF400             | BIUSM Module Configuration Register (BIUMCR)         |   |

| \$YFF402             | BIUSM Test Register (BIUTEST)                        |   |

| \$YFF404             | BIUSM Time Base Register (BIUTBR)                    |   |

| \$YFF406             | Reserved                                             |   |

| \$YFF408             | CPSM Control Register (CPCR)                         |   |

| \$YFF40A             | CPSM Test Register (CPTR)                            |   |

| \$YFF40C - \$YFF40E  |                                                      |   |

| \$YFF410             | MCSM2 Status/Interrupt/Control Register (MCSM2SIC)   |   |

| \$YFF412             | MCSM2 Counter (MCSM2CNT)                             |   |

| \$YFF414             | MCSM2 Modulus Latch (MCSM2ML)                        |   |

| \$YFF416             | Reserved                                             |   |

| \$YFF418             | DASM3 Status/Interrupt/Control Register (DASM3SIC)   |   |

| \$YFF41A             | DASM3 Register A (DASM3A)                            |   |

| \$YFF41C             | DASM3 Register B (DASM3B)                            |   |

| \$YFF41E             | Reserved                                             |   |

| \$YFF420             | DASM4 Status/Interrupt/Control Register (DASM4SIC)   |   |

| \$YFF422             | DASM4 Register A (DASM4A)                            |   |

| \$YFF424             | DASM4 Register B (DASM4B)                            |   |

| \$YFF426             | Reserved                                             |   |

| \$YFF428             | PWMSM5 Status/Interrupt/Control Register (PWM5SIC)   |   |

| \$YFF42A             | PWMSM5 Period (PWM5A)                                |   |

| \$YFF42C             | PWMSM5 Pulse Width (PWM5B)                           |   |

| \$YFF42E             | PWMSM5 Counter (PWM5C)                               |   |

| \$YFF430             | PWMSM6 Status/Interrupt/Control Register (PWM6SIC)   |   |

| \$YFF432             | PWMSM6 Period (PWM6A)                                |   |

| \$YFF434             | PWMSM6 Pulse Width (PWM6B)                           |   |

| \$YFF436             | PWMSM6 Counter (PWM6C)                               |   |

| \$YFF438             | PWMSM7 Status/Interrupt/Control Register (PWM7SIC)   |   |

| \$YFF43A             | PWMSM7 Period (PWM7A)                                |   |

| \$YFF43C             | PWMSM7 Pulse Width (PWM7B)                           |   |

| \$YFF43E             | PWMSM7 Counter (PWM7C)                               |   |

| \$YFF440             | PWMSM8 Status/Interrupt/Control Register (PWM8SIC)   |   |

| \$YFF442             | PWMSM8 Period (PWM8A)                                |   |

| \$YFF444             | PWMSM8 Pulse Width (PWM8B)                           |   |

| \$YFF446             | PWMSM8 Counter (PWM8C)                               |   |

| \$YFF448             | DASM9 Status/Interrupt/Control Register (DASM9SIC)   |   |

| \$YFF44A             | DASM9 Register A (DASM9A)                            |   |

| \$YFF44C             | DASM9 Register B (DASM9B)                            |   |

| \$YFF44E             | Reserved                                             |   |

| \$YFF450             | DASM10 Status/Interrupt/Control Register (DASM10SIC) |   |

| \$YFF452             | DASM10 Register A (DASM10A)                          |   |

| \$YFF454             | DASM10 Register B (DASM10B)                          |   |

| \$YFF456             | Reserved                                             |   |

| \$YFF458             | MCSM11 Status/Interrupt/Control Register (MCSM11SIC) |   |

| CSBAR D-17                                         | DCNR D-80                                       |

|----------------------------------------------------|-------------------------------------------------|

| CSBARBT D-17                                       | DDRE 5-64, D-10                                 |

| CSBOOT 5-50, 5-56, 5-58, 7-3                       | DDRF 5-64, D-11                                 |

| reset values 5-63                                  | DDRQA 8-2, D-30                                 |

| CSOR D-18                                          | DDRQS 9-4, 9-16, 9-19, D-47                     |

| CSORBT D-18                                        | Delay                                           |

| CSPAR D-15                                         | after transfer (DT) 9-18, D-54                  |

| CTD9 D-62                                          | before SCK (DSCKL) D-50                         |

| CTM Reference Manual 10-1                          | · · · · · · · · · · · · · · · · · · ·           |

|                                                    | Designated CPU space 5-22                       |

| CTM2C D-62                                         | Development                                     |

| CTM4                                               | support and test registers (TPU) 11-17          |

| address map 10-2, D-56                             | tools and support C-1                           |

| block diagram 10-1                                 | DFC 4-7                                         |

| bus interface unit submodule (BIUSM) 10-3          | Digital                                         |

| components 10-1                                    | control section                                 |

| counter prescaler submodule (CPSM) 10-4            | contents 8-1, 8-16-??                           |

| double-action submodule (DASM) 10-10               | input                                           |

| features 3-2                                       | /output port (PQA) 8-4                          |

| free-running counter submodule (FCSM) 10-5         | port (PQB) 8-4                                  |

| interrupt priority and vector/pin allocation 10-18 | to analog converter (DAC) 8-1, 8-15             |

| interrupts 10-18                                   | DIO 11-6                                        |

| modulus counter submodule (MCSM) 10-5, 10-7        | DIS D-67, D-68                                  |

| pulse width modulation submodule (PWMSM) 10-12     | Disabled mode 8-20                              |

| CWP D-36                                           | Discrete input/output (DIO) 11-6                |

| Cyclic redundancy check error (CRCERR) D-94        | Distributed register (DREG) D-21                |

| Cyclic redundancy check error (Creditive) D 54     | DIV8 clock 11-15                                |

| D.                                                 | Divide by 2/divide by 3 (DIV23) D-59            |

| –D–                                                | , , ,                                           |

|                                                    | Double                                          |

| DAC 8-1                                            | -action submodule. See DASM 10-10               |

| DASM 10-10                                         | -buffered 9-26, 9-28                            |

| block diagram 10-11                                | bus fault 4-20, 5-36                            |

| channels 10-10                                     | -row header 4-25                                |

| interrupts 10-12                                   | DREG D-21                                       |

| mode flag status bit states D-64                   | Drive time base bus (DRV) D-60, D-61            |

| modes of operation 10-10                           | DRV D-60, D-61                                  |

| registers 10-12                                    | DS 5-22, 5-27, 5-37                             |

| · ·                                                | DSACK 5-14, 5-27, 5-31, 5-53, 5-58, 5-60        |

| data register A (DASMA) D-66                       | assertion results 5-35                          |

| data register B (DASMB) D-67                       | external/internal generation 5-30               |

| status/interrupt/control register (DASMSIC)        | option fields 5-30                              |

| D-63                                               | signal effects 5-24                             |

| timing (electricals) A-33                          | source specification in asynchronous mode 5-60, |

| DASMA D-66                                         | D-19                                            |

| operations D-67                                    | DSCK D-55                                       |

| DASMB D-67                                         | DSCKL D-50                                      |

| operations D-68                                    | DSCLK 4-24                                      |

| DASMSIC D-63                                       |                                                 |

| DATA 5-21                                          | DSCR D-75                                       |

| Data                                               | DSSR D-76                                       |

| and size acknowledge (DSACK) 5-14, 5-23            | DT D-54                                         |

| bus                                                | DTL D-51                                        |

| mode selection 5-42                                | Dynamic bus sizing 5-24                         |

| signals (DATA) 5-21                                |                                                 |

| field for RX/TX frames (TouCAN) 13-4               | –E–                                             |

| frame 9-25                                         |                                                 |

| multiplexer 5-25                                   | EBI 5-52                                        |

|                                                    |                                                 |

| strobe (DS) 5-22                                   | ECLK 5-12                                       |

| types 4-4                                          | bus timing A-21                                 |

| DATA (definition) 2-8                              | output timing diagram A-10                      |

| DBcc 4-15                                          | timing diagram A-22                             |

| DC characteristics (electricals) A-4               | Edge polarity (EDPOL) bit D-65                  |

MOTOROLA MC68336/376 I-4 USER'S MANUAL

| EDGEN D-62                                      | reset (EXT) D-9                                |

|-------------------------------------------------|------------------------------------------------|

| EDGEP D-62                                      | trigger pins 8-5                               |

| EDIV 5-12, D-8                                  | Externally                                     |

| EDPOL D-65                                      | input clock frequency D-14                     |

| EMPTY 13-4                                      | multiplexed mode (MUX) D-31                    |

| EMU 11-5, 11-15, D-74                           | EXTRST (external reset) 5-48                   |

| EMUL D-25                                       |                                                |

| Emulation                                       | -F-                                            |

| control (EMU) 11-15, D-74                       |                                                |

| mode control (EMUL) D-25                        | Factory tost 5-64                              |

| support 11-5                                    | Factory test 5-64 FAR 4-22                     |

| EN D-70                                         |                                                |

| Encoded                                         | Fast                                           |

| one of three channel priority levels (CH) D-80  | quadrature decode (FQD) 11-12<br>reference 5-4 |

| time function for each channel (CHANNEL) D-78   |                                                |

| type of host service (CH) D-79                  | circuit 5-5                                    |

| Ending queue pointer (ENDQP) D-52               | termination                                    |

| End-of-                                         | cycles 5-26, 5-30                              |

| frame (EOF) 13-16                               | read cycle timing diagram A-13                 |

| queue condition 8-30                            | write cycle timing diagram A-14                |

| ENDQP 9-8, D-52                                 | Fast reference frequency D-14                  |

| EOF 13-16                                       | Fault confinement state (FCS) 13-10, D-95      |

| ERRINT D-96                                     | FC 5-22                                        |

| ERRMSK D-89                                     | FCS 13-10, D-95                                |

| Error                                           | FCSM 10-5                                      |

| conditions 9-28                                 | block diagram 10-5                             |

| counters 13-9                                   | clock sources 10-6                             |

| detection circuitry 9-2                         | counter 10-6                                   |

| interrupt (ERRINT) D-96                         | external event counting 10-6                   |

| interrupt mask (ERRMSK) D-89                    | interrupts 10-6                                |

| ESTAT D-94                                      | registers 10-7                                 |

| ETRIG 8-5                                       | counter register (FCSMCNT) D-61                |

| Event flag (FLAG) D-63                          | status/interrupt/control register (FCSMSIC)    |

| Event timing 11-3                               | D-59                                           |

| Exception                                       | time base bus drivers 10-6                     |

| instruction (RTE) 5-36                          | timing (electricals) A-31                      |

| processing 4-15, 5-40                           | FCSMCNT D-61                                   |

| sequence 4-17                                   | FCSMSIC D-59                                   |

| types of exceptions 4-17                        | FE 9-28, D-46                                  |

| vectors 4-15                                    | Final sample time 8-13                         |

| exception vector assignments 4-16               | FLAG D-63, D-68                                |

| vector 5-40, 11-6                               | FORCA D-65                                     |

| EXOFF D-6                                       | FORCB D-65                                     |

| EXT D-9                                         | Force (FORCA/B) D-65                           |

| Extended message format 13-1                    | FORMERR D-94                                   |

| frames 13-4                                     | f <sub>PWM</sub> 10-16                         |

| External                                        | f <sub>QCLK</sub> 8-24                         |

| bus                                             | FQD 11-12                                      |

| arbitration 5-38                                | FQM 11-13                                      |

| clock                                           | Frame 9-25                                     |

| division (EDIV) D-8                             | size 9-28                                      |

| division bit (EDIV) 5-12                        | Frames                                         |

| operation during LPSTOP 5-12                    | overload 13-16                                 |

|                                                 | remote 13-15                                   |

| signal (ECLK) 5-12<br>interface (EBI) 5-19      | Framing error (FE) flag 9-28, D-46             |

| ,                                               | Free-running counter submodule. See FCSM 10-5  |

| control signals 5-21                            | FREEZ ACK 13-16                                |

| clock input timing diagram A-10                 | FREEZE                                         |

| clock off (EXOFF) D-6<br>digital supply pin 8-6 | assertion response (FRZ)                       |

| digital supply pin 8-6<br>multiplexing 8-10     | BIUSM 10-3, D-57                               |

| multiplexiting o-10                             | QADC 8-7, D-29                                 |

|                                                 |                                                |

MC68336/376 USER'S MANUAL