Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Batalla                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Obsolete                                                                  |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128d3-an |

## 28.1.5 Communication Functions

| SCL    | Serial Clock for TWI                                               |

|--------|--------------------------------------------------------------------|

| SDA    | Serial Data for TWI                                                |

| SCLIN  | Serial Clock In for TWI when external driver interface is enabled  |

| SCLOUT | Serial Clock Out for TWI when external driver interface is enabled |

| SDAIN  | Serial Data In for TWI when external driver interface is enabled   |

| SDAOUT | Serial Data Out for TWI when external driver interface is enabled  |

| XCKn   | Transfer Clock for USART n                                         |

| RXDn   | Receiver Data for USART n                                          |

| TXDn   | Transmitter Data for USART n                                       |

| SS     | Slave Select for SPI                                               |

| MOSI   | Master Out Slave In for SPI                                        |

| MISO   | Master In Slave Out for SPI                                        |

| SCK    | Serial Clock for SPI                                               |

## 28.1.6 Oscillators, Clock, and Event

| TOSCn  | Timer Oscillator pin n            |

|--------|-----------------------------------|

| XTALn  | Input/Output for Oscillator pin n |

| CLKOUT | Peripheral Clock Output           |

| EVOUT  | Event Channel Output              |

| RTCOUT | RTC Clock Source Output           |

# 28.1.7 Debug/system Functions

| RESET    | Reset pin                             |

|----------|---------------------------------------|

| PDI_CLK  | Program and Debug Interface Clock pin |

| PDI_DATA | Program and Debug Interface Data pin  |

# 28.2 Alternate Pin Functions

The tables below show the primary/default function for each pin on a port in the first column, the pin number in the second column, and then all alternate pin functions in the remaining columns. The head row shows what peripheral that enable and use the alternate pin functions.

For better flexibility, some alternate functions also have selectable pin locations for their functions, this is noted under the first table where this apply.

| PORT C | PIN# | INTERRUPT | TCC0 (1)(2) | AWEXC  | TCC1 | USARTC0 (3) | SPIC (4) | TWIC | CLOCKOUT (5)       | EVENTOUT (6) |

|--------|------|-----------|-------------|--------|------|-------------|----------|------|--------------------|--------------|

| PC6    | 22   | SYNC      |             | OC0DLS |      |             | MISO     |      | RTCOUT             |              |

| PC7    | 23   | SYNC      |             | OC0DHS |      |             | SCK      |      | clk <sub>PER</sub> | EVOUT        |

| GND    | 24   |           |             |        |      |             |          |      |                    |              |

| vcc    | 25   |           |             |        |      |             |          |      |                    |              |

Notes:

- 1. Pin mapping of all TC0 can optionally be moved to high nibble of port.

- 2. If TC0 is configured as TC2 all eight pins can be used for PWM output.

- 3. Pin mapping of all USART0 can optionally be moved to high nibble of port.

- 4. Pins MOSI and SCK for all SPI can optionally be swapped.

- 5. CLKOUT can optionally be moved between port C, D, and E and between pin 4 and 7.

- 6. EVOUT can optionally be moved between port C, D, and E and between pin 4 and 7.

#### Table 28-4. Port D - Alternate Functions

| PORT D | PIN# | INTERRUPT  | TCD0 | USARTD0 | SPID | CLOCKOUT           | EVENTOUT |

|--------|------|------------|------|---------|------|--------------------|----------|

| PD0    | 26   | SYNC       | OC0A |         |      |                    |          |

| PD1    | 27   | SYNC       | OC0B | XCK0    |      |                    |          |

| PD2    | 28   | SYNC/ASYNC | OC0C | RXD0    |      |                    |          |

| PD3    | 29   | SYNC       | OC0D | TXD0    |      |                    |          |

| PD4    | 30   | SYNC       |      |         | SS   |                    |          |

| PD5    | 31   | SYNC       |      |         | MOSI |                    |          |

| PD6    | 32   | SYNC       |      |         | MISO |                    |          |

| PD7    | 33   | SYNC       |      |         | SCK  | Clk <sub>PER</sub> | EVOUT    |

| GND    | 34   |            |      |         |      |                    |          |

| vcc    | 35   |            |      |         |      |                    |          |

#### Table 28-5. Port E - Alternate Functions

| PORT E | PIN# | INTERRUPT  | TCE0 | USARTE0 | TOSC  | TWIE | СГОСКОПТ           | EVENTOUT |

|--------|------|------------|------|---------|-------|------|--------------------|----------|

| PE0    | 36   | SYNC       | OC0A |         |       | SDA  |                    |          |

| PE1    | 37   | SYNC       | OC0B | XCK0    |       | SCL  |                    |          |

| PE2    | 38   | SYNC/ASYNC | OC0C | RXD0    |       |      |                    |          |

| PE3    | 39   | SYNC       | OC0D | TXD0    |       |      |                    |          |

| PE4    | 40   | SYNC       |      |         |       |      |                    |          |

| PE5    | 41   | SYNC       |      |         |       |      |                    |          |

| PE6    | 42   | SYNC       |      |         | TOSC2 |      |                    |          |

| PE7    | 43   | SYNC       |      |         | TOSC1 |      | Clk <sub>PER</sub> | EVOUT    |

| GND    | 44   |            |      |         |       |      |                    |          |

| vcc    | 45   |            |      |         |       |      |                    |          |

# 32.1.11 Power-on Reset Characteristics

Table 32-16. Power-on Reset Characteristics

| Symbol                           | Parameter                                     | Condition                                | Min. | Тур. | Max. | Units |

|----------------------------------|-----------------------------------------------|------------------------------------------|------|------|------|-------|

| V (1)                            | POR threshold voltage falling V <sub>CC</sub> | V <sub>CC</sub> falls faster than 1V/ms  | 0.4  | 1.0  |      |       |

| V <sub>POT-</sub> <sup>(1)</sup> |                                               | V <sub>CC</sub> falls at 1V/ms or slower | 0.8  | 1.3  |      | V     |

| V <sub>POT+</sub>                | POR threshold voltage rising V <sub>CC</sub>  |                                          |      | 1.3  | 1.59 |       |

Note:

# 32.1.12 Flash and EEPROM Memory Characteristics

Table 32-17. Endurance and Data Retention

| Symbol | Parameter  | Condition          |       | Min. | Тур. | Max. | Units |

|--------|------------|--------------------|-------|------|------|------|-------|

|        |            |                    | 25°C  | 10K  |      |      |       |

|        |            | Write/Erase cycles | 85°C  | 10K  |      |      | Cycle |

|        | Flash      |                    | 105°C | 2K   |      |      |       |

|        | 1 10311    |                    | 25°C  | 100  |      |      |       |

|        |            | Data retention     | 85°C  | 25   |      |      | Year  |

|        |            |                    | 105°C | 10   |      |      |       |

|        |            | Write/Erase cycles | 25°C  | 100K |      |      | Cycle |

|        |            |                    | 85°C  | 100K |      |      |       |

|        | EEPROM     |                    | 105°C | 30K  |      |      |       |

|        | LLI IVOIVI |                    | 25°C  | 100  |      |      | Year  |

|        |            | Data retention     | 85°C  | 25   |      |      |       |

|        |            |                    | 105°C | 10   |      |      |       |

Table 32-18. Programming Time

| Symbol | Parameter         | Condition                   | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|--------|-------------------|-----------------------------|------|---------------------|------|-------|

|        | Chip erase (2)    | 32KB Flash, EEPROM          |      | 50                  |      |       |

|        | Application erase | Section erase               |      | 6                   |      |       |

|        |                   | Page erase                  |      | 4                   |      |       |

|        | Flash             | Page write                  |      | 4                   |      |       |

|        |                   | Atomic page erase and write |      | 8                   |      | ms    |

|        |                   | Page erase                  |      | 4                   |      |       |

|        | EEPROM            | Page write                  |      | 4                   |      |       |

|        |                   | Atomic page erase and write |      | 8                   |      |       |

Notes:

<sup>1.</sup>  $V_{POT-}$  values are only valid when BOD is disabled. When BOD is enabled  $V_{POT-} = V_{POT+}$ .

<sup>1.</sup> Programming is timed from the 2MHz internal oscillator.

$<sup>2. \</sup>quad \hbox{EEPROM is not erased if the EESAVE fuse is programmed}. \\$

Table 32-25. External Clock with Prescaler (1) for System Clock

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units   |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|---------|

| 1 /+              | Clock Frequency (2)                               | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 90   | MHz     |

| 1/t <sub>CK</sub> |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 142  | IVII IZ |

| 4                 | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 11   |      |      |         |

| t <sub>CK</sub>   | CIOCK PERIOU                                      | V <sub>CC</sub> = 2.7 - 3.6V | 7    |      |      |         |

| 4                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      |         |

| t <sub>CH</sub>   | Clock High Time                                   | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      | -       |

| 4                 | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      | ns      |

| t <sub>CL</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      | 115     |

| 4                 | Pico Timo (for maximum fraquancy)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  |         |

| t <sub>CR</sub>   | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  |         |

| 4                 | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  |         |

| t <sub>CF</sub>   | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  |         |

| Δt <sub>CK</sub>  | Change in period from one clock cycle to the next |                              |      |      | 10   | %       |

Notes:

- 1. System Clock Prescalers must be set so that maximum CPU clock frequency for device is not exceeded.

- 2. The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

# 32.1.13.7 External 16MHz Crystal Oscillator and XOSC Characteristics

Table 32-26. External 16MHz Crystal Oscillator and XOSC Characteristics

| Symbol | Parameter             | Condition |                     | Min. | Тур.  | Max. | Units    |

|--------|-----------------------|-----------|---------------------|------|-------|------|----------|

|        |                       | XOSCPWR=0 | FRQRANGE=0          |      | 0     |      |          |

|        | Cycle to cycle jitter | AUSCHWR-U | FRQRANGE=1, 2, or 3 |      | 0     |      |          |

|        |                       | XOSCPWR=1 |                     |      | 0     |      | ns       |

|        |                       | XOSCPWR=0 | FRQRANGE=0          |      | 0     |      | 115      |

|        | Long term jitter      | AUSCHWR-U | FRQRANGE=1, 2, or 3 |      | 0     |      |          |

|        |                       | XOSCPWR=1 |                     |      | 0     |      |          |

|        |                       |           | FRQRANGE=0          |      | 0.03  |      |          |

|        | Fraguency error       | XOSCPWR=0 | FRQRANGE=1          |      | 0.03  |      |          |

|        | Frequency error       |           | FRQRANGE=2 or 3     |      | 0.03  |      |          |

|        |                       | XOSCPWR=1 |                     |      | 0.003 |      | %        |

|        |                       |           | FRQRANGE=0          |      | 50    |      | - %<br>- |

|        | Duty cycle            | XOSCPWR=0 | FRQRANGE=1          |      | 50    |      |          |

|        | Duty Cycle            |           | FRQRANGE=2 or 3     |      | 50    |      |          |

|        |                       | XOSCPWR=1 |                     |      | 50    |      |          |

| Symbol             | Parameter                          | Condition | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------|-----------|------|------|------|-------|

| C <sub>XTAL1</sub> | Parasitic capacitance<br>XTAL1 pin |           |      | 5.9  |      |       |

| C <sub>XTAL2</sub> | Parasitic capacitance<br>XTAL1 pin |           |      | 8.3  |      | pF    |

| C <sub>LOAD</sub>  | Parasitic capacitance load         |           |      | 3.5  |      |       |

Note: 1. Numbers for negative impedance are not tested in production but guaranteed from design and characterization.

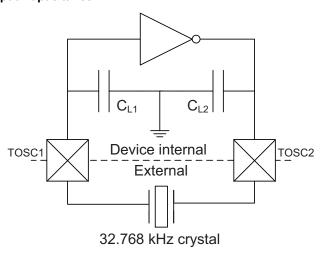

## 32.3.13.8 External 32.768kHz Crystal Oscillator and TOSC Characteristics

Table 32-85. External 32.768kHz Crystal Oscillator and TOSC Characteristics

| Symbol             | Parameter                                              | Condition                                         |   | Тур. | Max. | Units |

|--------------------|--------------------------------------------------------|---------------------------------------------------|---|------|------|-------|

|                    | Recommended crystal equivalent series resistance (ESR) | Crystal load capacitance 6.5pF                    |   |      | 60   |       |

| ESR/R1             |                                                        | Crystal load capacitance 9.0pF                    |   |      | 35   | kΩ    |

|                    |                                                        | Crystal load capacitance 12pF                     |   |      | 28   |       |

| C <sub>TOSC1</sub> | Parasitic capacitance<br>TOSC1 pin                     |                                                   |   | 3.5  |      | pF    |

| C <sub>TOSC2</sub> | Parasitic capacitance<br>TOSC2 pin                     |                                                   |   | 3.5  |      | ρi    |

|                    | Recommended safety factor                              | Capacitance load matched to crystal specification | 3 |      |      |       |

Note: See Figure 32-18 for definition.

Figure 32-18.TOSC Input Capacitance

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

Table 32-86. SPI Timing Characteristics and Requirements

| Symbol             | Parameter               | Condition | Min.                     | Тур.                               | Max. | Units |

|--------------------|-------------------------|-----------|--------------------------|------------------------------------|------|-------|

| t <sub>sck</sub>   | SCK period              | Master    |                          | (See Table 20-3 in XMEGA D manual) |      |       |

| t <sub>SCKW</sub>  | SCK high/low width      | Master    |                          | 0.5 * SCK                          |      |       |

| t <sub>SCKR</sub>  | SCK rise time           | Master    |                          | 2.7                                |      |       |

| t <sub>SCKF</sub>  | SCK fall time           | Master    |                          | 2.7                                |      |       |

| t <sub>MIS</sub>   | MISO setup to SCK       | Master    |                          | 10                                 |      |       |

| t <sub>MIH</sub>   | MISO hold after SCK     | Master    |                          | 10                                 |      |       |

| t <sub>MOS</sub>   | MOSI setup SCK          | Master    |                          | 0.5 * SCK                          |      |       |

| t <sub>MOH</sub>   | MOSI hold after SCK     | Master    |                          | 1                                  |      |       |

| t <sub>ssck</sub>  | Slave SCK Period        | Slave     | 4 * t Clk <sub>PER</sub> |                                    |      |       |

| t <sub>ssckw</sub> | SCK high/low width      | Slave     | 2 * t Clk <sub>PER</sub> |                                    |      | ns    |

| t <sub>SSCKR</sub> | SCK rise time           | Slave     |                          |                                    | 1600 |       |

| t <sub>SSCKF</sub> | SCK fall time           | Slave     |                          |                                    | 1600 |       |

| t <sub>SIS</sub>   | MOSI setup to SCK       | Slave     | 3                        |                                    |      |       |

| t <sub>SIH</sub>   | MOSI hold after SCK     | Slave     | t Clk <sub>PER</sub>     |                                    |      |       |

| t <sub>sss</sub>   | SS setup to SCK         | Slave     | 21                       |                                    |      |       |

| t <sub>SSH</sub>   | SS hold after SCK       | Slave     | 20                       |                                    |      |       |

| t <sub>sos</sub>   | MISO setup SCK          | Slave     |                          | 8                                  |      |       |

| t <sub>SOH</sub>   | MISO hold after SCK     | Slave     |                          | 13                                 |      |       |

| t <sub>soss</sub>  | MISO setup after SS low | Slave     |                          | 11                                 |      |       |

| t <sub>sosh</sub>  | MISO hold after SS high | Slave     |                          | 8                                  |      |       |

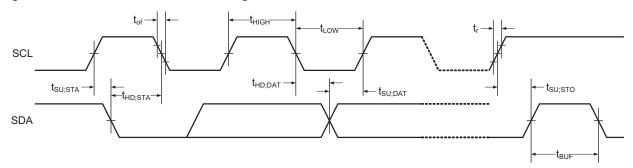

## 32.3.15 Two-wire Interface Characteristics

Table 32-87 on page 119 describes the requirements for devices connected to the Two-Wire Interface Bus. The Atmel AVR XMEGA Two-Wire Interface meets or exceeds these requirements under the noted conditions. Timing symbols refer to Figure 32-21.

Figure 32-21.Two-wire Interface Bus Timing

#### 32.4.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

Table 32-94. I/O Pin Characteristics

| Symbol                                                          | Parameter                               | Condition                    |                        | Min.                  | Тур.  | Max.                  | Units |

|-----------------------------------------------------------------|-----------------------------------------|------------------------------|------------------------|-----------------------|-------|-----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> / I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current             |                              |                        | -15                   |       | 15                    | mA    |

| V                                                               | High level input voltage                | V <sub>CC</sub> = 2.4 - 3.6V |                        | 0.7 * V <sub>CC</sub> |       | V <sub>CC</sub> + 0.5 |       |

| V <sub>IH</sub>                                                 | Trigit level input voltage              | V <sub>CC</sub> = 1.6 - 2.4V |                        | 0.8 * V <sub>CC</sub> |       | V <sub>CC</sub> + 0.5 |       |

| V                                                               | Low lovel input voltage                 | V <sub>CC</sub> = 2.4 - 3.6V |                        | -0.5                  |       | 0.3 * V <sub>CC</sub> |       |

| V <sub>IL</sub>                                                 | V <sub>IL</sub> Low level input voltage |                              |                        | -0.5                  |       | 0.2 * V <sub>CC</sub> |       |

|                                                                 | High level output voltage               | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -4mA | 2.6                   | 2.9   |                       | V     |

| V <sub>OH</sub>                                                 |                                         | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -3mA | 2.1                   | 2.6   |                       | V     |

|                                                                 |                                         | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -1mA | 1.4                   | 1.6   |                       |       |

|                                                                 | Low level output voltage                | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 8mA  |                       | 0.4   | 0.76                  |       |

| V <sub>OL</sub>                                                 |                                         | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 5mA  |                       | 0.3   | 0.64                  |       |

|                                                                 |                                         | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 3mA  |                       | 0.2   | 0.46                  |       |

| I <sub>IN</sub>                                                 | Input leakage current I/O pin           | T = 25°C                     |                        |                       | <0.01 | 1.0                   | μA    |

| R <sub>P</sub>                                                  | Pull/buss keeper resistor               |                              |                        |                       | 25    |                       | kΩ    |

Notes:

The sum of all  $I_{OH}$  for PORTA and PORTB must not exceed 100mA. The sum of all  $I_{OH}$  for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all  $I_{OH}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[6-7] on PORTF, PORTR, and PDI must not exceed 100mA.

The sum of all  $I_{OL}$  for PORTA and PORTB must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[6-7] on PORTF, PORTR, and PDI must not exceed 100mA.

Table 32-144. SPI Timing Characteristics and Requirements

| Symbol             | Parameter               | Condition | Min.                     | Тур.                               | Max. | Units |

|--------------------|-------------------------|-----------|--------------------------|------------------------------------|------|-------|

| t <sub>sck</sub>   | SCK period              | Master    |                          | (See Table 20-3 in XMEGA D manual) |      |       |

| t <sub>SCKW</sub>  | SCK high/low width      | Master    |                          | 0.5 * SCK                          |      |       |

| t <sub>SCKR</sub>  | SCK rise time           | Master    |                          | 2.7                                |      |       |

| t <sub>SCKF</sub>  | SCK fall time           | Master    |                          | 2.7                                |      |       |

| t <sub>MIS</sub>   | MISO setup to SCK       | Master    |                          | 10                                 |      |       |

| t <sub>MIH</sub>   | MISO hold after SCK     | Master    |                          | 10                                 |      |       |

| t <sub>MOS</sub>   | MOSI setup SCK          | Master    |                          | 0.5 * SCK                          |      |       |

| t <sub>MOH</sub>   | MOSI hold after SCK     | Master    |                          | 1                                  |      |       |

| t <sub>ssck</sub>  | Slave SCK Period        | Slave     | 4 * t Clk <sub>PER</sub> |                                    |      |       |

| t <sub>ssckw</sub> | SCK high/low width      | Slave     | 2 * t Clk <sub>PER</sub> |                                    |      | ns    |

| t <sub>SSCKR</sub> | SCK rise time           | Slave     |                          |                                    | 1600 |       |

| t <sub>SSCKF</sub> | SCK fall time           | Slave     |                          |                                    | 1600 |       |

| t <sub>SIS</sub>   | MOSI setup to SCK       | Slave     | 3                        |                                    |      |       |

| t <sub>SIH</sub>   | MOSI hold after SCK     | Slave     | t Clk <sub>PER</sub>     |                                    |      |       |

| t <sub>sss</sub>   | SS setup to SCK         | Slave     | 21                       |                                    |      |       |

| t <sub>SSH</sub>   | SS hold after SCK       | Slave     | 20                       |                                    |      |       |

| t <sub>sos</sub>   | MISO setup SCK          | Slave     |                          | 8                                  |      |       |

| t <sub>SOH</sub>   | MISO hold after SCK     | Slave     |                          | 13                                 |      |       |

| t <sub>soss</sub>  | MISO setup after SS low | Slave     |                          | 11                                 |      |       |

| t <sub>sosh</sub>  | MISO hold after SS high | Slave     |                          | 8                                  |      |       |

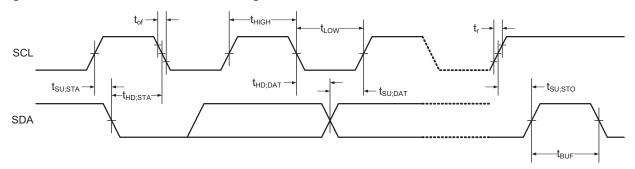

## 32.5.15 Two-wire Interface Characteristics

Table 32-145 on page 157 describes the requirements for devices connected to the Two-Wire Interface Bus. The Atmel AVR XMEGA Two-Wire Interface meets or exceeds these requirements under the noted conditions. Timing symbols refer to Figure 32-35.

Figure 32-35. Two-wire Interface Bus Timing

# 32.6.8 Bandgap and Internal 1.0V Reference Characteristics

Table 32-158. Bandgap and Internal 1.0V Reference Characteristics

| Symbol | Parameter                              | Condition                      | Min. | Тур.                         | Max. | Units |

|--------|----------------------------------------|--------------------------------|------|------------------------------|------|-------|

|        | Startun timo                           | As reference for ADC           |      | 1 Clk <sub>PER</sub> + 2.5µs |      |       |

|        | Startup time                           | As input voltage to ADC and AC |      | 1.5                          |      | μs    |

|        | Bandgap voltage                        |                                |      | 1.1                          |      | V     |

| INT1V  | Internal 1.00V reference               | T = 85°C, after calibration    | 0.99 | 1                            | 1.01 | V     |

|        | Variation over voltage and temperature | Calibrated at T = 85°C         |      | 2                            |      | %     |

# 32.6.9 Brownout Detection Characteristics

Table 32-159. Brownout Detection Characteristics (1)

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|

|                   | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 |       |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.9  |      |       |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      |       |

| V                 | BOD level 3 falling V <sub>CC</sub> |                 |      | 2.2  |      | V     |

| V <sub>BOT</sub>  | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      |       |

|                   | BOD level 5 falling V <sub>CC</sub> |                 |      | 2.6  |      |       |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      |       |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      |       |

| t                 | Detection time                      | Continuous mode |      | 0.4  |      | 116   |

| t <sub>BOD</sub>  |                                     | Sampled mode    |      | 1000 |      | μs    |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.0  |      | %     |

Note: 1. BOD is calibrated at 85°C within BOD level 0 values, and BOD level 0 is the default level.

# 32.6.10 External Reset Characteristics

Table 32-160. External Reset Characteristics

| Symbol           | Parameter                                | Condition                    | Min. | Тур.                   | Max. | Units |

|------------------|------------------------------------------|------------------------------|------|------------------------|------|-------|

| t <sub>EXT</sub> | Minimum reset pulse width                |                              | 1000 | 90                     |      | ns    |

| V                | V <sub>RST</sub> Reset threshold voltage | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.45 * V <sub>CC</sub> |      | V     |

| V RST            |                                          | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.42 * V <sub>CC</sub> |      |       |

| R <sub>RST</sub> | Reset pin pull-up resistor               |                              |      | 25                     |      | kΩ    |

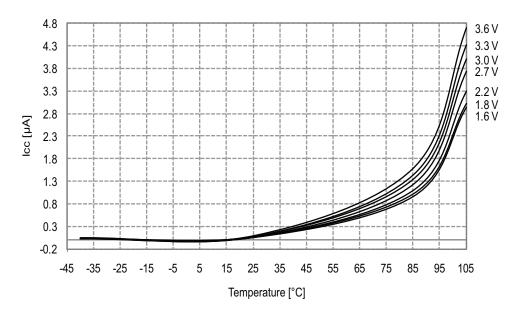

Figure 33-88. Power-down Mode Supply Current vs. Temperature

\*\*All functions disabled\*\*

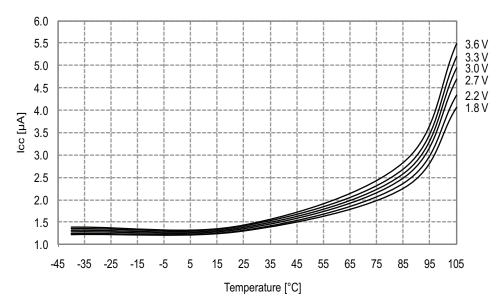

Figure 33-89. Power-down Mode Supply Current vs. Temperature

Watchdog and sampled BOD enabled and running from internal ULP oscillator

# 33.2.10 PDI Characteristics

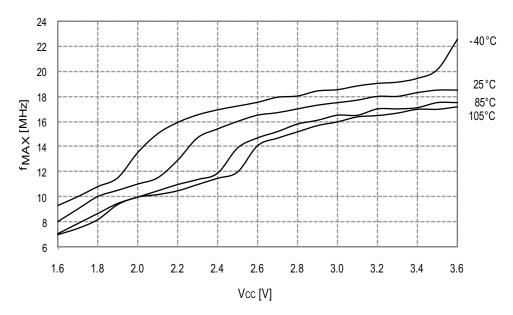

Figure 33-142. Maximum PDI Frequency vs.  $V_{\rm CC}$

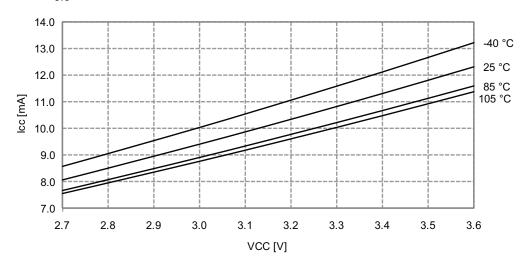

Figure 33-219. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 32MHz$  internal oscillator

# 33.4.1.2 Idle Mode Supply Current

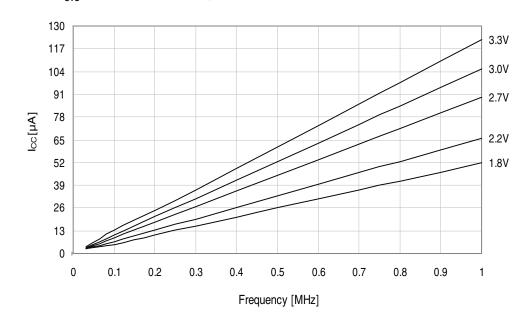

Figure 33-220.ldle Mode Supply Current vs. Frequency  $f_{SYS} = 0$  - 1MHz external clock,  $T = 25^{\circ}C$

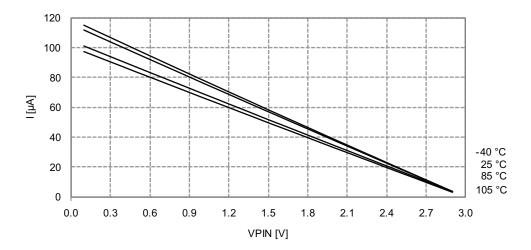

Figure 33-231.I/O Pin Pull-up Resistor Current vs. Input Voltage  $V_{CC}$  = 3.0V

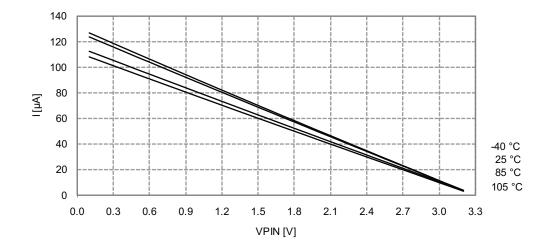

Figure 33-232.I/O Pin Pull-up Resistor Current vs. Input Voltage  $V_{CC}$  = 3.3V

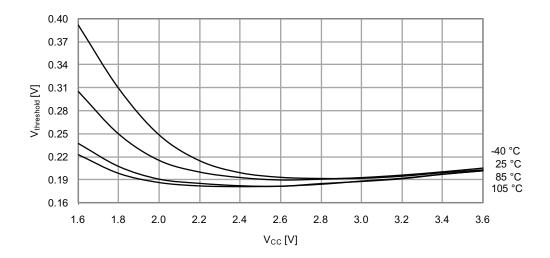

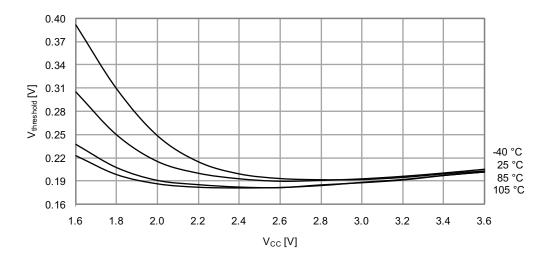

Figure 33-241.I/O Pin Input Hysteresis vs.  $V_{\rm CC}$

#### 33.4.3 ADC Characteristics

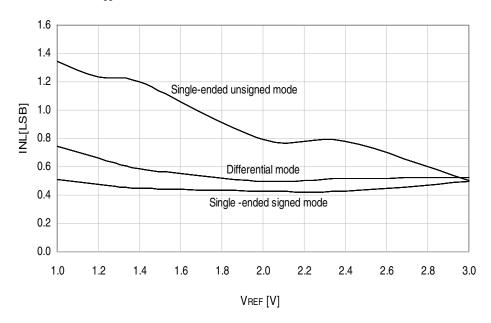

Figure 33-242.INL Error vs. External  $V_{REF}$  $T = 25 \, \text{C}, V_{CC} = 3.6 V, external reference}$

Figure 33-263.Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.3V$

144 126 108 90 RESET [µA] 72 54 -40 °C 36 25 °C 85 °C 18 105°C 0 0.0 0.3 0.6 0.9 1.2 1.5 1.8 2.1 2.4 2.7 3.0 3.3

$V_{\mathsf{RESET}}[\mathsf{V}]$

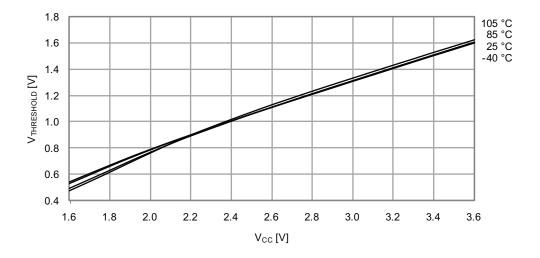

Figure 33-264.Reset Pin Input Threshold Voltage vs.  $V_{CC}$  $V_{IH}$  - Reset pin read as "1"

Figure 33-381.I/O Pin Input Hysteresis vs. V<sub>CC</sub>

# 33.6.3 ADC Characteristics

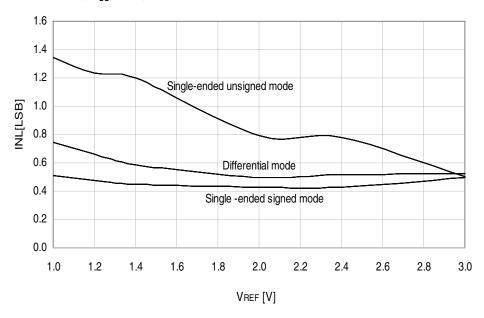

Figure 33-382. INL Error vs. External  $V_{REF}$  $T = 25 \, \text{C}, V_{CC} = 3.6 V, \text{ external reference}$

# Problem fix/workaround

The TxD pin direction can be set to input using the Port DIR register. Be advised that setting the Port DIR register to input will be immediate. Ongoing transmissions will be truncated.

## 34.2.9 Rev. A

Not sampled.

#### Problem fix/workaround

Table 34-4. Configure PWM and CWCM According to this Table:

| PGM | CWCM | Description           |

|-----|------|-----------------------|

| 0   | 0    | PGM and CWCM disabled |

| 0   | 1    | PGM enabled           |

| 1   | 0    | PGM and CWCM enabled  |

| 1   | 1    | PGM enabled           |

## 11. PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/workaround

Do a write to any AWeX I/O register to re-enable the output.

## 12. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the  $V_{CC}$  voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until  $V_{CC}$  is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/workaround

Do not set the BOD level higher than  $V_{CC}$  even if the BOD is not used.

## 13. EEPROM page buffer always written when NVM DATA0 is written

If the EEPROM is memory mapped, writing to NVM DATA0 will corrupt data in the EEPROM page buffer.

## Problem fix/workaround

Before writing to NVM DATA0, for example when doing software CRC or flash page buffer write, check if EEPROM page buffer active loading flag (EELOAD) is set. Do not write NVM DATA0 when EELOAD is set.

#### 14. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

## Problem fix/workaround

None.

#### 15. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

## Problem fix/workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (that is, connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

## 16. NMI Flag for Crystal Oscillator Failure automatically cleared

NMI flag for Crystal Oscillator Failure (XOSCFDIF) will be automatically cleared when executing the NMI interrupt handler.

#### Problem fix/workaround

This device revision has only one NMI interrupt source, so checking the interrupt source in software is not required.

#### 17. RTC Counter value not correctly read after sleep

If the RTC is set to wake up the device on RTC Overflow and bit 0 of RTC CNT is identical to bit 0 of RTC PER as the device is entering sleep, the value in the RTC count register can not be read correctly within the first prescaled RTC clock cycle after wake-up. The value read will be the same as the value in the register when entering sleep.

The same applies if RTC Compare Match is used as wake-up source.

#### Problem fix/workaround

Wait at least one prescaled RTC clock cycle before reading the RTC CNT value.

#### 18. Pending asynchronous RTC-interrupts will not wake up device

Asynchronous Interrupts from the Real-Time-Counter that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again.

#### Problem fix/workaround

None.

#### 19. TWI Transmit collision flag not cleared on repeated start

The TWI transmit collision flag should be automatically cleared on start and repeated start, but is only cleared on start.

#### Problem fix/workaround

Clear the flag in software after address interrupt.

## 20. Clearing TWI Stop Interrupt Flag may lock the bus

If software clears the STOP Interrupt Flag (APIF) on the same Peripheral Clock cycle as the hardware sets this flag due to a new address received, CLKHOLD is not cleared and the SCL line is not released. This will lock the bus.

#### Problem fix/workaround

Check if the bus state is IDLE. If this is the case, it is safe to clear APIF. If the bus state is not IDLE, wait for the SCL pin to be low before clearing APIF.

## Code:

#### Problem fix/workaround

Check if the bus state is IDLE. If this is the case, it is safe to clear APIF. If the bus state is not IDLE, wait for the SCL pin to be low before clearing APIF.

#### Code:

```

/* Only clear the interrupt flag if within a "safe zone". */

while ( /* Bus not IDLE: */

((COMMS TWI.MASTER.STATUS & TWI MASTER BUSSTATE gm) !=

TWI MASTER BUSSTATE IDLE gc)) &&

/* SCL not held by slave: */

! (COMMS TWI.SLAVE.STATUS & TWI SLAVE CLKHOLD bm)

)

{

/* Ensure that the SCL line is low */

if ( !(COMMS PORT.IN & PIN1 bm) )

if (!(COMMS PORT.IN & PIN1 bm))

break;

/* Check for an pending address match interrupt */

if ( ! (COMMS TWI.SLAVE.STATUS & TWI SLAVE CLKHOLD bm) )

/* Safely clear interrupt flag */

COMMS TWI.SLAVE.STATUS |= (uint8 t) TWI SLAVE APIF bm;

}

```

# 22. TWI START condition at bus timeout will cause transaction to be dropped

If Bus Timeout is enabled and a timeout occurs on the same Peripheral Clock cycle as a START is detected, the transaction will be dropped.

#### Problem fix/workaround

None.

#### 23. TWI Data Interrupt Flag erroneously read as set

When issuing the TWI slave response command CMD=0b11, it takes one Peripheral Clock cycle to clear the data interrupt flag (DIF). A read of DIF directly after issuing the command will show the DIF still set.

## Problem fix/workaround

Add one NOP instruction before checking DIF.

#### 24. WDR instruction inside closed window will not issue reset

When a WDR instruction is execute within one ULP clock cycle after updating the window control register, the counter can be cleared without giving a system reset.

#### Problem fix/workaround

Wait at least one ULP clock cycle before executing a WDR instruction.