Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 192KB (96K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega192d3-anr |

after reset, and the initial value is the highest address of the internal SRAM. If the SP is changed, it must be set to point above address 0x2000, and it must be defined before any subroutine calls are executed or before interrupts are enabled.

During interrupts or subroutine calls, the return address is automatically pushed on the stack. The return address can be two or three bytes, depending on program memory size of the device. For devices with 128KB or less of program memory, the return address is two bytes, and hence the stack pointer is decremented/incremented by two. For devices with more than 128KB of program memory, the return address is three bytes, and hence the SP is decremented/incremented by three. The return address is popped off the stack when returning from interrupts using the RETI instruction, and from subroutine calls using the RET instruction.

The SP is decremented by one when data are pushed on the stack with the PUSH instruction, and incremented by one when data is popped off the stack using the POP instruction.

To prevent corruption when updating the stack pointer from software, a write to SPL will automatically disable interrupts for up to four instructions or until the next I/O memory write.

After reset the stack pointer is initialized to the highest address of the SRAM. See Figure 7-2 on page 16.

## 6.8 Register File

The register file consists of 32 \* 8-bit general purpose working registers with single clock cycle access time. The register file supports the following input/output schemes:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

Six of the 32 registers can be used as three 16-bit address register pointers for data space addressing, enabling efficient address calculations. One of these address pointers can also be used as an address pointer for lookup tables in flash program memory.

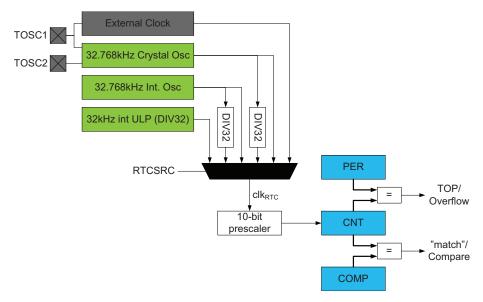

## 19. RTC – 16-bit Real-Time Counter

### 19.1 Features

- 16-bit resolution

- Selectable clock source

- 32.768kHz external crystal

- External clock

- 32.768kHz internal oscillator

- 32kHz internal ULP oscillator

- Programmable 10-bit clock prescaling

- One compare register

- One period register

- Clear counter on period overflow

- Optional interrupt/event on overflow and compare match

## 19.2 Overview

The 16-bit real-time counter (RTC) is a counter that typically runs continuously, including in low-power sleep modes, to keep track of time. It can wake up the device from sleep modes and/or interrupt the device at regular intervals.

The reference clock is typically the 1.024kHz output from a high-accuracy crystal of 32.768kHz, and this is the configuration most optimized for low power consumption. The faster 32.768kHz output can be selected if the RTC needs a resolution higher than 1ms. The RTC can also be clocked from an external clock signal, the 32.768kHz internal oscillator or the 32kHz internal ULP oscillator.

The RTC includes a 10-bit programmable prescaler that can scale down the reference clock before it reaches the counter. A wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the maximum resolution is 30.5µs, and time-out periods can range up to 2000 seconds. With a resolution of 1s, the maximum timeout period is more than18 hours (65536 seconds). The RTC can give a compare interrupt and/or event when the counter equals the compare register value, and an overflow interrupt and/or event when it equals the period register value.

Figure 19-1. Real-time Counter Overview

# 32.1.3 Current Consumption

Table 32-4. Current Consumption for Active Mode and Sleep Modes

| Symbol          | Parameter                    | Condition                             |                        | Min. | Тур. | Max. | Units |

|-----------------|------------------------------|---------------------------------------|------------------------|------|------|------|-------|

|                 |                              | 20kHz Est Clk                         | V <sub>CC</sub> = 1.8V |      | 50   |      |       |

|                 |                              | 32kHz, Ext. Clk                       | V <sub>CC</sub> = 3.0V |      | 130  |      | μА    |

|                 | Active power consumption (1) | 1MLI- Evt Olk                         | V <sub>CC</sub> = 1.8V |      | 215  |      |       |

|                 |                              | 1MHz, Ext. Clk                        | V <sub>CC</sub> = 3.0V |      | 475  |      |       |

|                 |                              | 2MHz, Ext. Clk                        | V <sub>CC</sub> = 1.8V |      | 445  | 600  |       |

|                 |                              | ZIVII IZ, LAL. GIR                    | V <sub>CC</sub> = 3.0V |      | 0.95 | 1.5  | mA    |

|                 |                              | 32MHz, Ext. Clk                       | V <sub>CC</sub> - 3.0V |      | 7.8  | 12.0 | ША    |

|                 |                              | 32kHz, Ext. Clk                       | V <sub>CC</sub> = 1.8V |      | 2.8  |      |       |

|                 | Idle power consumption (1)   | JZNI IZ, EXt. OIK                     | V <sub>CC</sub> = 3.0V |      | 3    |      | μΑ    |

|                 |                              | 1MHz, Ext. Clk                        | V <sub>CC</sub> = 1.8V |      | 46   |      |       |

|                 |                              |                                       | V <sub>CC</sub> = 3.0V |      | 92   |      |       |

|                 |                              | 2MHz, Ext. Clk                        | V <sub>CC</sub> = 1.8V |      | 93   | 225  |       |

|                 |                              |                                       | V <sub>CC</sub> = 3.0V |      | 184  | 350  |       |

| I <sub>CC</sub> |                              | 32MHz, Ext. Clk                       | VCC - 0.0V             |      | 2.9  | 5.0  | mA    |

|                 | Power-down power             | T = 25°C                              | V <sub>CC</sub> = 3.0V |      | 0.07 | 1.0  |       |

|                 |                              | T = 85°C                              |                        |      | 1.3  | 5.0  |       |

|                 |                              | T = 105°C                             |                        |      | 4.0  | 8.0  |       |

|                 | consumption                  | WDT and sampled BOD enabled, T = 25°C |                        |      | 1.3  | 2.0  |       |

|                 |                              | WDT and sampled BOD enabled, T = 85°C | V <sub>CC</sub> = 3.0V |      | 2.6  | 6.0  |       |

|                 |                              | WDT and sampled BOD enabled, T= 105°C |                        |      | 5.0  | 10   |       |

|                 |                              | RTC from ULP clock, WDT and sampled   | V <sub>CC</sub> = 1.8V |      | 1.7  |      | μA    |

|                 |                              | BOD enabled, T = 25°C                 | V <sub>CC</sub> = 3.0V |      | 1.8  |      |       |

|                 | Power-save power             | RTC from 1.024kHz low power 32.768kHz | V <sub>CC</sub> = 1.8V |      | 0.5  | 2.0  |       |

|                 | consumption (2)              | TOSC, T = 25°C                        | V <sub>CC</sub> = 3.0V |      | 0.7  | 2.0  |       |

|                 |                              | RTC from low power 32.768kHz TOSC,    | V <sub>CC</sub> = 1.8V |      | 0.9  | 3.0  |       |

|                 |                              | T = 25°C                              | V <sub>CC</sub> = 3.0V |      | 1.2  | 3.0  |       |

|                 | Reset power consumption      | Current through RESET pin substracted | V <sub>CC</sub> = 3.0V |      | 120  |      |       |

Notes:

<sup>1.</sup> All Power Reduction Registers set.

<sup>2.</sup> Maximum limits are based on characterization, and not tested in production.

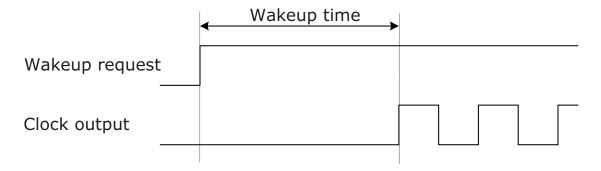

# 32.1.4 Wake-up Time from Sleep Modes

Table 32-6. Device Wake-up Time from Sleep Modes with Various System Clock Sources

| Symbol              | Parameter                                                        | Condition                     | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|---------------------|------------------------------------------------------------------|-------------------------------|------|---------------------|------|-------|

|                     | Wake-up time from idle,<br>standby, and extended standby<br>mode | External 2MHz clock           |      | 2.0                 |      |       |

|                     |                                                                  | 32.768kHz internal oscillator |      | 125                 |      |       |

| <sup>‡</sup> wakeup |                                                                  | 2MHz internal oscillator      |      | 2.0                 |      |       |

|                     |                                                                  | 32MHz internal oscillator     |      | 0.2                 |      |       |

|                     | Wake-up time from power-save and power-down mode                 | External 2MHz clock           |      | 4.6                 |      | μs    |

|                     |                                                                  | 32.768kHz internal oscillator |      | 330                 |      |       |

|                     |                                                                  | 2MHz internal oscillator      |      | 9.5                 |      |       |

|                     |                                                                  | 32MHz internal oscillator     |      | 5.6                 |      |       |

Note:

Figure 32-2. Wake-up Time Definition

<sup>1.</sup> The wake-up time is the time from the wake-up request is given until the peripheral clock is available on pin, see Figure 32-2. All peripherals and modules start execution from the first clock cycle, expect the CPU that is halted for four clock cycles before program execution starts.

**Table 32-69. Gain Stage Characteristics**

| Symbol              | Parameter                    | Condition               | Min. | Тур. | Max.                   | Units                     |

|---------------------|------------------------------|-------------------------|------|------|------------------------|---------------------------|

| R <sub>in</sub>     | Input resistance             | Switched in normal mode |      | 4.0  |                        | kΩ                        |

| C <sub>sample</sub> | Input capacitance            | Switched in normal mode |      | 4.4  |                        | pF                        |

|                     | Signal range                 | Gain stage output       | 0    |      | AV <sub>CC</sub> - 0.6 | V                         |

|                     | Propagation delay            | ADC conversion rate     | 1/2  | 1    | 3                      | Clk <sub>ADC</sub> cycles |

|                     | Clock frequency              | Same as ADC             | 100  |      | 1800                   | kHz                       |

|                     | Gain error                   | 0.5x gain, normal mode  |      | -1   |                        |                           |

|                     |                              | 1x gain, normal mode    |      | -1   |                        | %                         |

|                     |                              | 8x gain, normal mode    |      | -1   |                        | /0                        |

|                     |                              | 64x gain, normal mode   |      | 5    |                        |                           |

|                     | Offset error, input referred | 0.5x gain, normal mode  |      | 10   |                        |                           |

|                     |                              | 1x gain, normal mode    |      | 5    |                        | mV                        |

|                     |                              | 8x gain, normal mode    |      | -20  |                        | IIIV                      |

|                     |                              | 64x gain, normal mode   |      | -126 |                        |                           |

# 32.3.7 Analog Comparator Characteristics

**Table 32-70. Analog Comparator Characteristics**

| Symbol             | Parameter                                 | Condition                        | Min. | Тур. | Max.             | Units |

|--------------------|-------------------------------------------|----------------------------------|------|------|------------------|-------|

| V <sub>off</sub>   | Input offset voltage                      |                                  |      | 10   |                  | mV    |

| I <sub>lk</sub>    | Input leakage current                     |                                  |      | <10  | 50               | nA    |

|                    | Input voltage range                       |                                  | -0.1 |      | AV <sub>CC</sub> | V     |

|                    | AC startup time                           |                                  |      | 50   |                  | μs    |

| V <sub>hys1</sub>  | Hysteresis, none                          | V <sub>CC</sub> = 1.6V - 3.6V    |      | 0    |                  |       |

| V <sub>hys2</sub>  | Hysteresis, small                         | V <sub>CC</sub> = 1.6V - 3.6V    |      | 15   |                  | mV    |

| V <sub>hys3</sub>  | Hysteresis, large                         | V <sub>CC</sub> = 1.6V - 3.6V    |      | 30   |                  |       |

| +                  | Propagation delay                         | $V_{CC} = 3.0V, T = 85^{\circ}C$ |      | 20   | 90               | ns    |

| t <sub>delay</sub> | 1 Topagation delay                        | V <sub>CC</sub> = 3.0V           |      | 17   |                  | 113   |

|                    | 64-level voltage scaler                   | Integral non-linearity (INL)     |      | 0.3  | 0.5              | lsb   |

|                    | Current source accuracy after calibration |                                  |      | 5    |                  | %     |

|                    | Current source calibration range          | Single mode                      | 4    |      | 6                | μA    |

## 32.6.11 Power-on Reset Characteristics

Table 32-161. Power-on Reset Characteristics

| Symbol                           | Parameter                                     | Condition                                | Min. | Тур. | Max. | Units |

|----------------------------------|-----------------------------------------------|------------------------------------------|------|------|------|-------|

| V (1) DOD through                | DOR throshold voltage folling V               | V <sub>CC</sub> falls faster than 1V/ms  | 0.4  | 1.0  |      |       |

| V <sub>POT-</sub> <sup>(1)</sup> | POR threshold voltage falling V <sub>CC</sub> | V <sub>CC</sub> falls at 1V/ms or slower | 0.8  | 1.3  |      | V     |

| V <sub>POT+</sub>                | POR threshold voltage rising $V_{\rm CC}$     |                                          |      | 1.3  | 1.59 |       |

Note:

# 32.6.12 Flash and EEPROM Memory Characteristics

Table 32-162. Endurance and Data Retention

| Symbol | Parameter | Condition          |       | Min. | Тур. | Max. | Units |

|--------|-----------|--------------------|-------|------|------|------|-------|

|        |           |                    | 25°C  | 10K  |      |      | Cycle |

|        |           |                    | 85°C  | 10K  |      |      |       |

|        | Flash     |                    | 105°C | 2K   |      |      |       |

|        | riasii    | Data retention     | 25°C  | 100  |      |      | Year  |

|        |           |                    | 85°C  | 25   |      |      |       |

|        |           |                    | 105°C | 10   |      |      |       |

|        |           | Write/Erase cycles | 25°C  | 100K |      |      | Cycle |

|        |           |                    | 85°C  | 100K |      |      |       |

|        | EEPROM    |                    | 105°C | 30K  |      |      |       |

|        |           | Data retention     | 25°C  | 100  |      |      |       |

|        |           |                    | 85°C  | 25   |      |      | Year  |

|        |           |                    | 105°C | 10   |      |      |       |

Table 32-163. Programming Time

| Symbol | Parameter         | Condition                   | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|--------|-------------------|-----------------------------|------|---------------------|------|-------|

|        | Chip erase (2)    | 384KB Flash, EEPROM         |      | 130                 |      |       |

|        | Application erase | Section erase               |      | 6                   |      |       |

|        | Flash             | Page erase                  |      | 6                   |      |       |

|        |                   | Page write                  |      | 6                   |      | ms    |

|        |                   | Atomic page erase and write |      | 12                  |      | 1115  |

|        |                   | Page erase                  |      | 6                   |      |       |

|        |                   | Page write                  |      | 6                   |      |       |

|        |                   | Atomic page erase and write |      | 12                  |      |       |

Notes:

<sup>2.</sup> EEPROM is not erased if the EESAVE fuse is programmed.

<sup>1.</sup>  $V_{POT-}$  values are only valid when BOD is disabled. When BOD is enabled  $V_{POT-} = V_{POT+}$ .

<sup>1.</sup> Programming is timed from the 2MHz internal oscillator.

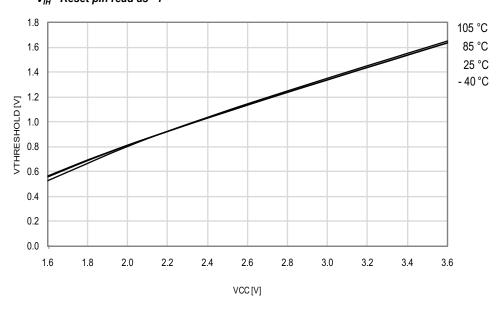

Figure 33-124. Reset Pin Input Threshold Voltage vs.  $V_{CC}$  $V_{IH}$  - Reset pin read as "1"

## 33.2.8 Oscillator Characteristics

## 33.2.8.1 Ultra Low-Power Internal Oscillator

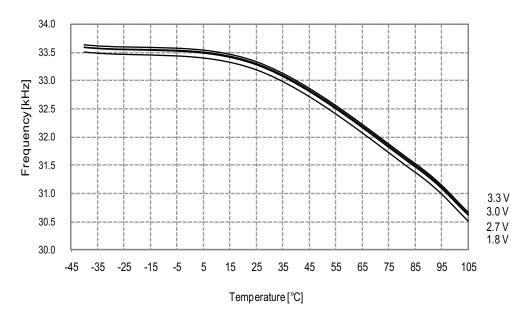

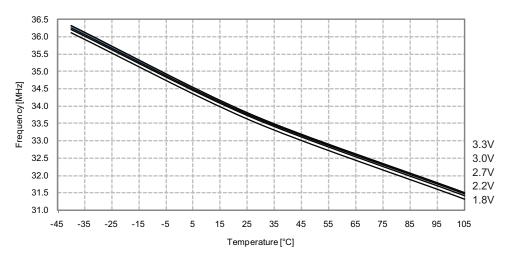

Figure 33-125. Ultra Low-Power Internal Oscillator Frequency vs. Temperature

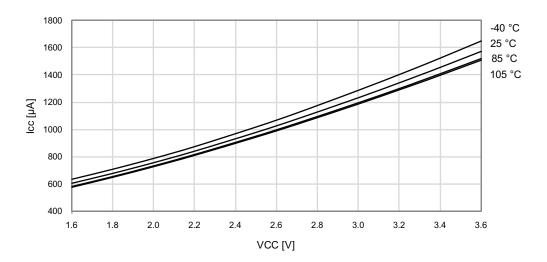

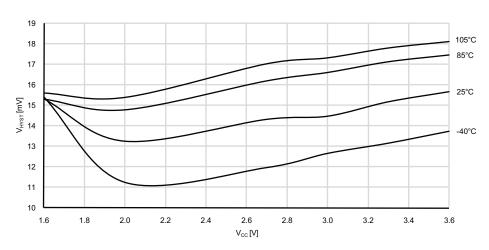

Figure 33-155. Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 32MHz$  internal oscillator prescaled to 8MHz

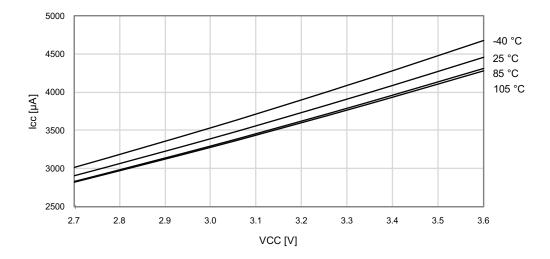

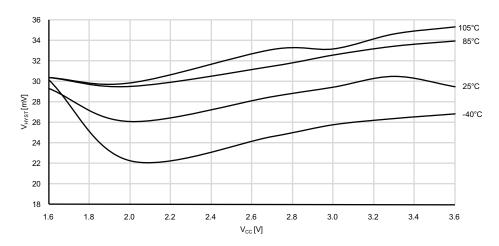

Figure 33-156. Idle Mode Current vs.  $V_{CC}$  $f_{SYS}$  = 32MHz internal oscillator

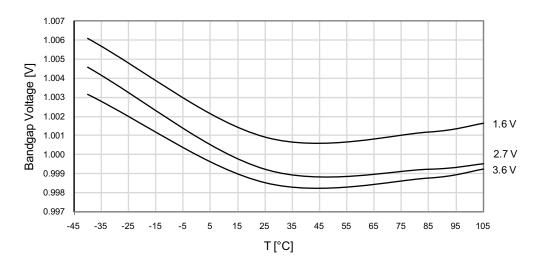

## 33.4.5 Internal 1.0V Reference Characteristics

Figure 33-257.ADC Internal 1.0V Reference vs. Temperature

## 33.4.6 BOD Characteristics

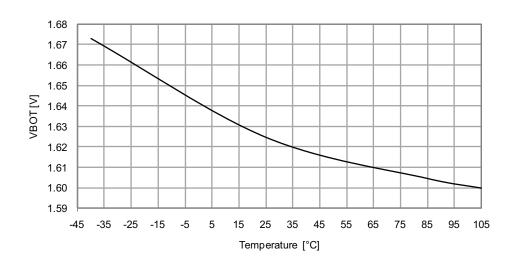

Figure 33-258.BOD Thresholds vs. Temperature BOD level = 1.6V

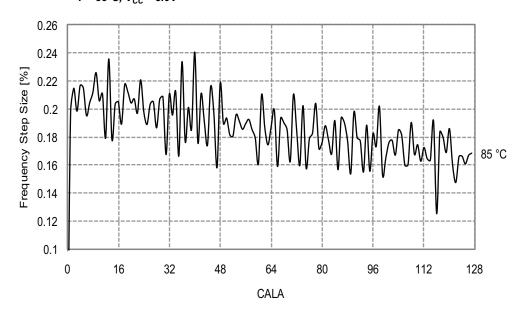

Figure 33-275. 32MHz Internal Oscillator CALA Calibration Step Size  $T=85^{\circ}C,\ V_{CC}=3.0V$

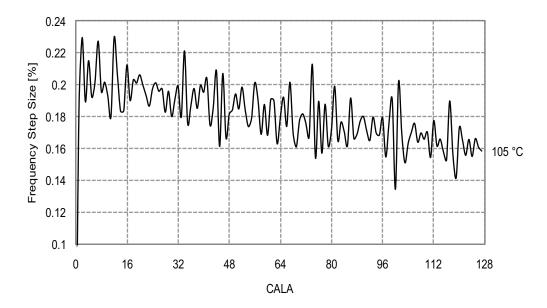

Figure 33-276. 32MHz Internal Oscillator CALA Calibration Step Size  $T=105^{\circ}C$ ,  $V_{CC}=3.0V$

# 33.5 Atmel ATxmega256D3

## 33.5.1 Current Consumption

## 33.5.1.1 Active Mode Supply Current

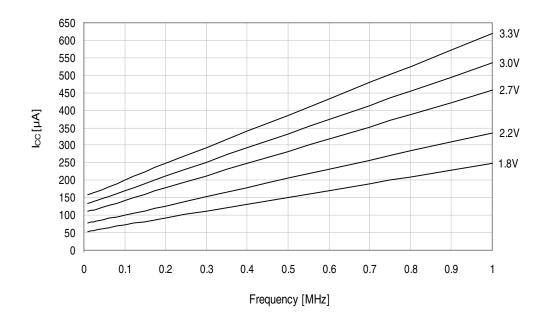

Figure 33-283. Active Supply Current vs. Frequency  $f_{SYS} = 0 - 1MHz$  external clock,  $T = 25^{\circ}C$

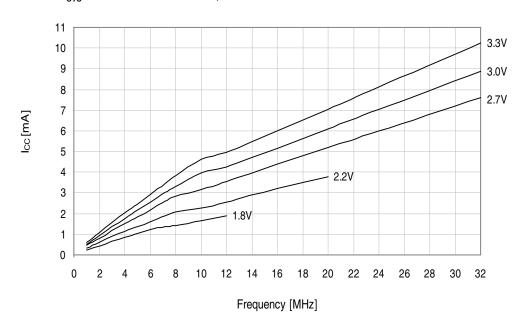

Figure 33-284. Active Supply Current vs. Frequency  $f_{SYS} = 1 - 32MHz$  external clock,  $T = 25^{\circ}C$

## 33.5.2.2 Output Voltage vs. Sink/Source Current

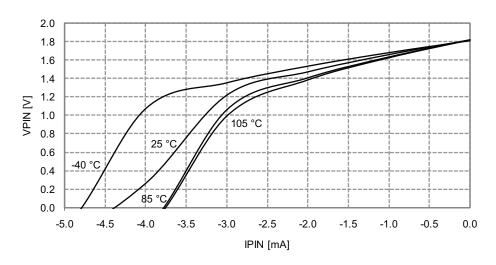

Figure 33-303.I/O Pin Output Voltage vs. Source Current

$V_{CC} = 1.8V$

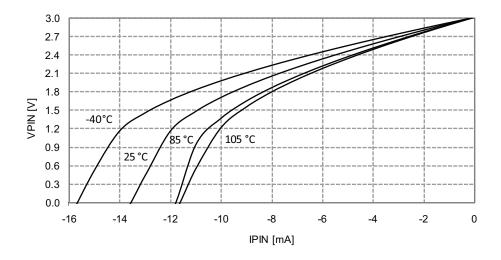

Figure 33-304.I/O Pin Output Voltage vs. Source Current

$V_{CC} = 3.0V$

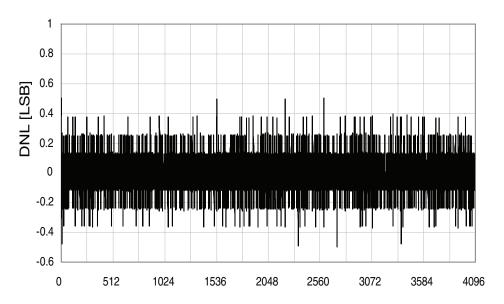

Figure 33-317.DNL Error vs. Input Code

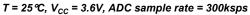

Figure 33-318. Gain Error vs.  $\mathbf{V}_{\text{REF}}$

### 33.5.8 Oscillator Characteristics

### 33.5.8.1 Ultra Low-Power Internal Oscillator

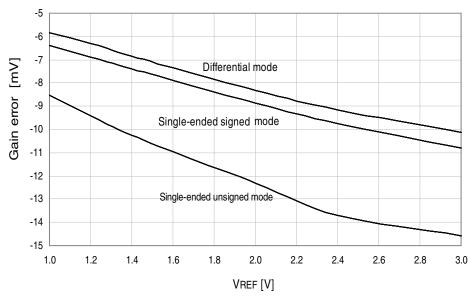

Figure 33-335. Ultra Low-Power Internal Oscillator Frequency vs. Temperature

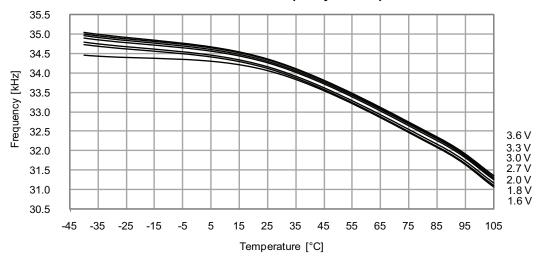

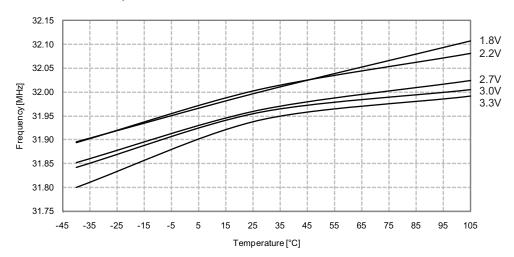

### 33.5.8.2 32.768kHz Internal Oscillator

Figure 33-336. 32.768kHz Internal Oscillator Frequency vs. Temperature

### 33.5.8.4 32MHz Internal Oscillator

Figure 33-341. 32MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

Figure 33-342. 32MHz Internal Oscillator Frequency vs. Temperature DFLL enabled, from the 32.768kHz internal oscillator

# 33.6.4 Analog Comparator Characteristics

Figure 33-393. Analog Comparator Hysteresis vs. V<sub>CC</sub> Small hysteresis

Figure 33-394. Analog Comparator Hysteresis vs. V<sub>CC</sub> *Large hysteresis*

#### Problem fix/workaround

Check if the bus state is IDLE. If this is the case, it is safe to clear APIF. If the bus state is not IDLE, wait for the SCL pin to be low before clearing APIF.

#### Code:

```

/* Only clear the interrupt flag if within a "safe zone". */

while ( /* Bus not IDLE: */

((COMMS TWI.MASTER.STATUS & TWI MASTER BUSSTATE gm) !=

TWI MASTER BUSSTATE IDLE gc)) &&

/* SCL not held by slave: */

! (COMMS TWI.SLAVE.STATUS & TWI SLAVE CLKHOLD bm)

)

{

/* Ensure that the SCL line is low */

if ( !(COMMS PORT.IN & PIN1 bm) )

if (!(COMMS PORT.IN & PIN1 bm))

break;

/* Check for an pending address match interrupt */

if ( ! (COMMS TWI.SLAVE.STATUS & TWI SLAVE CLKHOLD bm) )

/* Safely clear interrupt flag */

COMMS TWI.SLAVE.STATUS |= (uint8 t) TWI SLAVE APIF bm;

}

```

### 22. TWI START condition at bus timeout will cause transaction to be dropped

If Bus Timeout is enabled and a timeout occurs on the same Peripheral Clock cycle as a START is detected, the transaction will be dropped.

### Problem fix/workaround

None.

### 23. TWI Data Interrupt Flag erroneously read as set

When issuing the TWI slave response command CMD=0b11, it takes one Peripheral Clock cycle to clear the data interrupt flag (DIF). A read of DIF directly after issuing the command will show the DIF still set.

## Problem fix/workaround

Add one NOP instruction before checking DIF.

### 24. WDR instruction inside closed window will not issue reset

When a WDR instruction is execute within one ULP clock cycle after updating the window control register, the counter can be cleared without giving a system reset.

### Problem fix/workaround

Wait at least one ULP clock cycle before executing a WDR instruction.

### 25. Non available functions and options

The below function and options are not available. Writing to any registers or fuse to try and enable or configure these functions or options will have no effect, and will be as writing to a reserved address location.

- TWIE, the TWI module on PORTE

- TWI SDAHOLD option in the TWI CTRL register is one bit

#### 34.4.8 Rev. B

- Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously

- VCC voltage scaler for AC is non-linear

- ADC gain stage cannot be used for single conversion

- ADC has increased INL error for some operating conditions

- ADC gain stage output range is limited to 2.4V

- ADC Event on compare match non-functional

- ADC propagation delay is not correct when 8x 64x gain is used

- Bandgap measurement with the ADC is non-functional when VCC is below 2.7V

- Accuracy lost on first three samples after switching input to ADC gain stage

- Configuration of PGM and CWCM not as described in the XMEGA D Manual

- PWM is not restarted properly after a fault in cycle-by-cycle mode

- BOD will be enabled at any reset

- EEPROM page buffer always written when NVM DATA0 is written

- Pending full asynchronous pin change interrupts will not wake the device

- Pin configuration does not affect Analog Comparator Output

- NMI Flag for Crystal Oscillator Failure automatically cleared

- Writing EEPROM or Flash while reading any of them will not work

- RTC Counter value not correctly read after sleep

- Pending asynchronous RTC-interrupts will not wake up device

- TWI Transmit collision flag not cleared on repeated start

- Clearing TWI Stop Interrupt Flag may lock the bus

- TWI START condition at bus timeout will cause transaction to be dropped

- TWI Data Interrupt Flag (DIF) erroneously read as set

- WDR instruction inside closed window will not issue reset

- Non available functions and options

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

### 1. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for another AC, the first comparator will be affected for up to 1µs and could potentially give a wrong comparison result.

## Problem fix/workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

### 2. VCC voltage scaler for AC is non-linear

The 6-bit VCC voltage scaler in the Analog Comparators is non-linear.

#### 34.5.5 Rev. E

- Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously

- V<sub>CC</sub> voltage scaler for AC is non-linear

- ADC gain stage cannot be used for single conversion

- ADC has increased INL error for some operating conditions

- ADC gain stage output range is limited to 2.4V

- ADC Event on compare match non-functional

- ADC propagation delay is not correct when 8x 64x gain is used

- Bandgap measurement with the ADC is non-functional when V<sub>CC</sub> is below 2.7V

- Accuracy lost on first three samples after switching input to ADC gain stage

- Configuration of PGM and CWCM not as described in the XMEGA D Manual

- PWM is not restarted properly after a fault in cycle-by-cycle mode

- BOD will be enabled at any reset

- EEPROM page buffer always written when NVM DATA0 is written

- Pending full asynchronous pin change interrupts will not wake the device

- Pin configuration does not affect Analog Comparator Output

- NMI Flag for Crystal Oscillator Failure automatically cleared

- RTC Counter value not correctly read after sleep

- Pending asynchronous RTC-interrupts will not wake up device

- TWI Transmit collision flag not cleared on repeated start

- Clearing TWI Stop Interrupt Flag may lock the bus

- TWI START condition at bus timeout will cause transaction to be dropped

- TWI Data Interrupt Flag (DIF) erroneously read as set

- WDR instruction inside closed window will not issue reset

- Non available functions and options

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

- Disabling the USART transmitter does not automatically set the TxD pin direction to input

### 1. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for another AC, the first comparator will be affected for up to 1µs and could potentially give a wrong comparison result.

### Problem fix/workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

### 2. V<sub>CC</sub> voltage scaler for AC is non-linear

The 6-bit V<sub>CC</sub> voltage scaler in the Analog Comparators is non-linear.

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8134Q-AVR-ATxmega32D3-64D3-128D3-192D3-256D3-384D3-Datasheet \_10/2015.

$Atmel \ \ Ogo and combinations thereof, AVR^{@}, Enabling \ Unlimited \ Possibilities^{@}, XMEGA^{@}, QTouch^{@}, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.$

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL MEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.