Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 192KB (96K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega192d3-mnr |

|                            |                                                                            |

## 6. AVR CPU

## 6.1 Features

- 8/16-bit, high-performance Atmel AVR RISC CPU

- 137 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack pointer accessible in I/O memory space

- Direct addressing of up to 16MB of program memory and 16MB of data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Efficient support for 8-, 16-, and 32-bit arithmetic

- Configuration change protection of system-critical features

## 6.2 Overview

All Atmel AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 28.

## 6.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to <a href="https://www.atmel.com/avr">www.atmel.com/avr</a>.

## 11.4 Reset Sources

#### 11.4.1 Power-on Reset

A power-on reset (POR) is generated by an on-chip detection circuit. The POR is activated when the  $V_{CC}$  rises and reaches the POR threshold voltage ( $V_{POT}$ ), and this will start the reset sequence.

The POR is also activated to power down the device properly when the  $V_{CC}$  falls and drops below the  $V_{POT}$  level.

The  $V_{POT}$  level is higher for falling  $V_{CC}$  than for rising  $V_{CC}$ . Consult the datasheet for POR characteristics data.

#### 11.4.2 Brownout Detection

The on-chip brownout detection (BOD) circuit monitors the V<sub>CC</sub> level during operation by comparing it to a fixed, programmable level that is selected by the BODLEVEL fuses. If disabled, BOD is forced on at the lowest level during chip erase and when the PDI is enabled.

#### 11.4.3 External Reset

The external reset circuit is connected to the external  $\overline{RESET}$  pin. The external reset will trigger when the  $\overline{RESET}$  pin is driven below the  $\overline{RESET}$  pin threshold voltage,  $V_{RST}$ , for longer than the minimum pulse period,  $t_{EXT}$ . The reset will be held as long as the pin is kept low. The  $\overline{RESET}$  pin includes an internal pull-up resistor.

## 11.4.4 Watchdog Reset

The watchdog timer (WDT) is a system function for monitoring correct program operation. If the WDT is not reset from the software within a programmable timeout period, a watchdog reset will be given. The watchdog reset is active for one to two clock cycles of the 2MHz internal oscillator. For more details see "WDT – Watchdog Timer" on page 27.

#### 11.4.5 Software Reset

The software reset makes it possible to issue a system reset from software by writing to the software reset bit in the reset control register. The reset will be issued within two CPU clock cycles after writing the bit. It is not possible to execute any instruction from when a software reset is requested until it is issued.

## 11.4.6 Program and Debug Interface Reset

The program and debug interface reset contains a separate reset source that is used to reset the device during external programming and debugging. This reset source is accessible only from external debuggers and programmers.

# 16. TC2 – Timer/Counter Type 2

## 16.1 Features

- Eight 8-bit timer/counters

- Four Low-byte timer/counter

- Four High-byte timer/counter

- Up to eight compare channels in each Timer/Counter 2

- Four compare channels for the low-byte timer/counter

- Four compare channels for the high-byte timer/counter

- Waveform generation

- Single slope pulse width modulation

- Timer underflow interrupts/events

- One compare match interrupt/event per compare channel for the low-byte timer/counter

- Can be used with the event system for count control

## 16.2 Overview

There are four Timer/Counter 2. These are realized when a Timer/Counter 0 is set in split mode. It is then a system of two eight-bit timer/counters, each with four compare channels. This results in eight configurable pulse width modulation (PWM) channels with individually controlled duty cycles, and is intended for applications that require a high number of PWM channels.

The two eight-bit timer/counters in this system are referred to as the low-byte timer/counter and high-byte timer/counter, respectively. The difference between them is that only the low-byte timer/counter can be used to generate compare match interrupts and events. The two eight-bit timer/counters have a shared clock source and separate period and compare settings. They can be clocked and timed from the peripheral clock, with optional prescaling, or from the event system. The counters are always counting down.

PORTC, PORTD, PORTE, and PORTF each has one Timer/Counter 2. Notation of these are TCC2 (Timer/Counter C2), TCD2, TCE2, and TCF2, respectively.

| Mnemonics | Operands | Description                                         | Opera                                      | ation      |                     | Flags | #Clocks          |

|-----------|----------|-----------------------------------------------------|--------------------------------------------|------------|---------------------|-------|------------------|

| LD        | Rd, X+   | Load Indirect and Post-Increment                    | Rd<br>X                                    | <b>←</b>   | (X)<br>X + 1        | None  | 1 (1)(2)         |

| LD        | Rd, -X   | Load Indirect and Pre-Decrement                     | $X \leftarrow X - 1$ , $Rd \leftarrow (X)$ | <b>←</b>   | X - 1<br>(X)        | None  | 2 (1)(2)         |

| LD        | Rd, Y    | Load Indirect                                       | $Rd \leftarrow (Y)$                        | <b>←</b>   | (Y)                 | None  | 1 (1)(2)         |

| LD        | Rd, Y+   | Load Indirect and Post-Increment                    | Rd<br>Y                                    | <b>←</b>   | (Y)<br>Y + 1        | None  | 1 (1)(2)         |

| LD        | Rd, -Y   | Load Indirect and Pre-Decrement                     | Y<br>Rd                                    | <b>←</b>   | Y - 1<br>(Y)        | None  | 2 (1)(2)         |

| LDD       | Rd, Y+q  | Load Indirect with Displacement                     | Rd                                         | <b>←</b>   | (Y + q)             | None  | 2 (1)(2)         |

| LD        | Rd, Z    | Load Indirect                                       | Rd                                         | ←          | (Z)                 | None  | 1 (1)(2)         |

| LD        | Rd, Z+   | Load Indirect and Post-Increment                    | Rd<br>Z                                    | <b>← ←</b> | (Z),<br>Z+1         | None  | 1 (1)(2)         |

| LD        | Rd, -Z   | Load Indirect and Pre-Decrement                     | Z<br>Rd                                    | <b>←</b>   | Z - 1,<br>(Z)       | None  | 2 (1)(2)         |

| LDD       | Rd, Z+q  | Load Indirect with Displacement                     | Rd                                         | <b>←</b>   | (Z + q)             | None  | 2 (1)(2)         |

| STS       | k, Rr    | Store Direct to Data Space                          | (k)                                        | <b>←</b>   | Rd                  | None  | 2 (1)            |

| ST        | X, Rr    | Store Indirect                                      | (X)                                        | <b>←</b>   | Rr                  | None  | 1 (1)            |

| ST        | X+, Rr   | Store Indirect and Post-Increment                   | (X)<br>X                                   | <b>←</b>   | Rr,<br>X + 1        | None  | 1 (1)            |

| ST        | -X, Rr   | Store Indirect and Pre-Decrement                    | X<br>(X)                                   | <b>← ←</b> | X - 1,<br>Rr        | None  | 2 (1)            |

| ST        | Y, Rr    | Store Indirect                                      | (Y)                                        | <b>←</b>   | Rr                  | None  | 1 (1)            |

| ST        | Y+, Rr   | Store Indirect and Post-Increment                   | (Y)<br>Y                                   | <b>←</b>   | Rr,<br>Y + 1        | None  | 1 (1)            |

| ST        | -Y, Rr   | Store Indirect and Pre-Decrement                    | Y<br>(Y)                                   | <b>←</b>   | Y - 1,<br>Rr        | None  | 2 (1)            |

| STD       | Y+q, Rr  | Store Indirect with Displacement                    | (Y + q)                                    | <b>←</b>   | Rr                  | None  | 2 (1)            |

| ST        | Z, Rr    | Store Indirect                                      | (Z)                                        | <b>←</b>   | Rr                  | None  | 1 (1)            |

| ST        | Z+, Rr   | Store Indirect and Post-Increment                   | (Z)<br>Z                                   | <b>←</b>   | Rr<br>Z + 1         | None  | 1 <sup>(1)</sup> |

| ST        | -Z, Rr   | Store Indirect and Pre-Decrement                    | Z                                          | <b>←</b>   | Z - 1               | None  | 2 (1)            |

| STD       | Z+q, Rr  | Store Indirect with Displacement                    | (Z + q)                                    | <b>←</b>   | Rr                  | None  | 2 (1)            |

| LPM       |          | Load Program Memory                                 | R0                                         | <b>←</b>   | (Z)                 | None  | 3                |

| LPM       | Rd, Z    | Load Program Memory                                 | Rd                                         | <b>←</b>   | (Z)                 | None  | 3                |

| LPM       | Rd, Z+   | Load Program Memory and Post-Increment              | Rd<br>Z                                    | <b>←</b>   | (Z),<br>Z + 1       | None  | 3                |

| ELPM      |          | Extended Load Program Memory                        | R0                                         | <b>←</b>   | (RAMPZ:Z)           | None  | 3                |

| ELPM      | Rd, Z    | Extended Load Program Memory                        | Rd                                         | <b>←</b>   | (RAMPZ:Z)           | None  | 3                |

| ELPM      | Rd, Z+   | Extended Load Program Memory and Post-<br>Increment | Rd<br>Z                                    | <b>←</b>   | (RAMPZ:Z),<br>Z + 1 | None  | 3                |

| SPM       |          | Store Program Memory                                | (RAMPZ:Z)                                  | <b>←</b>   | R1:R0               | None  | -                |

| SPM       | Z+       | Store Program Memory and Post-Increment by 2        | (RAMPZ:Z)<br>Z                             | <b>←</b>   | R1:R0,<br>Z + 2     | None  | -                |

| IN        | Rd, A    | In From I/O Location                                | Rd                                         | <b>←</b>   | I/O(A)              | None  | 1                |

| OUT       | A, Rr    | Out To I/O Location                                 | I/O(A)                                     | <b>←</b>   | Rr                  | None  | 1                |

| PUSH      | Rr       | Push Register on Stack                              | STACK                                      | <b>←</b>   | Rr                  | None  | 1 <sup>(1)</sup> |

| POP       | Rd       | Pop Register from Stack                             | Rd                                         | <b>←</b>   | STACK               | None  | 2 (1)            |

## 32.1.14 SPI Characteristics

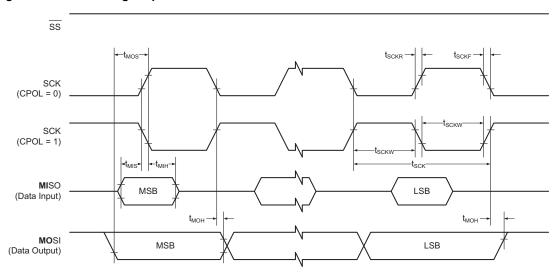

Figure 32-5. SPI Timing Requirements in Master Mode

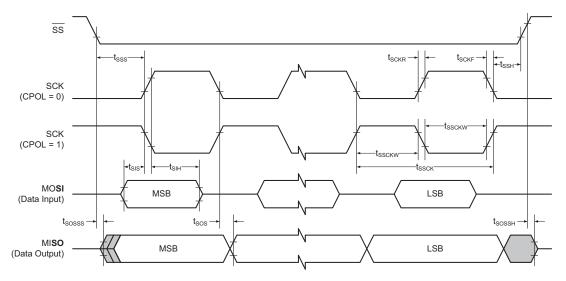

Figure 32-6. SPI Timing Requirements in Slave Mode

| Symbol             | Parameter                          | Condition | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------|-----------|------|------|------|-------|

| C <sub>XTAL1</sub> | Parasitic capacitance<br>XTAL1 pin |           |      | 5.9  |      |       |

| C <sub>XTAL2</sub> | Parasitic capacitance<br>XTAL2 pin |           |      | 8.3  |      | pF    |

| C <sub>LOAD</sub>  | Parasitic capacitance load         |           |      | 3.5  |      |       |

Note: 1. Numbers for negative impedance are not tested in production but guaranteed from design and characterization.

## 32.2.13.8 External 32.768kHz Crystal Oscillator and TOSC Characteristics

Table 32-56. External 32.768kHz Crystal Oscillator and TOSC Characteristics

| Symbo<br>I         | Parameter                                              | Condition                                         | Min. | Тур. | Max. | Units |  |

|--------------------|--------------------------------------------------------|---------------------------------------------------|------|------|------|-------|--|

|                    |                                                        | Crystal load capacitance 6.5pF                    |      |      | 60   | kΩ    |  |

|                    | Recommended crystal equivalent series resistance (ESR) | Crystal load capacitance 9.0pF                    |      |      | 35   |       |  |

|                    |                                                        | Crystal load capacitance 12pF                     |      |      | 28   |       |  |

| C <sub>TOSC1</sub> | Parasitic capacitance TOSC1 pin                        |                                                   |      | 3.5  |      | pF    |  |

| C <sub>TOSC2</sub> | Parasitic capacitance TOSC2 pin                        |                                                   |      | 3.5  |      |       |  |

|                    | Recommended safety factor                              | Capacitance load matched to crystal specification | 3    |      |      |       |  |

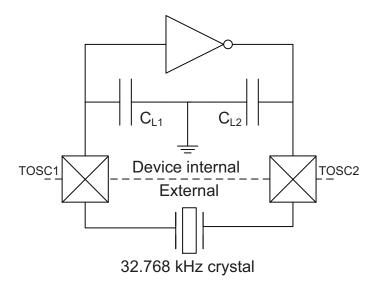

Note: See Figure 32-11 for definition.

Figure 32-11.TOSC Input Capacitance

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

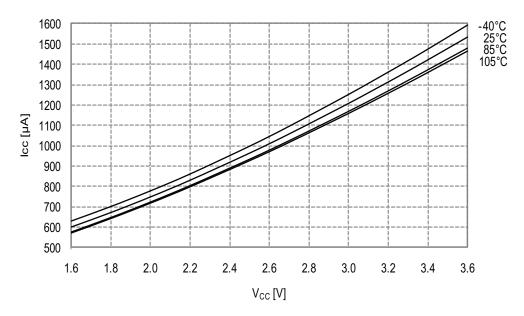

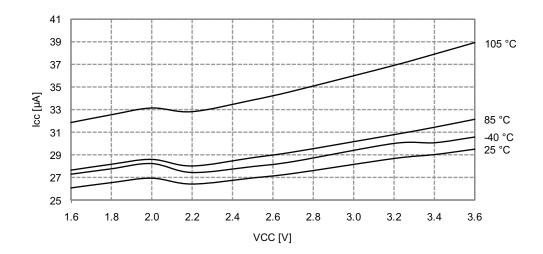

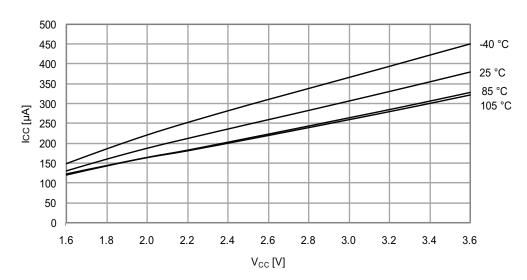

Figure 33-13. Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 32MHz$  internal oscillator prescaled to 8MHz

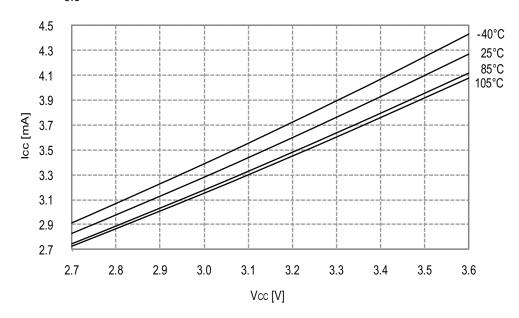

Figure 33-14. Idle Mode Current vs.  $V_{CC}$  $f_{SYS} = 32MHz$  internal oscillator

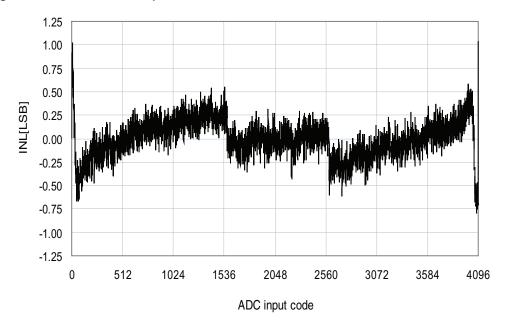

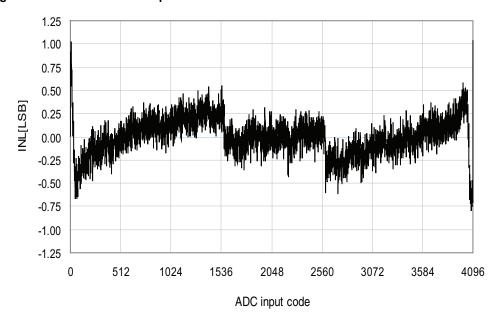

Figure 33-33. INL Error vs. Input Code

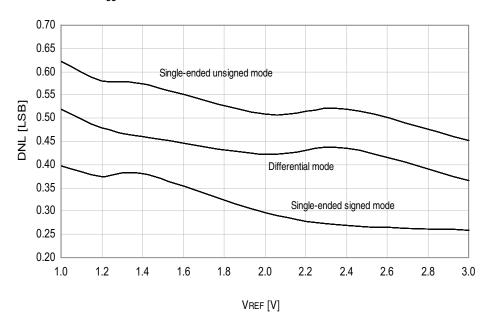

Figure 33-34. DNL Error vs. External  $V_{REF}$  $T = 25 \, \text{C}, V_{CC} = 3.6 V, \text{ external reference}$

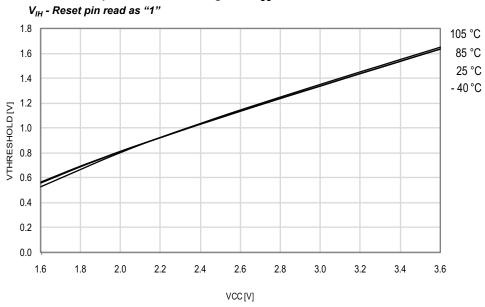

Figure 33-53. Reset Pin Input Threshold Voltage vs. V<sub>CC</sub>

## 33.1.8 Oscillator Characteristics

## 33.1.8.1 Ultra Low-power Internal Oscillator

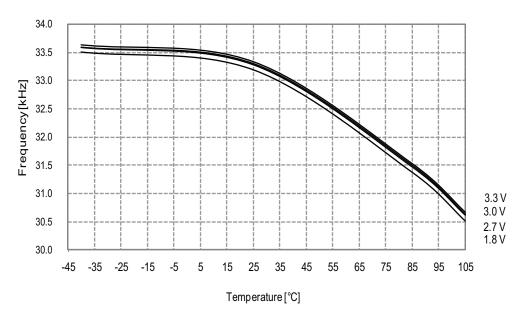

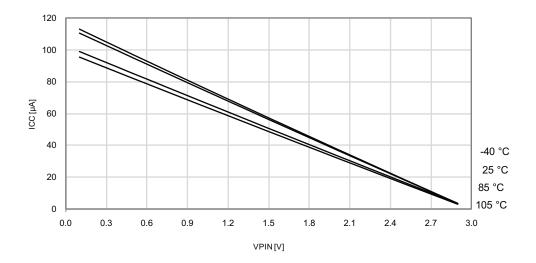

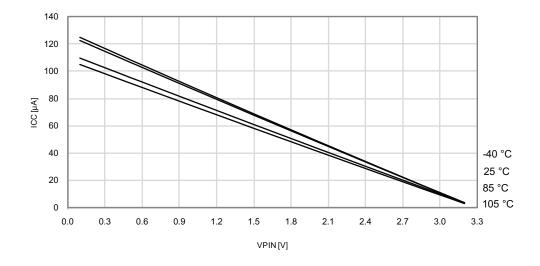

Figure 33-54. Ultra Low-power Internal Oscillator Frequency vs. Temperature

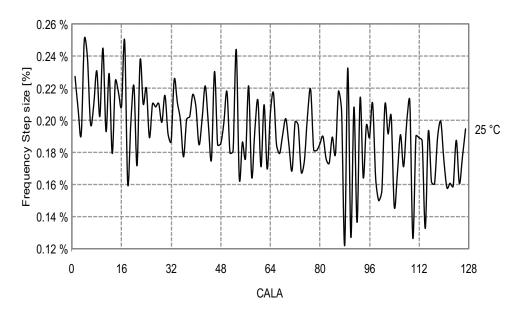

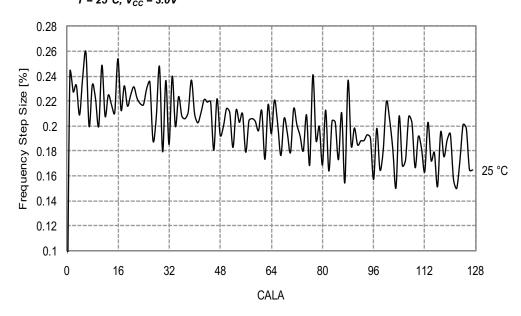

Figure 33-63. 32MHz Internal Oscillator CALA Calibration Step Size  $T = 25^{\circ}C$ ,  $V_{CC} = 3.0V$

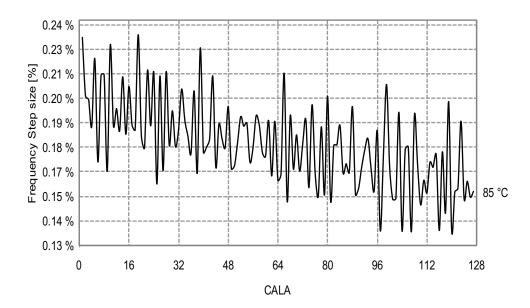

Figure 33-64. 32MHz Internal Oscillator CALA Calibration Step Size  $T = 85^{\circ}C$ ,  $V_{CC} = 3.0V$

## 33.2.8.3 2MHz Internal Oscillator

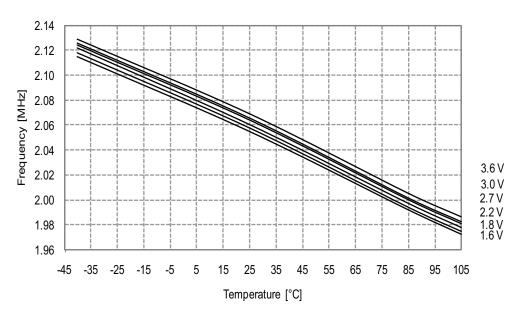

Figure 33-128. 2MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

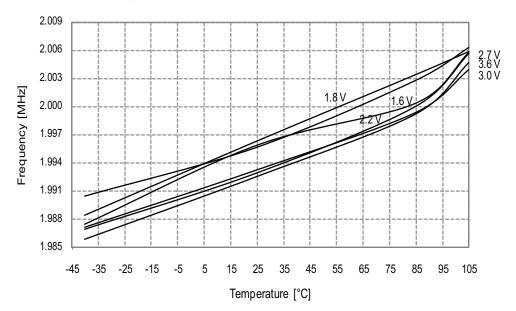

Figure 33-129. 2MHz Internal Oscillator Frequency vs. Temperature

DFLL enabled, from the 32.768kHz internal oscillator

Figure 33-161. I/O Pin Pull-up Resistor Current vs. Input Voltage  $V_{CC}$  = 3.0V

Figure 33-162. I/O Pin Pull-up Resistor Current vs. Input Voltage  $V_{CC}$  = 3.3V

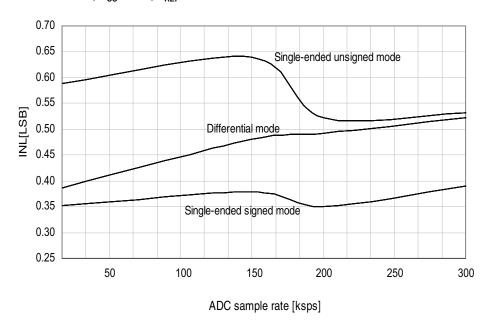

Figure 33-173. INL Error vs. Sample Rate  $T = 25 \, ^{\circ}\!\! \text{C}, \ V_{CC} = 3.6 \text{V}, \ V_{REF} = 3.0 \text{V external}$

Figure 33-174. INL Error vs. Input Code

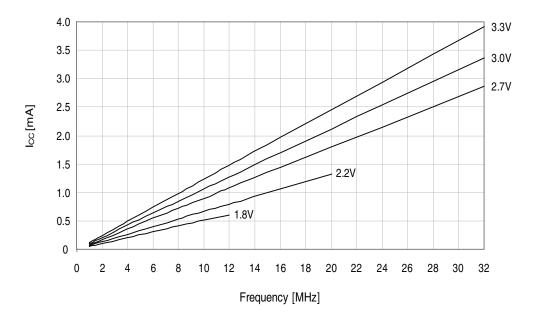

Figure 33-221.Idle Mode Supply Current vs. Frequency  $f_{\rm SYS}$  = 1 - 32MHz external clock, T = 25°C

Figure 33-222.Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS}$  = 32.768kHz internal oscillator

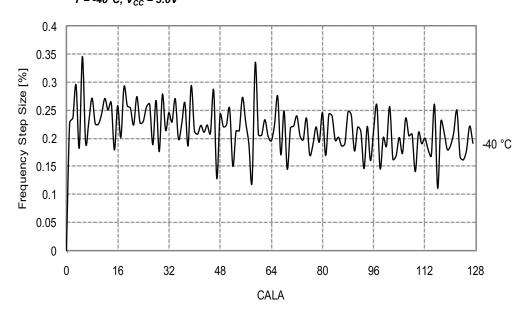

Figure 33-273. 32MHz Internal Oscillator CALA Calibration Step Size T = -40 °C,  $V_{CC} = 3.0V$

Figure 33-274. 32MHz Internal Oscillator CALA Calibration Step Size  $T=25^{\circ}C$ ,  $V_{CC}=3.0V$

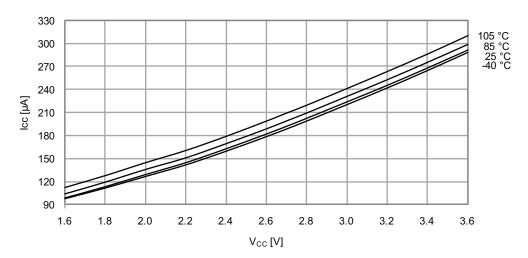

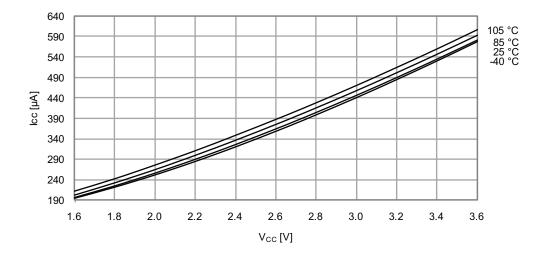

Figure 33-355. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 32.768kHz$  internal oscillator

Figure 33-356. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 1MHz$  external clock

Figure 33-363.Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 1MHz$  external clock

Figure 33-364.Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 2MHz internal oscillator$

## 34.2 Atmel ATxmega64D3

#### 34.2.1 Rev. I

- AC system status flags are only valid if AC-system is enabled

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

### 1. AC system status flags are only valid if AC-system is enabled

The status flags for the ac-output are updated even though the AC is not enabled which is invalid. Also, it is not possible to clear the AC interrupt flags without enabling either of the Analog comparators.

#### Problem fix/workaround

Software should clear the AC system flags once, after enabling the AC system before using the AC system status flags.

### 2. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC, and Analog Comparator.

#### Problem fix/workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

## 3. Temperature sensor not calibrated

Temperature sensor factory calibration not implemented.

#### Problem fix/workaround

None.

#### 34.2.2 Rev. H

Not sampled.

## 34.2.3 Rev. G

Not sampled.

#### 34.2.4 Rev. F

Not sampled.

## 34.5 Atmel ATxmega256D3

#### 34.5.1 Rev. I

- AC system status flags are only valid if AC-system is enabled

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

### 1. AC system status flags are only valid if AC-system is enabled

The status flags for the ac-output are updated even though the AC is not enabled which is invalid. Also, it is not possible to clear the AC interrupt flags without enabling either of the Analog comparators.

#### Problem fix/workaround

Software should clear the AC system flags once, after enabling the AC system before using the AC system status flags.

### 2. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC and Analog Comparator.

#### Problem fix/workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

## 3. Temperature sensor not calibrated

Temperature sensor factory calibration not implemented.

#### Problem fix/workaround

None.

#### 34.5.2 Rev. H

Not sampled.

## 34.5.3 Rev. G

Not sampled.

#### 34.5.4 Rev. F

Not sampled.

## 34.6 Atmel ATxmega384D3

#### 34.6.1 Rev. B

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

## 1. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC and Analog Comparator.

#### Problem fix/workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

## 2. Temperature sensor not calibrated

Temperature sensor factory calibration not implemented.

## Problem fix/workaround

None.

#### 34.6.2 Rev. A

Not sampled.