Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 256KB (128K x 16)                                                          |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega256d3-anr |

## 6. AVR CPU

## 6.1 Features

- 8/16-bit, high-performance Atmel AVR RISC CPU

- 137 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack pointer accessible in I/O memory space

- Direct addressing of up to 16MB of program memory and 16MB of data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Efficient support for 8-, 16-, and 32-bit arithmetic

- Configuration change protection of system-critical features

### 6.2 Overview

All Atmel AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 28.

### 6.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to <a href="https://www.atmel.com/avr">www.atmel.com/avr</a>.

Register File

R31 (ZH) R30 (ZL)

R29 (YH) R28 (XL)

R27 (XH) R26 (XL)

R28 R22

R23 R22

R21 R20

R19 R18

R17 R16

R15 R14

R13 R12

R11 R10

R9 R8

R7 R6

R5 R4

R3 R2

R1 R0

Instruction

Register

Stack

Pointer

ALU

Data Memory

Data Memory

Figure 6-1. Block Diagram of the AVR CPU Architecture

The arithmetic logic unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single-register operations can also be executed in the ALU. After an arithmetic operation, the status register is updated to reflect information about the result of the operation.

The ALU is directly connected to the fast-access register file. The 32 \* 8-bit general purpose working registers all have single clock cycle access time allowing single-cycle arithmetic logic unit (ALU) operation between registers or between a register and an immediate. Six of the 32 registers can be used as three 16-bit address pointers for program and data space addressing, enabling efficient address calculations.

The memory spaces are linear. The data memory space and the program memory space are two different memory spaces.

The data memory space is divided into I/O registers, SRAM, and external RAM. In addition, the EEPROM can be memory mapped in the data memory.

All I/O status and control registers reside in the lowest 4KB addresses of the data memory. This is referred to as the I/O memory space. The lowest 64 addresses can be accessed directly, or as the data space locations from 0x00 to 0x3F. The rest is the extended I/O memory space, ranging from 0x0040 to 0x0FFF. I/O registers here must be accessed as data space locations using load (LD/LDS/LDD) and store (ST/STS/STD) instructions.

The SRAM holds data. Code execution from SRAM is not supported. It can easily be accessed through the five different addressing modes supported in the AVR architecture. The first SRAM address is 0x2000.

Data addresses 0x1000 to 0x1FFF are reserved for memory mapping of EEPROM.

The program memory is divided in two sections, the application program section and the boot program section. Both sections have dedicated lock bits for write and read/write protection. The SPM instruction that is used for self-programming of the application flash memory must reside in the boot program section. The application section contains an application table section with separate lock bits for write and read/write protection. The application table section can be used for safe storing of nonvolatile data in the program memory.

## 22. USART

### 22.1 Features

- Three identical USART peripherals

- Full-duplex operation

- Asynchronous or synchronous operation

- Synchronous clock rates up to 1/2 of the device clock frequency

- Asynchronous clock rates up to 1/8 of the device clock frequency

- Supports serial frames with 5, 6, 7, 8, or 9 data bits and 1 or 2 stop bits

- Fractional baud rate generator

- Can generate desired baud rate from any system clock frequency

- No need for external oscillator with certain frequencies

- Built-in error detection and correction schemes

- Odd or even parity generation and parity check

- Data overrun and framing error detection

- · Noise filtering includes false start bit detection and digital low-pass filter

- Separate interrupts for

- Transmit complete

- Transmit data register empty

- Receive complete

- Multiprocessor communication mode

- Addressing scheme to address a specific devices on a multidevice bus

- Enable unaddressed devices to automatically ignore all frames

- Master SPI mode

- Double buffered operation

- Operation up to 1/2 of the peripheral clock frequency

- IRCOM module for IrDA compliant pulse modulation/demodulation

#### 22.2 Overview

The universal synchronous and asynchronous serial receiver and transmitter (USART) is a fast and flexible serial communication module. The USART supports full-duplex communication and asynchronous and synchronous operation. The USART can be configured to operate in SPI master mode and used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both directions, enabling continued data transmission without any delay between frames. Separate interrupts for receive and transmit complete enable fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

The clock generator includes a fractional baud rate generator that is able to generate a wide range of USART baud rates from any system clock frequencies. This removes the need to use an external crystal oscillator with a specific frequency to achieve a required baud rate. It also supports external clock input in synchronous slave operation.

When the USART is set in master SPI mode, all USART-specific logic is disabled, leaving the transmit and receive buffers, shift registers, and baud rate generator enabled. Pin control and interrupt generation are identical in both modes. The registers are used in both modes, but their functionality differs for some control settings.

An IRCOM module can be enabled for one USART to support IrDA 1.4 physical compliant pulse modulation and demodulation for baud rates up to 115.2kbps.

PORTC, PORTD, and PORTE each has one USART. Notation of these peripherals are USARTC0, USARTD0, and USARTE0, respectively.

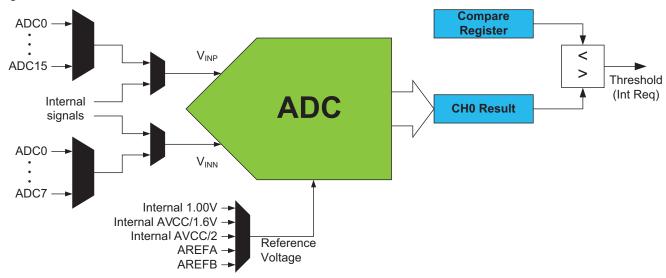

Figure 25-1. ADC Overview

The ADC may be configured for 8- or 12-bit result, reducing the minimum conversion time (propagation delay) from 3.35µs for 12-bit to 2.3µs for 8-bit result.

ADC conversion results are provided left- or right adjusted with optional '1' or '0' padding. This eases calculation when the result is represented as a signed integer (signed 16-bit number).

PORTA has one ADC. Notation of this peripheral is ADCA.

## 32.4 Atmel ATxmega192D3

## 32.4.1 Absolute Maximum Ratings

Stresses beyond those listed in Table 32-88 may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 32-88. Absolute Maximum Ratings

| Symbol           | Parameter                                           | Condition | Min. | Тур. | Max.                  | Units |

|------------------|-----------------------------------------------------|-----------|------|------|-----------------------|-------|

| V <sub>CC</sub>  | Power supply voltage                                |           | -0.3 |      | 4                     | V     |

| I <sub>vcc</sub> | Current into a V <sub>CC</sub> pin                  |           |      |      | 200                   | mA    |

| I <sub>GND</sub> | Current out of a Gnd pin                            |           |      |      | 200                   | IIIA  |

| $V_{PIN}$        | Pin voltage with respect to Gnd and $V_{\text{CC}}$ |           | -0.5 |      | V <sub>CC</sub> + 0.5 | V     |

| I <sub>PIN</sub> | I/O pin sink/source current                         |           | -25  |      | 25                    | mA    |

| T <sub>A</sub>   | Storage temperature                                 |           | -65  |      | 150                   | °C    |

| T <sub>j</sub>   | Junction temperature                                |           |      |      | 150                   | C     |

### 32.4.2 General Operating Ratings

The device must operate within the ratings listed in Table 32-89 in order for all other electrical characteristics and typical characteristics of the device to be valid.

Table 32-89. General Operating Conditions

| Symbol           | Parameter             | Condition | Min. | Тур. | Max. | Units |

|------------------|-----------------------|-----------|------|------|------|-------|

| V <sub>CC</sub>  | Power supply voltage  |           | 1.60 |      | 3.6  | V     |

| AV <sub>CC</sub> | Analog supply voltage |           | 1.60 |      | 3.6  | V     |

| T <sub>A</sub>   | Temperature range     |           | -40  |      | 85   | °C    |

| T <sub>j</sub>   | Junction temperature  |           | -40  |      | 105  |       |

Table 32-90. Operating Voltage and Frequency

| Symbol             | Parameter           | Condition              | Min. | Тур. | Max. | Units |

|--------------------|---------------------|------------------------|------|------|------|-------|

| Clk <sub>CPU</sub> | CPU clock frequency | V <sub>CC</sub> = 1.6V | 0    |      | 12   | MHz   |

|                    |                     | V <sub>CC</sub> = 1.8V | 0    |      | 12   |       |

|                    |                     | V <sub>CC</sub> = 2.7V | 0    |      | 32   |       |

|                    |                     | V <sub>CC</sub> = 3.6V | 0    |      | 32   |       |

The maximum CPU clock frequency depends on  $V_{CC}$ . As shown in Figure 32-22 on page 121 the frequency vs.  $V_{CC}$  curve is linear between 1.8V <  $V_{CC}$  < 2.7V.

## 32.5.13.5 Internal Phase Locked Loop (PLL) Characteristics

Table 32-139. Internal PLL Characteristics

| Symbol           | Parameter            | Condition                                        | Min. | Тур. | Max. | Units |

|------------------|----------------------|--------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>  | Input frequency      | Output frequency must be within f <sub>OUT</sub> | 0.4  |      | 64   |       |

| f                | Output frequency (1) | V <sub>CC</sub> = 1.6 - 1.8V                     | 20   |      | 48   | MHz   |

| f <sub>OUT</sub> | Output frequency V   | V <sub>CC</sub> = 2.7 - 3.6V                     | 20   |      | 128  |       |

|                  | Start-up time        |                                                  |      | 25   |      | III C |

|                  | Re-lock time         |                                                  |      | 25   |      | μs    |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

### 32.5.13.6 External Clock Characteristics

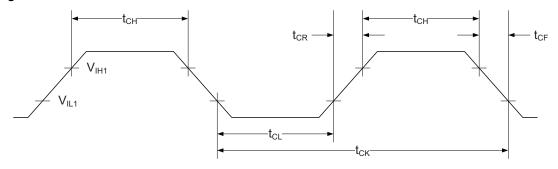

Figure 32-31.External Clock Drive Waveform

Table 32-140.External Clock used as System Clock without Prescaling

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units  |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|--------|

| 1 /4              | Clock Frequency (1)                               | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 12   | MHz    |

| 1/t <sub>CK</sub> | Clock Frequency V                                 | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 32   | IVIITZ |

| 4                 | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 83.3 |      |      |        |

| t <sub>CK</sub>   | CIOCK P GIIOU                                     | V <sub>CC</sub> = 2.7 - 3.6V | 31.5 |      |      |        |

| 4                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      |        |

| t <sub>CH</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      |        |

| 4                 | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | ns     |

| t <sub>CL</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | 113    |

| 4                 | Pico Timo (for maximum fraguancy)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |        |

| t <sub>CR</sub>   | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    |        |

| 4                 | Fall Time (for more income for more a)            | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |        |

| t <sub>CF</sub>   | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    |        |

| Δt <sub>CK</sub>  | Change in period from one clock cycle to the next |                              |      |      | 10   | %      |

Note: 1. The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

| Symbol          | Parameter            | Condition                        | Min.              | Тур. | Max.                  | Units |

|-----------------|----------------------|----------------------------------|-------------------|------|-----------------------|-------|

| V <sub>in</sub> | Input range          |                                  | 0                 |      | $V_{REF}$             |       |

|                 | Conversion range     | Differential mode, Vinp - Vinn   | -V <sub>REF</sub> |      | V <sub>REF</sub>      | V     |

|                 | Conversion range     | Single ended unsigned mode, Vinp | -ΔV               |      | V <sub>REF</sub> - ΔV |       |

| ΔV              | Fixed offset voltage |                                  |                   | 200  |                       | lsb   |

# Table 32-154. Clock and Timing

| Symbol              | Parameter                 | Condition                                                                   | Min. | Тур. | Max. | Units              |

|---------------------|---------------------------|-----------------------------------------------------------------------------|------|------|------|--------------------|

| CIL                 | ADO als all fra more      | Maximum is 1/4 of peripheral clock frequency                                | 100  |      | 1800 | kHz                |

| Clk <sub>ADC</sub>  | ADC clock frequency       | Measuring internal signals                                                  | 100  |      | 125  | NI IZ              |

| f <sub>ClkADC</sub> | Sample rate               |                                                                             | 16   |      | 300  |                    |

|                     |                           | Current limitation (CURRLIMIT) off                                          | 16   |      | 300  |                    |

| f                   | Sample rate               | CURRLIMIT = LOW                                                             | 16   |      | 250  | ksps               |

| f <sub>ADC</sub>    |                           | CURRLIMIT = MEDIUM                                                          | 16   |      | 150  |                    |

|                     |                           | CURRLIMIT = HIGH                                                            | 16   |      | 50   |                    |

|                     | Sampling time             | Configurable in steps of 1/2 $Clk_{ADC}$ cycles up to 32 $Clk_{ADC}$ cycles | 0.28 |      | 320  | μs                 |

|                     | Conversion time (latency) | (RES+1)/2 + GAIN<br>RES (Resolution) = 8 or 12, GAIN = 0 to 3               | 5.5  |      | 10   | Clk <sub>ADC</sub> |

|                     | Start-up time             | ADC clock cycles                                                            |      | 12   | 24   |                    |

|                     | ADC settling time         | After changing reference or input mode                                      |      | 7    | 7    |                    |

## 33.1.6 BOD Characteristics

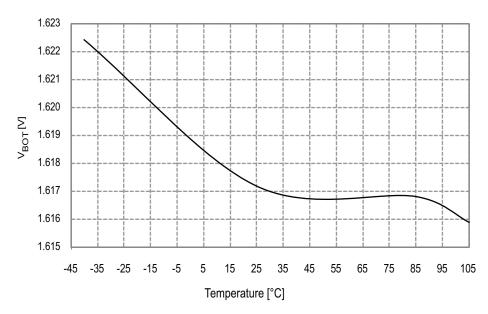

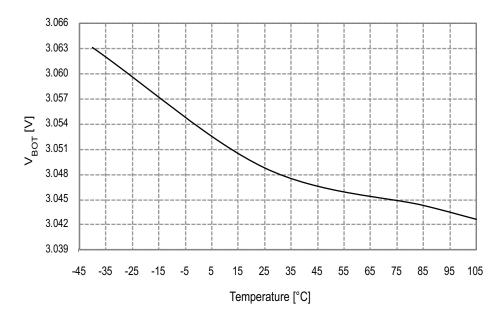

Figure 33-47. BOD Thresholds vs. Temperature BOD level = 1.6V

Figure 33-48. BOD Thresholds vs. Temperature BOD level = 3.0V

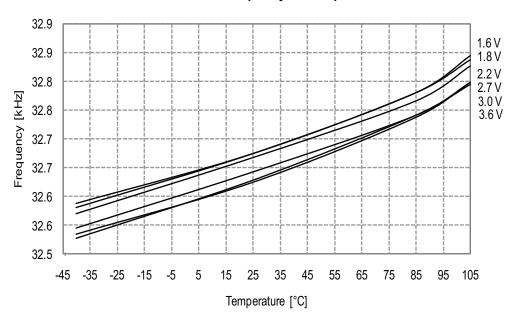

## 33.1.8.2 32.768kHz Internal Oscillator

Figure 33-55. 32.768kHz Internal Oscillator Frequency vs. Temperature

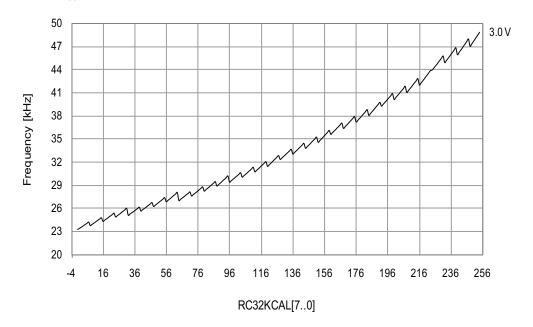

Figure 33-56. 32.768kHz Internal Oscillator Frequency vs. Calibration Value  $V_{CC}$  = 3.0V, T = 25°C

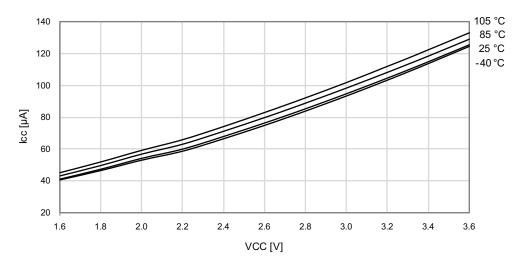

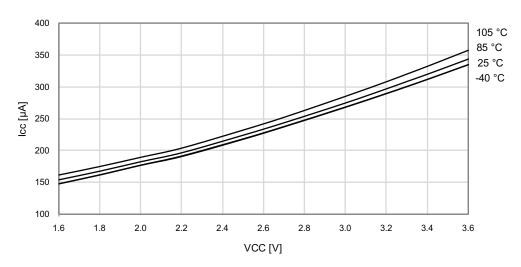

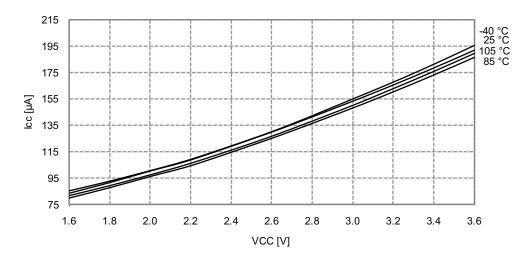

Figure 33-153. Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 1MHz$  external clock

Figure 33-154. Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 2MHz$  internal oscillator

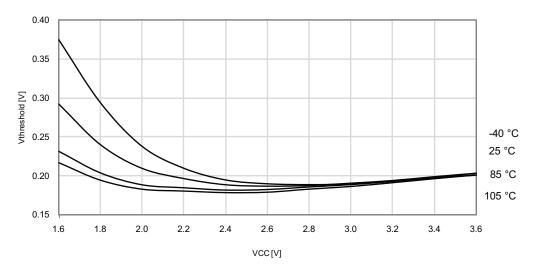

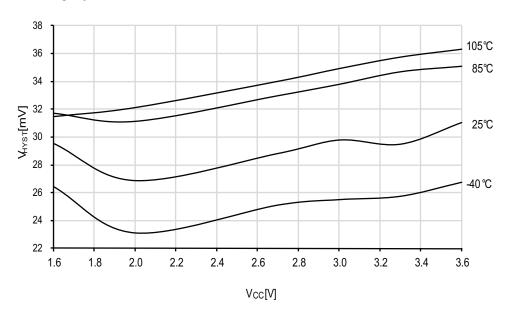

Figure 33-171. I/O Pin Input Hysteresis vs.  $V_{\rm CC}$

### 33.3.3 ADC Characteristics

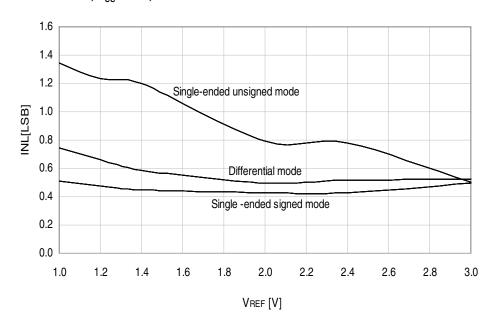

Figure 33-172. INL Error vs. External  $V_{REF}$  $T = 25 \, \text{C}, V_{CC} = 3.6 V, \text{ external reference}$

# 33.3.4 Analog Comparator Characteristics

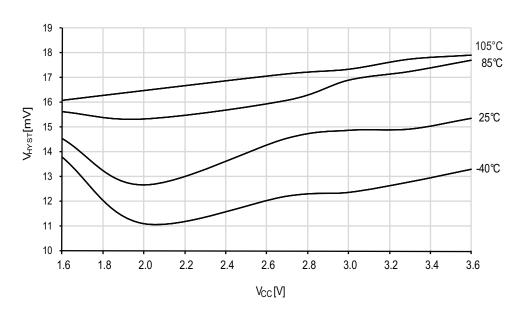

Figure 33-183. Analog Comparator Hysteresis vs. V<sub>CC</sub> Small hysteresis

Figure 33-184. Analog Comparator Hysteresis vs. V<sub>CC</sub>

Large hysteresis

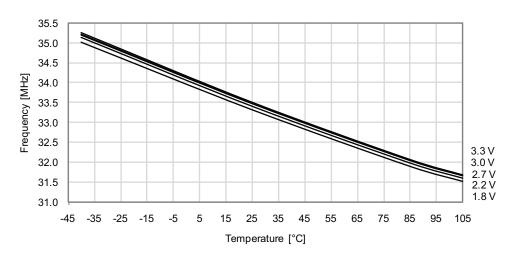

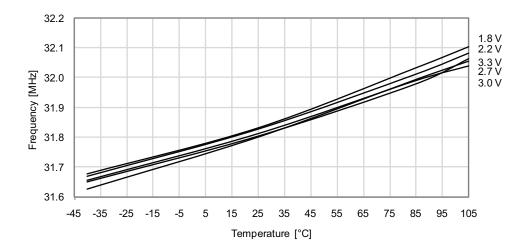

## 33.3.8.4 32MHz Internal Oscillator

Figure 33-201. 32MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

Figure 33-202. 32MHz Internal Oscillator Frequency vs. Temperature DFLL enabled, from the 32.768kHz internal oscillator

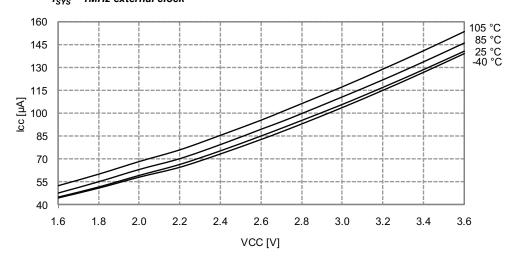

Figure 33-223.Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 1MHz$  external clock

Figure 33-224.Idle Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 2MHz internal oscillator$

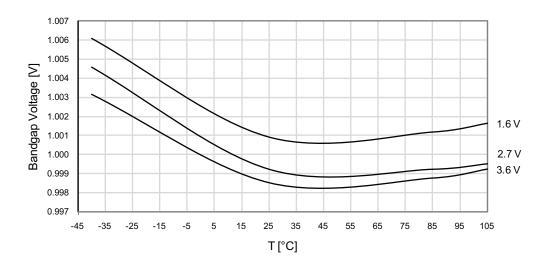

## 33.4.5 Internal 1.0V Reference Characteristics

Figure 33-257.ADC Internal 1.0V Reference vs. Temperature

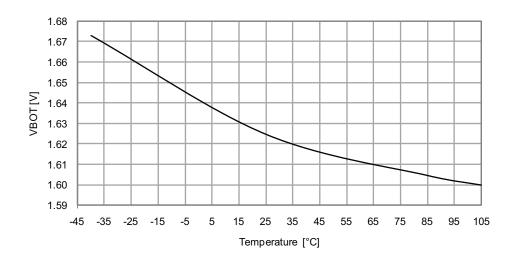

## 33.4.6 BOD Characteristics

Figure 33-258.BOD Thresholds vs. Temperature BOD level = 1.6V

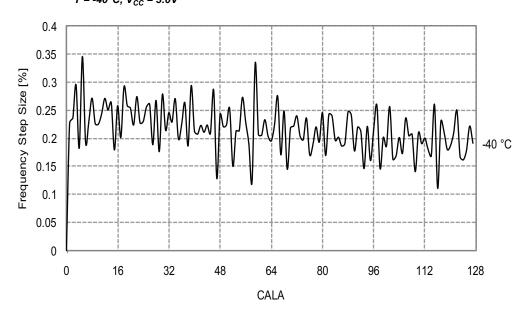

Figure 33-273. 32MHz Internal Oscillator CALA Calibration Step Size T = -40 °C,  $V_{CC} = 3.0V$

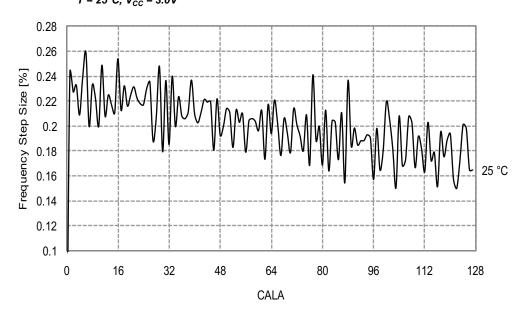

Figure 33-274. 32MHz Internal Oscillator CALA Calibration Step Size  $T=25^{\circ}C$ ,  $V_{CC}=3.0V$

```

2.4 V

1×

gain:

2×

gain:

1.2 V

4×

gain:

0.6 V

8×

gain:

300 mV

16×

gain:

150 mV

32×

gain:

75

mV

64×

gain:

38 mV

```

#### Problem fix/workaround

Keep the amplified voltage output from the ADC gain stage below 2.4V in order to get a correct result, or keep ADC voltage reference below 2.4V.

#### 6. ADC Event on compare match non-functional

ADC signalling event will be given at every conversion complete even if Interrupt mode (INTMODE) is set to BELOW or ABOVE.

#### Problem fix/workaround

Enable and use interrupt on compare match when using the compare function.

#### 7. ADC propagation delay is not correct when 8x - 64x gain is used

The propagation delay will increase by only one ADC clock cycle for all gain settings.

#### Problem fix/workaround

None.

### 8. Bandgap measurement with the ADC is non-functional when $V_{CC}$ is below 2.7V

The ADC can not be used to do bandgap measurements when  $V_{CC}$  is below 2.7V.

#### Problem fix/workaround

None.

### 9. Accuracy lost on first three samples after switching input to ADC gain stage

Due to memory effect in the ADC gain stage, the first three samples after changing input channel must be disregarded to achieve 12-bit accuracy.

#### Problem fix/workaround

Run three ADC conversions and discard these results after changing input channels to ADC gain stage.

#### 10. Configuration of PGM and CWCM not as described in XMEGA D Manual

Enabling Common Waveform Channel Mode will enable Pattern generation mode (PGM), but not Common Waveform Channel Mode.

Enabling Pattern Generation Mode (PGM) and not Common Waveform Channel Mode (CWCM) will enable both Pattern Generation Mode and Common Waveform Channel Mode.

#### Problem fix/workaround

Table 34-3. Configure PWM and CWCM According to this Table:

| PGM | CWCM | Description           |

|-----|------|-----------------------|

| 0   | 0    | PGM and CWCM disabled |

| 0   | 1    | PGM enabled           |

| 1   | 0    | PGM and CWCM enabled  |

| 1   | 1    | PGM enabled           |

### 11. PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/workaround

Do a write to any AWeX I/O register to re-enable the output.

### 12. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the  $V_{CC}$  voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until  $V_{CC}$  is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/workaround

Do not set the BOD level higher than  $V_{CC}$  even if the BOD is not used.

### 13. EEPROM page buffer always written when NVM DATA0 is written

If the EEPROM is memory mapped, writing to NVM DATA0 will corrupt data in the EEPROM page buffer.

### Problem fix/workaround

Before writing to NVM DATA0, for example when doing software CRC or flash page buffer write, check if EEPROM page buffer active loading flag (EELOAD) is set. Do not write NVM DATA0 when EELOAD is set.

#### 14. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

### Problem fix/workaround

None.

#### 15. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

### Problem fix/workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (that is, connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

# 34.4.9 Rev. A

Not sampled.

|     | 34.6    | Atmel ATxmega384D3     | 453 |

|-----|---------|------------------------|-----|

| 35. | Datas   | sheet revision history | 454 |

|     | 35.1    | 8134Q – 10/2015        |     |

|     | 35.2    | 8134P – 11/2014        | 454 |

|     | 35.3    | 81340 – 09/2014        | 454 |

|     | 35.4    | 8134N – 03/2014        | 454 |

|     | 35.5    | 8134M – 07/2013        | 455 |

|     | 35.6    | 8134L – 07/2013        | 455 |

|     | 35.7    | 8134K – 05/2013        | 455 |

|     | 35.8    | 8134J – 03/2013        | 455 |

|     | 35.9    | 8134I – 12/2010        | 456 |

|     | 35.10   | 8134H – 09/2010        | 457 |

|     | 35.11   | 8134G – 08/2010        | 457 |

|     | 35.12   | 8134F – 02/2010        | 457 |

|     | 35.13   | 8134E – 01/2010        | 457 |

|     | 35.14   | 8134D – 11/2009        | 458 |

|     | 35.15   | 8134C – 10/2009        | 458 |

|     | 35.16   | 8134B – 08/2009        | 458 |

|     | 35.17   | 8134A – 03/2009        | 458 |

| Tab | le of ( | Contents               | i   |