Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 256KB (128K x 16)                                                          |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega256d3-aur |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6. AVR CPU

## 6.1 Features

- 8/16-bit, high-performance Atmel AVR RISC CPU

- 137 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack pointer accessible in I/O memory space

- Direct addressing of up to 16MB of program memory and 16MB of data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Efficient support for 8-, 16-, and 32-bit arithmetic

- Configuration change protection of system-critical features

## 6.2 Overview

All Atmel AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 28.

## 6.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to www.atmel.com/avr.

after reset, and the initial value is the highest address of the internal SRAM. If the SP is changed, it must be set to point above address 0x2000, and it must be defined before any subroutine calls are executed or before interrupts are enabled.

During interrupts or subroutine calls, the return address is automatically pushed on the stack. The return address can be two or three bytes, depending on program memory size of the device. For devices with 128KB or less of program memory, the return address is two bytes, and hence the stack pointer is decremented/incremented by two. For devices with more than 128KB of program memory, the return address is three bytes, and hence the SP is decremented/incremented by three. The return address is popped off the stack when returning from interrupts using the RETI instruction, and from subroutine calls using the RET instruction.

The SP is decremented by one when data are pushed on the stack with the PUSH instruction, and incremented by one when data is popped off the stack using the POP instruction.

To prevent corruption when updating the stack pointer from software, a write to SPL will automatically disable interrupts for up to four instructions or until the next I/O memory write.

After reset the stack pointer is initialized to the highest address of the SRAM. See Figure 7-2 on page 16.

## 6.8 Register File

The register file consists of 32 \* 8-bit general purpose working registers with single clock cycle access time. The register file supports the following input/output schemes:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

Six of the 32 registers can be used as three 16-bit address register pointers for data space addressing, enabling efficient address calculations. One of these address pointers can also be used as an address pointer for lookup tables in flash program memory.

## 7. Memories

## 7.1 Features

- Flash program memory

- One linear address space

- In-system programmable

- Self-programming and boot loader support

- Application section for application code

- Application table section for application code or data storage

- Boot section for application code or boot loader code

- Separate read/write protection lock bits for all sections

- Built in fast CRC check of a selectable flash program memory section

- Data memory

- One linear address space

- Single-cycle access from CPU

- SRAM

- EEPROM

- Byte and page accessible

- Optional memory mapping for direct load and store

- I/O memory

- Configuration and status registers for all peripherals and modules

- Four bit-accessible general purpose registers for global variables or flags

- Production signature row memory for factory programmed data

- ID for each microcontroller device type

- Serial number for each device

- Calibration bytes for factory calibrated peripherals

- User signature row

- One flash page in size

- Can be read and written from software

- Content is kept after chip erase

## 7.2 Overview

The Atmel AVR architecture has two main memory spaces, the program memory and the data memory. Executable code can reside only in the program memory, while data can be stored in the program memory and the data memory. The data memory includes the internal SRAM, and EEPROM for nonvolatile data storage. All memory spaces are linear and require no memory bank switching. Nonvolatile memory (NVM) spaces can be locked for further write and read/write operations. This prevents unrestricted access to the application software.

A separate memory section contains the fuse bytes. These are used for configuring important system functions, and can only be written by an external programmer.

The available memory size configurations are shown in "Ordering Information" on page 2. In addition, each device has a Flash memory signature row for calibration data, device identification, serial number etc.

## 7.3 Flash Program Memory

The Atmel AVR XMEGA devices contain on-chip, in-system reprogrammable flash memory for program storage. The flash memory can be accessed for read and write from an external programmer through the PDI or from application software running in the device.

All AVR CPU instructions are 16 or 32 bits wide, and each flash location is 16 bits wide. The flash memory is organized in two main sections, the application section and the boot loader section. The sizes of the different sections are fixed, but

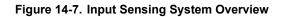

## 14.4 Input Sensing

Input sensing is synchronous or asynchronous depending on the enabled clock for the ports, and the configuration is shown in Figure 14-7.

When a pin is configured with inverted I/O, the pin value is inverted before the input sensing.

## 14.5 Alternate Port Functions

Most port pins have alternate pin functions in addition to being a general purpose I/O pin. When an alternate function is enabled, it might override the normal port pin function or pin value. This happens when other peripherals that require pins are enabled or configured to use pins. If and how a peripheral will override and use pins is described in the section for that peripheral. "Pinout and Pin Functions" on page 50 shows which modules on peripherals that enable alternate functions on a pin, and which alternate functions that are available on a pin.

## 22. USART

## 22.1 Features

- Three identical USART peripherals

- Full-duplex operation

- Asynchronous or synchronous operation

- Synchronous clock rates up to 1/2 of the device clock frequency

- Asynchronous clock rates up to 1/8 of the device clock frequency

- Supports serial frames with 5, 6, 7, 8, or 9 data bits and 1 or 2 stop bits

- Fractional baud rate generator

- Can generate desired baud rate from any system clock frequency

- No need for external oscillator with certain frequencies

- Built-in error detection and correction schemes

- Odd or even parity generation and parity check

- Data overrun and framing error detection

- Noise filtering includes false start bit detection and digital low-pass filter

- Separate interrupts for

- Transmit complete

- Transmit data register empty

- Receive complete

- Multiprocessor communication mode

- Addressing scheme to address a specific devices on a multidevice bus

- Enable unaddressed devices to automatically ignore all frames

- Master SPI mode

- Double buffered operation

- Operation up to 1/2 of the peripheral clock frequency

- IRCOM module for IrDA compliant pulse modulation/demodulation

## 22.2 Overview

The universal synchronous and asynchronous serial receiver and transmitter (USART) is a fast and flexible serial communication module. The USART supports full-duplex communication and asynchronous and synchronous operation. The USART can be configured to operate in SPI master mode and used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both directions, enabling continued data transmission without any delay between frames. Separate interrupts for receive and transmit complete enable fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

The clock generator includes a fractional baud rate generator that is able to generate a wide range of USART baud rates from any system clock frequencies. This removes the need to use an external crystal oscillator with a specific frequency to achieve a required baud rate. It also supports external clock input in synchronous slave operation.

When the USART is set in master SPI mode, all USART-specific logic is disabled, leaving the transmit and receive buffers, shift registers, and baud rate generator enabled. Pin control and interrupt generation are identical in both modes. The registers are used in both modes, but their functionality differs for some control settings.

An IRCOM module can be enabled for one USART to support IrDA 1.4 physical compliant pulse modulation and demodulation for baud rates up to 115.2kbps.

PORTC, PORTD, and PORTE each has one USART. Notation of these peripherals are USARTC0, USARTD0, and USARTE0, respectively.

## 27. Programming and Debugging

## 27.1 Features

- Programming

- External programming through PDI interface

- Minimal protocol overhead for fast operation

- Built-in error detection and handling for reliable operation

- Boot loader support for programming through any communication interface

- Debugging

- Nonintrusive, real-time, on-chip debug system

- No software or hardware resources required from device except pin connection

- Program flow control

- Go, Stop, Reset, Step Into, Step Over, Step Out, Run-to-Cursor

- Unlimited number of user program breakpoints

- Unlimited number of user data breakpoints, break on:

- Data location read, write, or both read and write

- Data location content equal or not equal to a value

- Data location content is greater or smaller than a value

- Data location content is within or outside a range

- No limitation on device clock frequency

- Program and Debug Interface (PDI)

- Two-pin interface for external programming and debugging

- Uses the Reset pin and a dedicated pin

- No I/O pins required during programming or debugging

## 27.2 Overview

The Program and Debug Interface (PDI) is an Atmel proprietary interface for external programming and on-chip debugging of a device.

The PDI supports fast programming of nonvolatile memory (NVM) spaces; flash, EEPOM, fuses, lock bits, and the user signature row.

Debug is supported through an on-chip debug system that offers nonintrusive, real-time debug. It does not require any software or hardware resources except for the device pin connection. Using the Atmel tool chain, it offers complete program flow control and support for an unlimited number of program and complex data breakpoints. Application debug can be done from a C or other high-level language source code level, as well as from an assembler and disassembler level.

Programming and debugging can be done through the PDI physical layer. This is a two-pin interface that uses the Reset pin for the clock input (PDI\_CLK) and one other dedicated pin for data input and output (PDI\_DATA). Any external programmer or on-chip debugger/emulator can be directly connected to this interface.

| Table 32-5. | Current Consum | ption for Modules | and Peripherals |

|-------------|----------------|-------------------|-----------------|

|-------------|----------------|-------------------|-----------------|

| Symbol          | Parameter                 | Condition <sup>(1)</sup>                |                                                    | Min. | Тур. | Max. | Units |  |

|-----------------|---------------------------|-----------------------------------------|----------------------------------------------------|------|------|------|-------|--|

|                 | ULP oscillator            |                                         |                                                    |      | 0.9  |      |       |  |

|                 | 32.768kHz int. oscillator |                                         |                                                    |      | 29   |      |       |  |

|                 | 2MHz int. oscillator      |                                         |                                                    |      | 82   |      |       |  |

|                 |                           | DFLL enabled with                       | DFLL enabled with 32.768kHz int. osc. as reference |      |      |      |       |  |

|                 | 32MHz int. oscillator     |                                         |                                                    |      | 250  |      |       |  |

|                 |                           | DFLL enabled with                       | n 32.768kHz int. osc. as reference                 |      | 400  |      | μΑ    |  |

|                 | PLL                       | 20× multiplication<br>32MHz int. osc. D | factor,<br>IV4 as reference                        |      | 300  |      |       |  |

|                 | Watchdog timer            |                                         |                                                    |      | 1.0  |      |       |  |

|                 | DOD                       | Continuous mode 14                      |                                                    |      |      |      | -     |  |

|                 | BOD                       | Sampled mode, in                        |                                                    | 1.4  |      |      |       |  |

| I <sub>CC</sub> | Internal 1.0V reference   |                                         |                                                    | 180  |      |      |       |  |

|                 | Temperature sensor        |                                         |                                                    |      | 175  |      |       |  |

|                 |                           | 16ksps<br>V <sub>REF</sub> = Ext. ref.  |                                                    |      | 1.23 |      |       |  |

|                 | ADC                       |                                         | CURRLIMIT = LOW                                    |      | 1.1  |      |       |  |

|                 |                           |                                         | CURRLIMIT = MEDIUM                                 |      | 0.98 |      |       |  |

|                 |                           |                                         | CURRLIMIT = HIGH                                   |      | 0.87 |      | mA    |  |

|                 |                           | 75ksps<br>V <sub>REF</sub> = Ext. ref.  | CURRLIMIT = LOW                                    |      | 1.7  |      |       |  |

|                 |                           | 300ksps<br>V <sub>REF</sub> = Ext. ref. |                                                    |      | 3.1  |      |       |  |

|                 | USART                     | Rx and Tx enabled                       | d, 9600 BAUD                                       |      | 9.7  |      | μA    |  |

|                 | Flash memory and EEPRC    | M programming                           |                                                    |      | 5    |      | mA    |  |

Note: 1. All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

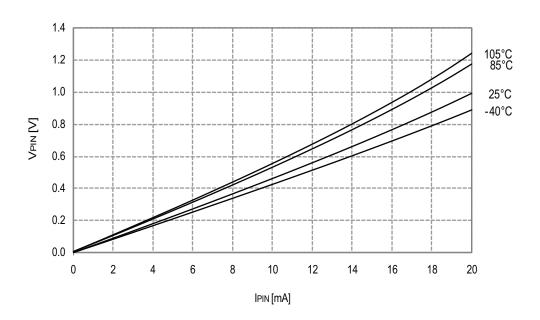

#### 32.2.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

#### Table 32-36. I/O Pin Characteristics

| Symbol                                                          | Parameter                                 | Condition                    |                        | Min.                  | Тур.  | Max.                  | Units |

|-----------------------------------------------------------------|-------------------------------------------|------------------------------|------------------------|-----------------------|-------|-----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> / I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current               |                              |                        | -15                   |       | 15                    | mA    |

| V <sub>IH</sub>                                                 | High level input voltage                  | V <sub>CC</sub> = 2.4 - 3.6V |                        | 0.7 * V <sub>CC</sub> |       | V <sub>CC</sub> + 0.5 |       |

| ۷IH                                                             | nightever input voltage                   | V <sub>CC</sub> = 1.6 - 2.4V |                        | 0.8 * V <sub>CC</sub> |       | V <sub>CC</sub> + 0.5 |       |

| V                                                               | Low level input voltage                   | V <sub>CC</sub> = 2.4 - 3.6V |                        | -0.5                  |       | 0.3 * V <sub>CC</sub> |       |

| ۷IL                                                             | V <sub>IL</sub> Low level input voltage   |                              |                        | -0.5                  |       | 0.2 * V <sub>CC</sub> |       |

|                                                                 |                                           | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -4mA | 2.6                   | 2.9   |                       | V     |

| V <sub>OH</sub>                                                 | V <sub>OH</sub> High level output voltage | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -3mA | 2.1                   | 2.6   |                       | v     |

|                                                                 |                                           | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -1mA | 1.4                   | 1.6   |                       |       |

|                                                                 |                                           | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 8mA  |                       | 0.4   | 0.76                  |       |

| V <sub>OL</sub> Low level of                                    | Low level output voltage                  | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 5mA  |                       | 0.3   | 0.64                  |       |

|                                                                 |                                           | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 3mA  |                       | 0.2   | 0.46                  |       |

| I <sub>IN</sub>                                                 | Input leakage current I/O pin             | T = 25°C                     |                        |                       | <0.01 | 1                     | μA    |

| R <sub>P</sub>                                                  | Pull/buss keeper resistor                 |                              |                        |                       | 25    |                       | kΩ    |

Notes:

1. The sum of all I<sub>OH</sub> for PORTA and PORTB must not exceed 100mA. The sum of all I<sub>OH</sub> for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all I<sub>OH</sub> for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all I<sub>OL</sub> for pins PF[6-7] on PORTF, PORTR, and PDI must not exceed 100mA.

The sum of all  $I_{OL}$  for PORTC, PORTD, and PORTE must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-7] on PORTF, PORTR, and PDI must not exceed 100mA. 2.

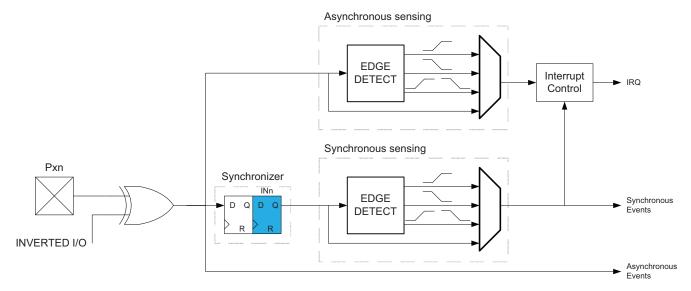

Figure 33-27. I/O Pin Output Voltage vs. Sink Current  $V_{CC}$  = 3.3V

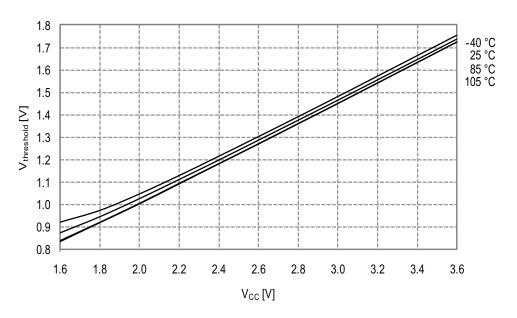

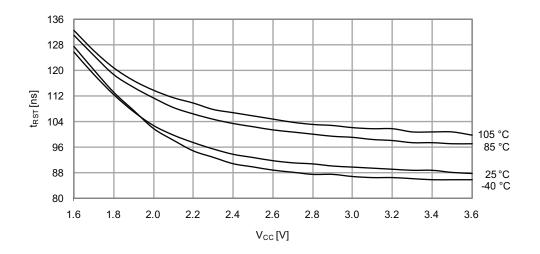

## 33.1.2.3 Thresholds and Hysteresis

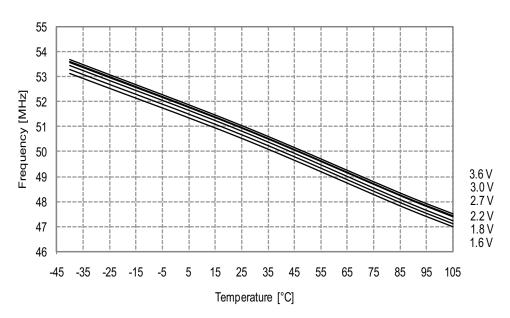

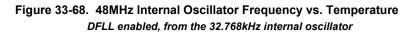

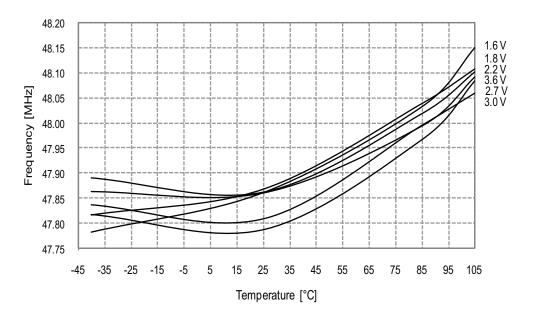

#### 33.1.8.5 32MHz Internal Oscillator Calibrated to 48MHz

Figure 33-67. 48MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

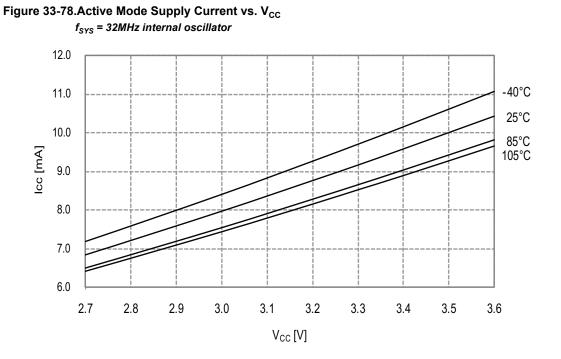

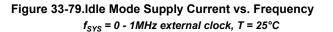

#### 33.2.1.2 Idle Mode Supply Current

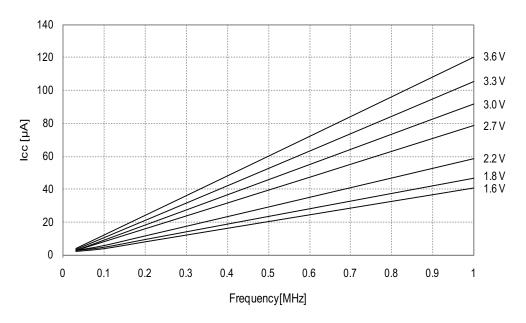

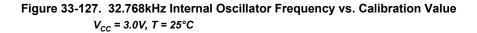

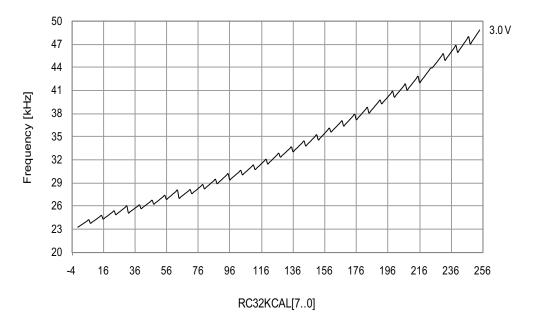

Figure 33-126. 32.768kHz Internal Oscillator Frequency vs. Temperature

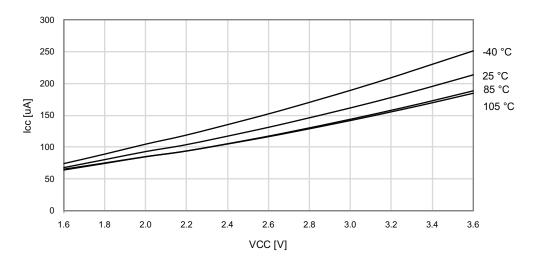

Figure 33-145. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS}$  = 32.768kHz internal oscillator

Figure 33-146. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 1MHz \ external \ clock$

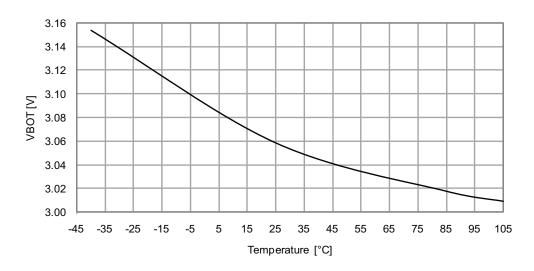

Figure 33-259.BOD Thresholds vs. Temperature BOD level = 3.0V

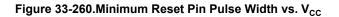

#### 33.4.7 External Reset Characteristics

Figure 33-381.I/O Pin Input Hysteresis vs. V<sub>cc</sub>

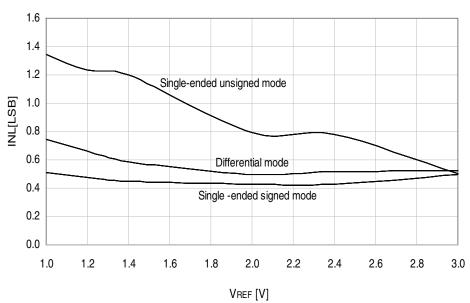

## 33.6.3 ADC Characteristics

Figure 33-382. INL Error vs. External  $V_{REF}$ T = 25 °C,  $V_{CC}$  = 3.6V, external reference

| PGM | CWCM | Description           |  |

|-----|------|-----------------------|--|

| 0   | 0    | PGM and CWCM disabled |  |

| 0   | 1    | PGM enabled           |  |

| 1   | 0    | PGM and CWCM enabled  |  |

| 1   | 1    | PGM enabled           |  |

#### Table 34-3. Configure PWM and CWCM According to this Table:

#### 11. PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/workaround

Do a write to any AWeX I/O register to re-enable the output.

#### 12. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the  $V_{CC}$  voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until  $V_{CC}$  is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/workaround

Do not set the BOD level higher than  $V_{CC}$  even if the BOD is not used.

## 13. EEPROM page buffer always written when NVM DATA0 is written

If the EEPROM is memory mapped, writing to NVM DATA0 will corrupt data in the EEPROM page buffer.

## Problem fix/workaround

Before writing to NVM DATA0, for example when doing software CRC or flash page buffer write, check if EEPROM page buffer active loading flag (EELOAD) is set. Do not write NVM DATA0 when EELOAD is set.

## 14. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

#### Problem fix/workaround

None.

## 15. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

#### Problem fix/workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (that is, connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

| PGM | CWCM | Description           |  |

|-----|------|-----------------------|--|

| 0   | 0    | PGM and CWCM disabled |  |

| 0   | 1    | PGM enabled           |  |

| 1   | 0    | PGM and CWCM enabled  |  |

| 1   | 1    | PGM enabled           |  |

#### Table 34-4. Configure PWM and CWCM According to this Table:

#### 11. PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/workaround

Do a write to any AWeX I/O register to re-enable the output.

#### 12. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the  $V_{CC}$  voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until  $V_{CC}$  is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/workaround

Do not set the BOD level higher than  $V_{CC}$  even if the BOD is not used.

## 13. EEPROM page buffer always written when NVM DATA0 is written

If the EEPROM is memory mapped, writing to NVM DATA0 will corrupt data in the EEPROM page buffer.

## Problem fix/workaround

Before writing to NVM DATA0, for example when doing software CRC or flash page buffer write, check if EEPROM page buffer active loading flag (EELOAD) is set. Do not write NVM DATA0 when EELOAD is set.

## 14. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

#### Problem fix/workaround

None.

## 15. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

## Problem fix/workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (that is, connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

- PORT remap functions with alternate pin locations for Timer/Counter output compare channels, USART0 and SPI, and the PORT REMAP register

- PORT RTC clock output option and the RTCOUT bit in the PORT CLKEVOUT register

- PORT remap functions with alternate pin locations for the clock and event output, and the CLKEVPIN bit in the PORT CLKEVOUT register

- TOSC alternate pin locations, and TOSCSEL bit in FUSEBYTE2

- Real Time Counter clock source options of external clock from TOSC1, and 32.768kHz from TOSC, and 32.768kHz from the 32.768kHz internal oscillator, and these configuration options in the RTCSRC bits in the Clock RTCTRL register

- PLL divide by two option, and the PLLDIV bit in the Clock PLLCTRL register

- PLL lock detection failure function and the PLLDIF and PLLFDEN bits in the Clock XOSCFAIL register

- The high drive option for external crystal and the XOSCPWR bit on the Oscillator XOSCCTRL register

- The option to enable sequential startup of the analog modules and the ANAINIT register in MCU Control memory

None.

#### 25. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC and Analog Comparator.

#### Problem fix/workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

## 26. Temperature sensor not calibrated

Temperature sensor factory calibration not implemented.

#### Problem fix/workaround

None.

## 34.4.6 Rev. D

Not sampled.

## 34.4.7 Rev. C

Not sampled.

| PGM | CWCM | Description           |  |

|-----|------|-----------------------|--|

| 0   | 0    | PGM and CWCM disabled |  |

| 0   | 1    | PGM enabled           |  |

| 1   | 0    | PGM and CWCM enabled  |  |

| 1   | 1    | PGM enabled           |  |

#### Table 34-7. Configure PWM and CWCM According to this Table:

#### 11. PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/workaround

Do a write to any AWeX I/O register to re-enable the output.

#### 12. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the  $V_{CC}$  voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until  $V_{CC}$  is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/workaround

Do not set the BOD level higher than  $V_{CC}$  even if the BOD is not used.

## 13. EEPROM page buffer always written when NVM DATA0 is written

If the EEPROM is memory mapped, writing to NVM DATA0 will corrupt data in the EEPROM page buffer.

## Problem fix/workaround

Before writing to NVM DATA0, for example when doing software CRC or flash page buffer write, check if EEPROM page buffer active loading flag (EELOAD) is set. Do not write NVM DATA0 when EELOAD is set.

## 14. Pending full asynchronous pin change interrupts will not wake the device

Any full asynchronous pin-change Interrupt from pin 2, on any port, that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again. This applies when entering all sleep modes where the System Clock is stopped.

#### Problem fix/workaround

None.

## 15. Pin configuration does not affect Analog Comparator output

The Output/Pull and inverted pin configuration does not affect the Analog Comparator output.

## Problem fix/workaround

None for Output/Pull configuration.

For inverted I/O, configure the Analog Comparator to give an inverted result (that is, connect positive input to the negative AC input and vice versa), or use and external inverter to change polarity of Analog Comparator output.

- PORT remap functions with alternate pin locations for Timer/Counter output compare channels, USART0 and SPI, and the PORT REMAP register

- PORT RTC clock output option and the RTCOUT bit in the PORT CLKEVOUT register

- PORT remap functions with alternate pin locations for the clock and event output, and the CLKEVPIN bit in the PORT CLKEVOUT register

- TOSC alternate pin locations, and TOSCSEL bit in FUSEBYTE2

- Real Time Counter clock source options of external clock from TOSC1, and 32.768kHz from TOSC, and 32.768kHz from the 32.768kHz internal oscillator, and these configuration options in the RTCSRC bits in the Clock RTCTRL register

- PLL divide by two option, and the PLLDIV bit in the Clock PLLCTRL register

- PLL lock detection failure function and the PLLDIF and PLLFDEN bits in the Clock XOSCFAIL register

- The high drive option for external crystal and the XOSCPWR bit on the Oscillator XOSCCTRL register

- The option to enable sequential startup of the analog modules and the ANAINIT register in MCU Control memory

None.

#### 25. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC and Analog Comparator.

#### Problem fix/workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

#### 26. Temperature sensor not calibrated

Temperature sensor factory calibration not implemented.

#### Problem fix/workaround

None.

## 27. Disabling of USART transmitter does not automatically set the TxD pin direction to input

If the USART transmitter is idle with no frames to transmit, setting TXEN to zero will not automatically set the TxD pin direction to input.

#### Problem fix/workaround

The TxD pin direction can be set to input using the Port DIR register. Be advised that setting the Port DIR register to input will be immediate. Ongoing transmissions will be truncated.

#### 34.5.6 Rev. D

Not sampled.

#### 34.5.7 Rev. C

Not sampled.