Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 384KB (384K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega384d3-mnr |

# 23. IRCOM - IR Communication Module

# 23.1 Features

- Pulse modulation/demodulation for infrared communication

- IrDA compatible for baud rates up to 115.2kbps

- Selectable pulse modulation scheme

- 3/16 of the baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built-in filtering

- Can be connected to and used by any USART

# 23.2 Overview

Atmel AVR XMEGA devices contain an infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2kbps. It can be connected to any USART to enable infrared pulse encoding/decoding for that USART.

# 26. AC – Analog Comparator

### 26.1 Features

- Two analog comparators (AC)

- Selectable hysteresis

- No

- Small

- Large

- Analog comparator output available on pin

- Flexible input selection

- All pins on the port

- Bandgap reference voltage

- A 64-level programmable voltage scaler of the internal AV<sub>CC</sub> voltage

- Interrupt and event generation on:

- Rising edge

- Falling edge

- Toggle

- Window function interrupt and event generation on:

- Signal above window

- Signal inside window

- Signal below window

- Constant current source with configurable output pin selection

### 26.2 Overview

The analog comparator (AC) compares the voltage levels on two inputs and gives a digital output based on this comparison. The analog comparator may be configured to generate interrupt requests and/or events upon several different combinations of input change.

The analog comparator hysteresis can be adjusted in order to achieve the optimal operation for each application.

The input selection includes analog port pins, several internal signals, and a 64-level programmable voltage scaler. The analog comparator output state can also be output on a pin for use by external devices.

A constant current source can be enabled and output on a selectable pin. This can be used to replace, for example, external resistors used to charge capacitors in capacitive touch sensing applications.

The analog comparators are always grouped in pairs on each port. These are called analog comparator 0 (AC0) and analog comparator 1 (AC1). They have identical behavior, but separate control registers. Used as pair, they can be set in window mode to compare a signal to a voltage range instead of a voltage level.

PORTA has one AC pair. Notation is ACA.

# 32.2.3 Current Consumption

Table 32-33. Current Consumption for Active Mode and Sleep Modes

| Symbol | Parameter                        | Condition                                            |                        | Min. | Тур. | Max. | Units |

|--------|----------------------------------|------------------------------------------------------|------------------------|------|------|------|-------|

| Icc    | Active power consumption (1)     | 22kHz Est Clk                                        | V <sub>CC</sub> = 1.8V |      | 50   |      |       |

|        |                                  | 32kHz, Ext. Clk                                      | V <sub>CC</sub> = 3.0V |      | 130  |      |       |

|        |                                  | ANALIS Fort Cile                                     | V <sub>CC</sub> = 1.8V |      | 215  |      | μA    |

|        |                                  | 1MHz, Ext. Clk                                       | V <sub>CC</sub> = 3.0V |      | 475  |      |       |

|        |                                  | 2MHz, Ext. Clk                                       | V <sub>CC</sub> = 1.8V |      | 445  | 600  |       |

|        |                                  |                                                      | \/ - 2 0\/             |      | 0.95 | 1.5  | mA    |

|        |                                  | 32MHz, Ext. Clk                                      | $V_{CC} = 3.0V$        |      | 7.8  | 12.0 |       |

|        | Idle power consumption (1)       | 32kHz, Ext. Clk                                      | V <sub>CC</sub> = 1.8V |      | 2.8  |      | μΑ    |

|        |                                  | JZNI IZ, EXt. OIK                                    | V <sub>CC</sub> = 3.0V |      | 3    |      |       |

|        |                                  | 1MHz, Ext. Clk                                       | V <sub>CC</sub> = 1.8V |      | 46   |      |       |

|        |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 92   |      |       |

|        |                                  | 2MHz, Ext. Clk                                       | V <sub>CC</sub> = 1.8V |      | 93   | 225  |       |

|        |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 184  | 350  |       |

|        |                                  | 32MHz, Ext. Clk                                      | - GC - 0.0 v           |      | 2.9  | 5.0  | mA    |

|        | Power-down power consumption     | T = 25°C                                             |                        |      | 0.07 | 1.0  |       |

|        |                                  | T = 85°C                                             | V <sub>CC</sub> = 3.0V |      | 1.3  | 5.0  |       |

|        |                                  | T = 105°C                                            |                        |      | 4.0  | 8.0  |       |

|        |                                  | WDT and sampled BOD enabled, T = 25°C                |                        |      | 1.3  | 2.0  |       |

|        |                                  | WDT and sampled BOD enabled, T = 85°C                | V <sub>CC</sub> = 3.0V |      | 2.6  | 6.0  |       |

|        |                                  | WDT and sampled BOD enabled, T= 105°C                |                        |      | 5.0  | 10   |       |

|        | Power-save power consumption (2) | RTC from ULP clock, WDT and sampled                  | V <sub>CC</sub> = 1.8V |      | 1.7  |      | μA    |

|        |                                  | BOD enabled, T = 25°C                                | V <sub>CC</sub> = 3.0V |      | 1.8  |      |       |

|        |                                  | RTC from 1.024kHz low power 32.768kHz TOSC, T = 25°C | V <sub>CC</sub> = 1.8V |      | 0.5  | 2.0  |       |

|        |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 0.7  | 2.0  |       |

|        |                                  | RTC from low power 32.768kHz TOSC,<br>T = 25°C       | V <sub>CC</sub> = 1.8V |      | 0.9  | 3.0  |       |

|        |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 1.2  | 3.0  |       |

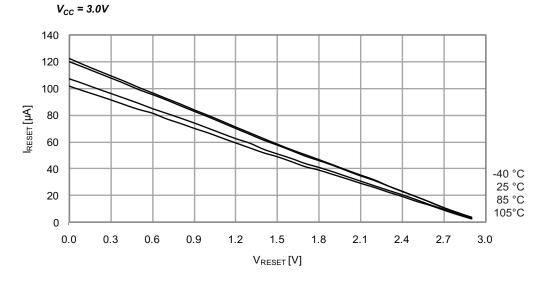

|        | Reset power consumption          | Current through RESET pin substracted                | V <sub>CC</sub> = 3.0V |      | 120  |      |       |

Notes:

<sup>1.</sup> All Power Reduction Registers set.

<sup>2.</sup> Maximum limits are based on characterization, and not tested in production.

# 32.3.3 Current Consumption

Table 32-62. Current Consumption for Active Mode and Sleep Modes

| Symbol          | Parameter                        | Condition                                            |                        | Min. | Тур. | Max. | Units |

|-----------------|----------------------------------|------------------------------------------------------|------------------------|------|------|------|-------|

|                 | Active power consumption (1)     | 221d In Firth Cily                                   | V <sub>CC</sub> = 1.8V |      | 55   |      | μΑ    |

|                 |                                  | 32kHz, Ext. Clk                                      | V <sub>CC</sub> = 3.0V |      | 135  |      |       |

|                 |                                  | ANALIS Fort Cile                                     | V <sub>CC</sub> = 1.8V |      | 237  |      |       |

|                 |                                  | 1MHz, Ext. Clk                                       | V <sub>CC</sub> = 3.0V |      | 515  |      |       |

|                 |                                  | 2MHz, Ext. Clk                                       | V <sub>CC</sub> = 1.8V |      | 425  | 700  |       |

|                 |                                  |                                                      | .,                     |      | 0.9  | 1.5  | mA    |

|                 |                                  | 32MHz, Ext. Clk                                      | $V_{CC} = 3.0V$        |      | 8.3  | 12   |       |

|                 | Idle power consumption (1)       | 2014  - 5.4 011                                      | V <sub>CC</sub> = 1.8V |      | 2.8  |      | μΑ    |

|                 |                                  | 32kHz, Ext. Clk                                      | V <sub>CC</sub> = 3.0V |      | 3.1  |      |       |

|                 |                                  | 1MHz, Ext. Clk                                       | V <sub>CC</sub> = 1.8V |      | 47   |      |       |

|                 |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 95   |      |       |

|                 |                                  | 2MHz, Ext. Clk                                       | V <sub>CC</sub> = 1.8V |      | 94   | 200  |       |

|                 |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 190  | 400  |       |

| I <sub>CC</sub> |                                  | 32MHz, Ext. Clk                                      | V <sub>CC</sub> – 3.0V |      | 3.0  | 7.0  | mA    |

|                 | Power-down power consumption     | T = 25°C                                             |                        |      | 0.1  | 1.0  |       |

|                 |                                  | T = 85°C                                             | V <sub>CC</sub> = 3.0V |      | 1.9  | 4.0  |       |

|                 |                                  | T = 105°C                                            |                        |      | 4.0  | 8.0  |       |

|                 |                                  | WDT and sampled BOD enabled, T = 25°C                |                        |      | 1.5  | 2.0  |       |

|                 |                                  | WDT and sampled BOD enabled, T = 85°C                | V <sub>CC</sub> = 3.0V |      | 3.0  | 8.0  |       |

|                 |                                  | WDT and sampled BOD enabled, T= 105°C                |                        |      | 5.0  | 10   |       |

|                 | Power-save power consumption (2) | RTC from ULP clock, WDT and sampled                  | V <sub>CC</sub> = 1.8V |      | 1.3  |      | μA    |

|                 |                                  | BOD enabled, T = 25°C                                | V <sub>CC</sub> = 3.0V |      | 1.4  |      |       |

|                 |                                  | RTC from 1.024kHz low power 32.768kHz TOSC, T = 25°C | V <sub>CC</sub> = 1.8V |      | 0.7  | 2.0  |       |

|                 |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 0.8  | 2.0  |       |

|                 |                                  | RTC from low power 32.768kHz TOSC,<br>T = 25°C       | V <sub>CC</sub> = 1.8V |      | 0.9  | 3.0  |       |

|                 |                                  |                                                      | V <sub>CC</sub> = 3.0V |      | 1.1  | 3.0  |       |

|                 | Reset power consumption          | Current through RESET pin substracted                | V <sub>CC</sub> = 3.0V |      | 145  |      |       |

Notes:

<sup>1.</sup> All Power Reduction Registers set.

<sup>2.</sup> Maximum limits are based on characterization, and not tested in production.

Table 32-87. Two-wire Interface Characteristics

| Symbol              | Parameter                                        | Condition                                | Min.                          | Тур. | Max.                  | Units |

|---------------------|--------------------------------------------------|------------------------------------------|-------------------------------|------|-----------------------|-------|

| V <sub>IH</sub>     | Input high voltage                               |                                          | 0.7V <sub>CC</sub>            |      | V <sub>CC</sub> + 0.5 |       |

| V <sub>IL</sub>     | Input low voltage                                |                                          | -0.5                          |      | 0.3V <sub>CC</sub>    | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs             |                                          | 0.05V <sub>CC</sub> (1)       |      |                       | V     |

| V <sub>OL</sub>     | Output low voltage                               | 3mA, sink current                        | 0                             |      | 0.4                   |       |

| t <sub>r</sub>      | Rise time for both SDA and SCL                   |                                          | 20 + 0.1C <sub>b</sub> (1)(2) |      | 300                   |       |

| t <sub>of</sub>     | Output fall time from $V_{IHmin}$ to $V_{ILmax}$ | 10pF < C <sub>b</sub> < 400pF (2)        | 20 + 0.1C <sub>b</sub> (1)(2) |      | 250                   | ns    |

| t <sub>SP</sub>     | Spikes suppressed by input filter                |                                          | 0                             |      | 50                    |       |

| I <sub>I</sub>      | Input current for each I/O pin                   | $0.1V_{CC} < V_{I} < 0.9V_{CC}$          | -10                           |      | 10                    | μA    |

| Cı                  | Capacitance for each I/O pin                     |                                          |                               |      | 10                    | pF    |

| f <sub>SCL</sub>    | SCL clock frequency                              | $f_{PER}^{(3)} > max(10f_{SCL}, 250kHz)$ | 0                             |      | 400                   | kHz   |

| Б                   | Value of pull-up resistor                        | f <sub>SCL</sub> ≤100kHz                 | $V_{CC} - 0.4V$               |      | $\frac{100ns}{C_b}$   |       |

| R <sub>P</sub>      |                                                  | f <sub>SCL</sub> > 100kHz                | $\frac{V_{CC} - 0.4V}{3mA}$   |      | $\frac{300ns}{C_b}$   | Ω     |

|                     | Hold time (repeated) START condition             | f <sub>SCL</sub> ≤ 100kHz                | 4.0                           |      |                       |       |

| t <sub>HD;STA</sub> |                                                  | f <sub>SCL</sub> > 100kHz                | 0.6                           |      |                       |       |

| 4                   | 1                                                | f <sub>SCL</sub> ≤ 100kHz                | 4.7                           |      |                       |       |

| t <sub>LOW</sub>    | Low period of SCL clock                          | f <sub>SCL</sub> > 100kHz                | 1.3                           |      |                       |       |

| +                   | High period of SCL clock                         | f <sub>SCL</sub> ≤ 100kHz                | 4.0                           |      |                       | μs    |

| t <sub>HIGH</sub>   |                                                  | f <sub>SCL</sub> > 100kHz                | 0.6                           |      |                       |       |

| +                   | Set-up time for a repeated START                 | f <sub>SCL</sub> ≤ 100kHz                | 4.7                           |      |                       |       |

| t <sub>SU;STA</sub> | condition                                        | f <sub>SCL</sub> > 100kHz                | 0.6                           |      |                       |       |

| 4                   | Data hold time                                   | f <sub>SCL</sub> ≤ 100kHz                | 0                             |      | 3.45                  |       |

| t <sub>HD;DAT</sub> | Data noid time                                   | f <sub>SCL</sub> > 100kHz                | 0                             |      | 0.9                   |       |

| 4                   | Data satur timo                                  | f <sub>SCL</sub> ≤ 100kHz                | 250                           |      |                       |       |

| t <sub>SU;DAT</sub> | Data setup time                                  | f <sub>SCL</sub> > 100kHz                | 100                           |      |                       |       |

| t                   | Setup time for STOP condition                    | f <sub>SCL</sub> ≤ 100kHz                | 4.0                           |      |                       | μs    |

| t <sub>SU;STO</sub> | octup time for o roi condition                   | f <sub>SCL</sub> > 100kHz                | 0.6                           |      |                       |       |

| +                   | Bus free time between a STOP and                 | f <sub>SCL</sub> ≤ 100kHz                | 4.7                           |      |                       |       |

| t <sub>BUF</sub>    | START condition                                  | f <sub>SCL</sub> > 100kHz                | 1.3                           |      |                       |       |

Notes:

- Required only for f<sub>SCL</sub> > 100kHz.

C<sub>b</sub> = Capacitance of one bus line in pF.

f<sub>PER</sub> = Peripheral clock frequency.

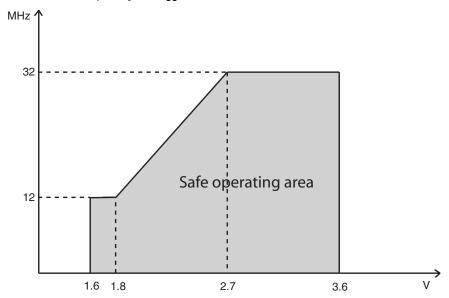

Figure 32-22.Maximum Frequency vs.  $V_{\rm CC}$

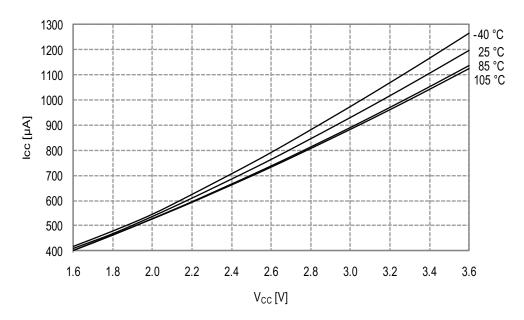

Figure 33-5. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 2MHz internal oscillator$

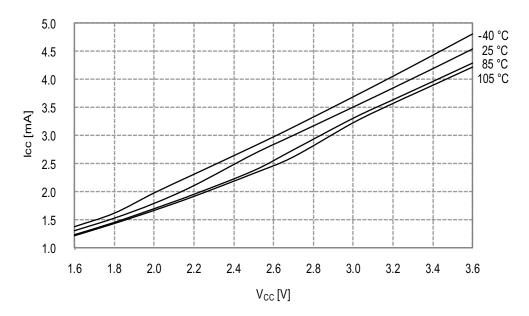

Figure 33-6. Active Mode Supply Current vs.  $V_{CC}$  $f_{SYS} = 32MHz$  internal oscillator prescaled to 8MHz

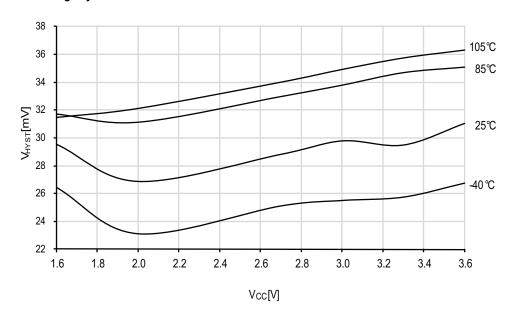

Figure 33-114. Analog Comparator Hysteresis vs. V<sub>CC</sub>

Large hysteresis

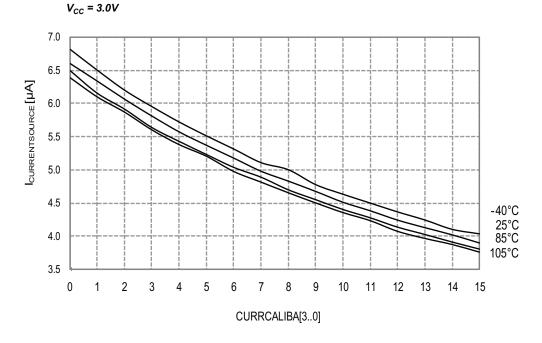

Figure 33-115. Analog Comparator Current Source vs. Calibration Value

# 33.2.8.2 32.768kHz Internal Oscillator

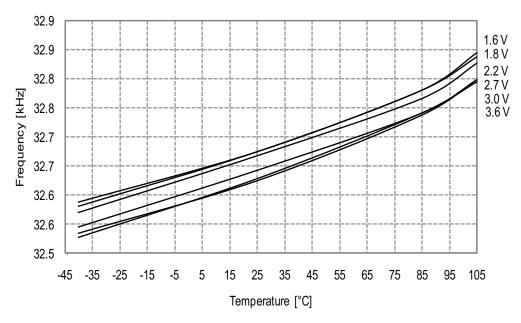

Figure 33-126. 32.768kHz Internal Oscillator Frequency vs. Temperature

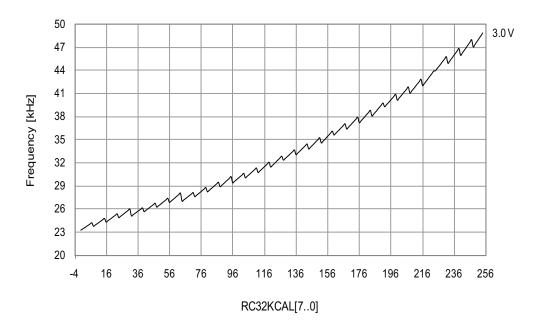

Figure 33-127. 32.768kHz Internal Oscillator Frequency vs. Calibration Value  $V_{CC}$  = 3.0V, T = 25°C

# 33.2.9 Two-Wire Interface Characteristics

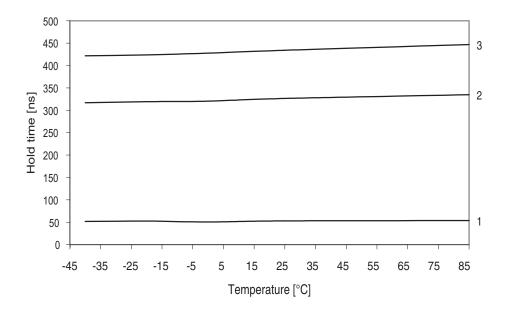

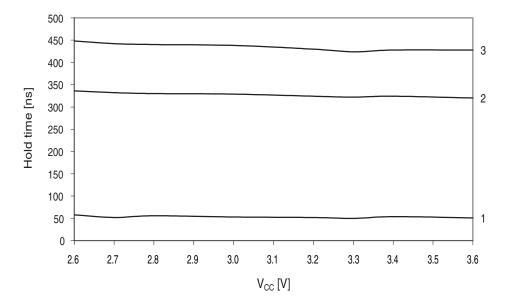

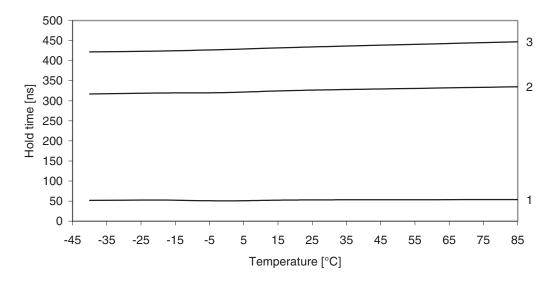

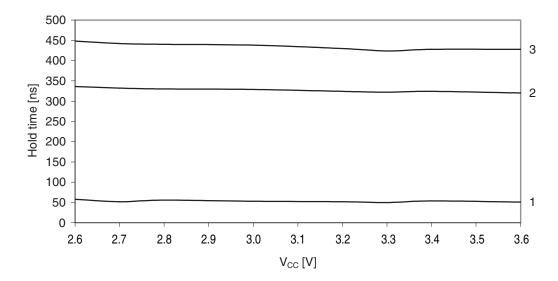

Figure 33-140. SDA Hold Time vs. Temperature

Figure 33-141. SDA Hold Time vs. Supply Voltage

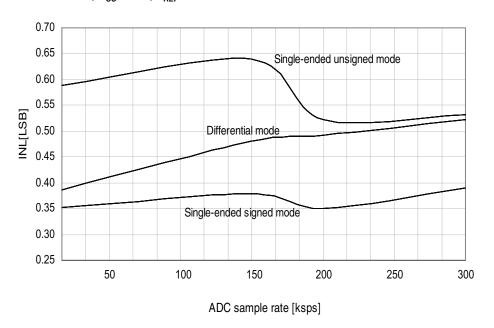

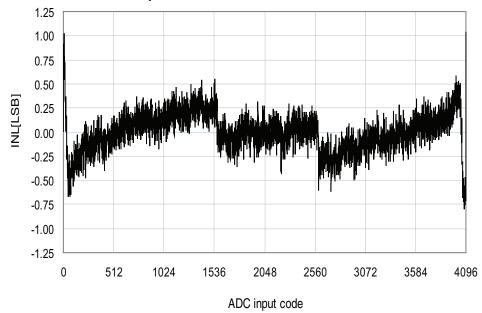

Figure 33-244.INL Error vs. Input Code

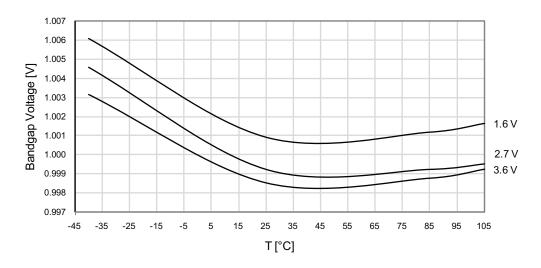

# 33.5.5 Internal 1.0V Reference Characteristics

Figure 33-327. ADC Internal 1.0V Reference vs. Temperature

# 33.5.6 BOD Characteristics

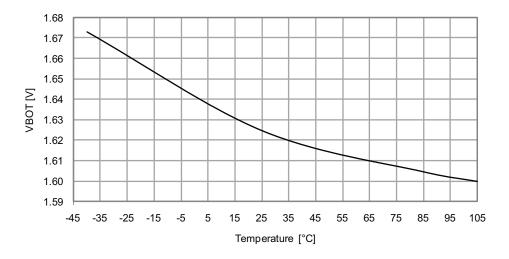

Figure 33-328. BOD Thresholds vs. Temperature BOD level = 1.6V

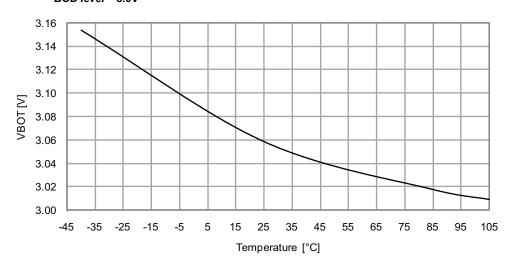

Figure 33-329. BOD Thresholds vs. Temperature BOD level = 3.0V

# 33.5.7 External Reset Characteristics

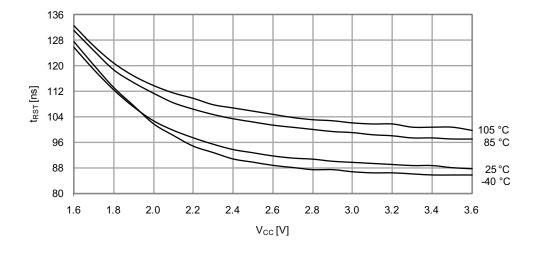

Figure 33-330. Minimum Reset Pin Pulse Width vs.  $V_{\text{CC}}$

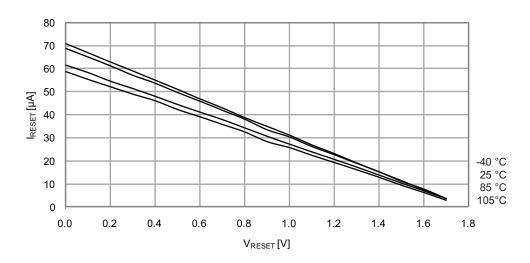

Figure 33-331. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC}$  = 1.8V

Figure 33-332. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage

# 33.6 Atmel ATxmega384D3

# 33.6.1 Current Consumption

# 33.6.1.1 Active Mode Supply Current

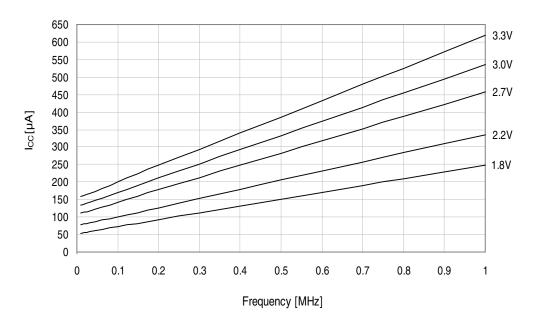

Figure 33-353. Active Supply Current vs. Frequency  $f_{SYS} = 0 - 1MHz$  external clock,  $T = 25^{\circ}C$

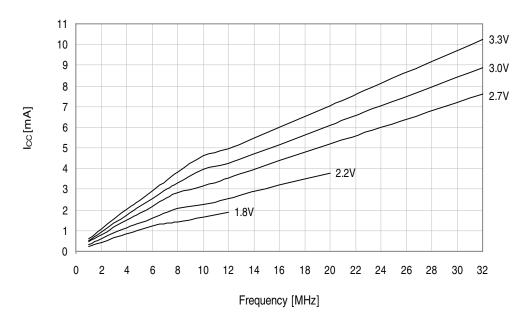

Figure 33-354. Active Supply Current vs. Frequency

$f_{SYS} = 1 - 32MHz$  external clock, T = 25°C

# 33.6.9 Two-Wire Interface Characteristics

Figure 33-417. SDA Hold Time vs. Temperature

Figure 33-418. SDA Hold Time vs. Supply Voltage

# 34. Errata

# 34.1 Atmel ATxmega32D3

#### 34.1.1 Rev. I

- AC system status flags are only valid if AC-system is enabled

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

# 1. AC system status flags are only valid if AC-system is enabled

The status flags for the ac-output are updated even though the AC is not enabled which is invalid. Also, it is not possible to clear the AC interrupt flags without enabling either of the Analog comparators.

#### Problem fix/workaround

Software should clear the AC system flags once, after enabling the AC system before using the AC system status flags.

### 2. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC, and Analog Comparator.

### Problem fix/workaround

If the bandgap is used as reference for either the ADC, DAC and Analog Comparator, the BOD must not be set in sampled mode.

### 3. Temperature sensor not calibrated

Temperature sensor factory calibration not implemented.

### Problem fix/workaround

None.

#### 34.1.2 Rev A - H

Not sampled.

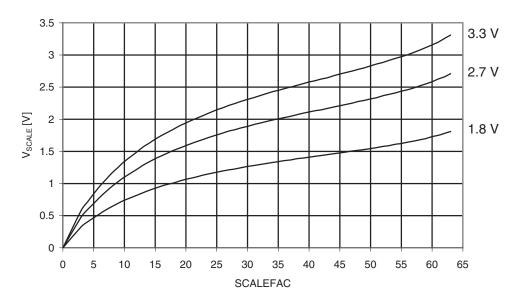

Figure 34-4. Analog Comparator Voltage Scaler vs. Scalefac T = 25°C

### Problem fix/workaround

Use external voltage input for the analog comparator if accurate voltage levels are needed.

### 3. ADC gain stage cannot be used for single conversion

The ADC gain stage will not output correct result for single conversion that is triggered and started from software or event system.

### Problem fix/workaround

When the gain stage is used, the ADC must be set in free running mode for correct results.

### 4. ADC has increased INL error for some operating conditions

Some ADC configurations or operating condition will result in increased INL error.

In signed mode INL is increased to:

6LSB for sample rates above 130ksps, and up to 8LSB for 200ksps sample rate.

6LSB for reference voltage below 1.1V when  $V_{CC}$  is above 3.0V.

20LSB for ambient temperature below 0°C and reference voltage below 1.3V.

In unsigned mode, the INL error cannot be guaranteed, and this mode should not be used.

### Problem fix/workaround

None, avoid using the ADC in the above configurations in order to prevent increased INL error. Use the ADC in signed mode also for single ended measurements.

### 5. ADC gain stage output range is limited to 2.4V

The amplified output of the ADC gain stage will never go above 2.4V, hence the differential input will only give correct output when below 2.4V/gain. For the available gain settings, this gives a differential input range of:

# Problem fix/workaround

The TxD pin direction can be set to input using the Port DIR register. Be advised that setting the Port DIR register to input will be immediate. Ongoing transmissions will be truncated.

### 34.3.10 Rev. A

Not sampled.

#### 34.4.8 Rev. B

- Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously

- VCC voltage scaler for AC is non-linear

- ADC gain stage cannot be used for single conversion

- ADC has increased INL error for some operating conditions

- ADC gain stage output range is limited to 2.4V

- ADC Event on compare match non-functional

- ADC propagation delay is not correct when 8x 64x gain is used

- Bandgap measurement with the ADC is non-functional when VCC is below 2.7V

- Accuracy lost on first three samples after switching input to ADC gain stage

- Configuration of PGM and CWCM not as described in the XMEGA D Manual

- PWM is not restarted properly after a fault in cycle-by-cycle mode

- BOD will be enabled at any reset

- EEPROM page buffer always written when NVM DATA0 is written

- Pending full asynchronous pin change interrupts will not wake the device

- Pin configuration does not affect Analog Comparator Output

- NMI Flag for Crystal Oscillator Failure automatically cleared

- Writing EEPROM or Flash while reading any of them will not work

- RTC Counter value not correctly read after sleep

- Pending asynchronous RTC-interrupts will not wake up device

- TWI Transmit collision flag not cleared on repeated start

- Clearing TWI Stop Interrupt Flag may lock the bus

- TWI START condition at bus timeout will cause transaction to be dropped

- TWI Data Interrupt Flag (DIF) erroneously read as set

- WDR instruction inside closed window will not issue reset

- Non available functions and options

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Temperature sensor not calibrated

### 1. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for another AC, the first comparator will be affected for up to 1µs and could potentially give a wrong comparison result.

# Problem fix/workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

### 2. VCC voltage scaler for AC is non-linear

The 6-bit VCC voltage scaler in the Analog Comparators is non-linear.