Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18854-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-3: PIC16(L)F18854 MEMORY MAP BANK 0-7

= Unimplemented data memory locations, read as '0'.

|      | BANK 0               |      | BANK 1         |      | BANK 2         |      | BANK 3         |      | BANK 4         |      | BANK 5         |      | BANK 6          |      | BANK 7          |

|------|----------------------|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|------|-----------------|------|-----------------|

| 000h |                      | 080h |                | 100h |                | 180h |                | 200h |                | 280h |                | 300h |                 | 380h |                 |

|      | Core Registers       |      | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers  |      | Core Registers  |

|      | (Table 3-2)          |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)     |      | (Table 3-2)     |

| 00Bh |                      | 08Bh |                | 10Bh |                | 18Bh |                | 20Bh |                | 28Bh |                | 30Bh |                 | 38Bh |                 |

| 00Ch | PORTA                | 08Ch | ADRESL         | 10Ch | ADCNT          | 18Ch | SSP1BUF        | 20Ch | TMR1L          | 28Ch | T2TMR          | 30Ch | CCPR1L          | 38Ch | PWM6DCL         |

| 00Dh | PORTB                | 08Dh | ADRESH         | 10Dh | ADRPT          | 18Dh | SSP1ADD        | 20Dh | TMR1H          | 28Dh | T2PR           | 30Dh | CCPR1H          | 38Dh | PWM6DCH         |

| 00Eh | PORTC                | 08Eh | ADPREVL        | 10Eh | ADLTHL         | 18Eh | SSP1MSK        | 20Eh | T1CON          | 28Eh | T2CON          | 30Eh | CCP1CON         | 38Eh | PWM6CON         |

| 00Fh | —                    | 08Fh | ADPREVH        | 10Fh | ADLTHH         | 18Fh | SSP1STAT       | 20Fh | T1GCON         | 28Fh | T2HLT          | 30Fh | CCP1CAP         | 38Fh | —               |

| 010h | PORTE                | 090h | ADACCL         | 110h | ADUTHL         | 190h | SSP1CON1       | 210h | T1GATE         | 290h | T2CLKCON       | 310h | CCPR2L          | 390h | PWM7DCL         |

| 011h | TRISA                | 091h | ADACCH         | 111h | ADUTHH         | 191h | SSP1CON2       | 211h | T1CLK          | 291h | T2RST          | 311h | CCPR2H          | 391h | PWM7DCH         |

| 012h | TRISB                | 092h |                | 112h | ADSTPTL        | 192h | SSP1CON3       | 212h | TMR3L          | 292h | T4TMR          | 312h | CCP2CON         | 392h | PWM7CON         |

| 013h | TRISC                | 093h | ADCON0         | 113h | ADSTPTH        | 193h | —              | 213h | TMR3H          | 293h | T4PR           | 313h | CCP2CAP         | 393h | —               |

| 014h | —                    | 094h | ADCON1         | 114h | ADFLTRL        | 194h | —              | 214h | T3CON          | 294h | T4CON          | 314h | CCPR3L          | 394h |                 |

| 015h | _                    | 095h | ADCON2         | 115h | ADFLTRH        | 195h | —              | 215h | T3GCON         | 295h | T4HLT          | 315h | CCPR3H          | 395h | —               |

| 016h | LATA                 | 096h | ADCON3         | 116h | ADERRL         | 196h | SSP2BUF        | 216h | T3GATE         | 296h | T4CLKCON       | 316h | CCP3CON         | 396h | —               |

| 017h | LATB                 | 097h | ADSTAT         | 117h | ADERRH         | 197h | SSP2ADD        | 217h | T3CLK          | 297h | T4RST          | 317h | CCP3CAP         | 397h | —               |

| 018h | LATC                 | 098h | ADCLK          | 118h | —              | 198h | SSP2MSK        | 218h | TMR5L          | 298h | T6TMR          | 318h | CCPR4L          | 398h |                 |

| 019h | —                    | 099h | ADACT          | 119h | RC1REG         | 199h | SSP2STAT       | 219h | TMR5H          | 299h | T6PR           | 319h | CCPR4H          | 399h |                 |

| 01Ah | —                    | 09Ah | ADREF          | 11Ah | TX1REG         | 19Ah | SSP2CON1       | 21Ah | T5CON          | 29Ah | T6CON          | 31Ah | CCP4CON         | 39Ah |                 |

| 01Bh | —                    | 09Bh | ADCAP          | 11Bh | SP1BRGL        | 19Bh | SSP2CON2       | 21Bh | T5GCON         | 29Bh | T6HLT          | 31Bh | CCP4CAP         | 39Bh |                 |

| 01Ch | TMR0L                | 09Ch | ADPRE          | 11Ch | SP1BRGH        | 19Ch | SSP2CON3       | 21Ch | T5GATE         | 29Ch | T6CLKCON       | 31Ch | CCPR5L          | 39Ch | —               |

| 01Dh | TMR0H                | 09Dh | ADACQ          | 11Dh | RC1STA         | 19Dh | —              | 21Dh | T5CLK          | 29Dh | T6RST          | 31Dh | CCPR5H          | 39Dh |                 |

| 01Eh | T0CON0               | 09Eh | ADPCH          | 11Eh | TX1STA         | 19Eh | —              | 21Eh | CCPTMRS0       | 29Eh | —              | 31Eh | CCP5CON         | 39Eh |                 |

| 01Fh | T0CON1               | 09Fh | —              | 11Fh | BAUD1CON       | 19Fh | —              | 21Fh | CCPTMRS1       | 29Fh | —              | 31Fh | CCP5CAP         | 39Fh | —               |

| 020h |                      | 0A0h |                | 120h |                | 1A0h |                | 220h |                | 2A0h |                | 320h | General Purpose | 3A0h |                 |

|      |                      |      |                |      |                |      |                |      |                |      |                |      | Register        |      |                 |

|      |                      |      | General        | 32Fh | 48 Bytes        |      |                 |

|      | - ·                  |      | Purpose        |      | . ,             |      | Unimplemented   |

|      | General              |      | Register       | 330h |                 |      | Read as '0'     |

|      | Purpose              |      | 80 Bytes       |      | Unimplemented   |      |                 |

|      | Register<br>96 Bytes |      |                |      |                |      |                |      |                |      |                |      | Read as '0'     |      |                 |

|      | 90 Byles             | 0EFh |                | 16Fh |                | 1EFh |                | 26Fh |                | 2EFh |                | 36Fh |                 | 3EFh |                 |

|      |                      | 0F0h | Common RAM     | 170h | Common RAM     | 1F0h | Common RAM     | 270h | Common RAM     | 2F0h | Common RAM     | 370h | Common RAM      | 3F0h | Common RAM      |

|      |                      |      | (Accesses       |      | (Accesses       |

| 07Fh |                      | 0FFh | 70h – 7Fh)     | 17Fh | 70h – 7Fh)     | 1FFh | 70h – 7Fh)     | 27Fh | 70h – 7Fh)     | 2FFh | 70h – 7Fh)     | 37Fh | 70h – 7Fh)      | 3FFh | ,<br>70h – 7Fh) |

Preliminary

DS40001826A-page 28

Legend:

| Address         | Name        | Bit 7   | Bit 6   | Bit 5   | Bit 4         | Bit 3        | Bit 2    | Bit 1   | Bit 0   | Value on:<br>POR, BOR | Value on all other Resets |

|-----------------|-------------|---------|---------|---------|---------------|--------------|----------|---------|---------|-----------------------|---------------------------|

| Bank 30         | (Continued) |         |         |         |               |              |          |         |         |                       |                           |

| F24h            | RC4PPS      | —       | —       |         |               | RC4          | PPS<5:0> |         |         | 00 0000               | uu uuuu                   |

| F25h            | RC5PPS      | —       | —       |         |               | RC5          | PPS<5:0> |         |         | 00 0000               | uu uuuu                   |

| F26h            | RC6PPS      | —       | —       |         |               | 00 0000      | uu uuuu  |         |         |                       |                           |

| F27h            | RC7PPS      | —       | —       |         |               | 00 0000      | uu uuuu  |         |         |                       |                           |

| F28h to<br>F37h | —           |         |         |         | Unimplemented |              |          |         |         |                       | —                         |

| F38h            | ANSELA      | ANSA7   | ANSA6   | ANSA5   | ANSA4         | ANSA3        | ANSA2    | ANSA1   | ANSA0   | 1111 1111             | 1111 1111                 |

| F39h            | WPUA        | WPUA7   | WPUA6   | WPUA5   | WPUA4         | WPUA3        | WPUA2    | WPUA1   | WPUA0   | 0000 0000             | 0000 0000                 |

| F3Ah            | ODCONA      | ODCA7   | ODCA6   | ODCA5   | ODCA4         | ODCA3        | ODCA2    | ODCA1   | ODCA0   | 0000 0000             | 0000 0000                 |

| F3Bh            | SLRCONA     | SLRA7   | SLRA6   | SLRA5   | SLRA4         | SLRA3        | SLRA2    | SLRA1   | SLRA0   | 1111 1111             | 1111 1111                 |

| F3Ch            | INLVLA      | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4       | INLVLA3      | INLVLA2  | INLVLA1 | INLVLA0 | 1111 1111             | 1111 1111                 |

| F3Dh            | IOCAP       | IOCAP7  | IOCAP6  | IOCAP5  | IOCAP4        | IOCAP3       | IOCAP2   | IOCAP1  | IOCAP0  | 0000 0000             | 0000 0000                 |

| F3Eh            | IOCAN       | IOCAN7  | IOCAN6  | IOCAN5  | IOCAN4        | IOCAN3       | IOCAN2   | IOCAN1  | IOCAN0  | 0000 0000             | 0000 0000                 |

| F3Fh            | IOCAF       | IOCAF7  | IOCAF6  | IOCAF5  | IOCAF4        | IOCAF3       | IOCAF2   | IOCAF1  | IOCAF0  | 0000 0000             | 0000 0000                 |

| F40h            | CCDNA       | CCDNA7  | CCDNA6  | CCDNA5  | CCDNA4        | CCDNA3       | CCDNA2   | CCDNA1  | CCDNA0  | 0000 0000             | 0000 0000                 |

| F41h            | CCDPA       | CCDPA7  | CCDPA6  | CCDPA5  | CCDPA4        | CCDPA3       | CCDPA2   | CCDPA1  | CCDPA0  | 0000 0000             | 0000 0000                 |

| F42h            | —           |         |         |         | U             | nimplemented |          |         | I       | —                     | _                         |

| F43h            | ANSELB      | ANSB7   | ANSB6   | ANSB5   | ANSB4         | ANSB3        | ANSB2    | ANSB1   | ANSB0   | 1111 1111             | 1111 1111                 |

| F44h            | WPUB        | WPUB7   | WPUB6   | WPUB5   | WPUB4         | WPUB3        | WPUB2    | WPUB1   | WPUB0   | 0000 0000             | 0000 0000                 |

| F45h            | ODCONB      | ODCB7   | ODCB6   | ODCB5   | ODCB4         | ODCB3        | ODCB2    | ODCB1   | ODCB0   | 0000 0000             | 0000 0000                 |

| F46h            | SLRCONB     | SLRB7   | SLRB6   | SLRB5   | SLRB4         | SLRB3        | SLRB2    | SLRB1   | SLRB0   | 1111 1111             | 1111 1111                 |

## TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18854 devices only.

2: Unimplemented, read as '1'.

| Name   | Bit 7  | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0   | Register<br>on Page |

|--------|--------|--------|-----------|-----------|--------|-----------|-----------|---------|---------------------|

| INTCON | GIE    | PEIE   | _         | _         |        | —         | _         | INTEDG  | 114                 |

| PIE0   | _      | —      | TMR0IE    | IOCIE     | _      | _         | _         | INTE    | 115                 |

| PIE1   | OSFIE  | CSWIE  | —         | —         | _      | —         | ADTIE     | ADIE    | 116                 |

| PIE2   | _      | ZCDIE  | —         | _         | _      | —         | C2IE      | C1IE    | 117                 |

| PIE3   | _      | _      | RCIE      | TXIE      | BCL2IE | SSP2IE    | BCL1IE    | SSP1IE  | 118                 |

| PIE4   | _      | —      | TMR6IE    | TMR5IE    | TMR4IE | TMR3IE    | TMR2IE    | TMR1IE  | 119                 |

| PIE5   | CLC4IE | CLC3IE | CLC2IE    | CLC1IE    | _      | TMR5GIE   | TMR3GIE   | TMR1GIE | 120                 |

| PIE6   | _      | —      | —         | CCP5IE    | CCP4IE | CCP3IE    | CCP2IE    | CCP1IE  | 121                 |

| PIE7   | SCANIE | CRCIE  | NVMIE     | NCO1IE    | —      | CWG3IE    | CWG2IE    | CWG1IE  | 122                 |

| PIE8   | _      | —      | SMT2PWAIE | SMT2PRAIE | SMT2IE | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 123                 |

| PIR0   | _      | —      | TMR0IF    | IOCIF     | _      | —         | _         | INTF    | 124                 |

| PIR1   | OSFIF  | CSWIF  | _         | _         | _      | _         | ADTIF     | ADIF    | 125                 |

| PIR2   | _      | ZCDIF  | _         | _         | _      | _         | C2IF      | C1IF    | 126                 |

| PIR3   | _      | _      | RCIF      | TXIF      | BCL2IF | SSP2IF    | BCL1IF    | SSP1IF  | 127                 |

| PIR4   | _      | _      | TMR6IF    | TMR5IF    | TMR4IF | TMR3IF    | TMR2IF    | TMR1IF  | 128                 |

| PIR5   | CLC4IF | CLC3IF | CLC2IF    | CLC1IF    |        | TMR5GIF   | TMR3GIF   | TMR1GIF | 129                 |

| PIR6   | _      | _      | —         | CCP5IF    | CCP4IF | CCP3IF    | CCP2IF    | CCP1IF  | 130                 |

| PIR7   | SCANIF | CRCIF  | NVMIF     | NCO1IF    | _      | CWG3IF    | CWG2IF    | CWG1IF  | 132                 |

| PIR8   | _      | _      | SMT2PWAIF | SMT2PRAIF | SMT2IF | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 133                 |

## TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

## 8.3 Register Definitions: Voltage Regulator and DOZE Control

## REGISTER 8-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER <sup>(1)</sup>

| U-0                                   | U-0 | U-0               | U-0                                                                  | U-0                                | U-0 | R/W-0/0 | R/W-1/1                                               |  |  |  |  |

|---------------------------------------|-----|-------------------|----------------------------------------------------------------------|------------------------------------|-----|---------|-------------------------------------------------------|--|--|--|--|

| _                                     |     |                   |                                                                      |                                    |     |         |                                                       |  |  |  |  |

|                                       | —   | —                 | —                                                                    | —                                  | _   | VREGPM  | Reserved                                              |  |  |  |  |

| bit 7                                 |     |                   |                                                                      |                                    |     |         | bit 0                                                 |  |  |  |  |

|                                       |     |                   |                                                                      |                                    |     |         |                                                       |  |  |  |  |

| Legend:                               |     |                   |                                                                      |                                    |     |         |                                                       |  |  |  |  |

| R = Readable bit W = Writable bit U = |     |                   |                                                                      | U = Unimplemented bit, read as '0' |     |         |                                                       |  |  |  |  |

| u = Bit is unchanged                  |     | x = Bit is unkn   | = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese |                                    |     |         | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set                      |     | '0' = Bit is clea | ared                                                                 |                                    |     |         |                                                       |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0' |

|---------|----------------------------|

| 1.11.4  |                            |

| bit 1 | VREGPM: Voltage Regulator Power Mode Selection bit       |

|-------|----------------------------------------------------------|

|       | 1 = Low-Power Sleep mode enabled in Sleep <sup>(2)</sup> |

|       | Draws lowest current in Sleep, slower wake-up            |

0 = Normal Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

bit 0 **Reserved:** Read as '1'. Maintain this bit set.

#### Note 1: PIC16F18855/75 only.

2: See Section 37.0 "Electrical Specifications".

### REGISTER 12-20: CCDPB: CURRENT CONTROLLED DRIVE POSITIVE PORTB REGISTER

| CCDPB7 CCDPB6 CCDPB | 5 CCDPB4 | CCDPB3  | CCDPB2 | CCDPB1 | CCDPB0 |

|---------------------|----------|---------|--------|--------|--------|

|                     |          | CCDI D3 | CCDFB2 | CCDFDI | CCDPBU |

| bit 7               |          |         |        |        | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

bit 7-0

- CCDPB<7:0>: RB<7:0> Current Controlled Drive Positive Control bits

- 1 = Current-controlled source enabled<sup>(1)</sup>

- 0 = Current-controlled source disabled

**Note 1:** If CCDPBy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

## REGISTER 12-21: CCDNB: CURRENT CONTROLLED DRIVE NEGATIVE PORTB REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCDNB7  | CCDNB6  | CCDNB5  | CCDNB4  | CCDNB3  | CCDNB2  | CCDNB1  | CCDNB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

CCDNB<7:0>: RB<7:0> Current Controlled Drive Negative Control bits

- 1 = Current-controlled source enabled<sup>(1)</sup>

- 0 = Current-controlled source disabled

**Note 1:** If CCDNBy is set when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 192                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 192                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 193                 |

| ANSELB  | ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 193                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 194                 |

| ODCONB  | ODCB7   | ODCB6   | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   | 194                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 195                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 195                 |

| CCDPB   | CCDPB7  | CCDPB6  | CCDPB5  | CCDPB4  | CCDPB3  | CCDPB2  | CCDPB1  | CCDPB0  | 196                 |

| CCDNB   | CCDNB7  | CCDNB6  | CCDNB5  | CCDNB4  | CCDNB3  | CCDNB2  | CCDNB1  | CCDNB0  | 196                 |

| CCDCON  | CCDEN   | _       | _       | _       | —       | _       | CCDS    | S<1:0>  | 181                 |

### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

Note 1: Unimplemented, read as '1'.

| R/W-0/0         | R/W-0/0                    | R/W-0/0                          | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|-----------------|----------------------------|----------------------------------|-----------------|----------------|------------------|------------------|-------------|

| NCOMD           | TMR6MD                     | TMR5MD                           | TMR4MD          | TMR3MD         | TMR2MD           | TMR1MD           | TMR0MD      |

| bit 7           | •                          |                                  |                 |                |                  |                  | bit 0       |

|                 |                            |                                  |                 |                |                  |                  |             |

| Legend:         |                            |                                  |                 |                |                  |                  |             |

| R = Readabl     | e bit                      | W = Writable                     | bit             | U = Unimplem   | nented bit, read | as '0'           |             |

| u = Bit is unc  | hanged                     | x = Bit is unkr                  | nown            | -n/n = Value a | t POR and BOI    | R/Value at all o | ther Resets |

| '1' = Bit is se | t                          | '0' = Bit is clea                | ared            | q = Value dep  | ends on condit   | ion              |             |

|                 |                            |                                  |                 |                |                  |                  |             |

| bit 7           |                            | able Numerical                   | ly Control Osci | illator bit    |                  |                  |             |

|                 |                            | odule disabled                   |                 |                |                  |                  |             |

| bit 6           |                            | sable Timer TM                   | 186             |                |                  |                  |             |

|                 |                            | odule disabled                   |                 |                |                  |                  |             |

|                 | 0 = TMR6 m                 | odule enabled                    |                 |                |                  |                  |             |

| bit 5           |                            | sable Timer TM                   | 1R5             |                |                  |                  |             |

|                 |                            | odule disabled                   |                 |                |                  |                  |             |

|                 |                            | odule enabled                    |                 |                |                  |                  |             |

| bit 4           |                            | sable Timer TN<br>odule disabled | 1R4             |                |                  |                  |             |

|                 |                            | odule enabled                    |                 |                |                  |                  |             |

| bit 3           | TMR3MD: Dis                | sable Timer TM                   | 1R3             |                |                  |                  |             |

|                 | -                          | odule disabled                   |                 |                |                  |                  |             |

|                 | 0 = TMR3 m                 | odule enabled                    |                 |                |                  |                  |             |

| bit 2           |                            | sable Timer TN                   | 1R2             |                |                  |                  |             |

|                 | 1 = TMR2 mo<br>0 = TMR2 mo | odule disabled                   |                 |                |                  |                  |             |

| bit 1           |                            | sable Timer TM                   |                 |                |                  |                  |             |

|                 |                            | odule disabled                   |                 |                |                  |                  |             |

|                 | 0 = TMR1 m                 | odule enabled                    |                 |                |                  |                  |             |

| bit 0           | TMR0MD: Dis                | sable Timer TM                   | 1R0             |                |                  |                  |             |

|                 |                            | odule disabled                   |                 |                |                  |                  |             |

|                 | 0 = TMR0 m                 | odule enabled                    |                 |                |                  |                  |             |

## 20.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWGxx pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWGxOCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWGxOCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWGxCON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 20.10 "Auto-Shutdown"**. An auto-shutdown event will only affect pins that have STRx = 1.

## 20.9.1 STEERING SYNCHRONIZATION

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

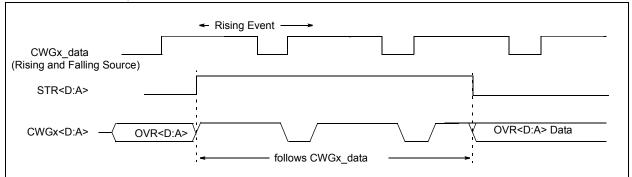

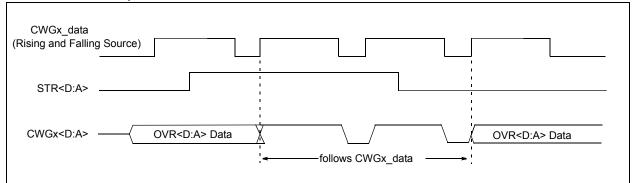

Figure 20-10 and Figure 20-11 illustrate the timing of asynchronous and synchronous steering, respectively.

FIGURE 20-10: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (MODE<2:0> = 000)

FIGURE 20-11: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (MODE<2:0> = 001)

| U-1            | R/W-0/0                                                                    | R/W-0/0                         | R/W-0/0     | R/W-0/0         | R/W-0/0          | R/W-0/0 | R/W-0/0      |

|----------------|----------------------------------------------------------------------------|---------------------------------|-------------|-----------------|------------------|---------|--------------|

|                | AS6E                                                                       | AS5E                            | AS4E        | AS3E            | AS2E             | AS1E    | AS0E         |

| bit 7          |                                                                            |                                 |             |                 |                  |         | bit (        |

|                |                                                                            |                                 |             |                 |                  |         |              |

| Legend:        |                                                                            |                                 |             |                 |                  |         |              |

| R = Readal     | ole bit                                                                    | W = Writable                    | bit         |                 | mented bit, read |         |              |

| u = Bit is ur  | nchanged                                                                   | x = Bit is unkr                 | nown        |                 | at POR and BO    |         | other Resets |

| '1' = Bit is s | et                                                                         | '0' = Bit is cle                | ared        | q = Value dep   | pends on condit  | ion     |              |

| bit 7          | Unimpleme                                                                  | nted: Read as '                 | 1'          |                 |                  |         |              |

| bit 6          | AS6E: CLC2                                                                 | 2 Output bit                    |             |                 |                  |         |              |

|                | 1 = LC2_ou                                                                 | t shut down is e                | nabled      |                 |                  |         |              |

|                | 0 = LC2_ou                                                                 | t shut down is d                | isabled     |                 |                  |         |              |

| bit 5          | AS5E: Com                                                                  | parator C2 Outp                 | ut bit      |                 |                  |         |              |

|                |                                                                            | ut shut-down is                 |             |                 |                  |         |              |

|                | •                                                                          | ut shut-down is                 |             |                 |                  |         |              |

| bit 4          | -                                                                          | parator C1 Outp                 |             |                 |                  |         |              |

|                |                                                                            | ut shut-down is ut shut-down is |             |                 |                  |         |              |

| bit 3          | •                                                                          | 6 Postscale Out                 |             |                 |                  |         |              |

|                |                                                                            | utput shut-dowr                 |             |                 |                  |         |              |

|                |                                                                            | utput shut-dowr                 |             |                 |                  |         |              |

| bit 2          | AS2E: TMR                                                                  | 4 Postscale Out                 | put bit     |                 |                  |         |              |

|                |                                                                            | utput shut-dowr                 |             |                 |                  |         |              |

|                |                                                                            | utput shut-dowr                 |             |                 |                  |         |              |

| bit 2          | AS1E: TMR2 Postscale Output bit<br>1 = TMR2 Postscale shut-down is enabled |                                 |             |                 |                  |         |              |

|                |                                                                            | ostscale shut-d                 |             |                 |                  |         |              |

| bit 0          | AS0E: CWG                                                                  | Sx Input Pin bit                |             |                 |                  |         |              |

|                |                                                                            | n selected by C\                | NGxPPS shut | -down is enabl  | ed               |         |              |

|                |                                                                            | •                               |             | -down is disabl |                  |         |              |

## REGISTER 20-6: CWGxAS1: CWGx AUTO-SHUTDOWN CONTROL REGISTER 1

## 22.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### **Note:** Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 22-3 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

| CLCxGLSy | LCxGyPOL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

#### TABLE 22-3: DATA GATING LOGIC

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 22-7)

- Gate 2: CLCxGLS1 (Register 22-8)

- Gate 3: CLCxGLS2 (Register 22-9)

- Gate 4: CLCxGLS3 (Register 22-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 22-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 22.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- · J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 22-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 22.1.4 OUTPUT POLARITY

The last stage in the Configurable Logic Cell is the output polarity. Setting the LCxPOL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

## 23.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 23-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 23-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 23-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

## EQUATION 23-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

ł

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.37\mus

Therefore:

$$TACQ = 2\mu s + 892ns + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

© 2016 Microchip Technology Inc.

## 24.1 NCO OPERATION

The NCO operates by repeatedly adding a fixed value to an accumulator. Additions occur at the input clock rate. The accumulator will overflow with a carry periodically, which is the raw NCO output (NCO\_overflow). This effectively reduces the input clock by the ratio of the addition value to the maximum accumulator value. See Equation 24-1.

The NCO output can be further modified by stretching the pulse or toggling a flip-flop. The modified NCO output is then distributed internally to other peripherals and can be optionally output to a pin. The accumulator overflow also generates an interrupt (NCO\_overflow).

The NCO period changes in discrete steps to create an average frequency. This output depends on the ability of the receiving circuit (i.e., CWG or external resonant converter circuitry) to average the NCO output to reduce uncertainty.

#### EQUATION 24-1: NCO OVERFLOW FREQUENCY

$FOVERFLOW = \frac{NCO \ Clock \ Frequency \times Increment \ Value}{2^{20}}$

## 24.1.1 NCO CLOCK SOURCES

Clock sources available to the NCO include:

- HFINTOSC

- Fosc

- LC1\_out

- LC2\_out

- LC3\_out

- LC4\_out

The NCO clock source is selected by configuring the N1CKS<2:0> bits in the NCO1CLK register.

#### 24.1.2 ACCUMULATOR

The accumulator is a 20-bit register. Read and write access to the accumulator is available through three registers:

- NCO1ACCL

- NCO1ACCH

- NCO1ACCU

#### 24.1.3 ADDER

The NCO Adder is a full adder, which operates independently from the source clock. The addition of the previous result and the increment value replaces the accumulator value on the rising edge of each input clock.

#### 24.1.4 INCREMENT REGISTERS

The increment value is stored in three registers making up a 20-bit incrementer. In order of LSB to MSB they are:

- NCO1INCL

- NCO1INCH

- NCO1INCU

When the NCO module is enabled, the NCO1INCU and NCO1INCH registers should be written first, then the NCO1INCL register. Writing to the NCO1INCL register initiates the increment buffer registers to be loaded simultaneously on the second rising edge of the NCO\_clk signal.

The registers are readable and writable. The increment registers are double-buffered to allow value changes to be made without first disabling the NCO module.

When the NCO module is disabled, the increment buffers are loaded immediately after a write to the increment registers.

**Note:** The increment buffer registers are not user-accessible.

| U-0                     | U-0                      | U-0                      | R/W-x/u          | R/W-x/u          | R/W-x/u          | R/W-x/u | R/W-x/u     |

|-------------------------|--------------------------|--------------------------|------------------|------------------|------------------|---------|-------------|

| _                       | _                        | _                        |                  |                  | MDMS<4:0>        |         |             |

| bit 7                   |                          |                          |                  |                  |                  |         | bit         |

| Levendu                 |                          |                          |                  |                  |                  |         |             |

| Legend:<br>R = Readable | e hit                    | W = Writable             | > hit            | l I = l Inimplen | nented bit, read | las '0' |             |

| u = Bit is unc          |                          | x = Bit is unl           |                  | •                | at POR and BO    |         | ther Resets |

| '1' = Bit is se         | •                        | '0' = Bit is cl          |                  |                  |                  |         |             |

| 1 Dit lo co             |                          |                          |                  |                  |                  |         |             |

| bit 7-5                 | Unimpleme                | ented: Read as           | <b>'</b> 0'      |                  |                  |         |             |

| bit 4-0                 | MDMS<4:0                 | > Modulation Se          | ource Selectior  | n bits           |                  |         |             |

|                         | 11111 <b>= Re</b>        | eserved. No cha          | nnel connecte    | d.               |                  |         |             |

|                         | •                        |                          |                  |                  |                  |         |             |

|                         | •                        |                          |                  |                  |                  |         |             |

|                         | 10100 = Re               | eserved. No cha          | nnel connecte    | d.               |                  |         |             |

|                         | 10011 <b>= M</b>         |                          |                  |                  |                  |         |             |

|                         | 10010 <b>= M</b>         |                          |                  |                  |                  |         |             |

|                         |                          | JSART TX/CK              |                  |                  |                  |         |             |

|                         |                          | JSART DT outp            | ut               |                  |                  |         |             |

|                         | 01111 = Cl<br>01110 = Cl |                          |                  |                  |                  |         |             |

|                         | 01101 = Cl               |                          |                  |                  |                  |         |             |

|                         | 01100 = Cl               |                          |                  |                  |                  |         |             |

|                         |                          | 2 (Comparator 2          |                  |                  |                  |         |             |

|                         |                          | 1 (Comparator 1          | ) output         |                  |                  |         |             |

|                         | 01001 = NO               | •                        |                  |                  |                  |         |             |

|                         |                          | NM7 output<br>NM6 output |                  |                  |                  |         |             |

|                         |                          | CP5 output (PW           | M Output mod     | e only)          |                  |         |             |

|                         |                          | CP4 output (PW           |                  |                  |                  |         |             |

|                         |                          | CP3 output (PW           |                  |                  |                  |         |             |

|                         | 00011 <b>= CO</b>        | CP2 output (PW           | M Output mod     | e only)          |                  |         |             |

|                         |                          | CP1 output (PW           |                  |                  |                  |         |             |

|                         | 00001 = M                | DRIT of MDCOI            | N0 register is m | nodulation sour  | ce               |         |             |

|                         | 00000 = M                |                          | to regiotor io n |                  | 00               |         |             |

## REGISTER 26-3: MDSRC: MODULATION SOURCE CONTROL REGISTER

| U-0                         |                                                                           | U-0                     | 3/5 GATE SE<br>R/W-0/u | R/W-0/u      | R/W-0/u         | R/W-0/u  | R/W-0/u      |

|-----------------------------|---------------------------------------------------------------------------|-------------------------|------------------------|--------------|-----------------|----------|--------------|

| _                           | _                                                                         | _                       |                        |              | GSS<4:0>        |          |              |

| bit 7                       |                                                                           |                         |                        |              |                 |          | bit          |

|                             |                                                                           |                         |                        |              |                 |          |              |

| <b>Legend</b> :<br>R = Read |                                                                           | W = Writable            | e bit                  | U = Unimplei | mented bit, rea | d as '0' |              |

|                             | unchanged                                                                 | x = Bit is unl          |                        | -            | at POR and BC   |          | other Resets |

| '1' = Bit is                | 0                                                                         | '0' = Bit is cl         |                        |              | leared by hardv |          |              |

|                             |                                                                           |                         |                        |              |                 |          |              |

| bit 7-5                     | -                                                                         | ented: Read as          |                        |              |                 |          |              |

| bit 4-0                     |                                                                           | Timer1 Gate S           | elect bits             |              |                 |          |              |

|                             | 11111 <b>= Re</b>                                                         | eserved                 |                        |              |                 |          |              |

|                             | •                                                                         |                         |                        |              |                 |          |              |

|                             | •                                                                         |                         |                        |              |                 |          |              |

|                             | 11001 <b>= Re</b>                                                         | eserved                 |                        |              |                 |          |              |

|                             | 11000 <b>= LC</b>                                                         |                         |                        |              |                 |          |              |

|                             | 10111 = LC                                                                |                         |                        |              |                 |          |              |

|                             | 10110 = LC<br>10101 = LC                                                  |                         |                        |              |                 |          |              |

|                             | 10100 = ZC                                                                |                         |                        |              |                 |          |              |

|                             | 10011 <b>= C</b> 2                                                        |                         |                        |              |                 |          |              |

|                             | 10010 <b>= C</b> 2                                                        |                         |                        |              |                 |          |              |

|                             | 10001 <b>= D</b> [                                                        |                         |                        |              |                 |          |              |

|                             | 10000 = PV                                                                |                         |                        |              |                 |          |              |

|                             | 01111 = PV<br>01110 = CC                                                  |                         |                        |              |                 |          |              |

|                             | 01101 <b>= C</b>                                                          |                         |                        |              |                 |          |              |

|                             | 01100 <b>= C</b>                                                          |                         |                        |              |                 |          |              |

|                             | 01011 <b>= CC</b>                                                         |                         |                        |              |                 |          |              |

|                             | 01010 <b>= C</b>                                                          |                         |                        |              |                 |          |              |

|                             | 01001 = SN                                                                | _                       |                        |              |                 |          |              |

|                             | 01000 = SN<br>00111 = TN                                                  | /IR6_postscale          | Ч                      |              |                 |          |              |

|                             |                                                                           | /IR5 overflow o         |                        |              |                 |          |              |

|                             |                                                                           | /IR4_postscale          |                        |              |                 |          |              |

|                             | 00100 = TN                                                                | /IR3 overflow o         | utput <sup>(2)</sup>   |              |                 |          |              |

|                             | 00011 = TN                                                                | /IR2_postscale          | d                      |              |                 |          |              |

|                             |                                                                           | IR1 overflow o          |                        |              |                 |          |              |

|                             | 00001 = 100000 = T100000 = T1000000 = T1000000 = T10000000 = T10000000000 | /IR0 overflow o<br>GPPS | սւթու                  |              |                 |          |              |

| Note 1:                     | For Timer1, this                                                          |                         |                        |              |                 |          |              |

| 2:                          | For Timer3, this                                                          |                         |                        |              |                 |          |              |

|                             |                                                                           |                         |                        |              |                 |          |              |

## REGISTER 28-4: TxGATE TIMER1/3/5 GATE SELECT REGISTER

- **2:** For Timer3, this bit is Reserved.

- **3:** For Timer5, this bit is Reserved.

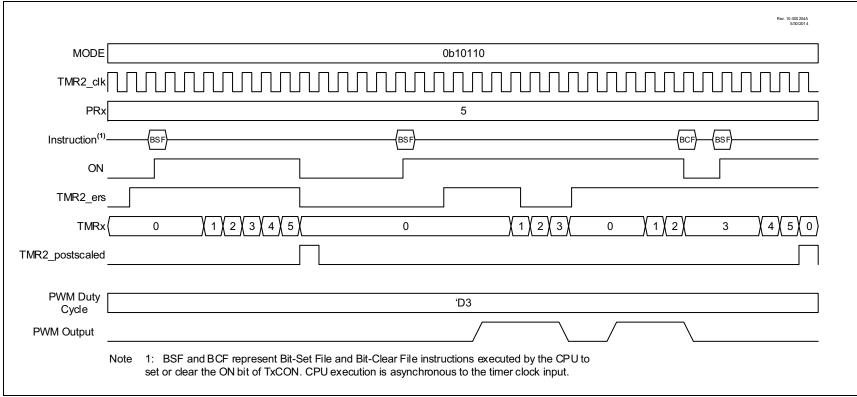

## FIGURE 29-13: LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE TIMING DIAGRAM (MODE = 10110)

#### REGISTER 30-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0

- MODE<3:0>: CCPx Mode Select bits<sup>(1)</sup> 1111 = PWM mode

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Compare mode: output will pulse 0-1-0; Clears TMR1

- 1010 = Compare mode: output will pulse 0-1-0

- 1001 = Compare mode: clear output on compare match

- 1000 = Compare mode: set output on compare match

- 0111 = Capture mode: every 16th rising edge of CCPx input

- 0110 = Capture mode: every 4th rising edge of CCPx input

- 0101 = Capture mode: every rising edge of CCPx input

- 0100 = Capture mode: every falling edge of CCPx input

- 0011 = Capture mode: every edge of CCPx input

- 0010 = Compare mode: toggle output on match

- 0001 = Compare mode: toggle output on match; clear TMR1

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- **Note 1:** All modes will set the CCPxIF bit, and will trigger an ADC conversion if CCPx is selected as the ADC trigger source.

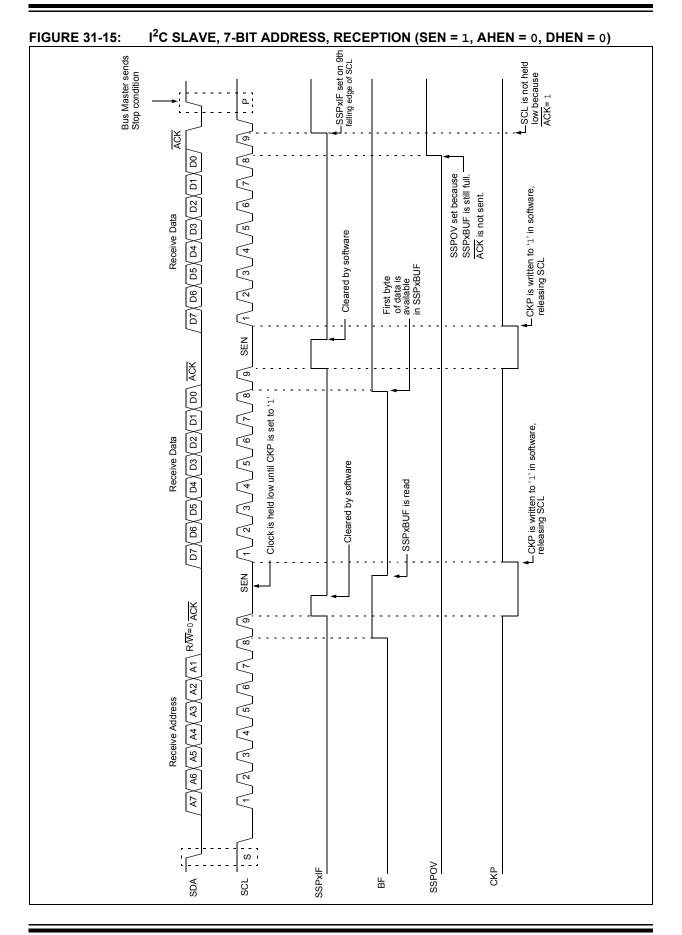

### REGISTER 31-5: SSPxMSK: SSPx MASK REGISTER

| R/W-1/1                                 | R/W-1/1                                                                                                                                                                                          | R/W-1/1          | R/W-1/1                                               | R/W-1/1      | R/W-1/1          | R/W-1/1  | R/W-1/1 |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------|--------------|------------------|----------|---------|--|

|                                         |                                                                                                                                                                                                  |                  | SSPxN                                                 | 1SK<7:0>     |                  |          |         |  |

| bit 7                                   |                                                                                                                                                                                                  |                  |                                                       |              |                  |          | bit 0   |  |

|                                         |                                                                                                                                                                                                  |                  |                                                       |              |                  |          |         |  |

| Legend:                                 |                                                                                                                                                                                                  |                  |                                                       |              |                  |          |         |  |

| R = Readable                            | e bit                                                                                                                                                                                            | W = Writable     | bit                                                   | U = Unimpler | nented bit, read | l as '0' |         |  |

| u = Bit is unchanged x = Bit is unknown |                                                                                                                                                                                                  | nown             | -n/n = Value at POR and BOR/Value at all other Resets |              |                  |          |         |  |

| '1' = Bit is set                        |                                                                                                                                                                                                  | '0' = Bit is cle | ared                                                  |              |                  |          |         |  |

| bit 7-1                                 | SSPyMSK<                                                                                                                                                                                         | 7:1>: Mask bits  |                                                       |              |                  |          |         |  |

|                                         | 1 = The received address bit n is compared to SSPxADD <n> to detect <math>I^2C</math> address match<br/>0 = The received address bit n is not used to detect <math>I^2C</math> address match</n> |                  |                                                       |              |                  |          |         |  |

| bit 0                                   | it 0 SSPxMSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address                                                                                                                        |                  |                                                       |              |                  |          |         |  |

|                                         | I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):                                                                                                                          |                  |                                                       |              |                  |          |         |  |

|                                         |                                                                                                                                                                                                  | eived address b  |                                                       |              |                  |          | atch    |  |

|                                         | 0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match                                                                                                              |                  |                                                       |              |                  |          |         |  |

MSK0 bit is ignored.

## **REGISTER 31-6:** SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SSPxAD  | D<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | SSPxADD<7:0>: Baud Rate Clock Divider bits      |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

I<sup>2</sup>C Slave mode, 7-bit address:

#### 10-Bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 SSPxADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode – Least Significant Address Byte:</u>

bit 7-0 SSPxADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

- bit 7-1 SSPxADD<7:1>: 7-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## REGISTER 32-16: SMTxPRL: SMT PERIOD REGISTER – LOW BYTE

| R/W-x/1          | R/W-x/1 | R/W-x/1           | R/W-x/1 | R/W-x/1        | R/W-x/1         | R/W-x/1        | R/W-x/1      |

|------------------|---------|-------------------|---------|----------------|-----------------|----------------|--------------|

|                  |         |                   | SMTxF   | PR<7:0>        |                 |                |              |

| bit 7            |         |                   |         |                |                 |                | bit 0        |

|                  |         |                   |         |                |                 |                |              |

| Legend:          |         |                   |         |                |                 |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, rea | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                 |                |              |

bit 7-0 SMTxPR<7:0>: Significant bits of the SMT Timer Value for Period Match – Low Byte

#### REGISTER 32-17: SMTxPRH: SMT PERIOD REGISTER – HIGH BYTE

| R/W-x/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SMTxPF  | R<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<15:8>: Significant bits of the SMT Timer Value for Period Match – High Byte

## REGISTER 32-18: SMTxPRU: SMT PERIOD REGISTER – UPPER BYTE

'0' = Bit is cleared

| R/W-x/1         | R/W-x/1 | R/W-x/1         | R/W-x/1 | R/W-x/1                                               | R/W-x/1 | R/W-x/1 | R/W-x/1 |  |  |  |

|-----------------|---------|-----------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

|                 |         |                 | SMTxPF  | R<23:16>                                              |         |         |         |  |  |  |

| bit 7           |         |                 |         |                                                       |         |         | bit 0   |  |  |  |

|                 |         |                 |         |                                                       |         |         |         |  |  |  |

| Legend:         |         |                 |         |                                                       |         |         |         |  |  |  |

| R = Readable    | bit     | W = Writable    | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unch | anged   | x = Bit is unkr | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

bit 7-0 SMTxPR<23:16>: Significant bits of the SMT Timer Value for Period Match – Upper Byte

'1' = Bit is set

|              |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

|              | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300          | _                 |                               | _                           | _                 |            | _                           |                   | _          | _                           |                    | _          | _                           |  |

| 1200         | —                 |                               | —                           | —                 |            | —                           | —                 | —          | —                           | —                  | —          | —                           |  |

| 2400         | —                 |                               | —                           | —                 | _          | —                           | —                 | —          | —                           | _                  | _          | _                           |  |

| 9600         | 9615              | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |  |

| 10417        | 10417             | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |  |

| 19.2k        | 19.23k            | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |  |

| 57.6k        | 57.14k            | -0.79                         | 34                          | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |  |

| 115.2k       | 117.64k           | 2.12                          | 16                          | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |  |

## TABLE 33-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

| BAUD<br>RATE | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

|              | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |