Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18854t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ρ          |

|------------|

| <b>C</b> 1 |

| 6          |

|            |

| )F1        |

| 88         |

| 354        |

|         |                        | 1      |             | 0              |               |                 | ,                 |             | 1        | 1                     |                           |

|---------|------------------------|--------|-------------|----------------|---------------|-----------------|-------------------|-------------|----------|-----------------------|---------------------------|

| Address | Name                   | Bit 7  | Bit 6       | Bit 5          | Bit 4         | Bit 3           | Bit 2             | Bit 1       | Bit 0    | Value on:<br>POR, BOR | Value on all other Resets |

| Banks 1 | 6                      |        |             |                |               |                 |                   |             |          |                       |                           |

|         |                        |        |             | c              | PU CORE REGIS | TERS; see Table | 3-2 for specifics |             |          |                       |                           |

| 80Ch    | WDTCON0                | —      | —           |                |               | PS<4:0>         |                   |             | SEN      | dd dddo               | dd dddo                   |

| 80Dh    | WDTCON1                | —      |             | WDTCS<2:0>     | >             | _               |                   | WINDOW<2:0> | •        | -বর্বর -বর্বর         | -ddd -ddd                 |

| 80Eh    | WDTPSL                 |        |             |                |               | PSCNT<7:0>      |                   |             |          | 0000 0000             | 0000 0000                 |

| 80Fh    | WDTPSH                 |        |             |                | I             | PSCNT<7:0>      |                   |             |          | 0000 0000             | 0000 0000                 |

| 810h    | WDTTMR                 | —      |             | WDT            | TMR<3:0>      |                 | STATE             | PSCNT       | <17:16>  | -000 0000             | -000 0000                 |

| 811h    | BORCON                 | SBOREN | —           | —              | —             | —               | —                 | —           | BORRDY   | 1q                    | u u                       |

| 812h    | VREGCON <sup>(1)</sup> | —      | _           | _              | —             | —               | —                 | VREGPM      | Reserved | 01                    | 01                        |

| 813h    | PCON0                  | STKOVF | STKUNF      | WDTWV          | RWDT          | RMCLR           | RI                | POR         | BOR      | 0011 11qq             | qqqq qquu                 |

| 814h    | CCDCON                 | CCDEN  | —           | _              | —             | _               | —                 | CCDS        | S<1:0>   | 0xx                   | 0uu                       |

| 815h    | _                      |        |             |                | U             | nimplemented    |                   |             |          | -                     | —                         |

| 816h    | _                      |        |             |                | U             | nimplemented    |                   |             |          | -                     | —                         |

| 817h    | _                      |        |             |                | U             | nimplemented    |                   |             |          | _                     | —                         |

| 818h    | _                      |        |             |                | U             | nimplemented    |                   |             |          | -                     | —                         |

| 819h    | _                      |        |             |                | U             | nimplemented    |                   |             |          | -                     | —                         |

| 81Ah    | NVMADRL                |        |             |                | Ν             | VMADR<7:0>      |                   |             |          | 0000 0000             | 0000 0000                 |

| 81Bh    | NVMADRH                | (2)    |             |                |               | NVMADR<14       | 4:8>              |             |          | 1000 0000             | 1000 0000                 |

| 81Ch    | NVMDATL                |        | NVMDAT<7:0> |                |               |                 |                   |             |          |                       | 0000 0000                 |

| 81Dh    | NVMDATH                | —      | —           | - NVMDAT<13:8> |               |                 |                   |             |          |                       | 00 0000                   |

| 81Eh    | NVMCON1                | —      | NVMREGS     | LWLO           | FREE          | WRERR           | WREN              | WR          | RD       | -000 x000             | -000 g000                 |

| 81Fh    | NVMCON2                |        |             |                | N             | /MCON2<7:0>     | •                 | -           | •        | 0000 0000             | 0000 0000                 |

# TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

DS40001826A-page 52

Legend:

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note

1:

Register present on PIC16F18854 devices only.

2: Unimplemented, read as '1'.

| Address | Name     | Bit 7           | Bit 6 | Bit 5 | Bit 4          | Bit 3           | Bit 2             | Bit 1   | Bit 0  | Value on: | Value on all |  |

|---------|----------|-----------------|-------|-------|----------------|-----------------|-------------------|---------|--------|-----------|--------------|--|

|         |          | DKI             | BRO   | Dir v | Dit 4          | Вко             | BRE               | Bitt    | BRU    | POR, BOR  | other Resets |  |

| Bank 29 |          |                 |       |       |                |                 |                   |         |        |           |              |  |

|         |          |                 |       | (     | CPU CORE REGIS | TERS; see Table | 3-2 for specifics |         |        |           |              |  |

| E8Ch    | _        |                 |       |       | U              | nimplemented    |                   |         |        | _         | _            |  |

| E8Dh    | _        |                 |       |       | U              | nimplemented    |                   |         |        | _         | _            |  |

| E8Eh    | -        | - Unimplemented |       |       |                |                 |                   |         |        |           |              |  |

| E8Fh    | PPSLOCK  | —               | —     | —     | -              | – – – PPSLOCKED |                   |         |        |           |              |  |

| E90h    | INTPPS   | _               | —     | _     | -              |                 | INTPPS            | <3:0>   | •      | 1000      | uuuu         |  |

| E91h    | TOCKIPPS | _               | —     | _     | -              |                 | TOCKIPF           | 'S<3:0> |        | 0100      | uuuu         |  |

| E92h    | T1CKIPPS | —               | —     | _     |                |                 | T1CKIPPS<4:0>     |         |        | 1 0000    | u uuuu       |  |

| E93h    | T1GPPS   | —               | —     | _     |                |                 | 0 1101            | u uuuu  |        |           |              |  |

| E94h    | T3CKIPPS | —               | —     | —     |                |                 | 1 0000            | u uuuu  |        |           |              |  |

| E95h    | T3GPPS   | —               | —     | _     |                | T3GPPS<4:0>     |                   |         |        |           |              |  |

| E96h    | T5CKIPPS | —               | —     | —     |                |                 | T5CKIPPS<4:0>     |         |        | 1 0000    | u uuuu       |  |

| E97h    | T5GPPS   | —               | —     | _     |                |                 | T5GPPS<4:0>       |         |        | 0 1100    | u uuuu       |  |

| E98h    | —        |                 |       |       | U              | nimplemented    |                   |         |        | _         | -            |  |

| E99h    | _        |                 |       |       | U              | nimplemented    |                   |         |        | _         | —            |  |

| E9Ah    | _        |                 |       |       | U              | nimplemented    |                   |         |        | _         | -            |  |

| E9Bh    | _        |                 |       |       | U              | nimplemented    |                   |         |        | _         | —            |  |

| E9Ch    | T2AINPPS | —               | —     | —     |                |                 | T2AINPPS<4:0>     |         |        | 1 0011    | u uuuu       |  |

| E9Dh    | T4AINPPS | —               | —     | _     |                |                 |                   | 1 0101  | u uuuu |           |              |  |

| E9Eh    | T6AINPPS | —               | —     | _     |                |                 | 0 1111            | u uuuu  |        |           |              |  |

| E9Fh    | _        |                 |       | _     | —              |                 |                   |         |        |           |              |  |

| EA0h    | _        |                 |       |       | _              | -               |                   |         |        |           |              |  |

| EA1h    | CCP1PPS  | —               | —     | —     |                |                 | CCP1PPS<4:0>      |         |        | 1 0010    | u uuuu       |  |

# TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, g =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Register present on PIC16F18854 devices only.

2: Unimplemented, read as '1'.

| IABLE             | 3-11: SPE                                       | CIAL FUNC     | TION RE       | GISTER SU |       | NKS 0-31 (C | ONTINUED) | 1       | •      |                       |                           |  |  |  |

|-------------------|-------------------------------------------------|---------------|---------------|-----------|-------|-------------|-----------|---------|--------|-----------------------|---------------------------|--|--|--|

| Address           | Name                                            | Bit 7         | Bit 6         | Bit 5     | Bit 4 | Bit 3       | Bit 2     | Bit 1   | Bit 0  | Value on:<br>POR, BOR | Value on all other Resets |  |  |  |

| Bank 31           |                                                 |               |               |           |       |             |           |         |        |                       |                           |  |  |  |

|                   | CPU CORE REGISTERS; see Table 3-2 for specifics |               |               |           |       |             |           |         |        |                       |                           |  |  |  |

| F8Ch<br>—<br>FE3h | _                                               | Unimplemented |               |           |       |             |           |         |        |                       | _                         |  |  |  |

| FE4h              | STATUS_SHAD                                     | —             | _             | _         | —     | —           | Z_SHAD    | DC_SHAD | C_SHAD | xxx                   | uuu                       |  |  |  |

| FE5h              | WREG_SHAD                                       |               | WREG_SHAD     |           |       |             |           |         |        | XXXX XXXX             | uuuu uuuu                 |  |  |  |

| FE6h              | BSR_SHAD                                        | _             | _             | BSR_SHAD  |       |             |           |         |        |                       | u uuuu                    |  |  |  |

| FE7h              | PCLATH_SHAD                                     | _             |               |           |       | PCLATH_SH   | IAD       |         |        | -xxx xxxx             | -uuu uuuu                 |  |  |  |

| FE8h              | FSR0L_SHAD                                      |               |               |           | F     | SR0L_SHAD   |           |         |        | xxxx xxxx             | uuuu uuuu                 |  |  |  |

| FE9h              | FSR0H_SHAD                                      |               |               |           | F     | SR0H_SHAD   |           |         |        | XXXX XXXX             | uuuu uuuu                 |  |  |  |

| FEAh              | FSR1L_SHAD                                      |               |               |           | F     | SR1L_SHAD   |           |         |        | XXXX XXXX             | uuuu uuuu                 |  |  |  |

| FEBh              | FSR1H_SHAD                                      |               |               |           | F     | SR1H_SHAD   |           |         |        | XXXX XXXX             | uuuu uuuu                 |  |  |  |

| FECh              | _                                               | Unimplemented | Unimplemented |           |       |             |           |         |        |                       |                           |  |  |  |

| FEDh              | STKPTR                                          | —             | STKPTR<4;0>   |           |       |             |           |         |        | 1 1111                | 1 1111                    |  |  |  |

| FEEh              | TOSL                                            | TOSL<7:0>     |               |           |       |             |           |         |        |                       | XXXX XXXX                 |  |  |  |

| FEFh              | TOSH                                            | —             |               |           |       | TOSH<6:0    | >         |         |        | -xxx xxxx             | -xxx xxxx                 |  |  |  |

# TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'. Legend:

Register present on PIC16F18854 devices only. Unimplemented, read as '1'. Note 1:

2:

# 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

# 4.7 Register Definitions: Device and Revision

# REGISTER 4-6: DEVID: DEVICE ID REGISTER

|                         |     | R      | R   | R     | R      | R | R     |  |  |  |  |

|-------------------------|-----|--------|-----|-------|--------|---|-------|--|--|--|--|

|                         |     |        |     | DEV<  | :13:8> |   |       |  |  |  |  |

|                         |     | bit 13 | 3 b |       |        |   |       |  |  |  |  |

|                         |     |        |     |       |        |   |       |  |  |  |  |

| R                       | R   | R      | R   | R     | R      | R | R     |  |  |  |  |

|                         |     |        | DEV | <7:0> |        |   |       |  |  |  |  |

| bit 7                   |     |        |     |       |        |   | bit 0 |  |  |  |  |

|                         |     |        |     |       |        |   |       |  |  |  |  |

| Legend:<br>R = Readable |     |        |     |       |        |   |       |  |  |  |  |

| R = Readable            | bit |        |     |       |        |   |       |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device       | DEVID<13:0> Values                 |

|--------------|------------------------------------|

| PIC16F18854  | 11 0000 0110 1010 ( <b>306Ah</b> ) |

| PIC16LF18854 | 11 0000 0110 1011 ( <b>306Bh</b> ) |

### REGISTER 4-7: REVISIONID: REVISION ID REGISTER

| R      | R | R | R           | R | R | R | R | R | R           | R     | R | R | R |  |

|--------|---|---|-------------|---|---|---|---|---|-------------|-------|---|---|---|--|

| 1      | 0 |   | MJRREV<5:0> |   |   |   |   |   | MNRREV<5:0> |       |   |   |   |  |

| bit 13 |   |   |             |   |   |   |   |   |             | bit 0 |   |   |   |  |

| Legend:              |                  |                    |  |

|----------------------|------------------|--------------------|--|

| R = Readable bit     |                  |                    |  |

| '0' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |  |

### bit 13-12 Fixed Value: Read-only bits

These bits are fixed with value '10' for all devices included in this data sheet.

### bit 11-6 MJRREV<5:0>: Major Revision ID bits

These bits are used to identify a major revision. A major revision is indicated by an all layer revision (B0, C0, etc.)

bit 5-0 **MNRREV<5:0>**: Minor Revision ID bits These bits are used to identify a minor revision.

| REGISTER                                                                                                   | (1-10) FIEO | . FERIFIERA                        |                  | ILNADLL        | REGISTER 0    |                   |            |  |

|------------------------------------------------------------------------------------------------------------|-------------|------------------------------------|------------------|----------------|---------------|-------------------|------------|--|

| U-0                                                                                                        | U-0         | R/W-0/0                            | R/W-0/0          | R/W-0/0        | R/W-0/0       | R/W-0/0           | R/W-0/0    |  |

|                                                                                                            | —           | SMT2PWAIE                          | SMT2PRAIE        | SMT2IE         | SMT1PWAIE     | SMT1PRAIE         | SMT1IE     |  |

| bit 7                                                                                                      |             | ·                                  |                  |                | •             |                   | bit C      |  |

|                                                                                                            |             |                                    |                  |                |               |                   |            |  |

| Legend:                                                                                                    |             |                                    |                  |                |               |                   |            |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                       |             |                                    |                  |                |               |                   |            |  |

| u = Bit is ur                                                                                              | nchanged    | x = Bit is unkn                    | own              | -n/n = Value   | at POR and BO | R/Value at all ot | her Resets |  |

| '1' = Bit is s                                                                                             | et          | '0' = Bit is clea                  | red              | HS = Hardwa    | are set       |                   |            |  |

|                                                                                                            |             |                                    |                  |                |               |                   |            |  |

| bit 7-6                                                                                                    | Unimpleme   | nted: Read as 'o                   | )'.              |                |               |                   |            |  |

| bit 6                                                                                                      | SMT2PWAIE   | E: SMT2 Pulse-V                    | Vidth Acquisitio | n Interrupt En | able bit      |                   |            |  |

|                                                                                                            |             | s the SMT acqui                    |                  |                |               |                   |            |  |

|                                                                                                            |             | es the SMT acqu                    | •                |                | •.            |                   |            |  |

| bit 5                                                                                                      |             | SMT2 Period /<br>s the SMT acqui   |                  | rrupt Enable b | bit           |                   |            |  |

|                                                                                                            |             | s the SMT acqui                    |                  |                |               |                   |            |  |

| bit 4                                                                                                      |             | IT2 Overflow Inte                  | •                |                |               |                   |            |  |

|                                                                                                            |             | s the SMT overf                    |                  |                |               |                   |            |  |

|                                                                                                            |             | es the SMT over                    | -                |                |               |                   |            |  |

| bit 2                                                                                                      |             | E: SMT1 Pulse-V                    | •                | n Interrupt En | able bit      |                   |            |  |

|                                                                                                            |             | s the SMT acqui<br>les the SMT acq | -                | +              |               |                   |            |  |

| bit 1                                                                                                      |             |                                    | •                |                | vit           |                   |            |  |

| bit 1 SMT1PRAIE: SMT1 Period Acquisition Interrupt Enable bit<br>1 = Enables the SMT acquisition interrupt |             |                                    |                  |                |               |                   |            |  |

|                                                                                                            |             | es the SMT acqu                    |                  |                |               |                   |            |  |

| bit 0                                                                                                      | SMT1IE: SM  | IT1 Overflow Inte                  | errupt Enable b  | it             |               |                   |            |  |

|                                                                                                            |             | s the SMT overf                    | •                |                |               |                   |            |  |

|                                                                                                            | 0 = Disabl  | es the SMT ove                     | rflow interrupt  |                |               |                   |            |  |

REGISTER 7-10: PIE8: PERIPHERAL INTERRUPT ENABLE REGISTER 8

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE8.

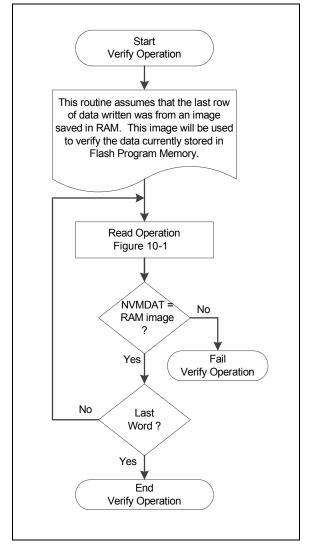

# 10.4.8 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

# REGISTER 11-3: CRCDATH: CRC DATA HIGH BYTE REGISTER

| R/W-xx               | R/W-x/x | R/W-x/x              | R/W-x/x | R/W-x/x           | R/W-x/x              | R/W-x/x             | R/W-x/x |

|----------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                      |         |                      | DAT<    | 15:8>             |                      |                     |         |

| bit 7                |         |                      |         |                   |                      |                     | bit 0   |

|                      |         |                      |         |                   |                      |                     |         |

| Legend:              |         |                      |         |                   |                      |                     |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 |                     |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | OR and BOR/Valu      | e at all other Rese | ets     |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0 DAT<15:8>: CRC Input/Output Data bits

# REGISTER 11-4: CRCDATL: CRC DATA LOW BYTE REGISTER

| R/W-xx               | R/W-x/x | R/W-x/x              | R/W-x/x | R/W-x/x           | R/W-x/x              | R/W-x/x              | R/W-x/x |

|----------------------|---------|----------------------|---------|-------------------|----------------------|----------------------|---------|

|                      |         |                      | DAT     | <7:0>             |                      |                      |         |

| bit 7                |         |                      |         |                   |                      |                      | bit 0   |

|                      |         |                      |         |                   |                      |                      |         |

| Legend:              |         |                      |         |                   |                      |                      |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 | ,                    |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | OR and BOR/Valu      | ue at all other Rese | ts      |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                      |         |

bit 7-0 DAT<7:0>

**DAT<7:0>**: CRC Input/Output Data bits Writing to this register fills the shifter.

### REGISTER 11-5: CRCACCH: CRC ACCUMULATOR HIGH BYTE REGISTER

| R/W-0/0            | R/W-0/0                           | R/W-0/0              | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|--------------------|-----------------------------------|----------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

|                    |                                   |                      | ACC                                                   | <15:8>                             |         |         |         |  |

| bit 7              |                                   |                      |                                                       |                                    |         |         | bit 0   |  |

|                    |                                   |                      |                                                       |                                    |         |         |         |  |

| Legend:            |                                   |                      |                                                       |                                    |         |         |         |  |

| R = Readable bit   | R = Readable bit W = Writable bit |                      |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchang | jed                               | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         | ets     |  |

| '1' = Bit is set   |                                   | '0' = Bit is cleared |                                                       |                                    |         |         |         |  |

bit 7-0 ACC<15:8>: CRC Accumulator Register bits

Writing to this register writes to the CRC accumulator register. Reading from this register reads the CRC accumulator.

# REGISTER 11-6: CRCACCL: CRC ACCUMULATOR LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|----------|---------|---------|---------|---------|---------|---------|

|         | ACC<7:0> |         |         |         |         |         |         |

| bit 7   | bit 7 b  |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ACC<7:0>: CRC Accumulator Register bits

Writing to this register writes to the CRC accumulator register through the CRC write bus. Reading from this register reads the CRC accumulator.

# REGISTER 11-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0                  | R-0 | R-0                                                               | R-0 | R-0                                | R-0 | R-0                 | R-0   |

|----------------------|-----|-------------------------------------------------------------------|-----|------------------------------------|-----|---------------------|-------|

|                      |     |                                                                   | SHI | -T<15:8>                           |     |                     |       |

| bit 7                |     |                                                                   |     |                                    |     |                     | bit 0 |

|                      |     |                                                                   |     |                                    |     |                     |       |

| Legend:              |     |                                                                   |     |                                    |     |                     |       |

| R = Readable bit     |     | W = Writable bit                                                  |     | U = Unimplemented bit, read as '0' |     |                     |       |

| u = Bit is unchanged |     | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other |     |                                    |     | ue at all other Res | ets   |

| '1' = Bit is set     |     | '0' = Bit is cleared                                              |     |                                    |     |                     |       |

bit 7-0

SHIFT<15:8>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

# REGISTER 11-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|

| SHIFT<7:0> |     |     |     |     |     |     |       |  |

| bit 7      |     |     |     |     |     |     | bit 0 |  |

|            |     |     |     |     |     |     |       |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

SHIFT<7:0>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

# REGISTER 11-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |  |

|---------|-----|-----|-----|-----|-----|-----|-------|--|

| X<15:8> |     |     |     |     |     |     |       |  |

| bit 7   |     |     |     |     |     |     | bit 0 |  |

|         |     |     |     |     |     |     |       |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 X<15:8>: XOR of Polynomial Term X<sub>N</sub> Enable bits

# REGISTER 11-10: CRCXORL: CRC XOR LOW BYTE REGISTER

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 XOR<7:1>: XOR of Polynomial Term X<sub>N</sub> Enable bits

bit 0 Unimplemented: Read as '1'

© 2016 Microchip Technology Inc.

### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| R/W-1/1 | R/W-1/1 | R/W-x/u | R/W-x/u | R/W-1/1 | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         | •       |         |         |         | •       | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATA<7:0>: RA<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

# REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSA7   | ANSA6   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSA<7:0>: Analog Select between Analog or Digital Function on pins RA<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

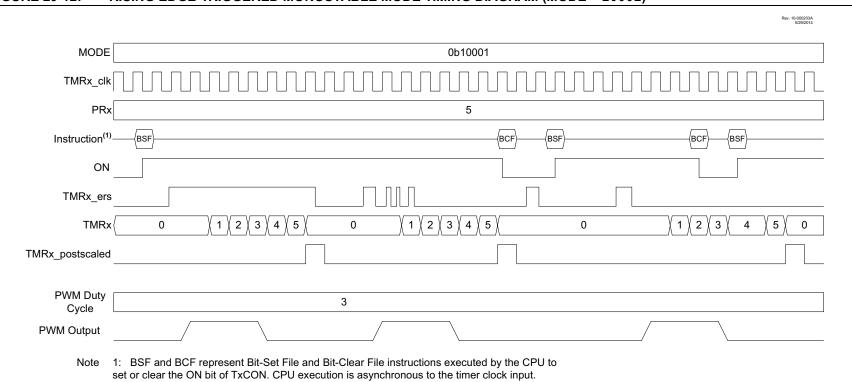

# FIGURE 29-12:

# 29-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

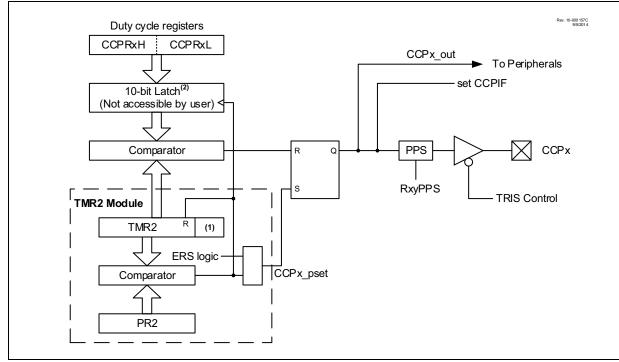

# FIGURE 30-4: SIMPLIFIED PWM BLOCK DIAGRAM

# 30.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the CCPxFMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

- Note: In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

# 30.3.3 CCP/PWM CLOCK SELECTION

The PIC16F18855/75 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2/4/6), PWM mode on the CCP and PWM modules can use any of these timers. The CCPTMRS0 and CCPTMRS1 registers is used to select which timer is used.

# REGISTER 31-7: SSPxBUF: MSSPx BUFFER REGISTER

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x         | R/W-x           | R/W-x  | R/W-x |

|------------------|-------|------------------|-------|---------------|-----------------|--------|-------|

|                  |       |                  | SSPxB | UF<7:0>       |                 |        |       |

| bit 7            |       |                  |       |               |                 |        | bit 0 |

|                  |       |                  |       |               |                 |        |       |

| Legend:          |       |                  |       |               |                 |        |       |

| D - Doodoblo bit |       | M = Mritable bit |       | II – Unimplor | nonted hit read | oo 'O' |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SSPxBUF<7:0>: MSSP Buffer bits

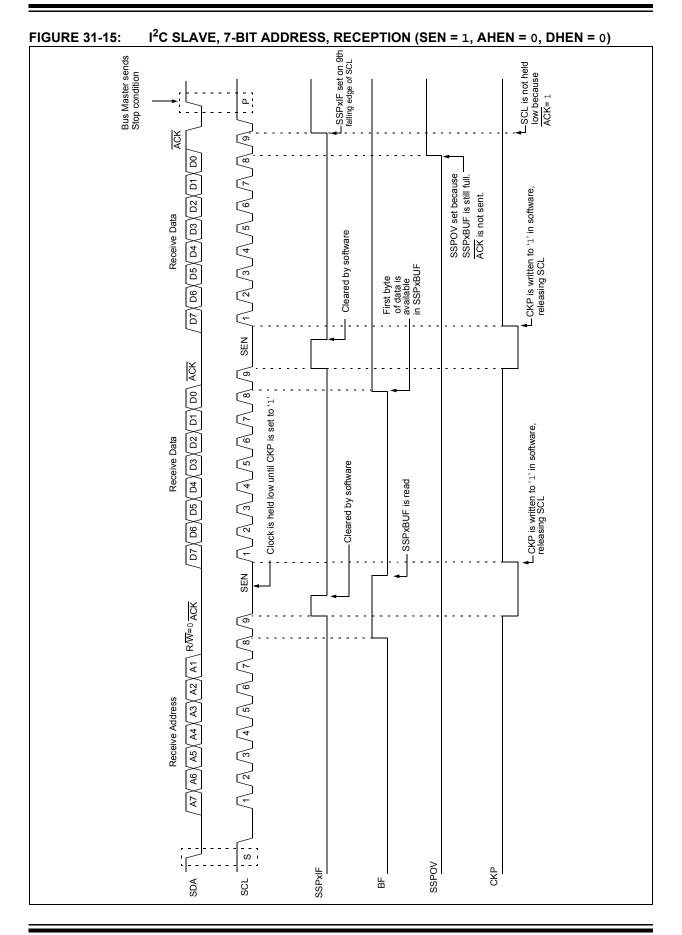

#### TABLE 31-3: SUMMARY OF REGISTERS ASSOCIATED WITH MSSPx

| Name       | Bit 7  | Bit 6   | Bit 5 | Bit 4       | Bit 3  | Bit 2       | Bit 1 | Bit 0  | Register<br>on Page |

|------------|--------|---------|-------|-------------|--------|-------------|-------|--------|---------------------|

| INTCON     | GIE    | PEIE    | —     | —           | —      | —           | —     | INTEDG | 114                 |

| PIR1       | OSFIF  | CSWIF   | —     | —           | —      | —           | ADTIF | ADIF   | 125                 |

| PIE1       | OSFIE  | CSWIE   | —     | —           | —      | —           | ADTIE | ADIE   | 116                 |

| SSP1STAT   | SMP    | CKE     | D/A   | Р           | S      | R/W         | UA    | BF     | 469                 |

| SSP1CON1   | WCOL   | SSPOV   | SSPEN | CKP         |        | SSPM        | <3:0> |        | 470                 |

| SSP1CON2   | GCEN   | ACKSTAT | ACKDT | ACKEN       | RCEN   | PEN         | RSEN  | SEN    | 471                 |

| SSP1CON3   | ACKTIM | PCIE    | SCIE  | BOEN        | SDAHT  | SBCDE       | AHEN  | DHEN   | 469                 |

| SSP1MSK    |        |         |       | SSPMS       | K<7:0> |             |       |        | 473                 |

| SSP1ADD    |        |         |       | SSPAD       | D<7:0> |             |       |        | 473                 |

| SSP1BUF    |        |         |       | SSPBUF<7:0> |        |             |       |        | 474                 |

| SSP2STAT   | SMP    | CKE     | D/A   | Р           | S      | R/W         | UA    | BF     | 469                 |

| SSP2CON1   | WCOL   | SSPOV   | SSPEN | CKP         |        | SSPM        | <3:0> |        | 470                 |

| SSP2CON2   | GCEN   | ACKSTAT | ACKDT | ACKEN       | RCEN   | PEN         | RSEN  | SEN    | 471                 |

| SSP2CON3   | ACKTIM | PCIE    | SCIE  | BOEN        | SDAHT  | SBCDE       | AHEN  | DHEN   | 469                 |

| SSP2MSK    |        |         |       | SSPMS       | K<7:0> |             |       |        | 473                 |

| SSP2ADD    |        |         |       | SSPAD       | D<7:0> |             |       |        | 473                 |

| SSP2BUF    |        |         |       | SSPBU       | F<7:0> |             |       |        | 474                 |

| SSP1CLKPPS | _      | —       | —     |             | SSF    | P1CLKPPS<4  | :0>   |        | 214                 |

| SSP1DATPPS | _      | _       | —     |             | SSF    | P1DATPPS<4  | :0>   |        | 214                 |

| SSP1SSPPS  | _      | _       | _     |             | SS     | P1SSPPS<4:  | 0>    |        | 214                 |

| SSP2CLKPPS |        | —       | _     |             | SSF    | 2CLKPPS<4   | :0>   |        | 214                 |

| SSP2DATPPS |        | —       | —     |             | SSF    | 2DATPPS<4   | :0>   |        | 214                 |

| SSP2SSPPS  | _      | —       | —     |             | SS     | P2SSPPS<4:  | 0>    |        | 214                 |

| RxyPPS     | —      | —       | —     |             | F      | RxyPPS<4:0> |       |        | 215                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx module

**Note 1:** When using designated  $I^2C$  pins, the associated pin values in INLVLx will be ignored.

# 32.8 Register Definitions: SMT Control

Long bit name prefixes for the Signal Measurement Timer peripherals are shown in **Section 1.1** "**Register and Bit naming conventions**".

# TABLE 32-2:LONG BIT NAMES PREFIXES<br/>FOR SMT PERIPHERALS

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| SMT1       | SMT1            |

| SMT2       | SMT2            |

# REGISTER 32-1: SMTxCON0: SMT CONTROL REGISTER 0

| R/W-0/0           | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 |

|-------------------|-----|---------|---------|---------|---------|-------------|---------|

| EN <sup>(1)</sup> | —   | STP     | WPOL    | SPOL    | CPOL    | SMTxPS<1:0> |         |

| bit 7             |     |         |         |         |         |             | bit 0   |

| Legend:          |                                                                                                                                                                                                                             |                          |                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------|--|--|--|

| R = Readable     | bit                                                                                                                                                                                                                         | W = Writable bit         | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                                                                       | x = Bit is unknown       | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                             | '0' = Bit is cleared     |                                                       |  |  |  |

| bit 7            | <b>EN:</b> SMT Er<br>1 = SMT is 0<br>0 = SMT is 0                                                                                                                                                                           | enabled                  | e reset, clock requests are disabled                  |  |  |  |

| bit 6            | Unimpleme                                                                                                                                                                                                                   | nted: Read as '0'        |                                                       |  |  |  |

| bit 5            | <b>STP:</b> SMT Counter Halt Enable bit<br>When SMTxTMR = SMTxPR:<br>1 = Counter remains SMTxPR; period match interrupt occurs when clocked<br>0 = Counter resets to 24'h000000; period match interrupt occurs when clocked |                          |                                                       |  |  |  |

| bit 4            | WPOL: SMTxWIN Input Polarity Control bit<br>1 = SMTxWIN signal is active-low/falling edge enabled<br>0 = SMTxWIN signal is active-high/rising edge enabled                                                                  |                          |                                                       |  |  |  |

| bit 3            | <b>SPOL:</b> SMTxSIG Input Polarity Control bit<br>1 = SMTx_signal is active-low/falling edge enabled<br>0 = SMTx_signal is active-high/rising edge enabled                                                                 |                          |                                                       |  |  |  |

| bit 2            | <b>CPOL:</b> SMT Clock Input Polarity Control bit<br>1 = SMTxTMR increments on the falling edge of the selected clock signal<br>0 = SMTxTMR increments on the rising edge of the selected clock signal                      |                          |                                                       |  |  |  |

| bit 1-0          | SMTxPS<1<br>11 = Presca<br>10 = Presca<br>01 = Presca<br>00 = Presca                                                                                                                                                        | aler = 1:4<br>aler = 1:2 | bits                                                  |  |  |  |

**Note 1:** Setting EN to '0' does not affect the register contents.

# 33.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUD1CON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Figure 33-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 33-1. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 33.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

### TABLE 33-1: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

#### 0000h XXXXh 001Ch **BRG** Value Edge #5 Edge #1 Edge #2 Edge #3 Edge #4 bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7 RX pin Start Stop bit Auto Cleared Set by User ABDEN bit RCIDL RCIF bit (Interrupt) Read RCREG SPBRGL XXh 1Ch XXh 00h SPBRGH Note 1: The ABD sequence requires the EUSART module to be configured in Asynchronous mode.

# FIGURE 33-6: AUTOMATIC BAUD RATE CALIBRATION

# 33.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TX1STA register configures the device for synchronous operation. Clearing the CSRC bit of the TX1STA register configures the device as a slave. Clearing the SREN and CREN bits of the RC1STA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RC1STA register enables the EUSART.

### 33.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 33.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 33.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

### TABLE 37-6: THERMAL CHARACTERISTICS

| Standar       | d Operating | Conditions (unless otherwise stated)   |                               |        |                                                             |

|---------------|-------------|----------------------------------------|-------------------------------|--------|-------------------------------------------------------------|

| Param.<br>No. | Sym.        | Characteristic                         | Тур.                          | Units  | Conditions                                                  |

| TH01          | θJA         | Thermal Resistance Junction to Ambient | 60                            | °C/W   | 28-pin SPDIP package                                        |

|               |             |                                        | 80                            | °C/W   | 28-pin SOJC package                                         |

|               |             |                                        | 90                            | °C/W   | 28-pin \$\$0P pa¢kage                                       |

|               |             |                                        | 27.5                          | °C/W   | 28-pin UQFN 4x4 mm package                                  |

|               |             |                                        | 27.5                          | °C/W   | 28-pin QFN 6x6mm package                                    |

| TH02          | θJC         | Thermal Resistance Junction to Case    | 31.4                          | °C/W   | 28-pin SPDIP package                                        |

|               |             |                                        | 24                            | °C/W   | 28-pin SOIC package                                         |

|               |             |                                        | 24                            | °C/W   | 28-pin SSOP package                                         |

|               |             |                                        | 24                            | °C/W   | 28 pin VQFN 4x4mm package                                   |

|               |             |                                        | 24                            | ∕_°C/W | 28-pin QFN 6x6mm package                                    |

| TH03          | TJMAX       | Maximum Junction Temperature           | 150                           | 26     | $\langle \rangle$                                           |

| TH04          | PD          | Power Dissipation                      | 7                             | W      | PD YPINTERNAL + PI/O                                        |

| TH05          | PINTERNAL   | Internal Power Dissipation             | Ę,                            | Ŵ      | PINTERNAL = IDD x VDD <sup>(1)</sup>                        |

| TH06          | Pi/o        | I/O Power Dissipation                  |                               | W      | $P_{I}/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07          | Pder        | Derated Power                          | $\langle \mathcal{F} \rangle$ | W      | РDER = PDмах (Тј - Та)/θја <sup>(2)</sup>                   |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

# 39.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 39.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- · Built-in support for Bugzilla issue tracker

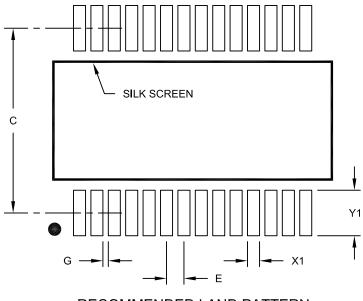

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units            |      |          | S    |  |

|--------------------------|------------------|------|----------|------|--|

| Dimension                | Dimension Limits |      |          | MAX  |  |

| Contact Pitch            | E                |      | 0.65 BSC |      |  |

| Contact Pad Spacing      | С                |      | 7.20     |      |  |

| Contact Pad Width (X28)  | X1               |      |          | 0.45 |  |

| Contact Pad Length (X28) | Y1               |      |          | 1.75 |  |

| Distance Between Pads    | G                | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A