#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18854t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ρ   |

|-----|

|     |

| 6   |

|     |

| )F1 |

| 88  |

| 54  |

| Address | Name                                            | Bit 7  | Bit 6     | Bit 5 | Bit 4 | Bit 3        | Bit 2 | Bit 1     | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |  |

|---------|-------------------------------------------------|--------|-----------|-------|-------|--------------|-------|-----------|---------|-----------------------|------------------------------|--|

| Bank 10 | 0                                               |        |           |       |       |              |       |           |         |                       |                              |  |

|         | CPU CORE REGISTERS; see Table 3-2 for specifics |        |           |       |       |              |       |           |         |                       |                              |  |

| 50Ch    | SMT2TMRL                                        |        |           |       |       | TMR<7:0>     |       |           |         | 0000 0000             | 0000 0000                    |  |

| 50Dh    | SMT2TMRH                                        |        |           |       |       | TMR<15:8>    |       |           |         | 0000 0000             | 0000 0000                    |  |

| 50Eh    | SMT2TMRU                                        |        |           |       | -     | TMR<23:16>   |       |           |         | 0000 0000             | 0000 0000                    |  |

| 50Fh    | SMT2CPRL                                        |        |           |       |       | CPR<7:0>     |       |           |         | xxxx xxxx             | uuuu uuuu                    |  |

| 510h    | SMT2CPRH                                        |        |           |       |       | CPR<15:8>    |       |           |         | xxxx xxxx             | uuuu uuuu                    |  |

| 511h    | SMT2CPRU                                        |        |           |       | (     | CPR<23:16>   |       |           |         | xxxx xxxx             | uuuu uuuu                    |  |

| 512h    | SMT2CPWL                                        |        |           |       |       | CPW<7:0>     |       |           |         | xxxx xxxx             | uuuu uuuu                    |  |

| 513h    | SMT2CPWH                                        |        | CPW<15:8> |       |       |              |       |           |         | xxxx xxxx             | uuuu uuuu                    |  |

| 514h    | SMT2CPWU                                        |        |           |       | (     | CPW<23:16>   |       |           |         | xxxx xxxx             | uuuu uuuu                    |  |

| 515h    | SMT2PRL                                         |        |           |       |       | PR<7:0>      |       |           |         | 1111 1111             | 1111 1111                    |  |

| 516h    | SMT2PRH                                         |        |           |       |       | PR<15:8>     |       |           |         | 1111 1111             | 1111 1111                    |  |

| 517h    | SMT2PRU                                         |        |           |       |       | PR<23:16>    |       |           |         | 1111 1111             | 1111 1111                    |  |

| 518h    | SMT2CON0                                        | EN     | —         | STP   | WPOL  | SPOL         | CPOL  | SMT2F     | PS<1:0> | 0-00 0000             | 0-00 0000                    |  |

| 519h    | SMT2CON1                                        | SMT2GO | REPEAT    | —     | —     |              | MODE  | <3:0>     |         | 00 0000               | 00 0000                      |  |

| 51Ah    | SMT2STAT                                        | CPRUP  | CPWUP     | RST   | —     | —            | TS    | WS        | AS      | 000000                | 000000                       |  |

| 51Bh    | SMT2CLK                                         | _      | —         | _     | _     | _            |       | CSEL<2:0> |         | 000                   | 000                          |  |

| 51Ch    | SMT2SIG                                         | —      | —         | _     |       | SSEL<4:0>    |       |           |         | 0 0000                | 0 0000                       |  |

| 51Dh    | SMT2WIN                                         | —      | —         | _     |       | WSEL<4:0>    |       |           |         |                       | 0 0000                       |  |

| 51Eh    | _                                               |        |           |       | U     | nimplemented |       |           |         | -                     | —                            |  |

| 51Fh    | —                                               |        |           |       | U     | nimplemented |       |           |         | -                     | _                            |  |

## TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

x = unknown, u = unchanged, g =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Register present on PIC16F18854 devices only. Unimplemented, read as '1'. Legend:

Note 1:

2:

## TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

| Address                                         | Name           | Bit 7        | Bit 6         | Bit 5             | Bit 4             | Bit 3                | Bit 2                | Bit 1             | Bit 0      | Value on:<br>POR, BOR | Value on all other Resets |

|-------------------------------------------------|----------------|--------------|---------------|-------------------|-------------------|----------------------|----------------------|-------------------|------------|-----------------------|---------------------------|

| Bank 20-27                                      |                |              |               |                   |                   |                      |                      |                   |            |                       |                           |

|                                                 |                |              |               |                   |                   |                      |                      |                   |            |                       |                           |

| CPU CORE REGISTERS; see Table 3-2 for specifics |                |              |               |                   |                   |                      |                      |                   |            |                       |                           |

| x0Ch/                                           | —              |              |               |                   | Ur                | nimplemented         |                      |                   |            | —                     | —                         |

| x8Ch                                            |                |              |               |                   |                   |                      |                      |                   |            |                       |                           |

| x1Fh/                                           |                |              |               |                   |                   |                      |                      |                   |            |                       |                           |

| x9Fh                                            |                |              |               |                   |                   |                      |                      |                   |            |                       |                           |

| Legend:                                         | x = unknown, u | = unchanged, | g =depends on | condition, - = un | implemented, read | d as '0', r = reserv | ed. Shaded locations | unimplemented, re | ad as '0'. |                       |                           |

Register present on PIC16F18854 devices only. Unimplemented, read as '1'. Note 1:

2:

# DS40001826A-page 56

#### 3.3 PCL and PCLATH

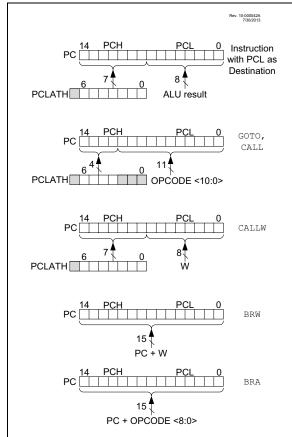

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 3.3.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 3.3.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.3.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1, the signed value of the operand of the BRA instruction.

#### 6.2.2.2 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 6-7).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 6.2.2.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- TMR1

- TMR0

- TMR2

- SMT1

- SMT2

- CLKREF

- CLC

#### 6.2.2.4 Oscillator Status and Manual Enable

The 'ready' status of each oscillator is displayed in the OSCSTAT register (Register 6-4). The oscillators can also be manually enabled through the OSCEN register (Register 6-7). Manual enabling makes it possible to verify the operation of the EXTOSC or SOSC crystal oscillators. This can be achieved by enabling the selected oscillator, then watching the corresponding 'ready' state of the oscillator in the OSCSTAT register.

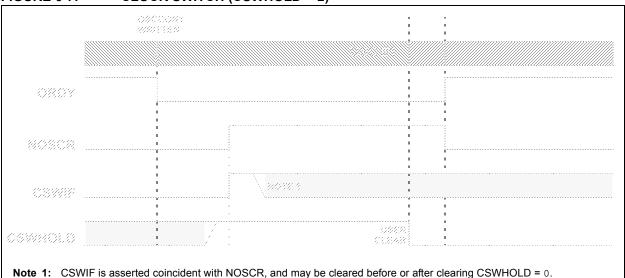

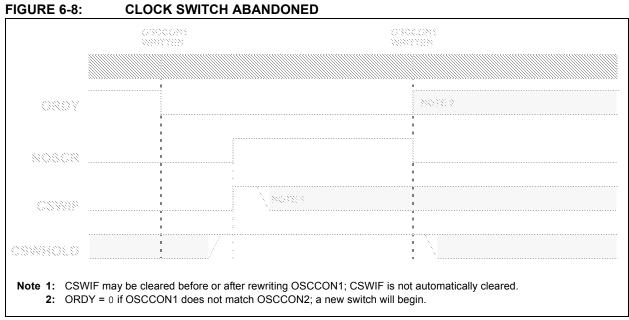

### 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register. The following clock sources can be selected using the following:

- External oscillator

- Internal Oscillator Block (INTOSC)

#### 6.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register select the system clock source that is used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, so the old source will be ready immediately. The device may enter Sleep while waiting for the switch as described in Section 6.3.3, Clock Switch and Sleep.

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR1 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CLKSIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the New Oscillator is ready bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- Set CSWHOLD = 0 so the switch can complete, or

- Copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

#### 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 8.0** "**Power-Saving Operation Modes**" for more details.

#### 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the PIE0 register. The INTEDG bit of the INTCON register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the PIR0 register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| U-0             | U-0        | U-0                                        | R/W/HS-0/0 | R/W/HS-0/0                            | R/W/HS-0       | )/0 R/W/HS-0/0                                    | R/W/HS-0/0         |  |  |

|-----------------|------------|--------------------------------------------|------------|---------------------------------------|----------------|---------------------------------------------------|--------------------|--|--|

| _               | _          | _                                          | CCP5IF     | CCP4IF                                | CCP3IF         | CCP2IF                                            | CCP1IF             |  |  |

| pit 7           |            |                                            |            |                                       |                |                                                   | bi                 |  |  |

| _egend:         |            |                                            |            |                                       |                |                                                   |                    |  |  |

| R = Readable    | e bit      | W = Writable bit                           | :          | U = Unimpleme                         | ented bit, rea | d as '0'                                          |                    |  |  |

| u = Bit is unc  | hanged     | x = Bit is unknow                          | wn         | -n/n = Value at                       | POR and BO     | DR/Value at all other                             | Resets             |  |  |

| '1' = Bit is se | t          | '0' = Bit is cleare                        | ed         | HS = Hardware                         | e set          |                                                   |                    |  |  |

| bit 7-5         | Unimpleme  | nted: Read as '0'                          |            |                                       |                |                                                   |                    |  |  |

| bit 4           | CCP5IF: CC | P5 Interrupt Flag bit                      | t          |                                       |                |                                                   |                    |  |  |

|                 | Value      |                                            |            | ССРМ                                  | Mode           |                                                   |                    |  |  |

|                 | value      | Captu                                      | re         | Comp                                  | are            | PWN                                               | 1                  |  |  |

|                 | 1          | Capture occurred<br>(must be cleared in se | oftware)   | Compare match o<br>(must be cleared i |                | Output trailing edge of (must be cleared in so    |                    |  |  |

|                 | 0          | Capture did not occur                      | r          | Compare match d                       | id not occur   | Output trailing edge d                            | d not occur        |  |  |

| bit 3           | CCP4IF: CC | P4 Interrupt Flag bit                      | t          |                                       |                |                                                   |                    |  |  |

|                 |            | CCPM Mode                                  |            |                                       |                |                                                   |                    |  |  |

|                 | Value      | Captu                                      | re         | Comp                                  | are            | PWN                                               | 1                  |  |  |

|                 | 1          | Capture occurred<br>(must be cleared in se | oftware)   | Compare match o<br>(must be cleared i |                | Output trailing edge of (must be cleared in so    |                    |  |  |

|                 | 0          | Capture did not occur                      | r          | Compare match d                       | id not occur   | Output trailing edge d                            | d not occur        |  |  |

| bit 2           | CCP3IF: CC | P3 Interrupt Flag bit                      | t          |                                       |                |                                                   |                    |  |  |

|                 | Value      |                                            |            | ССРМ                                  | Mode           |                                                   |                    |  |  |

|                 | Value      | Captu                                      | re         | Comp                                  | are            | PWM                                               | 1                  |  |  |

|                 | 1          | Capture occurred<br>(must be cleared in se | oftware)   | Compare match o<br>(must be cleared i |                | Output trailing edge or<br>(must be cleared in so |                    |  |  |

|                 | 0          | Capture did not occur                      | ſ          | Compare match d                       | id not occur   | Output trailing edge d                            | d not occur        |  |  |

| oit 1           | CCP2IF: CC | P2 Interrupt Flag bit                      | t          |                                       |                |                                                   |                    |  |  |

|                 | No. hou    | CCPM Mode                                  |            |                                       |                |                                                   |                    |  |  |

|                 | Value      | Captu                                      | re         | Comp                                  | are            | PWM                                               | 1                  |  |  |

|                 | 1          | Capture occurred<br>(must be cleared in se | oftware)   | Compare match o<br>(must be cleared i |                | Output trailing edge or<br>(must be cleared in so |                    |  |  |

|                 | 0          | Capture did not occur                      | r          | Compare match d                       | id not occur   | Output trailing edge d                            | d not occur        |  |  |

| bit 0           | CCP1IF: CC | P1 Interrupt Flag bit                      | t          |                                       |                |                                                   |                    |  |  |

|                 |            |                                            |            | ССРМ                                  | Mode           |                                                   |                    |  |  |

|                 | Value      | Captu                                      | re         | Comp                                  | are            | PWM                                               | 1                  |  |  |

|                 | 1          | Capture occurred<br>(must be cleared in se | oftware)   | Compare match o<br>(must be cleared i |                | Output trailing edge or<br>(must be cleared in so | ccurred<br>ftware) |  |  |

|                 | 0          | Capture did not occur                      | -          | Compare match d                       | id not occur   | Output trailing edge d                            | d not occur        |  |  |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1 **REGISTER 9-2:**

| U-0                                     | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | U-0                            | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |  |

|-----------------------------------------|----------------------------------------|-------------------------------------------------------------------------------|--------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--|

| -                                       |                                        | WDTCS<2:0>                                                                    | -                              |                                        | WINDOW<2:0>                            |                                        |  |

| bit 7                                   | bit 7 bit 0                            |                                                                               |                                |                                        |                                        |                                        |  |

|                                         |                                        |                                                                               |                                |                                        |                                        |                                        |  |

| Legend:                                 |                                        |                                                                               |                                |                                        |                                        |                                        |  |

| R = Readable bit W = Writable bit       |                                        | U = Unimple                                                                   | emented bit, read              | as '0'                                 |                                        |                                        |  |

| u = Bit is unchanged x = Bit is unknown |                                        | -n/n = Value at POR and BOR/Value at all other Resets                         |                                |                                        |                                        |                                        |  |

| '1' = Bit is set '0' = Bit is cleared   |                                        |                                                                               | q = Value depends on condition |                                        |                                        |                                        |  |

| bit 7 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       |                            |

bit 6-4 WDTCS<2:0>: Watchdog Timer Clock Select bits

111 = Reserved

- 010 = Reserved

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

- bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 62.5                            | 37.5                              |

| 001         | 75                              | 25                                |

| 000         | 87.5                            | 12.5                              |

Note 1: If WDTCCS <2:0> in CONFIG3 = 111, the Reset value of WDTCS<2:0> is 000.

2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3 register.

3: If WDTCCS<2:0> in CONFIG3  $\neq$  111, these bits are read-only.

4: If WDTCWS<2:0> in CONFIG3  $\neq$  111, these bits are read-only.

© 2016 Microchip Technology Inc.

### 10.0 NONVOLATILE MEMORY (NVM) CONTROL

NVM is separated into two types: Program Flash Memory (PFM) and Data EEPROM Memory.

NVM is accessible by using both the FSR and INDF registers, or through the NVMREG register interface.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways; by either code protection or write protection.

Code protection ( $\overline{CP}$  and  $\overline{CPD}$  bits in Configuration Word 5) disables access, reading and writing, to both the PFM and EEPROM via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be Reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits, and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT<1:0> bits of Configuration Word 4. Write protection does not affect a device programmer's ability to read, write, or erase the device.

#### 10.1 Program Flash Memory (PFM)

PFM consists of an array of 14-bit words as user memory, with additional words for User ID information, Configuration words, and interrupt vectors. PFM provides storage locations for:

- User program instructions

- User defined data

PFM data can be read and/or written to through:

- CPU instruction fetch (read-only)

- FSR/INDF indirect access (read-only) (Section 10.3 "FSR and INDF Access")

- NVMREG access (Section 10.4 "NVMREG Access"

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Read operations return a single word of memory. When write and erase operations are done on a row basis, the row size is defined in Table 10-1. PFM will erase to a logic '1' and program to a logic '0'.

TABLE 10-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device         | Row Erase<br>(words) | Write<br>Latches<br>(words) | Total<br>Program<br>Flash<br>(words) |

|----------------|----------------------|-----------------------------|--------------------------------------|

| PIC16(L)F18854 | 32                   | 32                          | 4096                                 |

It is important to understand the PFM memory structure for erase and programming operations. PFM is arranged in rows. A row consists of 32 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, all or a portion of this row can be programmed. Data to be written into the program memory row is written to 14-bit wide data write latches. These latches are not directly accessible, but may be loaded via sequential writes to the NVMDATH:NVMDATL register pair.

| Note: | To modify only a portion of a previously<br>programmed row, then the contents of the<br>entire row must be read and saved in<br>RAM prior to the erase. Then, the new<br>data and retained data can be written into<br>the write latches to reprogram the row of |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PFM. However, any unprogrammed<br>locations can be written without first<br>erasing the row. In this case, it is not<br>necessary to save and rewrite the other<br>previously programmed locations                                                               |

#### 10.1.1 PROGRAM MEMORY VOLTAGES

The PFM is readable and writable during normal operation over the full VDD range.

#### 10.1.1.1 Programming Externally

The program memory cell and control logic support write and Bulk Erase operations down to the minimum device operating voltage. Special BOR operation is enabled during Bulk Erase (Section 5.2.4 "BOR is always OFF").

#### 10.1.1.2 Self-programming

The program memory cell and control logic will support write and row erase operations across the entire VDD range. Bulk Erase is not supported when selfprogramming.

#### 12.4 PORTA Registers

#### 12.4.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 12.4.9 shows how to initialize PORTA.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The PORT data latch LATA (Register 12-4) holds the output port data, and contains the latest value of a LATA or PORTA write.

#### EXAMPLE 12-1: INITIALIZING PORTA

| ; | This | code | example | illustrates |  |

|---|------|------|---------|-------------|--|

|---|------|------|---------|-------------|--|

| ; | initializing | the | PORTA | register. | The |

|---|--------------|-----|-------|-----------|-----|

|   |              |     |       |           |     |

| ; other  | ports are i | nitialized in the same |

|----------|-------------|------------------------|

| ; manner | · .         |                        |

|          |             |                        |

| BANKSEL  | PORTA       | ;                      |

| CLRF     | PORTA       | ;Init PORTA            |

| BANKSEL  | LATA        | ;Data Latch            |

| CLRF     | LATA        | ;                      |

| BANKSEL  | ANSELA      | ;                      |

| CLRF     | ANSELA      | ;digital I/O           |

| BANKSEL  | TRISA       | ;                      |

| MOVLW    | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF    | TRISA       | ;and set RA<2:0> as    |

|          |             | ;outputs               |

#### 12.4.2 DIRECTION CONTROL

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 12.4.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 12-7) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

#### 12.4.4 SLEW RATE CONTROL

The SLRCONA register (Register 12-8) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

| Desired Input Pin | Value to Write to Register <sup>(1)</sup> |

|-------------------|-------------------------------------------|

| RA0               | 0x00                                      |

| RA1               | 0x01                                      |

| RA2               | 0x02                                      |

| RA3               | 0x03                                      |

| RA4               | 0x04                                      |

| RA5               | 0x05                                      |

| RA6               | 0x06                                      |

| RA7               | 0x07                                      |

| RB0               | 0x08                                      |

| RB1               | 0x09                                      |

| RB2               | 0x0A                                      |

| RB3               | 0x0B                                      |

| RB4               | 0x0C                                      |

| RB5               | 0x0D                                      |

| RB6               | 0x0E                                      |

| RB7               | 0x0F                                      |

| RC0               | 0x10                                      |

| RC1               | 0x11                                      |

| RC2               | 0x12                                      |

| RC3               | 0x13                                      |

| RC4               | 0x14                                      |

| RC5               | 0x15                                      |

| RC6               | 0x16                                      |

| RC7               | 0x17                                      |

| RE3               | 0x23                                      |

#### TABLE 13-2: PPS INPUT REGISTER VALUES

Note 1: Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA<7:0> and RB<7:0>) are valid values to write to the INTPPS register.

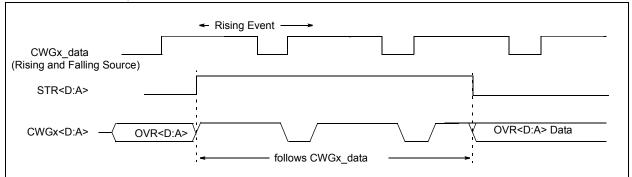

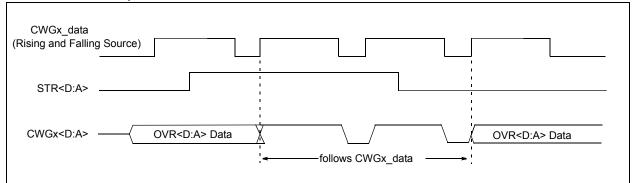

#### 20.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWGxx pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWGxOCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWGxOCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWGxCON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 20.10 "Auto-Shutdown"**. An auto-shutdown event will only affect pins that have STRx = 1.

#### 20.9.1 STEERING SYNCHRONIZATION

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

Figure 20-10 and Figure 20-11 illustrate the timing of asynchronous and synchronous steering, respectively.

FIGURE 20-10: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (MODE<2:0> = 000)

FIGURE 20-11: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (MODE<2:0> = 001)

#### 22.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 22.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 22-2. Data inputs in the figure are identified by a generic numbered input name.

Table 22-2 correlates the generic input name to the actual signal for each CLC module. The column labeled 'LCxDyS<4:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation for the MUX select input codes: LCxD1S<4:0> through LCxD4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 22-3 through Register 22-6).

#### TABLE 22-2: CLCx DATA INPUT SELECTION

| LCxDyS<4:0><br>Value     | CLCx Input Source     |

|--------------------------|-----------------------|

| 110000 to 111111 [48+]   | Reserved              |

| 101111 [47]              | CWG3B output          |

| 101110 [46]              | CWG3A output          |

| 101101 [45]              | CWG2B output          |

| 101100 [44]              | CWG2A output          |

| 101011 [43]              | CWG1B output          |

| 101010 <b>[42]</b>       | CWG1A output          |

| 101001 [41]              | MSSP2 SCK output      |

| 101000 [40]              | MSSP2 SDO output      |

| 100111 <b>[39]</b>       | MSSP1 SCK output      |

| 100110 <b>[38]</b>       | MSSP1 SDO output      |

| 100101 [37]              | EUSART (TX/CK) output |

| 100100 <b>[36]</b>       | EUSART (DT) output    |

| 100011 [35]              | CLC4 output           |

| 100010 [34]              | CLC3 output           |

| 100001 [33]              | CLC2 output           |

| 100000 [32]              | CLC1 output           |

| 011111 [31]              | DSM output            |

| 011110 [30]              | IOCIF                 |

| 011101 [29]              | ZCD output            |

| 011100 [28]              | Comparator 2 output   |

| 011011 [27]              | Comparator 1 output   |

| 011010 [26]              | NCO1 output           |

| 011001 [25]              | PWM7 output           |

| 011000 [24]              | PWM6 output           |

| 010111 [23]              | CCP5 output           |

| 010110 [22]              | CCP4 output           |

| 010101 [21]              | CCP3 output           |

| 010100 [20]              | CCP2 output           |

| 010011 [19]              | CCP1 output           |

| 010010 [18]              | SMT2 output           |

| 010001 [17]              | SMT1 output           |

| 010000 [16]              | TMR6 to PR6 match     |

| 001111 [15]              | TMR5 overflow         |

| 001110 [14]              | TMR4 to PR4 match     |

| 001101 [13]              | TMR3 overflow         |

| 001100 [12]              | TMR2 to PR2 match     |

| 001011 [11]              | TMR1 overflow         |

| 001010 [10]              | TMR0 overflow         |

| 001001 [9]               | CLKR output           |

| 001000 [8]               | FRC                   |

| 000111 [7]               | SOSC                  |

| 000110 [6]               | LFINTOSC              |

| 000101 [5]               | HFINTOSC              |

| 000100 [4]               | Fosc                  |

| 000011 [3]               | CLCIN3PPS             |

|                          | CLCIN2PPS             |

|                          |                       |

| 000010 [2]<br>000001 [1] | CLCIN1PPS             |

| <b>TABLE 22-4:</b> | SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued) |

|--------------------|-------------------------------------------------------|

|--------------------|-------------------------------------------------------|

| Name      | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3          | Bit 2        | Bit 1    | Bit 0    | Register<br>on Page |

|-----------|----------|----------|----------|----------|----------------|--------------|----------|----------|---------------------|

| CLC4GLS1  | LC4G2D4T | LC4G2D4N | LC4G2D3T | LC4G2D3N | LC4G2D2T       | LC4G2D2N     | LC4G2D1T | LC4G2D1N | 296                 |

| CLC4GLS2  | LC4G3D4T | LC4G3D4N | LC4G3D3T | LC4G3D3N | LC4G3D2T       | LC4G3D2N     | LC4G3D1T | LC4G3D1N | 297                 |

| CLC4GLS3  | LC4G4D4T | LC4G4D4N | LC4G4D3T | LC4G4D3N | LC4G4D2T       | LC4G4D2N     | LC4G4D1T | LC4G4D1N | 298                 |

| CLCDATA   | —        | _        | _        | -        | MLC4OUT        | MLC3OUT      | MLC2OUT  | MLC1OUT  | 299                 |

| CLCIN0PPS | _        | _        | _        |          | CLCIN0PPS<4:0> |              |          |          |                     |

| CLCIN1PPS | —        | _        | _        |          | (              | CLCIN1PPS<4: | 0>       |          | 214                 |

| CLCIN2PPS | _        | _        | _        |          | (              | CLCIN2PPS<4: | 0>       |          | 214                 |

| CLCIN3PPS | _        | _        | _        |          | (              | CLCIN3PPS<4: | 0>       |          | 214                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

#### 23.2 ADC Operation

#### 23.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. A conversion may be started by any of the following:

- Software setting the ADGO bit of ADCON0 to '1'

- An external trigger (selected by Register 23-3)

- A continuous-mode retrigger (see section Section 23.5.8 "Continuous Sampling Mode")

Note: The ADGO bit should not be set in the same instruction that turns on the ADC. Refer to Section 23.2.7 "ADC Conversion Procedure (Basic Mode)".

#### 23.2.2 COMPLETION OF A CONVERSION

When any individual conversion is complete, the value already in ADRES is written into ADPREV (if ADPSIS=1) and the new conversion results appear in ADRES. When the conversion completes, the ADC module will:

- Clear the ADGO bit (Unless the ADCONT bit of ADCON0 is set)

- · Set the ADIF Interrupt Flag bit

- Set the ADMATH bit

- Update ADACC

When ADDSEN=0 then after every conversion, or when ADDSEN=1 then after every other conversion, the following events occur:

- ADERR is calculated

- ADTIF is set if ADERR calculation meets threshold requirements

In addition, on the completion of every conversion if ADDSEN=0, or every other conversion if ADDSEN=1:

- · ADSTPE is calculated

- Depending on ADSTPE, the threshold comparison may set ADTIF

Importantly, filter and threshold computations occur after the conversion itself is complete. As such, interrupt handlers responding to ADIF should check ADTIF before reading filter and threshold results.

#### 23.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the ADGO bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted. In this case, filter and/or threshold occur.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

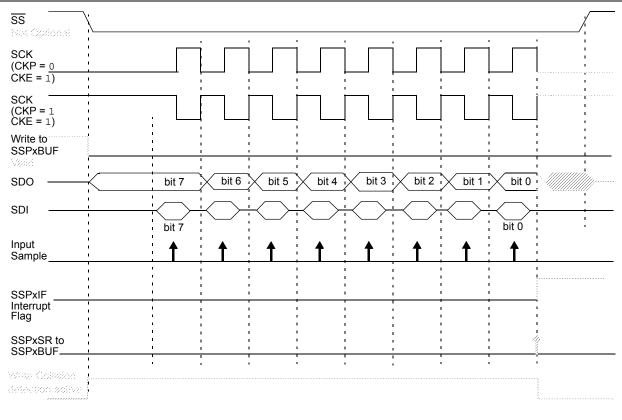

| FIGURE 31-9: | SDI MODE WAVEFORM | (SLAVE MODE WITH CKE = 0)  |

|--------------|-------------------|----------------------------|

| FIGURE 31-9. | SPI WODE WAVEFORW | (SLAVE WIDDE WITH CRE - U) |

|                                                |                                       |        |              |          |                       |                  |                       |            |                                         | ,  | . j                                       |

|------------------------------------------------|---------------------------------------|--------|--------------|----------|-----------------------|------------------|-----------------------|------------|-----------------------------------------|----|-------------------------------------------|

|                                                |                                       |        |              |          |                       |                  |                       |            |                                         |    | :<br>:<br>:<br>:<br>:                     |

| - (KE = 0)<br>- SOX<br>- CXF = 1<br>- CXF = 0) | ·<br>·<br>·                           |        |              |          |                       |                  |                       |            |                                         |    | :<br>:<br>:<br>:                          |

| VVRE 0<br>SSP2817                              | · · · · · · · · · · · · · · · · · · · |        |              | 2        | 9<br>1<br>1<br>1<br>1 | ;<br>;<br>;<br>; |                       | 5          | \$<br><<br><<br>\$<br>\$                |    | ,<br>,<br>,<br>,                          |

| N384<br>8920                                   |                                       | K 23.7 | <u> 88 8</u> | X 88 8   | X 337.4               | K 888.8          | X 398, Z              | X 323      |                                         |    | ········<br>· · · · · · · · · · · · · · · |

| 903                                            | · · · · · · · · · · · · · · · · · · · |        |              |          |                       |                  |                       |            |                                         |    | ,<br>;<br>;<br>,                          |

| ingsti<br>Sørrigiø                             | · · · · · · · · · · · · · · · · · · · | 14p.   |              |          |                       | . //s.           |                       | :<br>      | s<br>,<br>,                             | ų. |                                           |

| SSPodi<br>Internupt<br>Flag                    | :<br>:<br>:                           |        | :            | 4 4<br>5 | :<br>:<br>:           | ;<br>,<br>,<br>, | :                     |            | > .<br>< .<br>&                         |    |                                           |

| 939258 6<br>8997-8997                          | ·                                     | •      |              | 5        | :<br>:                |                  | 2<br>2<br>2<br>2<br>2 | ><br>><br> | \$;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |    |                                           |

| Verite Codisson<br>detection active            |                                       |        |              |          |                       |                  |                       |            |                                         |    |                                           |

#### REGISTER 31-7: SSPxBUF: MSSPx BUFFER REGISTER

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x         | R/W-x           | R/W-x  | R/W-x |

|------------------|-------|------------------|-------|---------------|-----------------|--------|-------|

|                  |       |                  | SSPxB | UF<7:0>       |                 |        |       |

| bit 7            |       |                  |       |               |                 |        | bit 0 |

|                  |       |                  |       |               |                 |        |       |

| Legend:          |       |                  |       |               |                 |        |       |

| D - Doodoblo bit |       | M = Mritable bit |       | II – Unimplor | nonted hit read | oo 'O' |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SSPxBUF<7:0>: MSSP Buffer bits

#### TABLE 31-3: SUMMARY OF REGISTERS ASSOCIATED WITH MSSPx

| Name       | Bit 7  | Bit 6   | Bit 5 | Bit 4 | Bit 3  | Bit 2       | Bit 1 | Bit 0  | Register<br>on Page |

|------------|--------|---------|-------|-------|--------|-------------|-------|--------|---------------------|

| INTCON     | GIE    | PEIE    | —     | —     | —      | —           | —     | INTEDG | 114                 |

| PIR1       | OSFIF  | CSWIF   | —     | —     | —      | —           | ADTIF | ADIF   | 125                 |

| PIE1       | OSFIE  | CSWIE   | —     | —     | —      | —           | ADTIE | ADIE   | 116                 |

| SSP1STAT   | SMP    | CKE     | D/A   | Р     | S      | R/W         | UA    | BF     | 469                 |

| SSP1CON1   | WCOL   | SSPOV   | SSPEN | CKP   |        | SSPM        | <3:0> |        | 470                 |

| SSP1CON2   | GCEN   | ACKSTAT | ACKDT | ACKEN | RCEN   | PEN         | RSEN  | SEN    | 471                 |

| SSP1CON3   | ACKTIM | PCIE    | SCIE  | BOEN  | SDAHT  | SBCDE       | AHEN  | DHEN   | 469                 |

| SSP1MSK    |        |         |       | SSPMS | K<7:0> |             |       |        | 473                 |

| SSP1ADD    |        |         |       | SSPAD | D<7:0> |             |       |        | 473                 |

| SSP1BUF    |        |         |       | SSPBU | F<7:0> |             |       |        | 474                 |

| SSP2STAT   | SMP    | CKE     | D/A   | Р     | S      | R/W         | UA    | BF     | 469                 |

| SSP2CON1   | WCOL   | SSPOV   | SSPEN | CKP   |        | SSPM        | <3:0> |        | 470                 |

| SSP2CON2   | GCEN   | ACKSTAT | ACKDT | ACKEN | RCEN   | PEN         | RSEN  | SEN    | 471                 |

| SSP2CON3   | ACKTIM | PCIE    | SCIE  | BOEN  | SDAHT  | SBCDE       | AHEN  | DHEN   | 469                 |

| SSP2MSK    |        |         |       | SSPMS | K<7:0> |             |       |        | 473                 |

| SSP2ADD    |        |         |       | SSPAD | D<7:0> |             |       |        | 473                 |

| SSP2BUF    |        |         |       | SSPBU | F<7:0> |             |       |        | 474                 |

| SSP1CLKPPS | _      | —       | —     |       | SSF    | 1CLKPPS<4   | :0>   |        | 214                 |

| SSP1DATPPS | _      | _       | —     |       | SSF    | 1DATPPS<4   | :0>   |        | 214                 |

| SSP1SSPPS  | _      | _       | _     |       | SS     | P1SSPPS<4:  | 0>    |        | 214                 |

| SSP2CLKPPS |        | —       |       |       | SSF    | 2CLKPPS<4   | :0>   |        | 214                 |

| SSP2DATPPS |        | —       | —     |       | SSF    | 2DATPPS<4   | :0>   |        | 214                 |

| SSP2SSPPS  | _      | —       | —     |       | SS     | P2SSPPS<4:  | 0>    |        | 214                 |

| RxyPPS     | —      | —       | —     |       | F      | RxyPPS<4:0> |       |        | 215                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx module

**Note 1:** When using designated  $I^2C$  pins, the associated pin values in INLVLx will be ignored.

#### 32.6.10 GATED COUNTER MODE

This mode counts pulses on the SMTx\_signal input, gated by the SMTxWIN input. It begins incrementing the timer upon seeing a rising edge of the SMTxWIN input and updates the SMTxCPW register upon a falling edge on the SMTxWIN input. See Figure 32-19 and Figure 32-20.

#### FIGURE 33-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

|           | - Biê seê by s                           |                                                  | furury                                 | 2<br>                                   | 1                                            | :<br>*                                       | :                     |                           |                                        |            | ssé                                     |

|-----------|------------------------------------------|--------------------------------------------------|----------------------------------------|-----------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------|---------------------------|----------------------------------------|------------|-----------------------------------------|

| 80.390.68 | •<br>•                                   | • ~ ~<br>• · · · · · · · · · · · · · · · · · · · |                                        | 2                                       | <br>                                         |                                              |                       |                           | . ž.                                   | ·····      |                                         |

| 0033368   | 9<br>1                                   | филикалиски стали<br>:                           | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                         |                                              |                                              | :<br>                 |                           | Michaelana                             |            |                                         |

| 26039     |                                          |                                                  |                                        | ,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                              |                                              |                       |                           | ······································ | enere Para |                                         |

|           | :<br>/////////////////////////////////// | :<br>///////////////////////////////////         | :<br>:<br>:                            | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | :<br>:<br>:::::::::::::::::::::::::::::::::: | :<br>:<br>:::::::::::::::::::::::::::::::::: | - Sectopic<br>minimum | soe to geer Re<br>minimum | ed dişili.<br>Mamana                   |            | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

#### FIGURE 33-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

$\Omega^{*}_{\rm c}$  . The SUSPART remains is its while the NGE bit is set.

#### 33.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TX1STA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TX1STA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 33-9 for the timing of the Break character sequence.

#### 33.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |  |

| Operation:       | See description below                                                                                                                                                                                              |  |

| Status Affected: | С                                                                                                                                                                                                                  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |

| SUBLW            | Subtract W from literal                                                                                                  |                 |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Syntax:          | [label] S                                                                                                                | UBLW k          |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |                 |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                |                 |  |

| Status Affected: | C, DC, Z                                                                                                                 |                 |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |                 |  |

|                  | <b>C</b> = 0                                                                                                             | W > k           |  |

|                  | <b>C</b> = 1                                                                                                             | $W \le k$       |  |

|                  | DC = 0                                                                                                                   | W<3:0> > k<3:0> |  |

DC = 1

$W<3:0> \le k<3:0>$

| SLEEP            | Enter Sleep mode                                                                                                                                                                                               |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                  |  |

| Operands:        | None                                                                                                                                                                                                           |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                          |  |

| Status Affected: | TO, PD                                                                                                                                                                                                         |  |

| Description:     | The power-down Status bit, $\overline{PD}$ is cleared. Time-out Status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.<br>See <b>Section 8.2 "Sleep Mode"</b> for more information. |  |

| SUBWF            | Subtract W                                                                                                                                                                                 | from f              |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| Syntax:          | [label] SU                                                                                                                                                                                 | IBWF f,d            |  |

|                  | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                         |                     |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                      |                     |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |                     |  |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |                     |  |

|                  | <b>C =</b> 0                                                                                                                                                                               | W > f               |  |

|                  | <b>C =</b> 1                                                                                                                                                                               | $W \leq f$          |  |

|                  | DC = 0                                                                                                                                                                                     | W<3:0> > f<3:0>     |  |

|                  | DC = 1                                                                                                                                                                                     | $W<3:0> \le f<3:0>$ |  |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                     |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                     |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |  |