Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18854-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.6 **RESET Instruction**

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 5-4 for default conditions after a RESET instruction has occurred.

#### 5.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.4.2** "**Overflow/Underflow Reset**" for more information.

#### 5.8 **Programming Mode Exit**

Upon exit of In-Circuit Serial Programming (ICSP) mode, the device will behave as if a POR had just occurred (the device does not reset upon run time self-programming/erase operations).

#### 5.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the PWRTE bit of the Configuration Words.

The Power-up Timer provides a nominal 64 ms time out on POR or Brown-out Reset. The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in the Configuration Words. The Power-up Timer starts after the release of the POR and BOR. For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*" (DS00607).

#### 5.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer Configuration. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 5-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

#### 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase Lock Loop (PLL) that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce a range from 1 to 32 MHz. The Low-Frequency Internal Oscillator (LFINTOSC) generates a 31 kHz frequency. The external oscillator block can also be used with the PLL. See **Section 6.2.1.4 "4x PLL"** for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset

- Write the NOSC<2:0> and NDIV<4:0> bits in the OSCCON1 register to switch the system clock source

See **Section 6.3 "Clock Switching**" for more information.

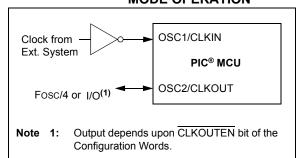

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.1-4 MHz

- ECL Low power, 0-0.1 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| REGISTER 7                                                                                                                                                        | -/: PIE5:                                           | PERIPHERA                                             |                | I ENABLE    | REGISTER 5       |                  |             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|----------------|-------------|------------------|------------------|-------------|

| R/W-0/0                                                                                                                                                           | R/W-0/0                                             | R/W-0/0                                               | R/W-0/0        | U-0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |

| CLC4IE                                                                                                                                                            | CLC3IE                                              | CLC2IE                                                | CLC1IE         |             | TMR5GIE          | TMR3GIE          | TMR1GIE     |

| bit 7                                                                                                                                                             |                                                     |                                                       |                |             |                  |                  | bit 0       |

|                                                                                                                                                                   |                                                     |                                                       |                |             |                  |                  |             |

| Legend:                                                                                                                                                           | L:1                                                 |                                                       | L 14           |             |                  | (0)              |             |

| R = Readable                                                                                                                                                      |                                                     | W = Writable                                          |                | •           | mented bit, read |                  |             |

| u = Bit is unch                                                                                                                                                   | angeo                                               | x = Bit is unkr                                       |                |             | at POR and BOI   | R/value at all o | iner Resets |

| '1' = Bit is set                                                                                                                                                  |                                                     | '0' = Bit is clea                                     | ared           | HS = Hardwa | are set          |                  |             |

| bit 7                                                                                                                                                             | 1 = CLC4 in                                         | 4 Interrupt Ena<br>terrupt enabled<br>terrupt disable | t              |             |                  |                  |             |

| bit 6                                                                                                                                                             | 1 = CLC3 in                                         | 3 Interrupt Ena<br>terrupt enabled<br>terrupt disable | t              |             |                  |                  |             |

| bit 5                                                                                                                                                             |                                                     |                                                       |                |             |                  |                  |             |

| bit 4 CLC1IE: CLC1 Interrupt Enable bit<br>1 = CLC1 interrupt enabled<br>0 = CLC1 interrupt disabled                                                              |                                                     |                                                       |                |             |                  |                  |             |

| bit 3                                                                                                                                                             | Unimplemen                                          | ted: Read as '                                        | 0'             |             |                  |                  |             |

| bit 2 <b>TMR5GIE:</b> Timer5 Gate Interrupt Enable bit<br>1 = Enables the Timer5 gate acquisition interrupt<br>0 = Disables the Timer5 gate acquisition interrupt |                                                     |                                                       |                |             |                  |                  |             |

| bit 1 <b>TMR3GIE:</b> Timer3 Gate Interrupt Enable bit<br>1 = Enables the Timer3 gate acquisition interrupt<br>0 = Disables the Timer3 gate acquisition interrupt |                                                     |                                                       |                |             |                  |                  |             |

| bit 0                                                                                                                                                             | 1 = Enables                                         | mer1 Gate Inte<br>the Timer1 ga<br>the Timer1 ga      | te acquisition | interrupt   |                  |                  |             |

| set                                                                                                                                                               | PEIE of the IN<br>to enable ar<br>htrolled by regis | ny peripheral                                         | interrupt      |             |                  |                  |             |

#### REGISTER 7-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

#### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT        |

|----------------------------------------------------------|------------|

| WDTE<1:0> = 00                                           |            |

| WDTE<1:0> = 01 and SEN = 0                               |            |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared    |

| CLRWDT Command                                           | Cleared    |

| Oscillator Fail Detected                                 |            |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |            |

| Change INTOSC divider (IRCF bits)                        | Unaffected |

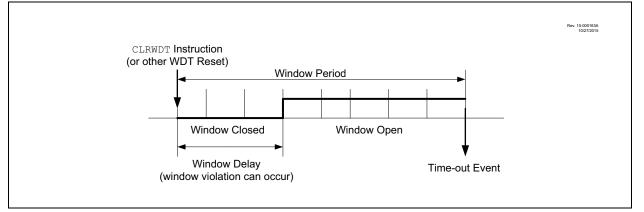

#### FIGURE 9-2: WINDOW PERIOD AND DELAY

#### REGISTER 9-3: WDTPSL: WDT PRESCALE SELECT LOW BYTE REGISTER (READ-ONLY)

| R-0/0                             | R-0/0 | R-0/0                | R-0/0                                                | R-0/0                 | R-0/0 | R-0/0  | R-0/0 |

|-----------------------------------|-------|----------------------|------------------------------------------------------|-----------------------|-------|--------|-------|

|                                   |       |                      | PSCN                                                 | ۲<7:0> <sup>(1)</sup> |       |        |       |

| bit 7                             |       |                      |                                                      |                       |       |        | bit 0 |

|                                   |       |                      |                                                      |                       |       |        |       |

| Legend:                           |       |                      |                                                      |                       |       |        |       |

| R = Readable bit W = Writable bit |       |                      | U = Unimpleme                                        | ented bit, read as    | ·'O'  |        |       |

| u = Bit is unchange               | d     | x = Bit is unknown   | vn -n/n = Value at POR and BOR/Value at all other Re |                       |       | Resets |       |

| '1' = Bit is set                  |       | '0' = Bit is cleared |                                                      |                       |       |        |       |

bit 7-0 **PSCNT<7:0>**: Prescale Select Low Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-4: WDTPSH: WDT PRESCALE SELECT HIGH BYTE REGISTER (READ-ONLY)

| bit 7 |       |       |        |                      |       |       | bit 0 |

|-------|-------|-------|--------|----------------------|-------|-------|-------|

|       |       |       | PSCNT< | 15:8> <sup>(1)</sup> |       |       |       |

| R-0/0 | R-0/0 | R-0/0 | R-0/0  | R-0/0                | R-0/0 | R-0/0 | R-0/0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSCNT<15:8>**: Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ-ONLY)

| U-0   | R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0  | R-0/0                 |

|-------|-------------|-------|-------|-------|-------|--------|-----------------------|

| _     | WDTTMR<3:0> |       |       |       | STATE | PSCNT< | 17:16> <sup>(1)</sup> |

| bit 7 |             |       |       |       |       |        | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '0'

bit 6-3 WDTTMR<3:0>: Watchdog Timer Value bits

bit 2 STATE: WDT Armed Status bit

- 1 = WDT is armed 0 = WDT is not armed

- bit 1-0 **PSCNT<17:16>**: Prescale Select Upper Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

; This write routine assumes the following:

#### EXAMPLE 10-4: WRITING TO PROGRAM FLASH MEMORY (PFM)

| ; 1.6         | 54 bytes of da | ata are loaded, startir | ng at the address in DATA_ADDR                     |

|---------------|----------------|-------------------------|----------------------------------------------------|

| ; 2. E        | Each word of d | data to be written is m | made up of two adjacent bytes in DATA_ADDR,        |

| ; 5           | stored in lit  | tle endian format       |                                                    |

| ; 3. A        | A valid start: | ing address (the least  | significant bits = 00000) is loaded in ADDRH:ADDRL |

| ; 4. <i>1</i> | ADDRH and ADDI | RL are located in commo | on RAM (locations 0x70 - 0x7F)                     |

| ; 5.1         | WM interrupt:  | s are not taken into ac | ccount                                             |

|               | BANKSEL        | NVMADRH                 |                                                    |

|               | MOVF           | ADDRH, W                |                                                    |

|               | MOVWF          | NVMADRH                 | ; Load initial address                             |

|               | MOVF           | ADDRL,W                 | , Ioda inicial dalebb                              |

|               | MOVWF          | NVMADRL                 |                                                    |

|               | MOVLW          | LOW DATA_ADDR           | ; Load initial data address                        |

|               | MOVWF          | FSR0L                   |                                                    |

|               | MOVLW          | HIGH DATA_ADDR          |                                                    |

|               | MOVWF          | FSROH                   |                                                    |

|               | BCF            | NVMCON1,NVMREGS         | ; Set Program Flash Memory as write location       |

|               | BSF            | NVMCON1,WREN            | ; Enable writes                                    |

|               | BSF            | NVMCON1, LWLO           | ; Load only write latches                          |

| TOOD          |                |                         |                                                    |

| LOOP          | MOVIW          | FSR0++                  |                                                    |

|               | MOVWF          | NVMDATL                 | ; Load first data byte                             |

|               | MOVWF<br>MOVIW | FSR0++                  | / Load TITSE data Dyte                             |

|               | MOVIW          | NVMDATH                 | ; Load second data byte                            |

|               | MOVF           | NVMADRL,W               |                                                    |

|               | XORLW          | 0x1F                    | ; Check if lower bits of address are 00000         |

|               | ANDLW          | 0x1F                    | ; and if on last of 32 addresses                   |

|               | BTFSC          | STATUS, Z               | ; Last of 32 words?                                |

|               | GOTO           | START_WRITE             | ; If so, go write latches into memory              |

|               | CALL           | UNLOCK_SEQ              | ; If not, go load latch                            |

|               | INCF           | NVMADRL, F              | ; Increment address                                |

|               | GOTO           | LOOP                    |                                                    |

| CTTA DTT      | MD T TTT       |                         |                                                    |

| SIARI         | _WRITE<br>BCF  | NVMCON1,LWLO            | ; Latch writes complete, now write memory          |

|               | CALL           | UNLOCK_SEQ              | ; Perform required unlock sequence                 |

|               | BCF            | NVMCON1, WREN           | ; Disable writes                                   |

|               |                |                         |                                                    |

| UNLOCI        | - ~            | 5.51                    |                                                    |

|               | MOVLW          | 55h                     |                                                    |

|               | BCF            | INTCON, GIE             | ; Disable interrupts                               |

|               | MOVWF          | NVMCON2                 | ; Begin unlock sequence                            |

|               | MOVLW<br>MOVWF | AAh<br>NVMCON2          |                                                    |

|               | BSF            | NVMCON2<br>NVMCON1,WR   |                                                    |

|               | BSF            | INTCON, GIE             | ; Unlock sequence complete, re-enable interrupts   |

|               | return         | THICON, GIE             | , ontook sequence compiece, re-enable interrupts   |

|               | recurii        |                         |                                                    |

| U-0                                   | R/W-0/0                                                                                                                                                      | R/W-0/0                                                                                                      | R/W/HC-0/0                                                                             | R/W/HC-x/q                                                                       | R/W-0/0                              | R/S/HC-0/0                                 | R/S/HC-0/0         |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|--------------------|

|                                       | NVMREGS                                                                                                                                                      | LWLO                                                                                                         | FREE                                                                                   | WRERR <sup>(1,2,3)</sup>                                                         | WREN                                 | WR <sup>(4,5,6)</sup>                      | RD <sup>(7)</sup>  |

| bit 7                                 |                                                                                                                                                              |                                                                                                              |                                                                                        |                                                                                  |                                      |                                            | bit                |

| Legend:                               |                                                                                                                                                              |                                                                                                              |                                                                                        |                                                                                  |                                      |                                            |                    |

| R = Readal                            | ble bit                                                                                                                                                      | W = Writable b                                                                                               | oit                                                                                    | U = Unimpleme                                                                    | nted bit read a                      | s '0'                                      |                    |

|                                       | only be set                                                                                                                                                  | x = Bit is unkn                                                                                              |                                                                                        |                                                                                  |                                      | Value at all other F                       | Resets             |

| '1' = Bit is s                        | 5                                                                                                                                                            | '0' = Bit is clea                                                                                            |                                                                                        | HC = Bit is clear                                                                |                                      |                                            |                    |

|                                       |                                                                                                                                                              |                                                                                                              |                                                                                        |                                                                                  | · ·                                  |                                            |                    |

| bit 7                                 | Unimplemente                                                                                                                                                 | ed: Read as '0'                                                                                              |                                                                                        |                                                                                  |                                      |                                            |                    |

| bit 6                                 |                                                                                                                                                              | -                                                                                                            |                                                                                        | and Device ID Re                                                                 | gisters                              |                                            |                    |

| bit 5                                 | <u>When FREE =</u><br>1 = The next                                                                                                                           | WR command u<br>WR command w                                                                                 | pdates the write                                                                       |                                                                                  | l within the row                     | ; no memory opera                          | ation is initiated |

| bit 4                                 | <u>When NVMRE</u><br>1 = Performs<br>address is                                                                                                              | rase Enable bit<br><u>GS:NVMADR po</u><br>an erase operat<br>s erased (to all 1<br>perations have o          | ion with the nex<br>s) to prepare for                                                  | t WR command; t<br>writing.                                                      | he 32-word pse                       | eudo-row containi                          | ng the indicate    |

| bit 3                                 | WRERR: Program/Erase Error<br>This bit is normally set by hard<br>1 = A write operation was inte<br>NVMADR points to a write<br>0 = The program or erase ope |                                                                                                              | ware.<br>errupted by a Re<br>e-protected addr                                          | ess.                                                                             | nlock sequence                       | e, or WR was writi                         | ten to one whil    |

| bit 2                                 | <ul> <li>WREN: Program/Erase Enable bit</li> <li>1 = Allows program/erase cycles</li> <li>0 = Inhibits programming/erasing of progr</li> </ul>               |                                                                                                              |                                                                                        | Flash                                                                            |                                      |                                            |                    |

| bit 1                                 | 1 = Initiates a<br>0 = NVM prog<br><u>When NVMRE</u><br>1 = Initiates th                                                                                     | G:NVMADR poin<br>n erase/program<br>gram/erase oper<br>G:NVMADR poin<br>ne operation indi<br>gram/erase oper | n cycle at the con<br>ation is complete<br><u>nts to a PFM loc</u><br>cated by Table 1 | rresponding EEPF<br>e and inactive<br><u>ation</u> :<br>10-4                     | ROM location                         |                                            |                    |

| bit 0                                 | <b>RD:</b> Read Con<br>1 = Initiates a<br>bit is clea                                                                                                        | trol bit <sup>(7)</sup><br>read at address                                                                   | eration is compl                                                                       | ete. The bit can or                                                              |                                      | akes one instructio<br>cleared) in softwar |                    |

| Note 1:<br>2:<br>3:<br>4:<br>5:<br>6: | Bit is undefined while<br>Bit must be cleared I<br>Bit may be written to<br>This bit can only be<br>Operations are self-t<br>Once a write operati            | by software; hard<br>'1' by software<br>set by following<br>timed, and the W                                 | dware will not cle<br>in order to imple<br>the unlock seque<br>/R bit is cleared       | ear this bit.<br>ment test sequen<br>ence of <b>Section 1</b><br>by hardware whe | ces.<br>0.4.2 "NVM Ur<br>n complete. |                                            |                    |

Reading from EEPROM loads only NVMDATL<7:0> (Register 10-1).

| U-0                                     | U-0               | U-0                                                   | R/W-1/1                            | U-0                                                                                                           | U-0                                                                                                                                       | U-0                                                                                                                                                                     |  |

|-----------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                         | —                 |                                                       | INLVLE3                            |                                                                                                               | _                                                                                                                                         | —                                                                                                                                                                       |  |

|                                         |                   |                                                       |                                    |                                                                                                               |                                                                                                                                           | bit 0                                                                                                                                                                   |  |

|                                         |                   |                                                       |                                    |                                                                                                               |                                                                                                                                           |                                                                                                                                                                         |  |

|                                         |                   |                                                       |                                    |                                                                                                               |                                                                                                                                           |                                                                                                                                                                         |  |

| R = Readable bit W = Writable bit       |                   |                                                       | U = Unimplemented bit, read as '0' |                                                                                                               |                                                                                                                                           |                                                                                                                                                                         |  |

| u = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |                                                                                                               |                                                                                                                                           |                                                                                                                                                                         |  |

|                                         | '0' = Bit is clea | ared                                                  |                                    |                                                                                                               |                                                                                                                                           |                                                                                                                                                                         |  |

|                                         |                   | bit W = Writable<br>anged x = Bit is unkn             | bit W = Writable bit               | INLVLE3       bit     W = Writable bit     U = Unimpler       anged     x = Bit is unknown     -n/n = Value a | INLVLE3        bit     W = Writable bit     U = Unimplemented bit, read       anged     x = Bit is unknown     -n/n = Value at POR and BO | INLVLE3              bit     W = Writable bit     U = Unimplemented bit, read as '0'       anged     x = Bit is unknown     -n/n = Value at POR and BOR/Value at all of |  |

#### REGISTER 12-34: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | INLVLE3: PORTE Input Level Select bits<br>For RE3 pin.                                                                                          |

|         | <ul> <li>1 = ST input used for PORT reads and interrupt-on-change</li> <li>0 = TTL input used for PORT reads and interrupt-on-change</li> </ul> |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                      |

#### TABLE 12-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|-------|-------|-------|-------|---------|-------|-------|-------|---------------------|

| PORTE  | —     | _     |       |       | RE3     |       |       |       | 206                 |

| WPUE   | —     | _     | _     |       | WPUE3   | _     | -     | _     | 206                 |

| INLVLE | _     | _     |       |       | INLVLE3 |       |       |       | 207                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

#### TABLE 12-6: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         |         | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    | _       | 74                  |

| CONFIG2 | 7:0  | BORE    | N<1:0>  | LPBOREN  |          |          | _        | PWRTE   | MCLRE   | 74                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

| R/W-0/0         | R/W-0/0                                                                                                        | U-0                                        | R/W-0/0          | R/W-0/0                     | R/W-0/0         | R/W-0/0          | R/W-0/0        |

|-----------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|-----------------------------|-----------------|------------------|----------------|

| SYSCMD          | FVRMD                                                                                                          | _                                          | CRCMD            | SCANMD                      | NVMMD           | CLKRMD           | IOCMD          |

| 7               | •                                                                                                              |                                            |                  |                             |                 |                  | (              |

|                 |                                                                                                                |                                            |                  |                             |                 |                  |                |

| Legend:         |                                                                                                                |                                            |                  |                             |                 |                  |                |

| R = Readable    | e bit                                                                                                          | W = Writable                               | bit              | U = Unimplem                | ented bit, read | <b>l as</b> '0'  |                |

| u = Bit is uncl | nanged                                                                                                         | x = Bit is unknown<br>'0' = Bit is cleared |                  | -n/n = Value a              | t POR and BO    | R/Value at all o | ther Resets    |

| 1' = Bit is set |                                                                                                                |                                            |                  | q = Value dep               | ends on condit  | ion              |                |

| bit 7           | See des<br>1 = System                                                                                          | scription in Sec                           | disabled (a.k.a. | tem Clock Disa              | ble".           |                  |                |

| bit 6           | <b>FVRMD:</b> Disable Fixed Voltage Reference (FVR) bit<br>1 = FVR module disabled<br>0 = FVR module enabled   |                                            |                  |                             |                 |                  |                |

| bit 5           | Unimpleme                                                                                                      | nted: Read as                              | ʻ0'              |                             |                 |                  |                |

| bit 4           | CRCMD: CRC module disable bit<br>1 = CRC module disabled<br>0 = CRC module enabled                             |                                            |                  |                             |                 |                  |                |

| bit 3           | SCANMD: Program Memory Scanner Module Disable bit<br>1 = Scanner module disabled<br>0 = Scanner module enabled |                                            |                  |                             |                 |                  |                |

| bit 2           | 1 = User me<br>FSR acc                                                                                         | •                                          |                  | nd writing is disa<br>zero. | abled; NVMCO    | N registers can  | not be writter |

| bit 1           | CLKRMD: Disable Clock Reference CLKR bit<br>1 = CLKR module disabled<br>0 = CLKR module enabled                |                                            |                  |                             |                 |                  |                |

| bit 0           | IOCMD: Disable Interrupt-on-Change bit, All Ports<br>1 = IOC module(s) disabled<br>0 = IOC module(s) enabled   |                                            |                  |                             |                 |                  |                |

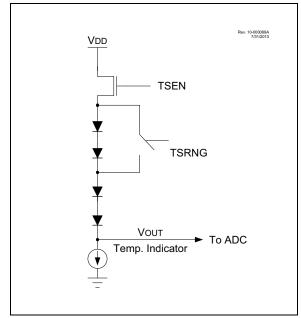

#### 17.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, "Use and Calibration of the Internal Temperature Indicator" (DS01333) for more details regarding the calibration process.

#### 17.1 Circuit Operation

Figure 17-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 17-1 describes the output characteristics of the temperature indicator.

#### EQUATION 17-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **16.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 17-1: TEMPERATURE CIRCUIT DIAGRAM

### 17.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 17-1 shows the recommended minimum  $V \mbox{\scriptsize DD}$  vs. range setting.

| TABLE 17-1: | <b>RECOMMENDED VDD VS.</b> |

|-------------|----------------------------|

|             | RANGE                      |

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

### 17.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 23.0 "Analog-to-Digital Converter With Computation (ADC2) Module" for detailed information.

| R/W-0/0          | U-0                                                      | R-0                                                                                                                          | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------------------|--------------|--|--|--|

| T0EN             |                                                          | TOOUT                                                                                                                        | T016BIT        |                  | TOOUTI           | PS<3:0>          |              |  |  |  |

| bit 7            |                                                          |                                                                                                                              |                |                  |                  |                  | bit (        |  |  |  |

|                  |                                                          |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

| Legend:          |                                                          |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

| R = Readable     | bit                                                      | W = Writable bit                                                                                                             |                | U = Unimplen     | nented bit, read | as '0'           |              |  |  |  |

| u = Bit is uncł  | nanged                                                   | x = Bit is unk                                                                                                               | nown           | -n/n = Value a   | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                                                          | '0' = Bit is cle                                                                                                             | ared           |                  |                  |                  |              |  |  |  |

|                  |                                                          |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

| bit 7            | TOEN: TMR0                                               |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  |                                                          | <ul> <li>1 = The module is enabled and operating</li> <li>0 = The module is disabled and in the lowest power mode</li> </ul> |                |                  |                  |                  |              |  |  |  |

|                  |                                                          |                                                                                                                              |                | vest power mot   | le               |                  |              |  |  |  |

| bit 6            | Unimplemen                                               |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

| bit 5            |                                                          | <b>T0OUT:</b> TMR0 Output bit (read-only)<br>TMR0 output bit                                                                 |                |                  |                  |                  |              |  |  |  |

| bit 4            | T016BIT: TMR0 Operating as 16-bit Timer Select bit       |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1 = TMR0 is a 16-bit timer<br>0 = TMR0 is an 8-bit timer |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

| L:1 0 0          |                                                          |                                                                                                                              |                |                  | L I              |                  |              |  |  |  |

| bit 3-0          |                                                          |                                                                                                                              | put postscaler | (divider) select | DIIS             |                  |              |  |  |  |

|                  | 1111 = 1:16 Postscaler<br>1110 = 1:15 Postscaler         |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1101 = 1:14 Postscaler                                   |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1100 = 1:13 Postscaler                                   |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1011 = 1:12 Postscaler                                   |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1010 = 1:11 Postscaler                                   |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1001 = 1:10 F                                            |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 1000 = 1:9 Pe                                            |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0111 = 1:8 Postscaler                                    |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0110 = 1:7 Postscaler                                    |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0101 = 1:6 Postscaler<br>0100 = 1:5 Postscaler           |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0100 = 1.3  P                                            |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0011 = 1.4 Pc<br>0010 = 1.3 Pc                           |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0001 = 1:2 P                                             |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

|                  | 0000 = 1:1 P                                             |                                                                                                                              |                |                  |                  |                  |              |  |  |  |

#### 29.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 29-3.

#### FIGURE 29-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                 | Rev. 10.000205A<br>180/2010 |

|-----------------|-----------------------------|

| CKPS            | 0b010                       |

| PRx             | 1                           |

| OUTPS           | 2                           |

| TMRx_clk        |                             |

| TMRx            |                             |

| TMRx_postscaled |                             |

| TMRxIF          | (1)                         |

|                 |                             |

|                 |                             |

#### 31.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 31-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 31-6, Figure 31-8, Figure 31-9 and Figure 31-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 31-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

Write to SSPxBUF SCK (CKP = 0  $\dot{C}KE = 0$ SCK (CKP = 1  $\dot{C}KE = 0$ ) 4 Clock Modes SCK (CKP = 0 CKE = 1) SCK (CKP = 1 CKE = 1) bit 6 bit 2 SDO bit 7 bit 5 bit 4 bit 3 bit 1 bit 0 (CKE = 0) bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 SDO (CKE = 1) SDI (SMP = 0)bit 7 bit 0 Input Sample (SMP = 0)SDI (SMP = 1) bit 7 hi 0 Input Sample (SMP = 1)1 SSPxIF SSPxSR to SSPxBUF

#### FIGURE 31-6: SPI MODE WAVEFORM (MASTER MODE)

## 31.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 31-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSPxIF is set.

- **Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

## 31.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 31-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 31-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

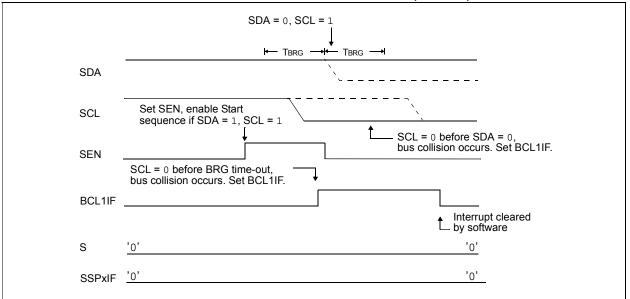

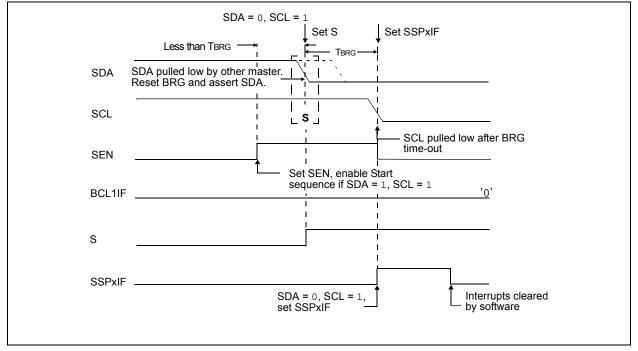

#### FIGURE 31-34: BUS COLLISION DURING START CONDITION (SCL = 0)

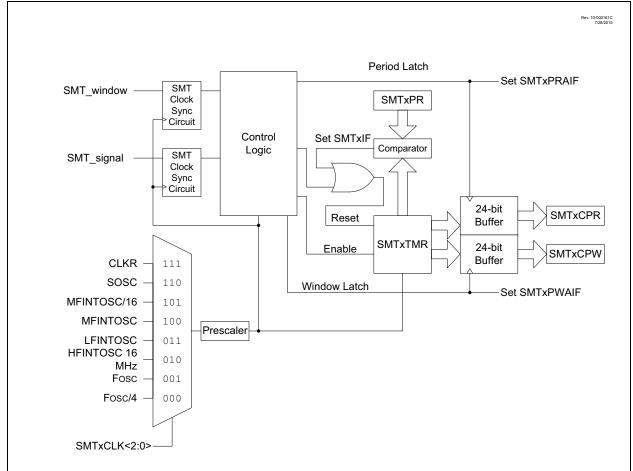

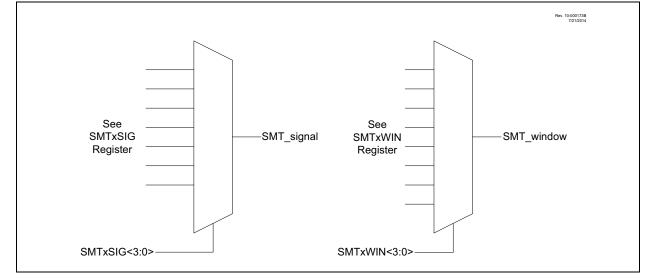

#### 32.6.8 CAPTURE MODE

This mode captures the Timer value based on a rising or falling edge on the SMTWINx input and triggers an interrupt. This mimics the capture feature of a CCP module. The timer begins incrementing upon the SMTxGO bit being set, and updates the value of the SMTxCPR register on each rising edge of SMTWINx, and updates the value of the CPW register on each falling edge of the SMTWINx. The timer is not reset by any hardware conditions in this mode and must be reset by software, if desired. See Figure 32-16 and Figure 32-17.

#### 34.0 REFERENCE CLOCK OUTPUT MODULE

The Reference Clock Output module provides the ability to send a clock signal to the clock reference output pin (CLKR). The Reference Clock Output can also be used as a signal for other peripherals, such as the Data Signal Modulator (DSM).

The Reference Clock Output module has the following features:

- · Selectable input clock

- Programmable clock divider

- · Selectable duty cycle

#### 34.1 CLOCK SOURCE

The Reference Clock Output module has a selectable clock source. The CLKRCLK register (Register 34-2) controls which input is used.

#### 34.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (CLKREN) is set, the module is ensured to be glitch-free at start-up.

When the Reference Clock Output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

#### 34.2 PROGRAMMABLE CLOCK DIVIDER

The module takes the system clock input and divides it based on the value of the CLKRDIV<2:0> bits of the CLKRCON register (Register 34-1).

The following configurations can be made based on the CLKRDIV<2:0> bits:

- Base Fosc value

- · Fosc divided by 2

- · Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDIV<2:0> bits should only be changed when the module is disabled (CLKREN = 0).

#### 34.3 SELECTABLE DUTY CYCLE

The CLKRDC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDC<1:0> bits should only be changed when the module is disabled (CLKREN = 0).

Note: The CLKRDC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

#### 34.4 OPERATION IN SLEEP MODE

The Reference Clock Output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the Reference Clock Output as an input signal.

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                                                   |

| Operands:        | None                                                                                                                                                                                                             |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ \text{0} \rightarrow \text{WDT} \text{ prescaler,} \\ \text{1} \rightarrow \overline{\text{TO}} \\ \text{1} \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                           |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{\text{TO}}$ and PD<br>are set.                                                             |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |