Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18854-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                | Function               | Input<br>Type              | Output Type | Description                                                                                     |  |  |

|-----------------------------------------------------------------------------------------------------|------------------------|----------------------------|-------------|-------------------------------------------------------------------------------------------------|--|--|

| RB7/ANB7/DAC1OUT2/T6IN <sup>(1)</sup> /<br>CLCIN3 <sup>(1)</sup> /IOCB7/ICSPDAT                     | RB7                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                            |  |  |

| CLCIN3 <sup>(*/</sup> IUCB7/ICSPDAI                                                                 | ANB7                   | AN                         | -           | ADC Channel B7 input.                                                                           |  |  |

|                                                                                                     | DAC1OUT2               | —                          | AN          | Digital-to-Analog Converter output.                                                             |  |  |

|                                                                                                     | T6IN <sup>(1)</sup>    | TTL/ST                     | -           | Timer6 external digital clock input.                                                            |  |  |

|                                                                                                     | CLCIN3 <sup>(1)</sup>  | TTL/ST                     | -           | Configurable Logic Cell source input.                                                           |  |  |

|                                                                                                     | IOCB7                  | TTL/ST                     | -           | Interrupt-on-change input.                                                                      |  |  |

|                                                                                                     | ICSPDAT                | ST                         | CMOS        | In-Circuit Serial Programming™ and debugging data input/out put.                                |  |  |

| RC0/ANC0/T1CKI(1)/T3CKI <sup>(1)</sup> /T3G <sup>(1)</sup> /<br>SMTWIN1 <sup>(1)</sup> /IOCC0/SOSCO | RC0                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                            |  |  |

| SMTWIN1 <sup>**</sup> /IOCC0/SOSCO                                                                  | ANC0                   | AN                         | -           | ADC Channel C0 input.                                                                           |  |  |

|                                                                                                     | T1CKI <sup>(1)</sup>   | TTL/ST                     | -           | Timer1 external digital clock input.                                                            |  |  |

|                                                                                                     | T3CKI <sup>(1)</sup>   | TTL/ST                     | -           | Timer3 external digital clock input.                                                            |  |  |

|                                                                                                     | T3G <sup>(1)</sup>     | TTL/ST                     | -           | Timer3 gate input.                                                                              |  |  |

|                                                                                                     | SMTWIN1 <sup>(1)</sup> | TTL/ST                     | -           | Signal Measurement Timer1 (SMT1) input.                                                         |  |  |

|                                                                                                     | IOCC0                  | TTL/ST                     | -           | Interrupt-on-change input.                                                                      |  |  |

|                                                                                                     | SOSCO                  | —                          | AN          | 32.768 kHz secondary oscillator crystal driver output.                                          |  |  |

| RC1/ANC1/SMTSIG1 <sup>(1)</sup> /CCP2 <sup>(1)</sup> /                                              | RC1                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                            |  |  |

| IOCC1/SOSCI                                                                                         | ANC1                   | AN                         | -           | ADC Channel C1 input.                                                                           |  |  |

|                                                                                                     | SMTSIG1 <sup>(1)</sup> | TTL/ST                     | -           | Signal Measurement Timer1 (SMT1) signal input.                                                  |  |  |

|                                                                                                     | CCP2 <sup>(1)</sup>    | TTL/ST                     | CMOS/OD     | Capture/compare/PWM2 (default input location for capture function).                             |  |  |

|                                                                                                     | IOCC1                  | TTL/ST                     | -           | Interrupt-on-change input.                                                                      |  |  |

|                                                                                                     | SOSCI                  | AN                         | —           | 32.768 kHz secondary oscillator crystal driver input.                                           |  |  |

| RC2/ANC2/T5CKI <sup>(1)</sup> /CCP1 <sup>(1)</sup> /IOCC2                                           | RC2                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                            |  |  |

|                                                                                                     | ANC2                   | AN                         | -           | ADC Channel C2 input.                                                                           |  |  |

|                                                                                                     | T5CKI <sup>(1)</sup>   | TTL/ST                     | -           | Timer5 external digital clock input.                                                            |  |  |

|                                                                                                     | CCP1 <sup>(1)</sup>    | TTL/ST                     | CMOS/OD     | Capture/compare/PWM1 (default input location for capture function).                             |  |  |

|                                                                                                     | IOCC2                  | TTL/ST                     | —           | Interrupt-on-change input.                                                                      |  |  |

| RC3/ANC3/SCL1 <sup>(3,4)</sup> /SCK1 <sup>(1)</sup> /T2IN <sup>(1)</sup> /<br>IOCC3                 | RC3                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                            |  |  |

| 0003                                                                                                | ANC3                   | AN                         | _           | ADC Channel C3 input.                                                                           |  |  |

|                                                                                                     | SCL1 <sup>(3,4)</sup>  | l <sup>2</sup> C/<br>SMBus | OD          | MSSP1 I <sup>2</sup> C clock input/output.                                                      |  |  |

|                                                                                                     | SCK1 <sup>(1)</sup>    | TTL/ST                     | CMOS/OD     | MSSP1 SPI clock input/output (default input location, SCK1 is PPS remappable input and output). |  |  |

|                                                                                                     | T2IN <sup>(1)</sup>    | TTL/ST                     | _           | Timer2 external input.                                                                          |  |  |

|                                                                                                     | IOCC3                  | TTL/ST                     | _           | Interrupt-on-change input.                                                                      |  |  |

#### **TABLE 1-2:** PIC16F18854 PINOUT DESCRIPTION (CONTINUED)

CMOS = CMOS compatible input or output Legend: AN = Analog input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

OD I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx Note 1: pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

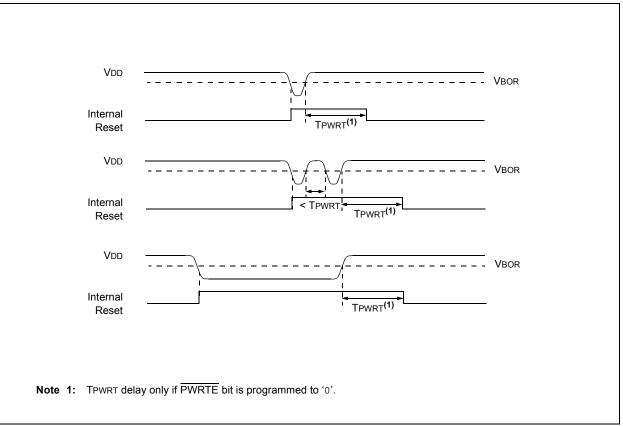

#### FIGURE 5-2: BROWN-OUT SITUATIONS

#### 5.2.4 BOR IS ALWAYS OFF

When the BOREN bits of the Configuration Words are programmed to '00', the BOR is off at all times. The device start-up is not delayed by the BOR ready condition or the VDD level.

### 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device reset, including when it is first powered up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the external clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 500 kHz)

- 2. ECM External Clock Medium Power mode (500 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these clock sources.

| R-q/q            | R-0/q                                                                                                                                         | R-0/q                                                           | R-0/q   | R-q/q            | R-q/q              | U-0               | R-q/q  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------|------------------|--------------------|-------------------|--------|

| EXTOR            | HFOR                                                                                                                                          | MFOR                                                            | LFOR    | SOR              | ADOR               | _                 | PLLR   |

| bit 7            |                                                                                                                                               |                                                                 |         |                  |                    |                   | bit    |

| Legend:          |                                                                                                                                               |                                                                 |         |                  |                    |                   |        |

| R = Readable     | bit                                                                                                                                           | W = Writable b                                                  | it      | U = Unimplem     | ented bit, read as | '0'               |        |

| u = Bit is unch  | anged                                                                                                                                         | x = Bit is unkno                                                | wn      | -n/n = Value at  | POR and BOR/Va     | alue at all other | Resets |

| '1' = Bit is set |                                                                                                                                               | '0' = Bit is clear                                              | ed      |                  |                    |                   |        |

| bit 7            | 1 = The osc                                                                                                                                   | DSC (external) O<br>illator is ready to<br>illator is not enab  | be used |                  | d.                 |                   |        |

| bit 6            | 1 = The osc                                                                                                                                   | OSC Oscillator R<br>illator is ready to<br>illator is not enab  | be used | ready to be use  | d.                 |                   |        |

| bit 5            | 1 = The oscil                                                                                                                                 | FOSC Oscillator F<br>lator is ready to b<br>lator is not enable | e used  | ready to be used |                    |                   |        |

| bit 4            | 1 = The osc                                                                                                                                   | OSC Oscillator Re<br>illator is ready to<br>llator is not enabl | be used | ready to be used | d.                 |                   |        |

| bit 3            | 1 = The osc                                                                                                                                   | ary (Timer1) Osci<br>illator is ready to<br>llator is not enabl | be used | ready to be used | d.                 |                   |        |

| bit 2            | ADOR: CRC Oscillator Ready bit<br>1 = The oscillator is ready to be used<br>0 = The oscillator is not enabled, or is not yet ready to be used |                                                                 |         |                  |                    |                   |        |

| bit 1            | Unimplement                                                                                                                                   | ed: Read as '0'                                                 | -       | -                |                    |                   |        |

| bit 0            | 1 = The PLL                                                                                                                                   |                                                                 |         |                  |                    |                   |        |

| U-0                                     | U-0 | R/W-0/0           | R/W-0/0                                               | U-0                                | U-0     | U-0 | R/W-0/0 |  |

|-----------------------------------------|-----|-------------------|-------------------------------------------------------|------------------------------------|---------|-----|---------|--|

| —                                       | —   | TMR0IE            | IOCIE                                                 | —                                  | —       | —   | INTE    |  |

| bit 7                                   |     |                   |                                                       |                                    |         |     | bit 0   |  |

|                                         |     |                   |                                                       |                                    |         |     |         |  |

| Legend:                                 |     |                   |                                                       |                                    |         |     |         |  |

| R = Readable bit W = Writable bit       |     |                   | bit                                                   | U = Unimplemented bit, read as '0' |         |     |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |     |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared                                                  | HS = Hardwa                        | are set |     |         |  |

|                                         |     |                   |                                                       |                                    |         |     |         |  |

#### REGISTER 7-2: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

| bit 5   | TMR0IE: TMR0 Overflow Interrupt Enable bit           |

|---------|------------------------------------------------------|

|         | <ol> <li>Enables the TMR0 interrupt</li> </ol>       |

|         | 0 = Disables the TMR0 interrupt                      |

| bit 4   | IOCIE: Interrupt-on-Change Interrupt Enable bit      |

|         | <ol> <li>Enables the IOC change interrupt</li> </ol> |

|         | 0 = Disables the IOC change interrupt                |

| bit 3-1 | Unimplemented: Read as '0'                           |

| bit 0   | INTE: INT External Interrupt Flag bit <sup>(1)</sup> |

|         | 1 = Enables the INT external interrupt               |

|         | 0 = Disables the INT external interrupt              |

|         |                                                      |

Unimplemented: Read as '0'

bit 7-6

#### Note 1: The External Interrupt GPIO pin is selected by INTPPS (Register 13-1).

| Note: | Bit PEIE of the INTCON register must be    |

|-------|--------------------------------------------|

|       | set to enable any peripheral interrupt     |

|       | controlled by PIE1-PIE8. Interrupt sources |

|       | controlled by the PIE0 register do not     |

|       | require PEIE to be set in order to allow   |

|       | interrupt vectoring (when GIE is set).     |

| REGISTER 7-14: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3 |                                                                                                                                                                                                                                   |                  |                |                                      |                  |                  |              |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|--------------------------------------|------------------|------------------|--------------|

| U-0                                                          | U-0                                                                                                                                                                                                                               | R-0              | R-0            | R/W/HS-0/0                           | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0   |

| _                                                            | _                                                                                                                                                                                                                                 | RCIF             | TXIF           | BCL2IF                               | SSP2IF           | BCL1IF           | SSP1IF       |

| bit 7                                                        |                                                                                                                                                                                                                                   |                  |                |                                      |                  |                  | bit          |

|                                                              |                                                                                                                                                                                                                                   |                  |                |                                      |                  |                  |              |

| Legend:                                                      |                                                                                                                                                                                                                                   |                  |                |                                      |                  |                  |              |

| R = Readable                                                 | e bit                                                                                                                                                                                                                             | W = Writable     | bit            | U = Unimpler                         | mented bit, read | l as '0'         |              |

| u = Bit is unc                                               | hanged                                                                                                                                                                                                                            | x = Bit is unkr  | nown           | -n/n = Value a                       | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set                                             | t                                                                                                                                                                                                                                 | '0' = Bit is cle | ared           | HS = Hardwa                          | are clearable    |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                |                                      |                  |                  |              |

| bit 7-6                                                      | Unimplemen                                                                                                                                                                                                                        | ted: Read as '   | 0'             |                                      |                  |                  |              |

| bit 5                                                        |                                                                                                                                                                                                                                   |                  | 1 0 (          | ead-only) bit <sup>(1)</sup>         |                  |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                | npty (contains a                     | t least one byte | )                |              |

|                                                              |                                                                                                                                                                                                                                   | ART receive bu   |                | · · · · · · · · · (2)                |                  |                  |              |

| bit 4                                                        |                                                                                                                                                                                                                                   | RT Transmit Int  |                |                                      |                  |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                |                                      | noccupied spac   |                  | rite to TXRE |

|                                                              |                                                                                                                                                                                                                                   |                  |                | ilable in the trar                   |                  |                  |              |

| bit 3                                                        | BCL2IF: MSS                                                                                                                                                                                                                       | SP2 Bus Collisi  | on Interrupt F | lag bit                              |                  |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  | •              | e cleared in soft                    | ware)            |                  |              |

|                                                              |                                                                                                                                                                                                                                   | ollision was det |                |                                      |                  |                  |              |

| bit 2                                                        | •                                                                                                                                                                                                                                 |                  | •              | 2) Interrupt Fla                     | •                |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                | ndition is compl<br>on/Bus Condition | ete (must be cle | eared in softwa  | re)          |

| bit 1                                                        | •                                                                                                                                                                                                                                 | SP1 Bus Collisi  | •              |                                      | on in progress   |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                | e cleared in soft                    | ware)            |                  |              |

|                                                              |                                                                                                                                                                                                                                   | ollision was de  | •              |                                      | (Marc)           |                  |              |

| bit 0                                                        | SSP1IF: Syno                                                                                                                                                                                                                      | chronous Seria   | I Port (MSSP   | 1) Interrupt Fla                     | g bit            |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                |                                      | ete (must be cle | eared in softwa  | re)          |

|                                                              | 0 = Waiting f                                                                                                                                                                                                                     | or the Transmi   | ssion/Recepti  | on/Bus Conditi                       | on in progress   |                  |              |

|                                                              | ne RCIF flag is a                                                                                                                                                                                                                 |                  |                |                                      | mware must re    | ad from RCRE     | G enough     |

|                                                              | nes to remove al                                                                                                                                                                                                                  | •                |                |                                      |                  |                  |              |

|                                                              | 2: The TXIF flag is a read-only bit, indicating if there is room in the transmit buffer. To clear the TXIF flag, the firmware must write enough data to TXREG to completely fill all available bytes in the buffer. The TXIF flag |                  |                |                                      |                  |                  |              |

|                                                              | bes not indicate t                                                                                                                                                                                                                |                  |                |                                      |                  | s in the buller. |              |

|                                                              |                                                                                                                                                                                                                                   |                  | <b>\</b>       |                                      |                  |                  |              |

|                                                              |                                                                                                                                                                                                                                   |                  |                |                                      |                  |                  |              |

| Mater In                                                     | to much floor bits o                                                                                                                                                                                                              |                  | interrunt      |                                      |                  |                  |              |

| Note: | Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of |

|-------|-----------------------------------------------------------------------------------------------|

|       | its corresponding enable bit or the Global                                                    |

|       | Enable bit, GIE, of the INTCON register.                                                      |

|       | User software should ensure the                                                               |

|       | appropriate interrupt flag bits are clear                                                     |

|       | prior to enabling an interrupt.                                                               |

| R/W-0/0           | R/W/HC-0/0                        | R-0                       | R-0                         | R/W-0/0             | U-0                      | R/W-0/0         | R/W-0/0              |

|-------------------|-----------------------------------|---------------------------|-----------------------------|---------------------|--------------------------|-----------------|----------------------|

| EN <sup>(1)</sup> | SCANGO <sup>(2, 3)</sup>          | BUSY <sup>(4)</sup>       | INVALID                     | INTM                | —                        | MODE            | <1:0> <sup>(5)</sup> |

| bit 7             |                                   |                           | •                           |                     |                          |                 | bit                  |

|                   |                                   |                           |                             |                     |                          |                 |                      |

| Legend:           |                                   |                           |                             |                     |                          |                 |                      |

| R = Readabl       | le bit                            | W = Writable              | bit                         | U = Unimplem        | ented bit, rea           | id as '0'       |                      |

| u = Bit is und    | changed                           | x = Bit is unk            | nown                        | -n/n = Value at     | t POR and B              | OR/Value at all | other Resets         |

| '1' = Bit is se   | et                                | '0' = Bit is cle          | eared                       | HC = Bit is cle     | ared by hard             | ware            |                      |

|                   |                                   |                           |                             |                     |                          |                 |                      |

| bit 7             | EN: Scanner                       | Enable bit <sup>(1)</sup> |                             |                     |                          |                 |                      |

|                   | 1 = Scanner i                     |                           |                             |                     |                          |                 |                      |

|                   |                                   |                           | ernal states ar             | e reset             |                          |                 |                      |

| bit 6             | SCANGO: So                        |                           |                             |                     |                          | dias to MDv os  | d data nasaa         |

|                   |                                   | ent peripheral.           |                             | NVM will be acc     | cessed accord            | ang to MDx an   | u data passe         |

|                   | 0 = Scanner o                     |                           |                             |                     |                          |                 |                      |

| bit 5             | BUSY: Scann                       | ner Busy Indic            | ator bit <sup>(4)</sup>     |                     |                          |                 |                      |

|                   | 1 = Scanner o                     |                           |                             |                     |                          |                 |                      |

|                   | 0 = Scanner o                     | cycle is compl            | ete (or never s             | tarted)             |                          |                 |                      |

| bit 4             | INVALID: Scanner Abort signal bit |                           |                             |                     |                          |                 |                      |

|                   |                                   |                           |                             | ontains an invali   | d address <sup>(6)</sup> |                 |                      |

| L:1 0             |                                   | -                         | to a valid addre            |                     | L 14                     |                 |                      |

| bit 3             |                                   |                           | upt Manageme                | ent Mode Select     | DIT                      |                 |                      |

|                   | If MODE = 10<br>This bit is igno  | -                         |                             |                     |                          |                 |                      |

|                   | •                                 |                           | d until all data is         | s transferred):     |                          |                 |                      |

|                   |                                   |                           |                             | ig interrupt opera  | tion: scanner            | resumes after   | returnina fror       |

|                   | interrupt                         |                           | (                           | .g                  | ,                        |                 |                      |

|                   |                                   |                           | d by interrupts             | , the interrupt res | sponse will be           | e affected      |                      |

|                   | <u>If MODE = 00</u>               |                           |                             |                     |                          |                 |                      |

|                   | 1 = SCANGO<br>from inte           |                           | (to zero) during            | g interrupt operat  | ion; scan ope            | rations resume  | after returning      |

|                   |                                   |                           | nt NVM access               | 5                   |                          |                 |                      |

| bit 2             | Unimplemen                        | -                         |                             |                     |                          |                 |                      |

| bit 1-0           | •                                 |                           | ess Mode bits <sup>(§</sup> | 5)                  |                          |                 |                      |

|                   | 11 = Triggere                     |                           |                             |                     |                          |                 |                      |

|                   | 10 = Peek mo                      | ode                       |                             |                     |                          |                 |                      |

|                   | 01 = Burst mo                     |                           |                             |                     |                          |                 |                      |

|                   | 00 = Concurr                      | ent mode                  |                             |                     |                          |                 |                      |

|                   | etting EN = 0 (SO                 |                           |                             | -                   | -                        | tent.           |                      |

|                   | his bit is cleared                |                           | -                           | -                   |                          |                 |                      |

|                   | INTM = 1, this bi                 |                           | -                           |                     |                          | -               |                      |

|                   | USY = $1$ when the $11 + 1$ for   |                           | -                           | or when the CRC     | senos a read             | ay signal.      |                      |

|                   | ee Table 11-1 for                 |                           |                             | ngo of the DEM      | ic coornod o             | ad completed i  | a daviaa             |

|                   | n invalid address                 |                           |                             | after the last so   |                          |                 |                      |

#### REGISTER 11-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

address is invalid.

memory is 0x4000 and SCANHADR = 0x3FFF, after the last scan SCANLADR increments to 0x4000, the

#### 14.0 PERIPHERAL MODULE DISABLE

The PIC16F18855/75 provides the ability to disable selected modules, placing them into the lowest possible Power mode.

For legacy reasons, all modules are ON by default following any Reset.

### 14.1 Disabling a Module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- The module is held in Reset.

- · Any SFRs become "unimplemented"

- Writing is disabled

- Reading returns 00h

- Module outputs are disabled; I/O goes to the next module according to pin priority

#### 14.2 Enabling a module

When the register bit is cleared, the module is reenabled and will be in its Reset state; SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

#### 14.3 Disabling a Module

When a module is disabled, any and all associated input selection registers (ISMs) are also disabled.

#### 14.4 System Clock Disable

Setting SYSCMD (PMD0, Register 14-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

### 20.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous ECCP functions.

The CWG has the following features:

- · Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- Output polarity control

- · Output steering

- Synchronized to rising event

- Immediate effect

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

The CWG modules available are shown in Table 20-1.

#### TABLE 20-1: AVAILABLE CWG MODULES

| Device         | CWG1 | CWG2 | CWG2 |

|----------------|------|------|------|

| PIC16(L)F18854 | •    | •    | •    |

#### 20.1 Fundamental Operation

The CWG module can operate in six different modes, as specified by MODE of the CWGxCON0 register:

- Half-Bridge mode (Figure 20-9)

- Push-Pull mode (Figure 20-2)

- Full-Bridge mode, Forward (Figure 20-3)

- Full-Bridge mode, Reverse (Figure 20-3)

- Steering mode (Figure 20-10)

- Synchronous Steering mode (Figure 20-11)

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. Thus, all output modes support auto-shutdown, which is covered in **20.10 "Auto-Shutdown"**.

#### 20.1.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 20-9. A non-overlap (dead-band) time is inserted between the two outputs to prevent shoot through current in various power supply applications. Dead-band control is described in **Section 20.5 "Dead-Band Control"**.

The unused outputs CWGxC and CWGxD drive similar signals, with polarity independently controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

#### **REGISTER 20-8: CWGxCLK: CWGx CLOCK SELECTION REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|-----|---------|

| —     | —   | —   |     | —   | —   |     | CS      |

| bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-1 Unimplemented: Read as '0'

bit 0

CS: CWGx Clock Selection bit

1 = HFINTOSC 16 MHz is selected

0 = Fosc is selected

#### REGISTER 20-9: CWGxISM: CWGx INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   |         | IS<     | 3:0>    |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-4 | Unimplemented: Read as '0'             |

|---------|----------------------------------------|

| bit 3-0 | IS<3:0>: CWGx Input Selection bits     |

|         | 1111 = Reserved. No channel connected. |

|         | •                                      |

|         | •                                      |

|         | •                                      |

1011 = Reserved. No channel connected. 1010 = PWM4\_out 1001 = PWM3\_out 1000 = Reserved. No channel connected. 0111 = Reserved. No channel connected. 0110 = LC2\_out 0101 = LC1\_out 0101 = LC1\_out 0100 = CCP4\_out 0011 = CCP3\_out 0010 = CCP2\_out 0001 = CCP1\_out 0000 = CWGx1CLK

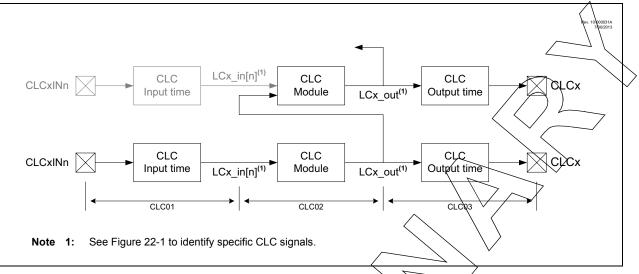

### 22.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 22.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 22-2. Data inputs in the figure are identified by a generic numbered input name.

Table 22-2 correlates the generic input name to the actual signal for each CLC module. The column labeled 'LCxDyS<4:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation for the MUX select input codes: LCxD1S<4:0> through LCxD4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 22-3 through Register 22-6).

#### TABLE 22-2: CLCx DATA INPUT SELECTION

| LCxDyS<4:0><br>Value     | CLCx Input Source     |

|--------------------------|-----------------------|

| 110000 to 111111 [48+]   | Reserved              |

| 101111 [47]              | CWG3B output          |

| 101110 [46]              | CWG3A output          |

| 101101 [45]              | CWG2B output          |

| 101100 [44]              | CWG2A output          |

| 101011 [43]              | CWG1B output          |

| 101010 <b>[42]</b>       | CWG1A output          |

| 101001 [41]              | MSSP2 SCK output      |

| 101000 [40]              | MSSP2 SDO output      |

| 100111 <b>[39]</b>       | MSSP1 SCK output      |

| 100110 <b>[38]</b>       | MSSP1 SDO output      |

| 100101 [37]              | EUSART (TX/CK) output |

| 100100 <b>[36]</b>       | EUSART (DT) output    |

| 100011 [35]              | CLC4 output           |

| 100010 [34]              | CLC3 output           |

| 100001 [33]              | CLC2 output           |

| 100000 [32]              | CLC1 output           |

| 011111 [31]              | DSM output            |

| 011110 [30]              | IOCIF                 |

| 011101 [29]              | ZCD output            |

| 011100 [28]              | Comparator 2 output   |

| 011011 [27]              | Comparator 1 output   |

| 011010 [26]              | NCO1 output           |

| 011001 [25]              | PWM7 output           |

| 011000 [24]              | PWM6 output           |

| 010111 [23]              | CCP5 output           |

| 010110 [22]              | CCP4 output           |

| 010101 [21]              | CCP3 output           |

| 010100 [20]              | CCP2 output           |

| 010011 [19]              | CCP1 output           |

| 010010 [18]              | SMT2 output           |

| 010001 [17]              | SMT1 output           |

| 010000 [16]              | TMR6 to PR6 match     |

| 001111 [15]              | TMR5 overflow         |

| 001110 [14]              | TMR4 to PR4 match     |

| 001101 [13]              | TMR3 overflow         |

| 001100 [12]              | TMR2 to PR2 match     |

| 001011 [11]              | TMR1 overflow         |

| 001010 [10]              | TMR0 overflow         |

| 001001 [9]               | CLKR output           |

| 001000 [8]               | FRC                   |

| 000111 [7]               | SOSC                  |

| 000110 [6]               | LFINTOSC              |

| 000101 [5]               | HFINTOSC              |

| 000100 [4]               | Fosc                  |

| 000011 [3]               | CLCIN3PPS             |

|                          | CLCIN2PPS             |

|                          |                       |

| 000010 [2]<br>000001 [1] | CLCIN1PPS             |

#### 25.6 Register Definitions: DAC Control

#### REGISTER 25-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | U-0                                                                                                                                                                                                     | R/W-0/0           | R/W-0/0        | R/W-0/0        | R/W-0/0          | U-0            | R/W-0/0      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|----------------|------------------|----------------|--------------|

| DAC1EN           | _                                                                                                                                                                                                       | DAC10E1           | DAC10E2        |                | PSS<1:0>         | _              | DAC1NSS      |

| bit 7            |                                                                                                                                                                                                         |                   |                |                |                  |                | bit C        |

|                  |                                                                                                                                                                                                         |                   |                |                |                  |                |              |

| Legend:          |                                                                                                                                                                                                         |                   |                |                |                  |                |              |

| R = Readable     | bit                                                                                                                                                                                                     | W = Writable      | bit            | U = Unimpler   | mented bit, read | as '0'         |              |

| u = Bit is unch  | anged                                                                                                                                                                                                   | x = Bit is unkr   | nown           | -n/n = Value a | at POR and BOF   | R/Value at all | other Resets |

| '1' = Bit is set |                                                                                                                                                                                                         | '0' = Bit is clea | ared           |                |                  |                |              |

| bit 7            | 27.00.2.0.27                                                                                                                                                                                            | C1 Enable bit     |                |                |                  |                |              |

|                  | 1 = DAC is e<br>0 = DAC is d                                                                                                                                                                            |                   |                |                |                  |                |              |

| bit 6            | Unimplemen                                                                                                                                                                                              | ted: Read as '    | D'             |                |                  |                |              |

| bit 5            | <b>DAC1OE1:</b> DAC1 Voltage Output 1 Enable bit<br>1 = DAC voltage level is also an output on the DAC1OUT1 pin<br>0 = DAC voltage level is disconnected from the DAC1OUT1 pin                          |                   |                |                |                  |                |              |

| bit 4            | <ul> <li>DAC1OE2: DAC1 Voltage Output 1 Enable bit</li> <li>1 = DAC voltage level is also an output on the DAC1OUT2 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT2 pin</li> </ul> |                   |                |                |                  |                |              |

| bit 3-2          |                                                                                                                                                                                                         |                   | itive Source S | Select bits    |                  |                |              |

| bit 1            | Unimplemented: Read as '0'                                                                                                                                                                              |                   |                |                |                  |                |              |

| bit 0            | DAC1NSS: DAC1 Negative Source Select bits<br>1 = VREF- pin<br>0 = Vss                                                                                                                                   |                   |                |                |                  |                |              |

#### REGISTER 25-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | DAC1R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5Unimplemented: Read as '0'bit 4-0DAC1R<4:0>: DAC1 Voltage Output Select bits

Vout = (Vsrc+ - Vsrc-)\*(DAC1R<4:0>/32) + Vsrc

#### 29.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

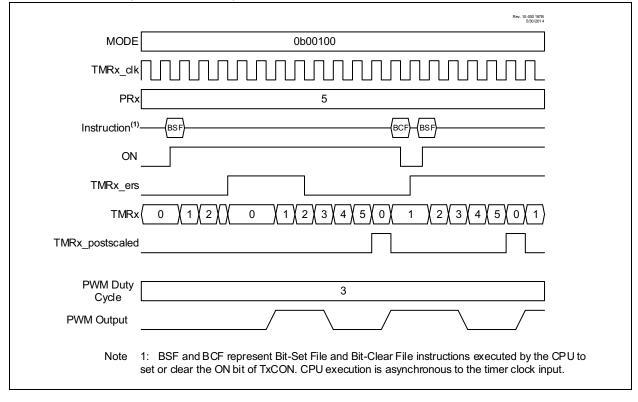

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

#### FIGURE 29-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 29-6.

| Name     | Bit 7       | Bit 6                                  | Bit 5                           | Bit 4  | Bit 3         | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |  |

|----------|-------------|----------------------------------------|---------------------------------|--------|---------------|-----------|---------|---------|---------------------|--|

| CCP1CON  | EN          |                                        | OUT                             | FMT    | FMT MODE<3:0> |           |         |         | 418                 |  |

| CCP2CON  | EN          | _                                      | OUT                             | FMT    |               | MODE      | =<3:0>  |         | 418                 |  |

| CCPTMRS0 | C4TSE       | L<1:0>                                 | C3TSE                           | L<1:0> | C2TSE         | L<1:0>    | C1TSE   | L<1:0>  | 421                 |  |

| CCPTMRS1 | _           | —                                      | P7TSE                           | L<1:0> | P6TSE         | L<1:0>    | C5TSE   | :L<1:0> | 421                 |  |

| INTCON   | GIE         | PEIE                                   | —                               | —      | —             | —         | —       | INTEDG  | 114                 |  |

| PIE1     | OSFIE       | CSWIE                                  | —                               | —      | —             | _         | ADTIE   | ADIE    | 116                 |  |

| PIR1     | OSFIF       | CSWIF                                  | —                               | _      | —             | _         | ADTIF   | ADIF    | 125                 |  |

| PR2      | Timer2 Mod  | ule Period Re                          | le Period Register              |        |               |           |         |         | 389*                |  |

| TMR2     | Holding Reg | ister for the 8                        | ter for the 8-bit TMR2 Register |        |               |           |         |         | 389*                |  |

| T2CON    | ON          |                                        | CKPS<2:0>                       |        |               | 407       |         |         |                     |  |

| T2CLKCON | —           |                                        | — — CS<3:0>                     |        |               |           |         |         | 406                 |  |

| T2RST    | _           | _                                      | _                               |        |               | RSEL<4:0> |         |         | 409                 |  |

| T2HLT    | PSYNC       | CKPOL                                  | CKSYNC                          | —      |               | 408       |         |         |                     |  |

| PR4      | Timer4 Mod  | ule Period Re                          | le Period Register              |        |               |           |         |         | 389*                |  |

| TMR4     | Holding Reg | g Register for the 8-bit TMR4 Register |                                 |        |               |           |         |         | 389*                |  |

| T4CON    | ON          |                                        | CKPS<2:0>                       |        |               | 407       |         |         |                     |  |

| T4CLKCON | —           | _                                      | _                               | _      | —             |           | 406     |         |                     |  |

| T4RST    | —           | _                                      | —                               |        |               | RSEL<4:0> |         |         | 409                 |  |

| T4HLT    | PSYNC       | CKPOL                                  | CKSYNC                          | -      |               | MODE      | E<3:0>  |         | 408                 |  |

| PR6      | Timer6 Mod  | lule Period Register                   |                                 |        |               |           |         | 389*    |                     |  |

| TMR6     | Holding Reg | g Register for the 8-bit TMR6 Register |                                 |        |               |           |         |         |                     |  |

| T6CON    | ON          |                                        | CKPS<2:0>                       |        |               | OUTP      | S<3:0>  |         | 407                 |  |

| T6CLKCON | —           | _                                      | _                               | —      | —             |           | CS<2:0> |         | 406                 |  |

| T6RST    | —           |                                        | _                               |        |               | RSEL<4:0> |         |         | 409                 |  |

| T6HLT    | PSYNC       | CKPOL                                  | CKSYNC                          | _      |               | MODE      | E<3:0>  |         | 408                 |  |

#### TABLE 29-3: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

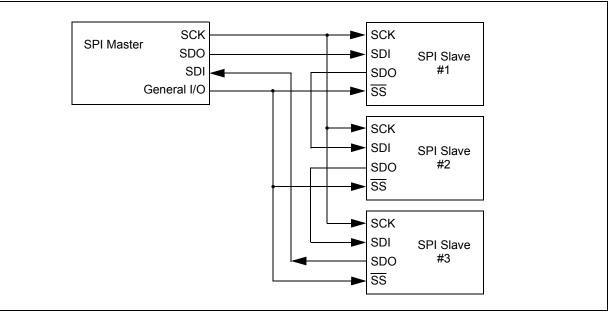

#### FIGURE 31-7: SPI DAISY-CHAIN CONNECTION

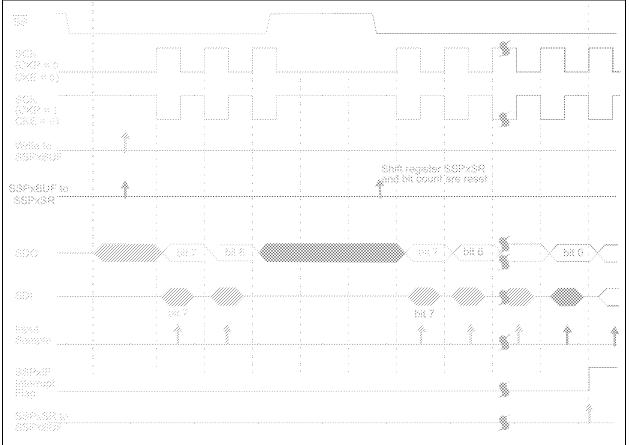

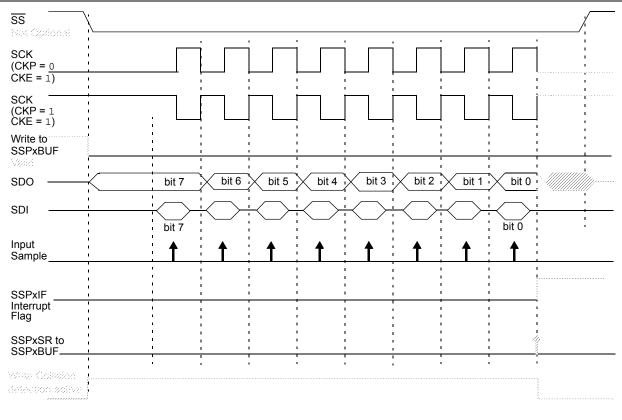

| FIGURE 31-9: | SDI MODE WAVEFORM | (SLAVE MODE WITH CKE = 0)  |

|--------------|-------------------|----------------------------|

| FIGURE 31-9. | SPI WODE WAVEFORW | (SLAVE WIDDE WITH CRE - U) |

|                                                |                                       |        |              |          |                       |                  |                  |            |                                         | ,  | . j                                       |

|------------------------------------------------|---------------------------------------|--------|--------------|----------|-----------------------|------------------|------------------|------------|-----------------------------------------|----|-------------------------------------------|

|                                                |                                       |        |              |          |                       |                  |                  |            |                                         |    | :<br>:<br>:<br>:                          |

| - (KE = 0)<br>- SOX<br>- CXF = 1<br>- CXF = 0) | ·<br>·<br>·                           |        |              |          |                       |                  |                  |            |                                         |    | :<br>:<br>:<br>:                          |

| VVRE 0<br>SSP2817                              | · · · · · · · · · · · · · · · · · · · |        |              | 2        | 9<br>1<br>1<br>1<br>1 | ;<br>;<br>;<br>; |                  | 5          | \$<br>c<br>c<br>s<br>s                  |    | ,<br>,<br>,<br>,                          |

| N384<br>8920                                   |                                       | K 23.7 | <u> 88 8</u> | X 88 8   | X 337.4               | K 888.8          | X 398, Z         | X 323      |                                         |    | ········<br>· · · · · · · · · · · · · · · |

| 903                                            | · · · · · · · · · · · · · · · · · · · |        |              |          |                       |                  |                  |            |                                         |    | ,<br>;<br>;<br>,                          |

| ingsti<br>Sørrigiø                             | · · · · · · · · · · · · · · · · · · · | 14p.   |              |          |                       | . //s.           |                  | :<br>      | s<br>,<br>,                             | ų. |                                           |

| SSPodi<br>Internupt<br>Flag                    | :<br>:<br>:                           |        | :            | 4 4<br>5 | :<br>:<br>:           | ;<br>,<br>,<br>, | :                |            | > .<br>< .<br>&                         |    |                                           |

| 939258 6<br>8997-8997                          | ·                                     | ·      |              | 5        | :<br>:                |                  | 2<br>2<br>2<br>2 | ><br>><br> | \$;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |    |                                           |

| Verite Codisson<br>detection active            |                                       |        |              |          |                       |                  |                  |            |                                         |    |                                           |

#### 32.6.9 COUNTER MODE

This mode increments the timer on each pulse of the SMTx\_signal input. This mode is asynchronous to the SMT clock and uses the SMTx\_signal as a time source. The SMTxCPW register will be updated with the current SMTxTMR value on the rising edge of the SMTxWIN input. See Figure 32-18.

| SWAPF            | Swap Nibbles in f                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                  |