Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

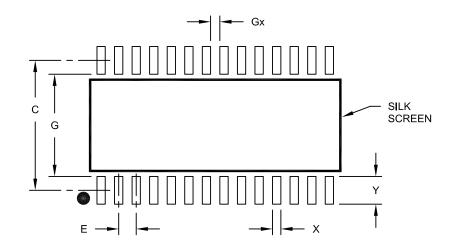

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18854-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Digital Peripherals (Cont.)**

- Cyclical Redundancy Check (CRC/SCAN):

- 16-bit CRC

- Scans memory for NVM integrity

- Communication:

- EUSART, RS-232, RS-485, LIN compatible

- Two SPI

- Two I<sup>2</sup>C, SMBus, PMBus™ compatible

- Up to 25 I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Input level selection control (ST or TTL)

- Digital open-drain enable

- Current mode enable

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

- Data Signal Modulator (DSM)

- Modulates a carrier signal with digital data to create custom carrier synchronized output waveforms

## **Analog Peripherals**

- Analog-to-Digital Converter with Computation (ADC<sup>2</sup>):

- 10-bit with up to 24 external channels

- Automated post-processing

- Automates math functions on input signals: averaging, filter calculations, oversampling and threshold comparison

- Operates in Sleep

- Two Comparators (COMP):

- Fixed Voltage Reference at (non) inverting input(s)

- Comparator outputs externally accessible

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

## **Flexible Oscillator Structure**

- High-Precision Internal Oscillator:

- Software selectable frequency range up to 32 MHz, ±1% typical

- x2/x4 PLL with Internal and External Sources

- Low-Power Internal 32 kHz Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- External Oscillator Block with:

- Three crystal/resonator modes up to 20 MHz

- Three external clock modes up to 20 MHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

- Oscillator Start-up Timer (OST)

- Ensures stability of crystal oscillator resources

## 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit 7 if a label points to a location in the program memory.

## EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants  |             |         |          |   |

|------------|-------------|---------|----------|---|

| RETLW      | DATA0       | ;Ind    | ex0 data | 1 |

| RETLW      | DATA1       | ;Ind    | ex1 data | 1 |

| RETLW      | DATA2       |         |          |   |

| RETLW      | DATA3       |         |          |   |

| my_functi  | on          |         |          |   |

| ; LO       | IS OF CODE. |         |          |   |

| MOVLW      | LOW cons    | tants   |          |   |

| MOVWF      | FSR1L       |         |          |   |

| MOVLW      | HIGH con    | stants  |          |   |

| MOVWF      | FSR1H       |         |          |   |

| MOVIW      | 0[FSR1]     |         |          |   |

| ; THE PROG | RAM MEMORY  | IS IN W | V        |   |

|            |             |         |          |   |

## 3.2 Data Memory Organization

The data memory is partitioned into 32 memory banks with 128 bytes in each bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect **Addressing**" for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

## 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-10.

| TABLE 3-2: | CORE REGISTERS |

|------------|----------------|

|------------|----------------|

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

| IADLL   | ABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |        |        |            |               |                 |                   |             |         |                       |                              |  |  |

|---------|---------------------------------------------------------------------|--------|--------|------------|---------------|-----------------|-------------------|-------------|---------|-----------------------|------------------------------|--|--|

| Address | Name                                                                | Bit 7  | Bit 6  | Bit 5      | Bit 4         | Bit 3           | Bit 2             | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |  |  |

| Bank 1  |                                                                     |        | •      |            |               |                 | •                 |             |         |                       |                              |  |  |

|         |                                                                     |        |        | c          | PU CORE REGIS | TERS: see Table | 3-2 for specifics |             |         |                       |                              |  |  |

|         |                                                                     |        |        |            |               |                 |                   |             |         |                       |                              |  |  |

| 08Ch    | ADRESL                                                              |        |        |            | A             | DRESL<7:0>      |                   |             |         | 0000 0000             | 0000 0000                    |  |  |

| 08Dh    | ADRESH                                                              |        |        |            | А             | DRESH<7:0>      |                   |             |         | 0000 0000             | 0000 0000                    |  |  |

| 08Eh    | ADPREVL                                                             |        |        |            | A             | DPREVL<7:0>     |                   |             |         | 0000 0000             | 0000 0000                    |  |  |

| 08Fh    | ADPREVH                                                             |        |        |            | AI            | DPREVH<7:0>     |                   |             |         | 0000 0000             | 0000 0000                    |  |  |

| 090h    | ADACCL                                                              |        |        |            | xxxx xxxx     | uuuu uuuu       |                   |             |         |                       |                              |  |  |

| 091h    | ADACCH                                                              |        |        |            | xxxx xxxx     | uuuu uuuu       |                   |             |         |                       |                              |  |  |

| 092h    | _                                                                   |        |        |            | U             | nimplemented    |                   |             |         | -                     | —                            |  |  |

| 093h    | ADCON0                                                              | ADON   | ADCONT | _          | ADCS          | _               | ADFRM0            | —           | ADGO    | 00-0 -0-0             | 00-0 -0-0                    |  |  |

| 094h    | ADCON1                                                              | ADPPOL | ADIPEN | ADGPOL     | —             | _               | _                 | —           | ADDSEN  | 0000                  | 0000                         |  |  |

| 095h    | ADCON2                                                              | ADPSIS |        | ADCRS<2:0> | >             | ADACLR          |                   | ADMD<2:0>   | L       | 0000 0000             | 0000 0000                    |  |  |

| 096h    | ADCON3                                                              | _      |        | ADCALC<2:0 | >             | ADSOI           |                   | ADTMD<2:0>  |         | -000 0000             | -000 0000                    |  |  |

| 097h    | ADSTAT                                                              | ADAOV  | ADUTHR | ADLTHR     | ADMATH        | _               |                   | ADSTAT<2:0> |         | 0000 -000             | 0000 -000                    |  |  |

| 098h    | ADCLK                                                               | _      | —      |            |               | ADO             | CCS<5:0>          |             |         | 00 0000               | 00 0000                      |  |  |

| 099h    | ADACT                                                               | _      | —      | _          |               |                 | ADACT<4:0>        |             |         | 0 0000                | 0 0000                       |  |  |

| 09Ah    | ADREF                                                               | _      | _      | _          | ADNREF        | _               | _                 | ADPRE       | EF<1:0> | 000                   | 000                          |  |  |

| 09Bh    | ADCAP                                                               | _      | —      | _          |               | •               | ADCAP<4:0>        | •           |         | 0 0000                | 0 0000                       |  |  |

| 09Ch    | ADPRE                                                               |        |        |            |               | ADPRE<7:0>      |                   |             |         | 0000 0000             | 0000 0000                    |  |  |

| 09Dh    | ADACQ                                                               |        |        |            | /             | ADACQ<7:0>      |                   |             |         | 0000 0000             | 0000 0000                    |  |  |

| 09Eh    | ADPCH                                                               | —      | —      |            |               | ADF             | PCH<5:0>          |             |         | 00 0000               | 00 0000                      |  |  |

| 09Fh    | —                                                                   |        |        |            | U             | nimplemented    |                   |             |         | -                     | _                            |  |  |

## TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18854 devices only.

2: Unimplemented, read as '1'.

| Address | Name    | Bit 7        | Bit 6         | Bit 5                 | Bit 4         | Bit 3           | Bit 2             | Bit 1    | Bit 0 | Value on:<br>POR, BOR | Value on all<br>other Resets |  |

|---------|---------|--------------|---------------|-----------------------|---------------|-----------------|-------------------|----------|-------|-----------------------|------------------------------|--|

| Bank 6  |         |              |               |                       |               |                 |                   |          |       |                       |                              |  |

|         |         |              |               | c                     | PU CORE REGIS | TERS; see Table | 3-2 for specifics |          |       |                       |                              |  |

| 30Ch    | CCPR1L  | Capture/Comp | are/PWM Regis | ster 1 (LSB)          |               |                 |                   |          |       | xxxx xxxx             | XXXX XXXX                    |  |

| 30Dh    | CCPR1H  | Capture/Comp | are/PWM Regis | ster 1 (MSB)          |               |                 |                   |          |       | xxxx xxxx             | XXXX XXXX                    |  |

| 30Eh    | CCP1CON | EN           | —             | OUT                   | FMT           |                 | MODE              | <3:0>    |       | 0-00 0000             | 0-00 0000                    |  |

| 30Fh    | CCP1CAP | _            | —             | —                     | —             | —               |                   | CTS<2:0> |       | 0000                  | 0000                         |  |

| 310h    | CCPR2L  | Capture/Comp | are/PWM Regis | /PWM Register 2 (LSB) |               |                 |                   |          |       |                       |                              |  |

| 311h    | CCPR2H  | Capture/Comp | are/PWM Regis | ster 2 (MSB)          |               |                 |                   |          |       | xxxx xxxx             | XXXX XXXX                    |  |

| 312h    | CCP2CON | EN           | —             | OUT                   | FMT           | MODE<3:0>       |                   |          |       | 0-00 0000             | 0-00 0000                    |  |

| 313h    | CCP2CAP | _            | —             | —                     | —             | —               |                   | CTS<2:0> |       | 0000                  | 0000                         |  |

| 314h    | CCPR3L  | Capture/Comp | are/PWM Regis | ster 3 (LSB)          |               |                 |                   |          |       | xxxx xxxx             | xxxx xxxx                    |  |

| 315h    | CCPR3H  | Capture/Comp | are/PWM Regis | ster 3 (MSB)          |               |                 |                   |          |       | xxxx xxxx             | xxxx xxxx                    |  |

| 316h    | CCP3CON | EN           | —             | OUT                   | FMT           |                 | MODE              | <3:0>    |       | 0-00 0000             | 0-00 0000                    |  |

| 317h    | CCP3CAP | —            | _             | —                     | _             |                 | CTS<              | 3:0>     |       | 0000                  | 0000                         |  |

| 318h    | CCPR4L  | Capture/Comp | are/PWM Regis | ster 4 (LSB)          |               |                 |                   |          |       | xxxx xxxx             | XXXX XXXX                    |  |

| 319h    | CCPR4H  | Capture/Comp | are/PWM Regis | ster 4 (MSB)          |               |                 |                   |          |       | xxxx xxxx             | xxxx xxxx                    |  |

| 31Ah    | CCP4CON | EN           | —             | OUT                   | FMT           |                 | MODE              | <3:0>    |       | 0-00 0000             | 0-00 0000                    |  |

| 31Bh    | CCP4CAP | —            | —             | -                     | _             |                 | CTS<              | 3:0>     |       | 0000                  | 0000                         |  |

| 31Ch    | CCPR5L  | Capture/Comp | are/PWM Regis | ster 5 (LSB)          |               |                 |                   |          |       | xxxx xxxx             | XXXX XXXX                    |  |

| 31Dh    | CCPR5H  | Capture/Comp | are/PWM Regis | ster 5 (MSB)          |               |                 |                   |          |       | xxxx xxxx             | XXXX XXXX                    |  |

| 31Eh    | CCP5CON | EN           | —             | OUT                   | FMT           | MODE<3:0>       |                   |          |       | 0-00 0000             | 0-00 0000                    |  |

| 31Fh    | CCP5CAP | _            |               | _                     | _             |                 | CTS<              | 3:0>     |       | 0000                  | 0000                         |  |

#### TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) 1

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend: Note 1:

Register present on PIC16F18854 devices only.

2: Unimplemented, read as '1'.

# PIC16(L)F18854

| R/W/HS-0/0                                                                                                                                                                             | R/W/HS-0/0                                                                                                              | U-0                                                                                     | U-0                                            | U-0             | U-0                                             | R/W/HS-0/0       | R/W/HS-0/0  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|-----------------|-------------------------------------------------|------------------|-------------|--|--|--|

| OSFIF                                                                                                                                                                                  | CSWIF                                                                                                                   | _                                                                                       | _                                              | _               | _                                               | ADTIF            | ADIF        |  |  |  |

| bit 7                                                                                                                                                                                  | 1                                                                                                                       |                                                                                         |                                                |                 |                                                 |                  | bit 0       |  |  |  |

|                                                                                                                                                                                        |                                                                                                                         |                                                                                         |                                                |                 |                                                 |                  |             |  |  |  |

| Legend:                                                                                                                                                                                |                                                                                                                         |                                                                                         |                                                |                 |                                                 |                  |             |  |  |  |

| R = Readabl                                                                                                                                                                            | e bit                                                                                                                   | W = Writable                                                                            | bit                                            | U = Unimpler    | nented bit, read                                | as '0'           |             |  |  |  |

| u = Bit is und                                                                                                                                                                         | hanged                                                                                                                  | x = Bit is unkn                                                                         | own                                            | -n/n = Value a  | at POR and BO                                   | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is se                                                                                                                                                                        | t                                                                                                                       | '0' = Bit is clea                                                                       | ared                                           | HS = Hardwa     | ire set                                         |                  |             |  |  |  |

| bit 7 <b>OSFIF</b> : Oscillator Fail-Safe Interrupt Flag bit<br>1 = Oscillator fail-safe interrupt has occurred (must be cleared in software)<br>0 = No oscillator fail-safe interrupt |                                                                                                                         |                                                                                         |                                                |                 |                                                 |                  |             |  |  |  |

| bit 6                                                                                                                                                                                  | CSWIF: Clock Switch Complete Interrupt Flag bit                                                                         |                                                                                         |                                                |                 |                                                 |                  |             |  |  |  |

|                                                                                                                                                                                        | 1 = The clock                                                                                                           |                                                                                         | indicates an                                   | interrupt condi | tion (must be cle<br>tion                       | eared in softwa  | ire)        |  |  |  |

| bit 5-2                                                                                                                                                                                | Unimplemen                                                                                                              | ted: Read as '                                                                          | )'                                             |                 |                                                 |                  |             |  |  |  |

| bit 1                                                                                                                                                                                  | 1 = An A/D m                                                                                                            | • •                                                                                     | as beyond the                                  | configured thr  | mpare Interrupt<br>eshold (must be<br>threshold | •                | tware)      |  |  |  |

| bit 0                                                                                                                                                                                  | 1 = An A/D co                                                                                                           | -to-Digital Conv<br>onversion or co<br>onversion or co                                  | mplex operati                                  | on has comple   | ted (must be cle                                | eared in softwa  | ire)        |  |  |  |

| cc<br>its<br>U<br>aj                                                                                                                                                                   | terrupt flag bits a<br>ondition occurs, r<br>s corresponding<br>nable bit, GIE, c<br>ser software<br>opropriate interre | egardless of the<br>enable bit or th<br>of the INTCON<br>should ensu<br>upt flag bits a | e state of<br>e Global<br>register.<br>ire the |                 |                                                 |                  |             |  |  |  |

## REGISTER 7-12: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

prior to enabling an interrupt.

| R/W/HS-0/0       | R/W/HS-0/0                                                                                                                                         | R/W/HS-0/0                                                                                                                                         | R/W/HS-0/0     | U-0              | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------------------|-------------|--|--|--|--|

| CLC4IF           | CLC3IF                                                                                                                                             | CLC2IF                                                                                                                                             | CLC1IF         | _                | TMR5GIF          | TMR3GIF          | TMR1GIF     |  |  |  |  |

| bit 7            |                                                                                                                                                    |                                                                                                                                                    |                |                  |                  |                  | bit (       |  |  |  |  |

| Legend:          |                                                                                                                                                    |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| R = Readable     | e bit                                                                                                                                              | W = Writable                                                                                                                                       | bit            | U = Unimpler     | mented bit, read | 1 as '0'         |             |  |  |  |  |

| u = Bit is uncł  | nanged                                                                                                                                             | x = Bit is unkr                                                                                                                                    | nown           | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set | -                                                                                                                                                  | '0' = Bit is clea                                                                                                                                  | ared           | HS = Hardwa      | are set          |                  |             |  |  |  |  |

|                  |                                                                                                                                                    |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| bit 7            | CLC4IF: CLC4 Interrupt Flag bit                                                                                                                    |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  |                                                                                                                                                    | <ul> <li>1 = A CLC4OUT interrupt condition has occurred (must be cleared in software)</li> <li>0 = No CLC4 interrupt event has occurred</li> </ul> |                |                  |                  |                  |             |  |  |  |  |

|                  |                                                                                                                                                    | •                                                                                                                                                  |                | 1                |                  |                  |             |  |  |  |  |

| bit 6            | <b>CLC3IF:</b> CLC3 Interrupt Flag bit                                                                                                             |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  |                                                                                                                                                    | <ul> <li>1 = A CLC4OUT interrupt condition has occurred (must be cleared in software)</li> <li>0 = No CLC4 interrupt event has occurred</li> </ul> |                |                  |                  |                  |             |  |  |  |  |

| bit 5            |                                                                                                                                                    | CLC2IF: CLC2 Interrupt Flag bit                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  |                                                                                                                                                    | 1 = A CLC4OUT interrupt condition has occurred (must be cleared in software)                                                                       |                |                  |                  |                  |             |  |  |  |  |

|                  | 0 = No CLC4 interrupt event has occurred                                                                                                           |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| bit 4            | CLC1IF: CLC1 Interrupt Flag bit                                                                                                                    |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  | <ul> <li>1 = A CLC4OUT interrupt condition has occurred (must be cleared in software)</li> <li>0 = No CLC4 interrupt event has occurred</li> </ul> |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  |                                                                                                                                                    |                                                                                                                                                    |                | 1                |                  |                  |             |  |  |  |  |

| bit 3            | -                                                                                                                                                  | ited: Read as '                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| bit 2            | TMR5GIF: Timer5 Gate Interrupt Flag bit                                                                                                            |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  | <ol> <li>The Timer5 Gate has gone inactive (the gate is closed)</li> <li>The Timer5 Gate has not gone inactive</li> </ol>                          |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| bit 1            | TMR3GIF: Timer3 Gate Interrupt Flag bit                                                                                                            |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  |                                                                                                                                                    | er5 Gate has go                                                                                                                                    |                | ne gate is close | ed)              |                  |             |  |  |  |  |

|                  | 0 = The Time                                                                                                                                       | er5 Gate has no                                                                                                                                    | t gone inactiv | e                |                  |                  |             |  |  |  |  |

| bit 0            | TMR1GIF: Timer1 Gate Interrupt Flag bit                                                                                                            |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  | <ul> <li>1 = The Timer1 Gate has gone inactive (the gate is closed)</li> <li>0 = The Timer1 Gate has not gone inactive</li> </ul>                  |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

|                  | 0 = The Time                                                                                                                                       | r'i Gate nas no                                                                                                                                    | t gone inactiv | e                |                  |                  |             |  |  |  |  |

| Note: Int        | errupt flag bits a                                                                                                                                 | are set when an                                                                                                                                    | interrunt      |                  |                  |                  |             |  |  |  |  |

|                  | ndition occurs, r                                                                                                                                  |                                                                                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| its              | corresponding                                                                                                                                      | enable bit or th                                                                                                                                   | e Global       |                  |                  |                  |             |  |  |  |  |

| En               | able bit, GIE, c                                                                                                                                   | of the INTCON                                                                                                                                      | register.      |                  |                  |                  |             |  |  |  |  |

## REGISTER 7-16: PIR5: PERIPHERAL INTERRUPT REQUEST REGISTER 5

User software should ensure the appropriate interrupt flag bits are clear

prior to enabling an interrupt.

## REGISTER 11-3: CRCDATH: CRC DATA HIGH BYTE REGISTER

| R/W-xx               | R/W-x/x | R/W-x/x              | R/W-x/x                                                 | R/W-x/x        | R/W-x/x              | R/W-x/x | R/W-x/x |  |

|----------------------|---------|----------------------|---------------------------------------------------------|----------------|----------------------|---------|---------|--|

|                      |         |                      | DAT<                                                    | 15:8>          |                      |         |         |  |

| bit 7                |         |                      |                                                         |                |                      |         | bit 0   |  |

|                      |         |                      |                                                         |                |                      |         |         |  |

| Legend:              |         |                      |                                                         |                |                      |         |         |  |

| R = Readable bit     |         | W = Writable bit     |                                                         | U = Unimplemer | nted bit, read as '0 |         |         |  |

| u = Bit is unchanged |         | x = Bit is unknown   | n -n/n = Value at POR and BOR/Value at all other Resets |                |                      |         |         |  |

| '1' = Bit is set     |         | '0' = Bit is cleared |                                                         |                |                      |         |         |  |

bit 7-0 DAT<15:8>: CRC Input/Output Data bits

## REGISTER 11-4: CRCDATL: CRC DATA LOW BYTE REGISTER

| R/W-xx               | R/W-x/x | R/W-x/x              | R/W-x/x                                               | R/W-x/x        | R/W-x/x              | R/W-x/x | R/W-x/x |  |

|----------------------|---------|----------------------|-------------------------------------------------------|----------------|----------------------|---------|---------|--|

|                      |         |                      | DAT                                                   | <7:0>          |                      |         |         |  |

| bit 7                |         |                      |                                                       |                |                      |         | bit 0   |  |

|                      |         |                      |                                                       |                |                      |         |         |  |

| Legend:              |         |                      |                                                       |                |                      |         |         |  |

| R = Readable bit     |         | W = Writable bit     |                                                       | U = Unimplemer | nted bit, read as '0 | ,       |         |  |

| u = Bit is unchanged |         | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |                |                      |         |         |  |

| '1' = Bit is set     |         | '0' = Bit is cleared |                                                       |                |                      |         |         |  |

bit 7-0 DAT<7:0>

**DAT<7:0>**: CRC Input/Output Data bits Writing to this register fills the shifter.

## REGISTER 11-5: CRCACCH: CRC ACCUMULATOR HIGH BYTE REGISTER

| R/W-0/0            | R/W-0/0 | R/W-0/0              | R/W-0/0                                                 | R/W-0/0       | R/W-0/0              | R/W-0/0 | R/W-0/0 |  |  |  |  |

|--------------------|---------|----------------------|---------------------------------------------------------|---------------|----------------------|---------|---------|--|--|--|--|

| ACC<15:8>          |         |                      |                                                         |               |                      |         |         |  |  |  |  |

| bit 7              |         |                      |                                                         |               |                      |         | bit 0   |  |  |  |  |

|                    |         |                      |                                                         |               |                      |         |         |  |  |  |  |

| Legend:            |         |                      |                                                         |               |                      |         |         |  |  |  |  |

| R = Readable bit   |         | W = Writable bit     |                                                         | U = Unimpleme | nted bit, read as '0 | ,       |         |  |  |  |  |

| u = Bit is unchang | jed     | x = Bit is unknown   | n -n/n = Value at POR and BOR/Value at all other Resets |               |                      |         |         |  |  |  |  |

| '1' = Bit is set   |         | '0' = Bit is cleared |                                                         |               |                      |         |         |  |  |  |  |

bit 7-0 ACC<15:8>: CRC Accumulator Register bits

Writing to this register writes to the CRC accumulator register. Reading from this register reads the CRC accumulator.

## REGISTER 11-6: CRCACCL: CRC ACCUMULATOR LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|---------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|--|

|         | ACC<7:0>    |         |         |         |         |         |         |  |  |  |  |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ACC<7:0>: CRC Accumulator Register bits

Writing to this register writes to the CRC accumulator register through the CRC write bus. Reading from this register reads the CRC accumulator.

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0             | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|--------------------|---------|---------------------|------------------|------------------|-------------|

|                  |         |                    | LADR<   | 15:8>( <b>1,2</b> ) |                  |                  |             |

| bit 7            |         |                    |         |                     |                  |                  | bit 0       |

|                  |         |                    |         |                     |                  |                  |             |

| Legend:          |         |                    |         |                     |                  |                  |             |

| R = Readable     | bit     | W = Writable       | bit     | U = Unimpler        | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unknown |         | -n/n = Value a      | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                     |                  |                  |             |

## REGISTER 11-12: SCANLADRH: SCAN LOW ADDRESS HIGH BYTE REGISTER

bit 7-0 LADR<15:8>: Scan Start/Current Address bits<sup>(1,2)</sup> Most Significant bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- **2:** While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 11-13: SCANLADRL: SCAN LOW ADDRESS LOW BYTE REGISTER

| R/W-0/0                    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------------------------|---------|---------|---------|---------|---------|---------|---------|

| LADR<7:0> <sup>(1,2)</sup> |         |         |         |         |         |         |         |

| bit 7                      |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LADR<7:0>: Scan Start/Current Address bits<sup>(1,2)</sup> Least Significant bits of the current address to be fetched from, value increments on each fetch of memory

- **Note 1:** Registers SCANLADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 12-25: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | ANSC<7:0>: Analog Select between Analog or Digital Function on Pins RC<7:0>, respectively <sup>(1)</sup> |

|---------|----------------------------------------------------------------------------------------------------------|

|         | 0 = Digital I/O. Pin is assigned to port or digital special function.                                    |

|         | 1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled.        |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 12-26: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

- 1 = Pull-up enabled

- 0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

## 18.12 Register Definitions: Comparator Control

## REGISTER 18-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0          | R-0/0                                                                                                                                                                              | U-0              | R/W-0/0                        | U-0             | U-0             | R/W-0/0           | R/W-0/0       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|-----------------|-----------------|-------------------|---------------|

| ON               | OUT                                                                                                                                                                                | _                | POL                            | _               | —               | HYS               | SYNC          |

| bit 7            |                                                                                                                                                                                    |                  |                                |                 |                 | ·                 | bit 0         |

|                  |                                                                                                                                                                                    |                  |                                |                 |                 |                   |               |

| Legend:          |                                                                                                                                                                                    |                  |                                |                 |                 |                   |               |

| R = Readable     | bit                                                                                                                                                                                | W = Writable     | bit                            | U = Unimpler    | mented bit, rea | d as '0'          |               |

| u = Bit is unch  | anged                                                                                                                                                                              | x = Bit is unki  | nown                           | -n/n = Value a  | at POR and BO   | OR/Value at all o | other Resets  |

| '1' = Bit is set |                                                                                                                                                                                    | '0' = Bit is cle | ared                           |                 |                 |                   |               |

| bit 7            | 1 = Comparat                                                                                                                                                                       |                  | and consumes                   | s no active pow | er              |                   |               |

| bit 6            | <b>OUT:</b> Comparator Output bit<br>$\frac{If CxPOL = 1 (inverted polarity):}{1 = CxVP < CxVN}$ $0 = CxVP > CxVN$ $\frac{If CxPOL = 0 (non-inverted polarity):}{1 = CxVP > CxVN}$ |                  |                                |                 |                 |                   |               |

|                  | 0 = CxVP < 0                                                                                                                                                                       |                  |                                |                 |                 |                   |               |

| bit 5            | Unimplemented: Read as '0'                                                                                                                                                         |                  |                                |                 |                 |                   |               |

| bit 4            | <ul> <li>POL: Comparator Output Polarity Select bit</li> <li>1 = Comparator output is inverted</li> <li>0 = Comparator output is not inverted</li> </ul>                           |                  |                                |                 |                 |                   |               |

| bit 3-2          | •                                                                                                                                                                                  | ted: Read as '   |                                |                 |                 |                   |               |

| bit 1            | <ul> <li>HYS: Comparator Hysteresis Enable bit</li> <li>1 = Comparator hysteresis enabled</li> <li>0 = Comparator hysteresis disabled</li> </ul>                                   |                  |                                |                 |                 |                   |               |

| bit 0            | 1 = Compara<br>Output u                                                                                                                                                            | pdated on the    | Fimer1 and I/C falling edge of |                 | ource.          | ges on Timer1     | clock source. |

## 22.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 32 input signals and, through the use of configurable gates, reduces the 32 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

The CLC modules available are shown in Table 22-1.

TABLE 22-1: AVAILABLE CLC MODULES

| Device         | CLC1 | CLC2 | CLC3 | CLC4 |

|----------------|------|------|------|------|

| PIC16(L)F18854 | •    | •    | •    | •    |

| Note: | The CLC1, CLC2, CLC3 and CLC4 are            |

|-------|----------------------------------------------|

|       | four separate module instances of the        |

|       | same CLC module design. Throughout           |

|       | this section, the lower case 'x' in register |

|       | and bit names is a generic reference to      |

|       | the CLC number (which should be substi-      |

|       | tuted with 1, 2, 3, or 4 during code devel-  |

|       | opment). For example, the control register   |

|       | is generically described in this chapter as  |

|       | CLCxCON, but the actual device registers     |

|       | are CLC1CON, CLC2CON, CLC3CON                |

|       | and CLC4CON. Similarly, the LCxEN bit        |

|       | represents the LC1EN, LC2EN, LC3EN           |

|       | and LC4EN bits.                              |

Refer to Figure 22-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

Using the Auto-conversion Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. See Table 23-2 for auto-conversion sources.

| ADACT Value | Sour0x1Dce<br>Peripher0x1Dal | Description                                      |  |  |

|-------------|------------------------------|--------------------------------------------------|--|--|

| 0x00        | Disabled                     | External Trigger Disabled                        |  |  |

| 0x01        | ADACTPPS                     | Pin selected by ADACTPPS                         |  |  |

| 0x02        | TMR0                         | Timer0 overflow condition                        |  |  |

| 0x03        | TMR1                         | Timer1 overflow condition                        |  |  |

| 0x04        | TMR2                         | Match between Timer2<br>postscaled value and PR2 |  |  |

| 0x05        | TMR3                         | Timer3 overflow condition                        |  |  |

| 0x06        | TMR4                         | Match between Timer4 postscaled value and PR4    |  |  |

| 0x07        | TMR5                         | Timer5 overflow condition                        |  |  |

| 0x08        | TMR6                         | Match between Timer6<br>postscaled value and PR6 |  |  |

| 0x09        | SMT1                         | Match between SMT1 and SMT1PR                    |  |  |

| 0x0A        | SMT2                         | Match between SMT2 and SMT2PR                    |  |  |

| 0x0B        | CCP1                         | CCP1 output                                      |  |  |

| 0x0C        | CCP2                         | CCP2 output                                      |  |  |

| 0x0D        | CCP3                         | CCP3 output                                      |  |  |

| 0x0E        | CCP4                         | CCP4 output                                      |  |  |

| 0x0F        | CCP5                         | CCP5 output                                      |  |  |

| 0x10        | PWM6                         | PWM6 output                                      |  |  |

| 0x11        | PWM7                         | PWM7 output                                      |  |  |

| 0x12        | C1                           | Comparator C1 output                             |  |  |

| 0x13        | C2                           | Comparator C2 output                             |  |  |

| 0x14        | IOC                          | Interrupt-on-change interrupt trigger            |  |  |

| 0x15        | CLC1                         | CLC1 output                                      |  |  |

| 0x16        | CLC2                         | CLC2 output                                      |  |  |

| 0x17        | CLC3                         | CLC3 output                                      |  |  |

| 0x18        | CLC4                         | CLC4 output                                      |  |  |

| 0x19-0x1B   | Reserved                     | Reserved, do not use                             |  |  |

| 0x1C        | ADERR                        | Read of ADERR register                           |  |  |

| 0x1D        | ADRESH                       | Read of ADRESH register                          |  |  |

| 0x1E        | Reserved                     | Reserved, do not use                             |  |  |

| 0x1F        | ADPCH                        | Read of ADPCH register                           |  |  |

## TABLE 23-2: ADC AUTO-CONVERSION TABLE

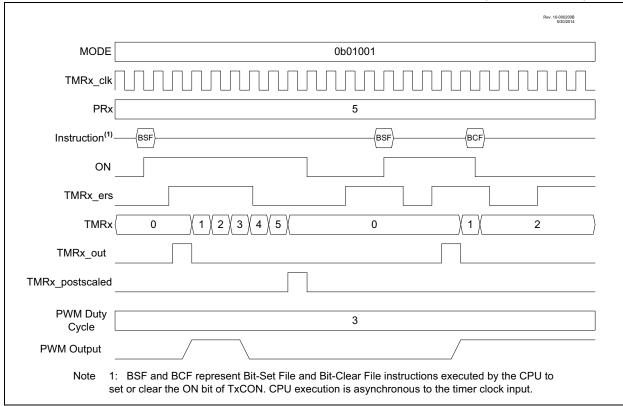

### 29.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 29-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

## FIGURE 29-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

## 29.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 29-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

## 31.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the  $PIC^{\mbox{\sc end}}$  microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 31.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

## 31.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

## 31.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note 1: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPDATPPS registers. The SCL input is selected with the SSPCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

## 31.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 31-1:I<sup>2</sup>C BUS TERMS

| TABLE 31-1.         |                                                                                                                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                           |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                         |

| Slave               | The device addressed by the master.                                                                                                                                                   |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                          |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                   |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                  |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                         |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                            |

| REGISTER 32-3: | SMTxSTAT: SMT STATUS REGISTER |

|----------------|-------------------------------|

|----------------|-------------------------------|

| R/W/HC-0/0                            | R/W/HC-0/0                                                                                               | R/W/HC-0/0                                                                       | U-0                                               | U-0             | R-0/0            | R-0/0            | R-0/0        |

|---------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------|-----------------|------------------|------------------|--------------|

| CPRUP                                 | CPWUP                                                                                                    | RST                                                                              | _                                                 | _               | TS               | WS               | AS           |

| bit 7                                 |                                                                                                          |                                                                                  |                                                   |                 |                  |                  | bit 0        |

|                                       |                                                                                                          |                                                                                  |                                                   |                 |                  |                  |              |

| Legend:                               |                                                                                                          |                                                                                  |                                                   |                 |                  |                  |              |