#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18854-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ρ          |

|------------|

| <b>C</b> 1 |

| 6          |

|            |

| )F1        |

| 88         |

| 354        |

#### Value on all Value on: Bit 7 Bit 6 Bit 5 Bit 4 Bit 2 Address Name Bit 3 Bit 1 Bit 0 POR, BOR other Resets Bank 8 CPU CORE REGISTERS; see Table 3-2 for specifics 40Ch SCANLADRL LADR<7:0> 0000 0000 0000 0000 SCANLADRH 40Dh LADR<15:8> 0000 0000 0000 0000 40Eh SCANHADRL HADR<7:0> 1111 1111 1111 1111 40Fh SCANHADRH HADR<15:8> 1111 1111 1111 1111 410h SCANCON0 ΕN SCANGO BUSY INVALID INTM MODE<1:0> 0000 0-00 0000 0-00 SCANTRIG 411h \_ TSEL<3:0> \_ \_ ---- 0000 ---- 0000 412h Unimplemented \_ \_ \_\_\_\_ 413h Unimplemented \_ \_ 414h Unimplemented \_ \_ \_\_\_\_ Unimplemented 415h \_ \_ \_ 416h CRCDATL DATA<7:0> XXXX XXXX XXXX XXXX 417h CRCDATH DATA<15:8> XXXX XXXX XXXX XXXX 418h CRCACCL ACC<7:0> 0000 0000 0000 0000 419h CRCACCH ACC<15:8> 0000 0000 0000 0000 41Ah CRCSHIFTL SHIFT<7:0> 0000 0000 0000 0000 41Bh CRCSHIFTH SHIFT<15:8> 0000 0000 0000 0000 41Ch CRCXORL X<7:1> xxxx xxxxxxx xxx-41Dh CRCXORH X<15:8> XXXX XXXX XXXX XXXX 41Eh CRCCON0 ΕN CRCGO BUSY ACCM SHIFTM FULL 0000 --00 0000 --00 \_ \_ 41Fh PLEN<3:0> CRCCON1 DLEN<3:0> 0000 0000 0000 0000

# TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Register present on PIC16F18854 devices only.

2: Unimplemented, read as '1'.

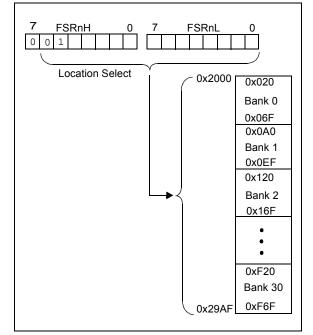

# 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

# 3.5.3 DATA EEPROM MEMORY

The EEPROM memory can be read or written through NVMCONx/NVMADRx/NVMDATx the register interface (see section Section 10.2 "Data EEPROM Memory"). However, to make access to the EEPROM memory easier, read-only access to the EEPROM contents are also available through indirect addressing by an FSR. When the MSB of the FSR (ex: FSRxH) is set to 0x70, the lower 8-bit address value (in FSRxL) determines the EEPROM location that may be read from (through the INDF register). In other words, the EEPROM address range 0x00-0xFF is mapped into the FSR address space between 0x7000-0x70FF. Writing to the EEPROM cannot be accomplished via the FSR/INDF interface. Reads from the EEPROM through the FSR/INDF interface will require one additional instruction cycle to complete.

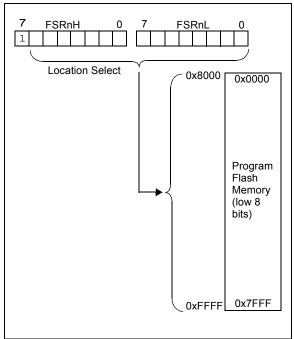

### 3.5.4 PROGRAM FLASH MEMORY

To make constant data access easier, the entire Program Flash Memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the Program Flash Memory cannot be accomplished via the FSR/INDF interface. All instructions that access Program Flash Memory via the FSR/INDF interface will require one additional instruction cycle to complete.

#### FIGURE 3-11: PROGRAM FLASH MEMORY MAP

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

# 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as shown in Table 4-1.

# TABLE 4-1:CONFIGURATION WORD<br/>LOCATIONS

| Configuration Word | Location |

|--------------------|----------|

| CONFIG1            | 8007h    |

| CONFIG2            | 8008h    |

| CONFIG3            | 8009h    |

| CONFIG4            | 800Ah    |

| CONFIG5            | 800Bh    |

| Note: | The DEBUG bit in Configuration Words is     |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

# 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

# 4.7 Register Definitions: Device and Revision

# REGISTER 4-6: DEVID: DEVICE ID REGISTER

|                         |     | R      | R   | R     | R      | R | R     |

|-------------------------|-----|--------|-----|-------|--------|---|-------|

|                         |     |        |     | DEV<  | :13:8> |   |       |

|                         |     | bit 13 |     |       |        |   | bit 8 |

|                         |     |        |     |       |        |   |       |

| R                       | R   | R      | R   | R     | R      | R | R     |

|                         |     |        | DEV | <7:0> |        |   |       |

| bit 7                   |     |        |     |       |        |   | bit 0 |

|                         |     |        |     |       |        |   |       |

| Legend:<br>R = Readable |     |        |     |       |        |   |       |

| R = Readable            | bit |        |     |       |        |   |       |

'1' = Bit is set

'0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device       | DEVID<13:0> Values                 |  |  |  |  |

|--------------|------------------------------------|--|--|--|--|

| PIC16F18854  | 11 0000 0110 1010 ( <b>306Ah</b> ) |  |  |  |  |

| PIC16LF18854 | 11 0000 0110 1011 ( <b>306Bh</b> ) |  |  |  |  |

#### REGISTER 4-7: REVISIONID: REVISION ID REGISTER

| R      | R | R | R           | R | R | R | R | R           | R | R | R | R | R     |

|--------|---|---|-------------|---|---|---|---|-------------|---|---|---|---|-------|

| 1      | 0 |   | MJRREV<5:0> |   |   |   |   | MNRREV<5:0> |   |   |   |   |       |

| bit 13 |   |   |             |   |   |   |   |             |   |   |   |   | bit 0 |

| Legend:              |                  |                    |  |

|----------------------|------------------|--------------------|--|

| R = Readable bit     |                  |                    |  |

| '0' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |  |

#### bit 13-12 Fixed Value: Read-only bits

These bits are fixed with value '10' for all devices included in this data sheet.

#### bit 11-6 MJRREV<5:0>: Major Revision ID bits

These bits are used to identify a major revision. A major revision is indicated by an all layer revision (B0, C0, etc.)

bit 5-0 **MNRREV<5:0>**: Minor Revision ID bits These bits are used to identify a minor revision.

| U-0          | U-0               | U-0                                    | R/W-0/0   | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|--------------|-------------------|----------------------------------------|-----------|----------------|------------------|------------------|--------------|

| _            | _                 |                                        | CCP5IE    | CCP4IE         | CCP3IE           | CCP2IE           | CCP1IE       |

| bit 7        |                   |                                        |           |                |                  |                  | bit          |

|              |                   |                                        |           |                |                  |                  |              |

| Legend:      |                   |                                        |           |                |                  |                  |              |

| R = Reada    | able bit          | W = Writable                           | bit       | U = Unimplen   | nented bit, read | as '0'           |              |

| u = Bit is u | nchanged          | x = Bit is unk                         | nown      | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is | set               | '0' = Bit is cle                       | ared      | HS = Hardwa    | re set           |                  |              |

|              |                   |                                        |           |                |                  |                  |              |

| bit 7-5      | Unimpleme         | nted: Read as                          | 0'.       |                |                  |                  |              |

| bit 4        |                   | CP5 Interrupt Er                       |           |                |                  |                  |              |

|              |                   | interrupt is enal                      |           |                |                  |                  |              |

|              |                   | interrupt is disa                      |           |                |                  |                  |              |

| bit 3        |                   | CP4 Interrupt Er                       |           |                |                  |                  |              |

|              |                   | interrupt is enal                      |           |                |                  |                  |              |

| 1.1.0        |                   | interrupt is disa                      |           |                |                  |                  |              |

| bit 2        |                   | CP3 Interrupt Er                       |           |                |                  |                  |              |

|              |                   | interrupt is enal<br>interrupt is disa |           |                |                  |                  |              |

| bit 1        |                   | CP2 Interrupt Er                       |           |                |                  |                  |              |

|              |                   | interrupt is enal                      |           |                |                  |                  |              |

|              |                   | interrupt is disa                      |           |                |                  |                  |              |

| bit 0        |                   | CP1 Interrupt Er                       |           |                |                  |                  |              |

|              |                   | interrupt is enal                      |           |                |                  |                  |              |

|              |                   | interrupt is disal                     |           |                |                  |                  |              |

|              |                   | -                                      |           |                |                  |                  |              |

| Note:        | Bit PEIE of the I | NTCON register                         | r must be |                |                  |                  |              |

|              | set to enable     |                                        |           |                |                  |                  |              |

|              | controlled by reg | isters PIE1_PIE                        | R         |                |                  |                  |              |

# REGISTER 7-8: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

| REGISTER 7        |                                                 |                                      |                  |                    |                                        |            | DAN/110 0/0 |

|-------------------|-------------------------------------------------|--------------------------------------|------------------|--------------------|----------------------------------------|------------|-------------|

| U-0               | U-0                                             | U-0                                  | R/W/HS-0/0       | R/W/HS-0/0         | R/W/HS-0/0                             | R/W/HS-0/0 | R/W/HS-0/0  |

| _                 | _                                               | —                                    | CCP5IF           | CCP4IF             | CCP3IF                                 | CCP2IF     | CCP1IF      |

| bit 7             |                                                 |                                      |                  |                    |                                        |            | bit 0       |

| Legend:           |                                                 |                                      |                  |                    |                                        |            |             |

| R = Readable bi   | it                                              | W = Writable bi                      | it               | U = Unimplem       | ented bit, read as                     | '0'        |             |

| u = Bit is unchar |                                                 | x = Bit is unkno                     |                  | •                  | POR and BOR/V                          |            | Resets      |

| 1' = Bit is set   | .900                                            | '0' = Bit is clear                   |                  | HS = Hardware      |                                        |            |             |

|                   |                                                 |                                      |                  |                    |                                        |            |             |

| bit 7-5           | Unimplemente                                    | d: Read as '0'                       |                  |                    |                                        |            |             |

| bit 4             | CCP5IF: CCP5                                    | Interrupt Flag bi                    | it               |                    |                                        |            |             |

|                   | <u>CCP5IF = 1</u> :                             |                                      | .,               |                    |                                        |            |             |

|                   |                                                 | Capture occurre<br>Compare matc      |                  |                    |                                        |            |             |

|                   |                                                 | utput trailing edg                   |                  |                    |                                        |            |             |

|                   | CCP5IF = 0:                                     |                                      | ,                |                    | ,                                      |            |             |

|                   |                                                 | Capture did not                      |                  |                    |                                        |            |             |

|                   |                                                 | : Compare matc<br>utput trailing edg |                  |                    |                                        |            |             |

| bit 3             |                                                 | Interrupt Flag bi                    |                  |                    |                                        |            |             |

|                   | CCP4IF = 1:                                     | interrupti log 2                     |                  |                    |                                        |            |             |

|                   | •                                               | Capture occurre                      | •                | ,                  |                                        |            |             |

|                   |                                                 | : Compare matc<br>utput trailing edg |                  |                    |                                        |            |             |

|                   | CCP4IF = 0:                                     | itput training eug                   |                  |                    | soltware)                              |            |             |

|                   |                                                 | Capture did not                      | occur            |                    |                                        |            |             |

|                   |                                                 | : Compare matc                       |                  |                    |                                        |            |             |

| h# 0              |                                                 | utput trailing edg                   |                  |                    |                                        |            |             |

| bit 2             | CCP3IF: CCP3<br>CCP3IF = 1:                     | Interrupt Flag bi                    | IL               |                    |                                        |            |             |

|                   |                                                 | Capture occurre                      | d (must be clea  | red in software)   |                                        |            |             |

|                   | •                                               | : Compare matc                       | · ·              |                    | ,                                      |            |             |

|                   | CCP3IF = 0:                                     | utput trailing edg                   | e occurred (mus  | st be cleared in s | software)                              |            |             |

|                   |                                                 | Capture did not                      | occur            |                    |                                        |            |             |

|                   |                                                 | : Compare matc                       |                  |                    |                                        |            |             |

|                   | PWM mode: Ou                                    | utput trailing edg                   | e did not occur  |                    |                                        |            |             |

| bit 1             |                                                 | Interrupt Flag bi                    | it               |                    |                                        |            |             |

|                   | $\frac{\text{CCP2IF} = 1}{\text{Capture mode}}$ | Capture occurre                      | d (must be clear | red in software)   |                                        |            |             |

|                   |                                                 | : Compare matc                       |                  |                    |                                        |            |             |

|                   |                                                 | utput trailing edg                   | e occurred (mus  | st be cleared in s | software)                              |            |             |

|                   | $\frac{\text{CCP2IF} = 0}{\text{CCP2IF} = 0}$   |                                      |                  |                    |                                        |            |             |

|                   |                                                 | Capture did not<br>Compare matc      |                  |                    |                                        |            |             |

|                   |                                                 | utput trailing edg                   |                  |                    |                                        |            |             |

| bit 0             | CCP1IF: CCP1                                    | Interrupt Flag bi                    | it               |                    |                                        |            |             |

|                   | CCP1IF = 1:                                     |                                      |                  |                    |                                        |            |             |

|                   |                                                 | Capture occurre                      |                  |                    |                                        |            |             |

|                   | •                                               | : Compare matc<br>utput trailing edg | •                |                    | ,                                      |            |             |

|                   | <u>CCP1IF = 0</u> :                             |                                      |                  |                    | ······································ |            |             |

|                   | Capture mode:                                   | Capture did not                      |                  |                    |                                        |            |             |

|                   | Compare mode                                    | · Comparo mate                       | h did not occur  |                    |                                        |            |             |

|                   |                                                 | utput trailing edg                   |                  |                    |                                        |            |             |

# REGISTER 7-18: PIR6: PERIPHERAL INTERRUPT REQUEST REGISTER 6

# 12.6 PORTB Registers

#### 12.6.1 DATA REGISTER

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-13). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 12.4.9 shows how to initialize PORTB.

Reading the PORTB register (Register 12-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The PORT data latch LATB (Register 12-14) holds the output port data, and contains the latest value of a LATB or PORTB write.

# EXAMPLE 12-2: INITIALIZING PORTA

| ; initia                                               | ports are in                                       | illustrates<br>ORTA register. The<br>itialized in the same                                                             |

|--------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| BANKSEL<br>CLRF<br>BANKSEL<br>CLRF<br>BANKSEL<br>MOVLW | PORTA<br>LATA<br>LATA<br>ANSELA<br>ANSELA<br>TRISA | ;<br>;Init PORTA<br>;Data Latch<br>;<br>;digital I/O<br>;<br>;Set RA<5:3> as inputs<br>;and set RA<2:0> as<br>;outputs |

# 12.6.2 DIRECTION CONTROL

The TRISB register (Register 12-13) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 12.6.3 OPEN-DRAIN CONTROL

The ODCONB register (Register 12-17) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

# 12.6.4 SLEW RATE CONTROL

The SLRCONB register (Register 12-18) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# PIC16(L)F18854

# REGISTER 12-30: CCDPC: CURRENT CONTROLLED DRIVE POSITIVE PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCDPC7  | CCDPC6  | CCDPC5  | CCDPC4  | CCDPC3  | CCDPC2  | CCDPC1  | CCDPC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

CCDPC<7:0>: RC<7:0> Current Controlled Drive Positive Control bits<sup>(1)</sup>

- 1 = Current-controlled source enabled

- 0 = Current-controlled source disabled

**Note 1:** If CCDPCy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

# REGISTER 12-31: CCDNC: CURRENT CONTROLLED DRIVE NEGATIVE PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCDNC7  | CCDNC6  | CCDNC5  | CCDNC4  | CCDNC3  | CCDNC2  | CCDNC1  | CCDNC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

CCDNC<7:0>: RC<7:0> Current Controlled Drive Negative Control bits<sup>(1)</sup>

- 1 = Current-controlled source enabled

- 0 = Current-controlled source disabled

**Note 1:** If CCDNCy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

| Input Signal<br>Name |                     | Default<br>Location | Remappable to Pins of PORTx<br>PIC16F18854 |       |       |  |  |

|----------------------|---------------------|---------------------|--------------------------------------------|-------|-------|--|--|

|                      | Input Register Name |                     |                                            |       |       |  |  |

|                      |                     | at POR              | PORTA                                      | PORTB | PORTC |  |  |

| CLCIN3               | CLCIN3PPS           | RB7                 |                                            | •     | •     |  |  |

| ADCACT               | ADCACTPPS           | RB4                 |                                            | •     | •     |  |  |

| SCK1/SCL1            | SSP1CLKPPS          | RC3                 |                                            | •     | •     |  |  |

| SDI1/SDA1            | SSP1DATPPS          | RC4                 |                                            | •     | •     |  |  |

| SS1                  | SSPSS1PPS           | RA5                 | •                                          |       | •     |  |  |

| SCK2/SCL2            | SSP2CLKPPS          | RB1                 |                                            | •     | •     |  |  |

| SDI2/SDA2            | SSP2DATPPS          | RB2                 |                                            | •     | •     |  |  |

| SS2                  | SSP2SSPPS           | RB0                 |                                            | •     | •     |  |  |

| RX/DT                | RXPPS               | RC7                 |                                            | •     | •     |  |  |

| СК                   | TXPPS               | RC6                 |                                            | •     | •     |  |  |

# TABLE 13-1: PPS INPUT SIGNAL ROUTING OPTIONS (CONTINUED)

| PPSLOCK<br>INTPPS<br>T0CKIPPS<br>T1CKIPPS<br>T1GPPS<br>T3CKIPPS |   | - | —                 | _                 |    |            |            |           |            |  |

|-----------------------------------------------------------------|---|---|-------------------|-------------------|----|------------|------------|-----------|------------|--|

| T0CKIPPS<br>T1CKIPPS<br>T1GPPS                                  | _ | _ |                   |                   | —  | —          | _          | PPSLOCKED | 215        |  |

| T1CKIPPS<br>T1GPPS                                              | _ |   | -                 | —                 |    | INT        | PPS<3:0>   | •         | 214        |  |

| T1GPPS                                                          |   | _ | _                 | —                 |    | TOCK       | (IPPS<3:0> |           | 214        |  |

|                                                                 | — | _ | _                 |                   |    | T1CKIPPS<  | 4:0>       |           | 214        |  |

| T3CKIPPS                                                        | _ | - | _                 |                   |    | T1GPPS<4   | :0>        |           | 214        |  |

|                                                                 | _ | _ | _                 | – T3CKIPPS<4:0>   |    |            |            |           |            |  |

| T3GPPS                                                          | _ | _ | _                 | — T3GPPS<4:0>     |    |            |            |           |            |  |

| T5CKIPPS                                                        | _ | - | _                 | — T5CKIPPS<4:0>   |    |            |            |           |            |  |

| T5GPPS                                                          | _ | - | _                 | 750770.40         |    |            |            |           |            |  |

| T5GPPS                                                          | _ | _ | _                 |                   |    | T5GPPS<4   | :0>        |           | 214        |  |

| T2AINPPS                                                        |   |   |                   |                   |    | T2AINPPS<  | 4:0>       |           | 214        |  |

| T4AINPPS                                                        |   |   |                   |                   |    | T5AINPPS<  | 4:0>       |           | 214        |  |

| T6AINPPS                                                        |   |   |                   |                   |    | T6AINPPS<  | 4:0>       |           | 214        |  |

| CCP1PPS                                                         | _ | _ | _                 |                   |    | CCP1PPS<   | 4:0>       |           | 214        |  |

| CCP2PPS                                                         | _ | — | _                 |                   |    | CCP2PPS<   | 4:0>       |           | 214        |  |

| CCP3PPS                                                         | _ | _ | _                 |                   |    | CCP3PPS<   | 4:0>       |           | 214        |  |

| CCP4PPS                                                         | _ | _ | _                 |                   |    | CCP4PPS<   | 4:0>       |           | 214        |  |

| CCP5PPS                                                         | _ | _ | _                 |                   |    | CCP5PPS<   | 4:0>       |           | 214        |  |

| CWG1PPS                                                         | _ | _ | _                 |                   |    | CWG1PPS<   | 4:0>       |           | 214        |  |

| CWG2PPS                                                         | _ | _ | _                 | - CWG2PPS<4:0>    |    |            |            |           |            |  |

| CWG3PPS                                                         | _ | _ | _                 |                   |    |            |            |           |            |  |

| MDCARLPPS                                                       | _ | _ | _                 |                   |    |            |            |           |            |  |

| MDCARHPPS                                                       | _ | _ | _                 | - MDCARHPPS<4:0>  |    |            |            |           |            |  |

| MDSRCPPS                                                        | _ | _ | _                 | - MDSRCPPS<4:0>   |    |            |            |           |            |  |

| SSP1CLKPPS                                                      | _ | _ | _                 | - SSP1CLKPPS<4:0> |    |            |            |           |            |  |

| SSP1DATPPS                                                      | _ | _ | _                 |                   |    | SSP1DATPPS | S<4:0>     |           | 214        |  |

| SSP1SSPPS                                                       | _ | _ | _                 |                   |    | SSP1SSPPS  | <4:0>      |           | 214        |  |

| SSP2CLKPPS                                                      | _ | _ | _                 |                   |    | SSP2CLKPPS | 6<4:0>     |           | 214        |  |

| SSP2DATPPS                                                      | _ | _ | _                 | - SSP2DATPPS<4:0> |    |            |            |           |            |  |

| SSP2SSPPS                                                       | _ | _ | _                 |                   |    |            |            |           |            |  |

| RXPPS                                                           | _ | _ | _                 | - RXPPS<4:0>      |    |            |            |           |            |  |

| TXPPS                                                           | _ | _ | _                 | - TXPPS<4:0>      |    |            |            |           |            |  |

| CLCIN0PPS                                                       | _ | _ | _                 |                   |    | CLCIN0PPS  | <4:0>      |           | 214        |  |

| CLCIN1PPS                                                       | _ | _ | _                 |                   |    |            |            |           |            |  |

| CLCIN2PPS                                                       | _ | _ | _                 | - CLCIN2PPS<4:0>  |    |            |            |           |            |  |

| CLCIN3PPS                                                       | _ | _ | _                 | - CLCIN3PPS<4:0>  |    |            |            |           |            |  |

| SMT1WINPPS                                                      | _ | _ | _                 | — SMT1WINPPS<4:0> |    |            |            |           |            |  |

| SMT1SIGPPS                                                      | _ | _ | _                 |                   |    |            |            |           |            |  |

| SMT2WINPPS                                                      | _ | _ | - SMT2WINPPS<4:0> |                   |    |            |            |           | 214<br>214 |  |

| SMT2SIGPPS                                                      | _ | _ | _                 |                   |    |            |            |           |            |  |

| ADCACTPPS                                                       | _ | _ | _                 | — ADCACTPPS<4:0>  |    |            |            |           |            |  |

| RA0PPS                                                          | _ | _ |                   | 1                 | RA | 0PPS<5:0>  |            |           | 215        |  |

| RA1PPS                                                          | _ | _ |                   |                   |    | 1PPS<5:0>  |            |           | 215        |  |

| RA2PPS                                                          | _ | _ |                   |                   |    | 2PPS<5:0>  |            |           | 215        |  |

| RA3PPS                                                          | _ | _ |                   |                   |    | 3PPS<5:0>  |            |           | 215        |  |

#### SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE **TABLE 13-4**:

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the PPS module. Note 1: PIC16F18875 only.

# 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-14 for more details.

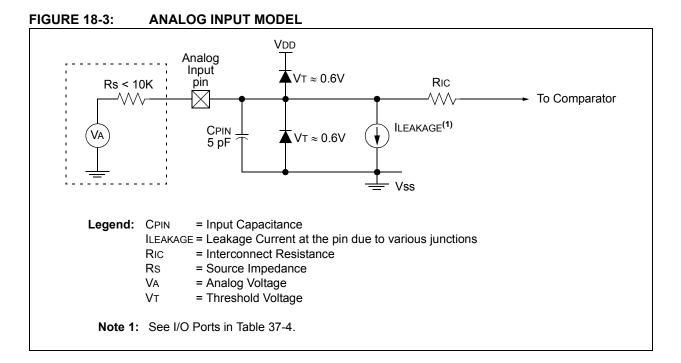

# 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

# 20.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWGxx pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWGxOCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWGxOCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWGxCON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 20.10 "Auto-Shutdown"**. An auto-shutdown event will only affect pins that have STRx = 1.

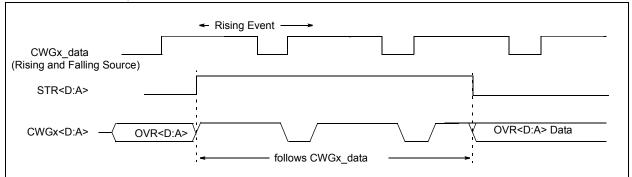

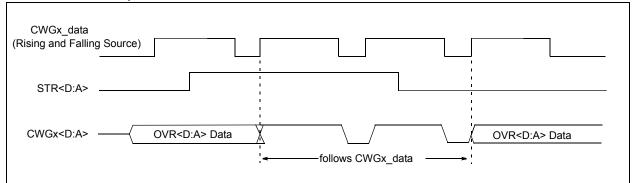

# 20.9.1 STEERING SYNCHRONIZATION

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

Figure 20-10 and Figure 20-11 illustrate the timing of asynchronous and synchronous steering, respectively.

FIGURE 20-10: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (MODE<2:0> = 000)

FIGURE 20-11: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (MODE<2:0> = 001)

# PIC16(L)F18854

| Name     | Bit 7    | Bit 6    | Bit 5       | Bit 4       | Bit 3    | Bit 2    | Bit 1        | Bit 0    | Register<br>on Page |

|----------|----------|----------|-------------|-------------|----------|----------|--------------|----------|---------------------|

| INTCON   | GIE      | PEIE     | —           | —           | —        | —        | —            | INTEDG   | 114                 |

| PIR5     | CLC4IF   | CLC3IF   | CLC2IF      | CLC1IF      | —        | TMR5GIF  | TMR3GIF      | TMR1GIF  | 129                 |

| PIE5     | CLC4IE   | CLC4IE   | CLC2IE      | CLC1IE      | —        | TMR5GIE  | TMR3GIE      | TMR1GIE  | 120                 |

| CLC1CON  | LC1EN    | _        | LC10UT      | LC1INTP     | LC1INTN  |          | LC1MODE<2:0  | >        | 292                 |

| CLC1POL  | LC1POL   | _        | _           | —           | LC1G4POL | LC1G3POL | LC1G2POL     | LC1G1POL | 293                 |

| CLC1SEL0 | _        | _        |             |             | LC1D     | 1S<5:0>  |              |          | 294                 |

| CLC1SEL1 | _        | _        |             |             | LC1D     | 2S<5:0>  |              |          | 294                 |

| CLC1SEL2 | _        | _        |             |             | LC1D     | 3S<5:0>  |              |          | 294                 |

| CLC1SEL3 | _        | _        |             |             | LC1D     | 4S<5:0>  |              |          | 294                 |

| CLC1GLS0 | LC1G1D4T | LC1G1D4N | LC1G1D3T    | LC1G1D3N    | LC1G1D2T | LC1G1D2N | LC1G1D1T     | LC1G1D1N | 295                 |

| CLC1GLS1 | LC1G2D4T | LC1G2D4N | LC1G2D3T    | LC1G2D3N    | LC1G2D2T | LC1G2D2N | LC1G2D1T     | LC1G2D1N | 296                 |

| CLC1GLS2 | LC1G3D4T | LC1G3D4N | LC1G3D3T    | LC1G3D3N    | LC1G3D2T | LC1G3D2N | LC1G3D1T     | LC1G3D1N | 297                 |

| CLC1GLS3 | LC1G4D4T | LC1G4D4N | LC1G4D3T    | LC1G4D3N    | LC1G4D2T | LC1G4D2N | LC1G4D1T     | LC1G4D1N | 298                 |

| CLC2CON  | LC2EN    | _        | LC2OUT      | LC2INTP     | LC2INTN  |          | LC2MODE<2:0  | >        | 292                 |

| CLC2POL  | LC2POL   | _        | _           | _           | LC2G4POL | LC2G3POL | LC2G2POL     | LC2G1POL | 293                 |

| CLC2SEL0 | _        | _        |             | LC2D1S<5:0> |          |          |              |          |                     |

| CLC2SEL1 | _        | _        |             | LC2D2S<5:0> |          |          |              |          |                     |

| CLC2SEL2 | _        | _        |             |             | LC2D     | 3S<5:0>  |              |          | 294                 |

| CLC2SEL3 | _        | _        |             |             | LC2D     | 4S<5:0>  |              |          | 294                 |

| CLC2GLS0 | LC2G1D4T | LC2G1D4N | LC2G1D3T    | LC2G1D3N    | LC2G1D2T | LC2G1D2N | LC2G1D1T     | LC2G1D1N | 295                 |

| CLC2GLS1 | LC2G2D4T | LC2G2D4N | LC2G2D3T    | LC2G2D3N    | LC2G2D2T | LC2G2D2N | LC2G2D1T     | LC2G2D1N | 296                 |

| CLC2GLS2 | LC2G3D4T | LC2G3D4N | LC2G3D3T    | LC2G3D3N    | LC2G3D2T | LC2G3D2N | LC2G3D1T     | LC2G3D1N | 297                 |

| CLC2GLS3 | LC2G4D4T | LC2G4D4N | LC2G4D3T    | LC2G4D3N    | LC2G4D2T | LC2G4D2N | LC2G4D1T     | LC2G4D1N | 298                 |

| CLC3CON  | LC3EN    | _        | LC3OUT      | LC3INTP     | LC3INTN  |          | LC3MODE<2:0  | >        | 292                 |

| CLC3POL  | LC3POL   | _        | _           | _           | LC3G4POL | LC3G3POL | LC3G2POL     | LC3G1POL | 293                 |

| CLC3SEL0 | _        | _        |             |             | LC3D     | 1S<5:0>  |              |          | 294                 |

| CLC3SEL1 | -        | _        |             |             | LC3D     | 2S<5:0>  |              |          | 294                 |

| CLC3SEL2 | -        | _        |             |             | LC3D     | 3S<5:0>  |              |          | 294                 |

| CLC3SEL3 | _        |          |             |             | LC3D     | 4S<5:0>  |              |          | 294                 |

| CLC3GLS0 | LC3G1D4T | LC3G1D4N | LC3G1D3T    | LC3G1D3N    | LC3G1D2T | LC3G1D2N | LC3G1D1T     | LC3G1D1N | 295                 |

| CLC3GLS1 | LC3G2D4T | LC3G2D4N | LC3G2D3T    | LC3G2D3N    | LC3G2D2T | LC3G2D2N | LC3G2D1T     | LC3G2D1N | 296                 |

| CLC3GLS2 | LC3G3D4T | LC3G3D4N | LC3G3D3T    | LC3G3D3N    | LC3G3D2T | LC3G3D2N | LC3G3D1T     | LC3G3D1N | 297                 |

| CLC3GLS3 | LC3G4D4T | LC3G4D4N | LC3G4D3T    | LC3G4D3N    | LC3G4D2T | LC3G4D2N | LC3G4D1T     | LC3G4D1N | 298                 |

| CLC4CON  | LC4EN    | _        | LC4OUT      | LC4INTP     | LC4INTN  |          | LC4MODE<2:0> | >        | 292                 |

| CLC4POL  | LC4POL   | _        | _           | _           | LC4G4POL | LC4G3POL | LC4G2POL     | LC4G1POL | 293                 |

| CLC4SEL0 | _        |          |             |             | LC4D     | 1S<5:0>  |              |          | 294                 |

| CLC4SEL1 | _        | _        | LC4D2S<5:0> |             |          |          |              | 294      |                     |

| CLC4SEL2 | _        | _        | LC4D3S<5:0> |             |          |          |              | 294      |                     |

| CLC4SEL3 | _        | _        | LC4D4S<5:0> |             |          |          |              | 294      |                     |

| CLC4GLS0 | LC4G1D4T | LC4G1D4N | LC4G1D3T    | LC4G1D3N    | LC4G1D2T | LC4G1D2N | LC4G1D1T     | LC4G1D1N | 295                 |

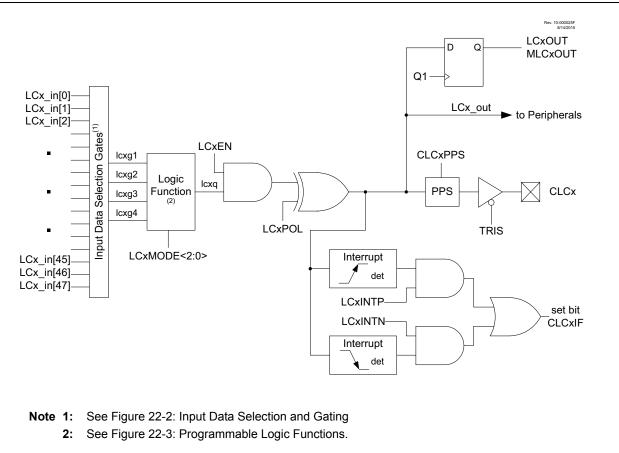

## TABLE 22-4: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

# 24.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

The Numerically Controlled Oscillator (NCO) module is a timer that uses overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter driven timer is that the output frequency resolution does not vary with the divider value. The NCO is most useful for application that requires frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCO include:

- 20-bit Increment Function

- Fixed Duty Cycle mode (FDC) mode

- Pulse Frequency (PF) mode

- Output Pulse Width Control

- Multiple Clock Input Sources

- Output Polarity Control

- Interrupt Capability

Figure 24-1 is a simplified block diagram of the NCO module.

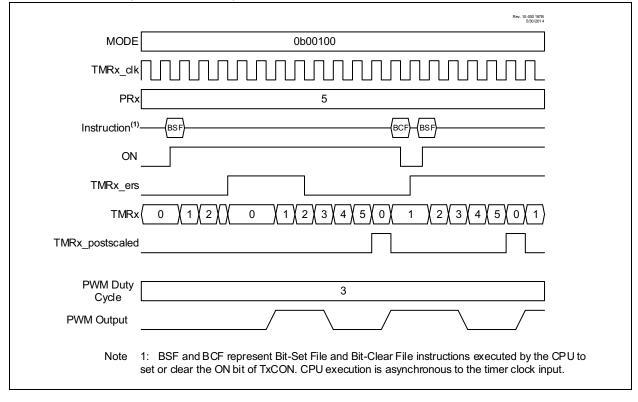

#### 29.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

## FIGURE 29-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 29-6.

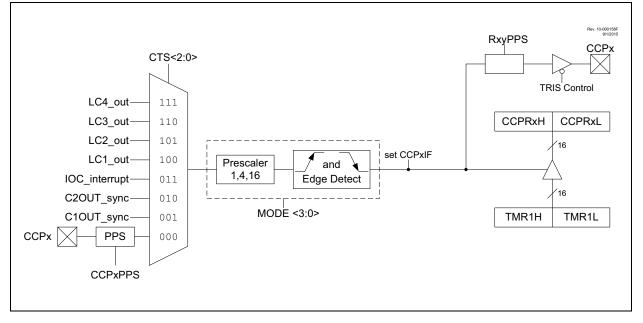

# 30.1 Capture Mode

The Capture mode function described in this section is available and identical for all CCP modules.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxMODE<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIR6 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value. Figure 30-1 shows a simplified diagram of the capture operation.

## 30.1.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCPx pin is configured as an output, |

|-------|---------------------------------------------|

|       | a write to the port can cause a capture     |

|       | condition.                                  |

The capture source is selected by configuring the CCPxCTS<2:0> bits of the CCPxCAP register. The following sources can be selected:

- CCPxPPS input

- C1OUT\_sync

- C2OUT\_sync

- IOC\_interrupt

- LC1\_out

- LC2\_out

- LC3\_out

- LC4\_out

# FIGURE 30-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

PIC16(L)F18854

DS40001826A-page 488

Preliminary

# 33.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUD1CON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TX1STA register and the BRG16 bit of the BAUD1CON register. In Synchronous mode, the BRGH bit is ignored.

Table 33-1 contains the formulas for determining the baud rate. Example 33-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 33-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

## EXAMPLE 33-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: Fosc Desired Baud Rate =  $\frac{1000}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL: Fosc  $X = \frac{Desired Baud Rate}{-1}$ 64 16000000  $\frac{9600}{64} - 1$ = [25.042] = 25 Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$ = 9615Error = Calc. Baud Rate – Desired Baud Rate Desired Baud Rate  $= \frac{(9615 - 9600)}{9600} = 0.16\%$

# PIC16(L)F18854