# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | PowerPC                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 66MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI, UART/USART                                 |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 64                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 2.7V                                                           |

| Data Converters            | A/D 32x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 388-BBGA                                                              |

| Supplier Device Package    | 388-PBGA (27x27)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc562mzp66r2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Signal Descriptions

| Signal Name           | No. of<br>Signals | Туре | Function after<br>Reset <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------------|-------------------|------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clocks and PLL        |                   |      |                                      |                                                                                                                                                                                                                                                                                                                                                                              |  |

| XTAL                  | 1                 | 0    | XTAL                                 | XTAL. This output signal is one of the connections to an external crystal for the internal oscillator circuitry.                                                                                                                                                                                                                                                             |  |

| EXTAL                 | 1                 | I    | EXTAL                                | EXTAL. This signal is one of the connections to an external crystal for the internal oscillator circuitry. If EXTAL is unused, it must be grounded.                                                                                                                                                                                                                          |  |

| XFC                   | 1                 | I    | XFC                                  | External Filter Capacitance. This input signal is the connection for an external capacitor filter for the PLL circuitry.                                                                                                                                                                                                                                                     |  |

| CLKOUT                | 1                 | 0    | CLKOUT                               | Clock Out. This output signal is the clock system frequency.<br>The CLKOUT drive strength can be configured to full<br>strength, half strength, quarter strength, or disabled. The<br>drive strength is configured using the COM[0:1] bits and<br>CQDS bits in the SCCR register in the USIU.                                                                                |  |

| EXTCLK                | 1                 | Ι    | EXTCLK                               | EXTCLK. This is the external frequency source for the MPC561/MPC563. If EXTCLK is unused, it must be grounded.                                                                                                                                                                                                                                                               |  |

| ENGCLK / BUCLK        | 1                 | 0    | ENGCLK (2.6                          | ENGCLK. This is the engineering clock output. Drive voltage<br>can be configured to 2.6 V, 5 V (with slew-rate control), or<br>disabled. The drive voltage is configured using the<br>EECLK[0:1] bits in the SCCR register in the SIU.                                                                                                                                       |  |

|                       |                   | 0    | V)                                   | BUCLK. When the MPC561/MPC563 is in limp mode, it is<br>operating from a less precise on-chip ring oscillator to allow<br>the system to continue minimum functionality until the<br>system clock is fixed. This backup clock can be seen<br>externally if selected by the values of the EECLK[0:1] bits in<br>the SCCR register in the USIU.                                 |  |

| VDDSYN                | 1                 | Ι    | VDDSYN                               | VDDSYN. This is the power supply of the PLL circuitry.                                                                                                                                                                                                                                                                                                                       |  |

| VSSSYN                | 1                 | Ι    | VSSSYN                               | VSSSYN. This is the ground reference of the PLL circuitry.                                                                                                                                                                                                                                                                                                                   |  |

|                       |                   |      | Configur                             | ation                                                                                                                                                                                                                                                                                                                                                                        |  |

| PULL_SEL <sup>3</sup> | 1                 | I    | PULL_SEL                             | Pull Select. PULL_SEL determines whether the pull devices<br>on the MIOS and TPU signals are pull-ups or pull-downs.<br>When pull-ups are selected, the pull-ups are to 5.0 V except<br>the following MIOS signals will be pulled to 2.6V:<br>VF[0:2]/MPIO32B[0:2], VFLS[0:1]/MPIO32B[3:4], and<br>MDO[7:4]/MPIO32B[7:10]. When this pin is low, pull-downs<br>are selected. |  |

|                       |                   |      | TouCA                                | AN                                                                                                                                                                                                                                                                                                                                                                           |  |

| A_CNTX0               | 1                 | 0    | A_CNTX0                              | TouCAN_A Transmit Data. This signal is the serial data output.                                                                                                                                                                                                                                                                                                               |  |

| A_CNRX0               | 1                 | l    | A_CNRX0                              | TouCAN_A Receive Data. This signal is the serial data input.                                                                                                                                                                                                                                                                                                                 |  |

| B_CNTX0               | 1                 | 0    | B_CNTX0                              | TouCAN_B Transmit Data. This signal is the serial data output.                                                                                                                                                                                                                                                                                                               |  |

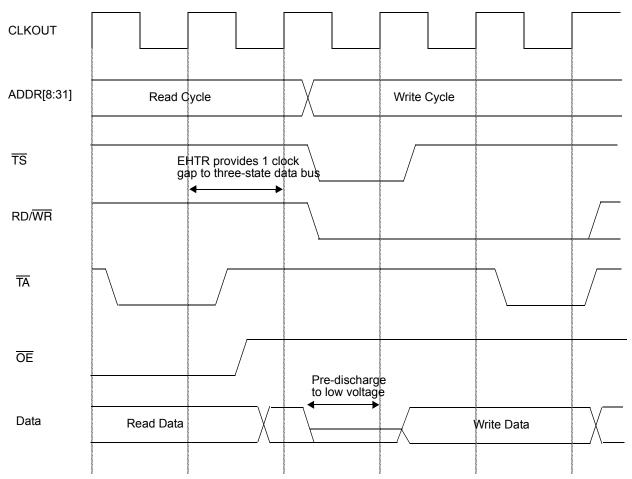

Refer to Section 2.4, "Pad Module Configuration Register (PDMCR2)," and Section 10.9.4, "Memory Controller Option Registers (OR0–OR3)," for more information on PREDIS\_EN, and EHTR configuration bits.

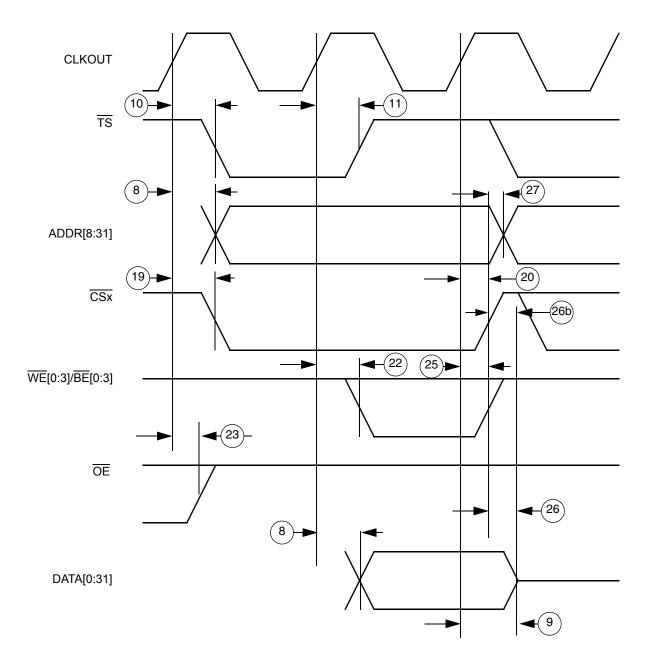

Figure 9-11. Read Followed by Write when Pre-Discharge Mode is Enabled, and EHTR is Set

# 9.5.4 Burst Transfer

The MPC561/MPC563 uses non-wrapping burst transfers to access operands of up to 32 bytes (eight words). A non-wrapping burst access stops accessing the external device when the word address is modulo four/eight. Burst configuration is determined by the value of BURST\_EN in the SIUMCR register. See Chapter 5, "Unified System Interface Unit (USIU) Overview" for further details. The MPC561/MPC563 begins the access by supplying a starting address that points to one of the words in the array and requires the memory to sequentially drive or sample each word on the data bus. The selected slave device must internally increment ADDR28 and ADDR29 (and ADDR30 in the case of a 16-bit port slave device, and also ADDR31 in the case of an 8-bit port slave device) of the supplied address for each transfer, causing the address to reach a four/eight word boundary, and then stop. The address and transfer attributes supplied by the MPC561/MPC563 remain stable during the transfers. The selected device terminates each transfer by driving or sampling the word on the data bus and asserting TA.

# 10.2.6.2 Case 2: Short Setup Time

Initial access:

Enabling short setup time requires one clock cycle:

Initial access time of memory + Data setup time of CPU + Delays = 49 + 3 + 1 = 53ns

The number of clocks required =  $\frac{53}{17.9}$  = 2.96 + 1(SST Enable Clock) = 3.96 therefore 4 clocks are required.

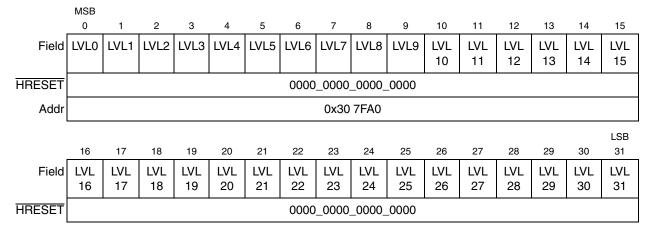

### Figure 12-8. Pending Interrupt Request Register (UIPEND)

#### Table 12-7. UIPEND Bit Descriptions

| Bits | Name         | Description                                                                                                                                                |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | LVL <i>x</i> | Pending interrupt request level. Accessible only in supervisor mode. $LVLx$ identifies the interrupt source as UIMB LVLx, where x is the interrupt number. |

#### QADC64E Enhanced Mode Operation

| Bits | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8    | IST       | Input Sample Time. The IST field allows software to specify the length of the sample window. Provision is made to vary the input sample time, through software control, to offer flexibility in the source impedance of the circuitry providing the QADC64E analog channel inputs. Longer sample times permit more accurate A/D conversions of signals with higher source impedances. The programmable sample time can also be used to increase the time interval between conversions to adjust the queue execution time or the sampling rate.<br>0 QCLK period x 2<br>1 QCLK period x 8                                                                                                                   |

| 9:15 | CHAN[6:0] | Channel Number. The CHAN field selects the input channel number. The software programs the channel field of the CCW with the channel number corresponding to the analog input signal to be sampled and converted. The analog input signal channel number assignments and the signal definitions vary depending on whether the multiplexed or non-multiplexed mode is used by the application. As far as the queue scanning operations are concerned, there is no distinction between an internally or externally multiplexed analog input. Refer to Section 14.2.5, "External Multiplexing" for more information on external multiplexing. Table 14-20 and Table 14-21 show the channel number assignments |

### Table 14-19. CCW Bit Descriptions (continued)

### Table 14-20. QADC64E\_A Multiplexed Channel Assignments and Signal Designations

| Multiplexed Input Signals            |                              |                                   |                                                              | Channel Number in CCW CHAN<br>Field                 |                      |  |

|--------------------------------------|------------------------------|-----------------------------------|--------------------------------------------------------------|-----------------------------------------------------|----------------------|--|

| Port Signal<br>Name                  | Analog<br>Signal Name        | Other Functions /<br>Descriptions | Signal Type                                                  | Binary                                              | Decimal              |  |

| ANw/A_PQB0                           | AN00 to AN07                 | _                                 | Input                                                        | 0000000 to<br>0000111                               | 0 to 7               |  |

| ANx/A_PQB1                           | AN08 to AN15                 | _                                 | Input                                                        | 0001000 to<br>0001111                               | 8 to 15              |  |

| ANy/A_PQB2                           | AN16 to AN23                 | _                                 | Input                                                        | 0010000 to<br>0010111                               | 16 to 23             |  |

| ANz/A_PQB3                           | AN24 to AN31                 | _                                 | Input                                                        | 0011000 to<br>0011111                               | 24 to 31             |  |

| _                                    | RESERVED                     | _                                 | -                                                            | 0100000 to<br>0101001                               | 32 to 41             |  |

| _                                    | RESERVED                     | —                                 | _                                                            | 0101010                                             | 42                   |  |

| _                                    | RESERVED                     | _                                 | _                                                            | 0101011                                             | 43                   |  |

| A_PQB0<br>A_PQB1<br>A_PQB2<br>A_PQB3 | AN44<br>AN45<br>AN46<br>AN47 | ANw<br>ANx<br>ANy<br>ANz          | Input/Output<br>Input/Output<br>Input/Output<br>Input/Output | 0101100<br>0101101<br>0101110<br>0101110<br>0101111 | 44<br>45<br>46<br>47 |  |

| A_PQB4<br>A_PQB5<br>A_PQB6<br>A_PQB7 | AN48<br>AN47<br>AN50<br>AN51 |                                   | Input/Output<br>Input/Output<br>Input/Output<br>Input/Output | 0110000<br>0110001<br>0110010<br>0110011            | 48<br>49<br>50<br>51 |  |

#### QADC64E Enhanced Mode Operation

Analog supplies should be isolated from digital supplies as much as possible. This necessity stems from the higher performance requirements often associated with analog circuits. Therefore, deriving an analog supply from a local digital supply is not recommended. However, if for economic reasons digital and analog power are derived from a common regulator, filtering of the analog power is recommended in addition to the bypassing of the supplies already mentioned.

### NOTE

An RC low pass filter could be used to isolate the digital and analog supplies when generated by a common regulator. If multiple high precision analog circuits are locally employed (i.e., two A/D converters), the analog supplies should be isolated from each other as sharing supplies introduces the potential for interference between analog circuits.

Grounding is the most important factor influencing analog circuit performance in mixed signal systems (or in stand-alone analog systems). Close attention must be paid not to introduce additional sources of noise into the analog circuitry. Common sources of noise include ground loops, inductive coupling, and combining digital and analog grounds together inappropriately.

The problem of how and when to combine digital and analog grounds arises from the large transients which the digital ground must handle. If the digital ground is not able to handle the large transients, the current from the large transients can return to ground through the analog ground. It is the excess current overflowing into the analog ground which causes performance degradation by developing a differential voltage between the true analog ground and the microcontroller's ground signal. The end result is that the ground observed by the analog circuit is no longer true ground and often ends in skewed results.

Two similar approaches designed to improve or eliminate the problems associated with grounding excess transient currents involve star-point ground systems. One approach is to star-point the different grounds at the power supply origin, thus keeping the ground isolated. Refer to Figure 14-49.

Queued Serial Multi-Channel Module

# 15.3 Memory Maps

The QSMCM memory maps, shown in Table 15-1 and Table 15-2, includes the global registers, the QSPI and dual SCI control and status registers, and the QSPI RAM. The QSMCM memory map can be divided into supervisor-only data space and assignable data space. The address offsets shown are from the base address of the QSMCM module. Refer to Figure 1-4 for a diagram of the MPC561/MPC563 internal memory map.

| Access <sup>1</sup> | Address   | MSB <sup>2</sup><br>0                                                                                                                                                                                                    | LSB<br>15                                                                                         |  |  |

|---------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| S                   | 0x30 5000 | QSMCM Module Configuration Register (QSMCMMCR)<br>See Table 15-7 for bit descriptions.                                                                                                                                   |                                                                                                   |  |  |

| Т                   | 0x30 5002 | QSMCM Tes                                                                                                                                                                                                                | t Register (QTEST)                                                                                |  |  |

| S                   | 0x30 5004 | Dual SCI Interrupt Level (QDSCI_IL)     Reserved       See <xrefblue>Table 15-5 for bit     descriptions.</xrefblue>                                                                                                     |                                                                                                   |  |  |

| S                   | 0x30 5006 | Reserved                                                                                                                                                                                                                 | Queued SPI Interrupt Level (QSPI_IL)<br>See <xrefblue>Table 15-6 for bit descriptions.</xrefblue> |  |  |

| S/U                 | 0x30 5008 |                                                                                                                                                                                                                          | Register 0 (SCC1R0)<br>e 15-24 for bit descriptions.                                              |  |  |

| S/U                 | 0x30 500A |                                                                                                                                                                                                                          | Register 1 (SCC1R1)<br>e 15-25 for bit descriptions.                                              |  |  |

| S/U                 | 0x30 500C |                                                                                                                                                                                                                          | SCI1 Status Register (SC1SR)<br>See <xrefblue>Table 15-26 for bit descriptions.</xrefblue>        |  |  |

| S/U                 | 0x30 500E | SCI1 Data Register (SC1DR)<br>See <xrefblue>Table 15-27 for bit descriptions.</xrefblue>                                                                                                                                 |                                                                                                   |  |  |

| S/U                 | 0x30 5010 | R                                                                                                                                                                                                                        | Reserved                                                                                          |  |  |

| S/U                 | 0x30 5012 | Reserved                                                                                                                                                                                                                 |                                                                                                   |  |  |

| S/U                 | 0x30 5014 | Reserved QSMCM Port Q Data Register (PORTQS)<br>See Section 15.5.1, "Port QS Data Register (PORTQS)," for<br>descriptions.                                                                                               |                                                                                                   |  |  |

| S/U                 | 0x30 5016 | QSMCM Pin Assignment Register<br>(PQSPAR)QSMCM Data Direction Register (DDI<br>See <xrefblue>Table 15-10 for bit<br/>descriptions.See <xrefblue>Table 15-10 for bit<br/>descriptions.descriptions.</xrefblue></xrefblue> |                                                                                                   |  |  |

| S/U                 | 0x30 5018 | QSPI Control Register 0 (SPCR0)<br>See <xrefblue>Table 15-13 for bit descriptions.</xrefblue>                                                                                                                            |                                                                                                   |  |  |

| S/U                 | 0x30 501A | QSPI Control Register 1 (SPCR1)<br>See <xrefblue>Table 15-15 for bit descriptions.</xrefblue>                                                                                                                            |                                                                                                   |  |  |

| S/U                 | 0x30 501C | QSPI Control Register 2 (SPCR2)<br>See <xrefblue>Table 15-16 for bit descriptions.</xrefblue>                                                                                                                            |                                                                                                   |  |  |

| S/U                 | 0x30 501E | QSPI Control Register 3 (SPCR3)QSPI Status Register (SPSR)See <xrefblue>Table 15-17 for bit<br/>descriptions.See <xrefblue>Table 15-18 for bit<br/>descriptions.</xrefblue></xrefblue>                                   |                                                                                                   |  |  |

MPC561/MPC563 Reference Manual, Rev. 1.2

#### **Queued Serial Multi-Channel Module**

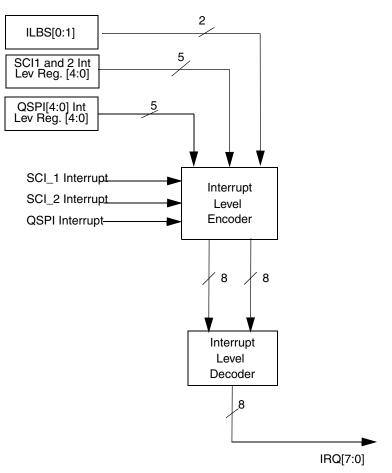

Figure 15-3. Interrupt Hardware Block Diagram

# 15.4.5 **QSPI Interrupt Generation**

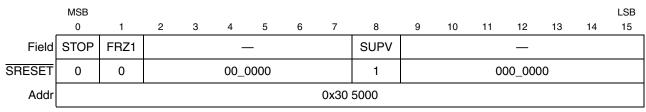

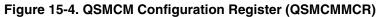

# 15.4.6 **QSMCM Configuration Register (QSMCMMCR)**

The QSMCMMCR contains parameters for interfacing to the CPU and the intermodule bus. This register can be modified only when the CPU is in supervisor mode.

| Bits[3:0] | Bits per Transfer |

|-----------|-------------------|

| 1011      | 11                |

| 1100      | 12                |

| 1101      | 13                |

| 1110      | 14                |

| 1111      | 15                |

## 15.6.1.2 QSPI Control Register 1 (SPCR1)

SPCR1 enables the QSPI and specifies transfer delays. The CPU has read/write access to SPCR1, but the QSPI has read access only to all bits except SPE. SPCR1 must be written last during initialization because it contains SPE. The QSPI automatically clears this bit after it completes all serial transfers or when a mode fault occurs. Writing a new value to SPCR1 while the QSPI is enabled disrupts operation.

| Bits | Name  | Description                                                                                                                                                                                                                             |  |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0    | SPE   | QSPI enable. Refer to Section 15.6.4.1, "Enabling, Disabling, and Halting the SPI.<br>0 = QSPI is disabled. QSPI pins can be used for general-purpose I/O.<br>1 = QSPI is enabled. Pins allocated by PQSPAR are controlled by the QSPI. |  |

| 1:7  | DSCKL | Delay before SCK. When the DSCK bit is set in a command RAM byte, this field determines the length of the delay from PCS valid to SCK transition. The following equation determines the actual delay before SCK:                        |  |

|      |       | PCS to SCK Delay = $\frac{\text{DSCKL}}{\text{f}_{\text{SYS}}}$                                                                                                                                                                         |  |

|      |       | where DSCKL equals is in the range of 1 to 127.<br>Refer to Section 15.6.5.3, "Delay Before Transfer for more information.                                                                                                              |  |

| 8:15 | DTL   | Length of delay after transfer. When the DT bit is set in a command RAM byte, this field determines the length of the delay after a serial transfer. The following equation is used to calculate the delay:                             |  |

|      |       | Delay after Transfer = $\frac{32XDTL}{f_{SYS}}$                                                                                                                                                                                         |  |

|      |       | where DTL is in the range of 1 to 255.                                                                                                                                                                                                  |  |

|      |       | A zero value for DTL causes a delay-after-transfer value of 8192 $\div$ f <sub>SYS</sub> (204.8 µs with a 40-MHz IMB3 clock).                                                                                                           |  |

|      |       | Refer to Section 15.6.5.4, "Delay After Transfer for more information.                                                                                                                                                                  |  |

# 24.2.2 Security

Security is provided via the UC3F censorship mechanism. If a UC3F array is in censored mode, reads or writes to the UC3F will not be allowed (RCPU will not be able to fetch instructions from the UC3F) once any of the following cases are detected:

- Program trace and/or data trace are enabled

- Read/write access is attempted (can be to any address location)

- RCPU development access is enabled.

# 24.2.3 Normal

Normal operation of the READI module allows for development support features to be available. These features include control of the device, access to registers, and the ability to perform data or instruction trace.

# 24.2.4 Disabled

If  $\overline{\text{EVTI}}$  is negated at negation of  $\overline{\text{RSTI}}$ , the READI module will be disabled. No trace output will be provided, and output auxiliary port will be three-stated. Any message sent by the tool is ignored.

# 24.3 Parametrics

With 32-deep message queues, throughput numbers were calculated for the following benchmark codes [assuming full port mode]:

- For an example benchmark which had 10.9% direct branches, 2.5% indirect branches, 10.4% data writes, and 19.3% data reads, approximately 20% of total data trace accesses will be traced.

- For another example benchmark which had 9.8% direct branches, 2.8% indirect branches, 6.6% data writes, and 18.3% data reads, approximately 27% of total data trace accesses will be traced.

### NOTE

The queue is only 16 messages deep on revisions prior to Rev. D of the MPC561 and is 16 deep in Rev. B and earlier versions of the MPC563.

For reduced port mode, the data trace feature should not be used, or used sparingly, so as not to cause queue overruns.

# 24.4 Messages

The READI module implements messaging via the auxiliary port according to the IEEE-ISTO 5001 - 1999. Messaging will be implemented via transfer codes (TCODEs) on the auxiliary port. The TCODE number for the message identifies the transfer format (the number and/or size of packets to be transferred) and the purpose of each packet.

Public messages outlined in Table 24-1 are supported by READI.

| Message Name         | Minimum<br>Packet<br>Size<br>(bits) | Maximu<br>m Packet<br>Size<br>(bits) | Packet<br>Type | Packet Description       | Direction |

|----------------------|-------------------------------------|--------------------------------------|----------------|--------------------------|-----------|

| Resource Full        | 6                                   | 6                                    | Fixed          | TCODE number = 27 (0x1B) | From      |

| Message <sup>2</sup> | 1                                   | 4                                    | Variable       | resource code            | Device    |

Table 24-19. Public Messages Supported (continued)

<sup>1</sup> Refer to Table 24-20 for the error message codes.

<sup>2</sup> Not available on the MPC561 prior to revision D and not available on MPC563 revision B and earlier.

| Error Code  | Description                          |  |  |  |  |

|-------------|--------------------------------------|--|--|--|--|

| 00000       | Ownership trace overrun <sup>1</sup> |  |  |  |  |

| 00001       | Program trace overrun <sup>1</sup>   |  |  |  |  |

| 00010       | Data trace overrun <sup>1</sup>      |  |  |  |  |

| 00011       | Read/write access error              |  |  |  |  |

| 00100       | Invalid message                      |  |  |  |  |

| 00101       | Invalid access opcode                |  |  |  |  |

| 00110       | Watchpoint overrun                   |  |  |  |  |

| 00111       | Program/data/ownership trace overrun |  |  |  |  |

| 01000-10111 | Reserved                             |  |  |  |  |

| 11000-11111 | Vendor Defined                       |  |  |  |  |

### Table 24-20. Error Message Codes

<sup>1</sup> This error message is not available on the MPC561 prior to revision D and is not available on the MPC563 revision B and earlier.

Vendor-defined messages outlined in Table 24-21 are also supported by READI.

| TCODE Name            | Minimum<br>Packet Size<br>(bits) | Maximum<br>Packet Size<br>(bits) | Packet<br>Type | Packet Description                        | Direction |

|-----------------------|----------------------------------|----------------------------------|----------------|-------------------------------------------|-----------|

| Dev Port Access —     | 6                                | 6                                | Fixed          | TCODE number = 56 (0x38)                  | From      |

| DSDI Data Message     | 10                               | 35                               | Variable       | BDM Development Serial Data In (DSDI)     | Tool      |

| Dev Port Access       | 6                                | 6                                | Fixed          | TCODE number = 57 (0x39)                  | From      |

| —DSDO Data<br>Message | 10                               | 35                               | Variable       | BDM Development Serial Data Out<br>(DSDO) | Device    |

| Dev Port Access —     | 6                                | 6                                | Fixed          | TCODE number = 58 (0x3A)                  | From      |

| BDM Status Message    | 1                                | 1                                | Fixed          | BDM status                                | Device    |

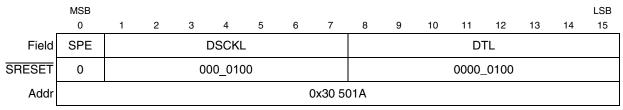

### Figure 24-16. Enabling Program Trace Out of System Reset

# 24.7.7 READI Signals

The READI signals support Nexus (IEEE-ISTO 5001-1999) auxiliary port interface for debug. There are two modes available, full port mode and reduced port mode. Reduced port mode allows for a 1 bit input stream and a 2 bit output stream. Full port mode allows for a 2 bit input stream and an 8 bit output stream. See Figure 24-11 for READI mode selection.

Steps to Enter READI (Nexus) mode:

- 1. Negate PORESET while holding JCOMP/ $\overline{\text{RSTI}}$  low.

- Configure TMS/EVTI and TDI/DSDI/MDI[0] while JCOMP/RSTI is low. (EVTI = low to enable Nexus)

- 3. Negate JCOMP/ $\overline{RSTI}$ .

- 4. If MDI[0] is high at JCOMP/RSTI negation, then full port mode is enabled otherwise Reduced mode is selected.

To exit READI mode:

1. Reassert JCOMP/ $\overline{\text{RSTI}}$  to disable READI.

Figure 24-17. READI Mode Selection

### 24.7.7.1 Reset Configuration for Debug Mode

To enable RCPU development access via the READI signals, the reset sequence outlined below should be used:

- Assert READI reset ( $\overline{RSTI}$ ), event-in ( $\overline{EVTI}$ ) and system reset ( $\overline{HRESET}$ )

- Negate RSTI

- Upon negation of RSTI, tool should configure the DOR, DME, and DPA fields in the DC register to desired setting.

- Tool negates HRESET at least 16 system clocks after receiving the device ready message

Refer to Figure 24-84 for further details.

| Address                  | Access           | Symbol   | Register                                                                                                     | Size                | Reset |

|--------------------------|------------------|----------|--------------------------------------------------------------------------------------------------------------|---------------------|-------|

| 0x30 4150 –<br>0x30 415F | S/U <sup>3</sup> | _        | <ul> <li>TPU3_A Channel 5 Parameter Registers.</li> <li>See Section 19.4.15 for more information.</li> </ul> |                     | -     |

| 0x30 4160 –<br>0x30 416F | S/U <sup>3</sup> | _        | TPU3_A Channel 6 Parameter Registers.<br>See Section 19.4.15 for more information.                           | 16, 32 <sup>2</sup> | —     |

| 0x30 4170 –<br>0x30 417F | S/U <sup>3</sup> | _        | TPU3_A Channel 7 Parameter Registers.<br>See Section 19.4.15 for more information.                           | 16, 32 <sup>2</sup> | —     |

| 0x30 4180 –<br>0x30 418F | S/U <sup>3</sup> | _        | TPU3_A Channel 8 Parameter Registers.<br>See Section 19.4.15 for more information.                           | 16, 32 <sup>2</sup> | —     |

| 0x30 4190 –<br>0x30 419F | S/U <sup>3</sup> | _        | TPU3_A Channel 9 Parameter Registers.<br>See Section 19.4.15 for more information.                           | 16, 32 <sup>2</sup> | _     |

| 0x30 41A0 –<br>0x30 41AF | S/U <sup>3</sup> | _        | TPU3_A Channel 10 Parameter Registers.<br>See Section 19.4.15 for more information.                          | 16, 32 <sup>2</sup> | _     |

| 0x30 41B0 –<br>0x30 41BF | S/U <sup>3</sup> | _        | TPU3_A Channel 11 Parameter Registers.<br>See Section 19.4.15 for more information.                          | 16, 32 <sup>2</sup> | _     |

| 0x30 41C0 –<br>0x30 41CF | S/U <sup>3</sup> | _        | TPU3_A Channel 11 Parameter Registers.<br>See Section 19.4.15 for more information.                          | 16, 32 <sup>2</sup> | _     |

| 0x30 41D0 –<br>0x30 41DF | S/U <sup>3</sup> | _        | TPU3_A Channel 11 Parameter Registers.<br>See Section 19.4.15 for more information.                          | 16, 32 <sup>2</sup> | _     |

| 0x30 41E0 –<br>0x30 41EF | S/U <sup>3</sup> | _        | TPU3_A Channel 14 Parameter Registers.<br>See Section 19.4.15 for more information.                          | 16, 32 <sup>2</sup> | -     |

| 0x30 41F0 –<br>0x30 41FF | S/U <sup>3</sup> | _        | TPU3_A Channel 15 Parameter Registers.<br>See Section 19.4.15 for more information.                          | 16, 32 <sup>2</sup> | _     |

|                          |                  |          | TPU3_B                                                                                                       |                     |       |

| 0x30 4400 <sup>1</sup>   | S <sup>1</sup>   | TPUMCR_B | TPU3_B Module Configuration Register                                                                         | 16 only             | S, M  |

| 0x30 4402                | Т                | TCR_B    | TPU3_B Test Configuration Register                                                                           | 16                  | S, M  |

| 0x30 4404                | Т                | DSCR_B   | TPU3_B Development Support Control Register                                                                  | 16 <sup>2</sup>     | S, M  |

| 0x30 4406                | Т                | DSSR_B   | TPU3_B Development Support Status Register                                                                   | 16 <sup>2</sup>     | S, M  |

| 0x30 4408                | S                | TICR_B   | TPU3_B Interrupt Configuration Register                                                                      | 16 <sup>2</sup>     | S, M  |

| 0x30 440A                | S                | CIER_B   | TPU3_B Channel Interrupt Enable Register                                                                     | 16 <sup>2</sup>     | S, M  |

| 0x30 440C                | S                | CFSR0_B  | TPU3_B Channel Function Selection Register 0                                                                 | 16 <sup>2</sup>     | S, M  |

| 0x30 440E                | S                | CFSR1_B  | TPU3_B Channel Function Selection Register 1                                                                 | 16 <sup>2</sup>     | S, M  |

| 0x30 4410                | S                | CFSR2_B  | TPU3_B Channel Function Selection Register 2                                                                 | 16 <sup>2</sup>     | S, M  |

| 0x30 4412                | S                | CFSR3_B  | TPU3_B Channel Function Selection Register 3                                                                 | 16 <sup>2</sup>     | S, M  |

| 0x30 4414                | S/U <sup>3</sup> | HSQR0_B  | TPU3_B Host Sequence Register 0                                                                              | 16 <sup>2</sup>     | S, M  |

| 0x30 4416                | S/U <sup>3</sup> | HSQR1_B  | TPU3_B Host Sequence Register 1                                                                              | 16 <sup>2</sup>     | S, M  |

| 0x30 4418                | S/U <sup>3</sup> | HSRR0_B  | TPU3_B Host Service Request Register 0                                                                       | 16 <sup>2</sup>     | S, M  |

| 0x30 441A                | S/U <sup>3</sup> | HSRR1_B  | TPU3_B Host Service Request Register 1                                                                       | 16 <sup>2</sup>     | S, M  |

| Table B-9. Time Processor Unit 3 A and B ( | (TPU3 A and B) (continued)  |

|--------------------------------------------|-----------------------------|

| Table D-9. Time Processor Offic 5 A and D  | (TF 05 A and D) (continued) |

MPC561/MPC563 Reference Manual, Rev. 1.2

# D.20 Serial Input/Output Port (SIOP)

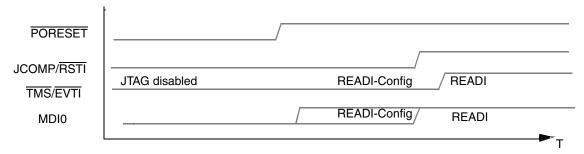

The serial input/output port (SIOP) TPU3 function uses two or three TPU3 channels to form a uni- or bidirectional synchronous serial port that can be used to communicate with a wide variety of devices. It can be used to add serial capabilities to a device without a serial port, or to extend the capabilities of one with a hardware-synchronous port. The SIOP TPU3 function has been designed to closely resemble the SIOP hardware port found on some Freescale MCUs.

SIOP operates in master mode (the TPU3 always generates the clock) and has the following programmable features:

- 1. Choice of one-channel clock-only, two-channel clock + transmit, two-channel clock + receive, or three-channel clock + transmit + receive operating modes

- 2. Freely programmable baud-rate period over a 15-bit range of TCR1 counts

- 3. Selection of MSB or LSB first shift direction

- 4. Variable transfer size from 1 to 16 bits

- 5. Programmable clock polarity

When a transfer of data is complete, the SIOP function notifies the host RCPU by issuing an interrupt request. The arrangement of the multiple SIOP channels is fixed: the data-out channel is the channel above the clock channel and the data-in channel is the channel below the clock channel. In clock-only or uni-directional mode, the unused TPU3 channels are free to run other TPU3 functions. Two possible SIOP configurations are shown in Figure D-31

#### Figure D-31. Two Possible SIOP Configurations

### **D.20.1** Parameters

Figure D-32 shows the host interface areas and parameter RAM for the SIOP function. The following sections describe these parameters.

MPC561/MPC563 Reference Manual, Rev. 1.2

Memory Access Timing

### Table E-2. Instruction Timing Examples for Different Buses

| A00055                              | Number of Clocks |                |     |     |     |   |   | Total |   |    |    |    |    |                |

|-------------------------------------|------------------|----------------|-----|-----|-----|---|---|-------|---|----|----|----|----|----------------|

| Access                              | 1                | 2              | 3   | 4   | 5   | 6 | 7 | 8     | 9 | 10 | 11 | 12 | 13 | TOLAI          |

| Load/Store -> Ebus                  | L                | U              | E   |     |     |   |   |       |   |    |    |    |    | 6 <sup>1</sup> |

|                                     |                  |                |     | E   | U   | L |   |       |   |    |    |    |    |                |

| Load/Store -> IMB                   | L                | U              | IMB |     |     |   |   |       |   |    |    |    |    | 6              |

| 16 bits                             |                  |                |     | IMB | U   | L |   |       |   |    |    |    |    |                |

| Instruction Fetch->                 | C,U              |                |     |     |     |   |   |       |   |    |    |    |    | 2              |

| cmf<br>new page                     |                  | U <sup>2</sup> |     |     |     |   |   |       |   |    |    |    |    |                |

| 3 consecutive<br>accesses           |                  | C,U            |     |     |     |   |   |       |   |    |    |    |    | 1              |

|                                     |                  | U              |     |     |     |   |   |       |   |    |    |    |    |                |

|                                     |                  |                | C,U |     |     |   |   |       |   |    |    |    |    | 1              |

|                                     |                  |                | U   |     |     |   |   |       |   |    |    |    |    |                |

| Instruction Fetch-><br>DECRAM       | U                | ICD<br>U       |     |     |     |   |   |       |   |    |    |    |    |                |

| (Decompression off)                 |                  | ICD<br>U       | U   |     |     |   |   |       |   |    |    |    |    |                |

| Instruction Fetch->                 | C,U              |                |     |     |     |   |   |       |   |    |    |    |    | 2              |

| cmf<br>new page                     |                  | U              |     |     |     |   |   |       |   |    |    |    |    |                |

| Load/Store -> IMB                   | L                | U              | IMB |     |     |   |   |       |   |    |    |    |    | 6              |

|                                     |                  |                |     | IMB | U   | L |   |       |   |    |    |    |    |                |

| Instruction Fetch->                 |                  | С              | U   |     |     |   |   |       |   |    |    |    |    | 6              |

| cmf<br>new page                     |                  |                |     |     |     | U |   |       |   |    |    |    |    |                |

| Load/Store -> IMB                   | L                | U              | IMB |     |     |   |   |       |   |    |    |    |    | 6              |

|                                     |                  |                |     | IMB | U   | L |   |       |   |    |    |    |    |                |

| External Bus-> cmf<br>new page      | Е                |                | U   |     |     |   |   |       |   |    |    |    |    | 5              |

|                                     |                  |                |     | U   | Е   |   |   |       |   |    |    |    |    |                |

| External Bus-> IMB                  | Е                |                | U   | IMB |     |   |   |       |   |    |    |    |    | 7              |

|                                     |                  |                |     |     | IMB | U | E |       |   |    |    |    |    |                |

| Load/Store-><br>DECRAM              | L                | U              |     |     |     |   |   |       |   |    |    |    |    |                |

| • • • • • • • • • • • • • • • • • • |                  |                | U   | L   |     |   |   |       |   |    |    |    |    |                |

#### Electrical Characteristics

is required is due to ESD diodes in the pad logic for dual 2.6-V/5-V compliant pins and 2.6-V pins. The diodes are forward biased when  $V_{DDL}$  is greater than  $V_{DDH}$  and will start to conduct current.

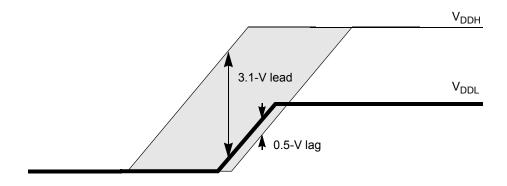

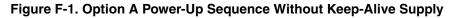

Figure F-1 illustrates the power-up sequence if no keep-alive supply is required. Figure F-2 illustrates the power-up sequence if a keep-alive supply is required. The keep-alive supply should be powered-up at the same instant or before both the high voltage and low voltage supplies are powered-up.

$V_{DDH}$  cannot lead  $V_{DDL}$  by more than 3.1 V  $V_{DDH}$  cannot lag  $V_{DDL}$  by more than 0.5 V

$V_{DDH}$  cannot lead  $V_{DDL}$  by more than 3.1 V  $V_{DDH}$  cannot lag  $V_{DDL}$  by more than 0.5 V

The option A power-down sequence (excluding  $V_{DDKA}$ ) is

- 1.  $V_{DDH} \le V_{DDL} + 3.1 \text{ V} (V_{DDH} \text{ cannot lag } V_{DDL} \text{ by more than } 3.1 \text{ V})$

- 2.  $V_{DDH} \ge V_{DDL}$  0.5 V (V<sub>DDH</sub> cannot lead V<sub>DDL</sub> by more than 0.5 V)

Figure F-3 illustrates the power-down sequence if no keep-alive supply is required.

MPC561/MPC563 Reference Manual, Rev. 1.2

**Electrical Characteristics**

### Table F-10. Bus Operation Timing (continued)

Note: (V<sub>DD</sub> = 2.6 V  $\pm$  0.1 V, V<sub>DDH</sub> = 5.0 V  $\pm$  0.25 V, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, 50 pF load unless noted otherwise)

|     | Oheresteristis                                                                                     | 40      | MHz | 56 I |      |        |

|-----|----------------------------------------------------------------------------------------------------|---------|-----|------|------|--------|

|     | Characteristic                                                                                     | Min Max |     | Min  | Мах  | – Unit |

| 10b | CLKOUT to RETRY assertion<br>(when driven by the<br>Memory Controller)                             |         | 10  |      | 10   | ns     |

| 11  | CLKOUT to TS, BB negation                                                                          | 7.25    | 14  | 5.5  | 10.5 | ns     |

| 11a | CLKOUT to TA, BI negation<br>(when driven by the<br>Memory Controller)                             | 2       | 11  | 2    | 11   | ns     |

| 11b | CLKOUT to RETRY negation<br>(when driven by the<br>Memory Controller)                              | 2       | 11  | 2    | 11   | ns     |

| 12  | CLKOUT to TS, BB High Z                                                                            | 6.25    | 20  | 4.5  | 16   | ns     |

| 12a | CLKOUT to TA, BI High Z<br>(when driven by the<br>Memory Controller)                               |         | 15  |      | 15   | ns     |

| 13  | CLKOUT to TEA assertion                                                                            |         | 8.5 |      | 8.5  | ns     |

| 14  | CLKOUT to TEA High Z                                                                               |         | 15  |      | 15   | ns     |

| 15  | Input Valid to CLKOUT<br>(Setup Time)<br>TA<br>TEA<br>BI <sup>3</sup>                              | 12      |     | 8.5  |      | ns     |

| 15a | Input Valid to CLKOUT<br>(Setup Time)<br>KR<br>CR<br>RETRY                                         | 10      |     | 7.25 |      | ns     |

| 15b | Input Valid to CLKOUT<br>(Setup Time)<br>BB<br>BG<br>BR <sup>2</sup>                               | 8       |     | 6.5  |      | ns     |

| 16  | CLKOUT to Signal Invalid<br>(Hold Time)<br>TA<br>TEA<br>BI<br>BB<br>BB<br>BG<br>BR <sup>2, 3</sup> | 2       |     | 2    |      | ns     |

### Table F-10. Bus Operation Timing (continued)

| Note: (V_DD = 2.6 V $\pm$ 0.1 V, V_DDH = 5.0 V $\pm$ 0.25 V, T/ | $T_A = T_L$ to $T_H$ , 50 pF load unless noted otherwise) |

|-----------------------------------------------------------------|-----------------------------------------------------------|

|-----------------------------------------------------------------|-----------------------------------------------------------|

|     | Ohavaataviatia                                                                                                                                           | 40   | MHz | 56   | 56 MHz <sup>1</sup> |      |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|---------------------|------|--|

|     | Characteristic                                                                                                                                           | Min  | Max | Min  | Мах                 | Unit |  |

| 16a | CLKOUT to Signal Invalid<br>(Hold Time)<br>RETRY<br>KR<br>CR                                                                                             | 2    |     | 2    |                     | ns   |  |

| 17  | Signal Valid to CLKOUT<br>Rising Edge (Setup Time)<br>D[0:31] <sup>4</sup>                                                                               | 6    |     | 6    |                     | ns   |  |

| 17b | Signal Valid to CLKOUT<br>Rising Edge (Short Setup<br>Time, SST = 1)<br>D[0:31] <sup>4</sup>                                                             | 3    |     | 3    |                     |      |  |

| 18  | CLKOUT Rising Edge to Signal<br>Invalid (Hold Time)<br>D[0:31] <sup>4</sup>                                                                              | 2    |     | 2    |                     | ns   |  |

| 19  | CLKOUT Rising Edge to $\overline{CS}$<br>asserted<br>-GPCM- ACS = 00                                                                                     | 7.25 | 15  | 6.5  | 11.5                | ns   |  |

| 19a | CLKOUT Falling Edge to $\overline{CS}$<br>asserted<br>-GPCM- ACS = 10, TRLX = 0<br>or 1                                                                  |      | 8   |      | 6                   | ns   |  |

| 19b | CLKOUT Falling Edge to $\overline{CS}$<br>asserted<br>-GPCM- ACS = 11, TRLX = 0<br>or 1                                                                  | 6.25 | 14  | 5.5  | 10.5                | ns   |  |

| 19c | CLKOUT Falling Edge to $\overline{CS}$<br>asserted<br>-GPCM- ACS = 11, TRLX = 0,<br>EBDF = 1                                                             | 6.25 | 17  | 6.69 | 12.69               | ns   |  |

| 20  | CLKOUT Rising Edge to $\overline{CS}$<br>negated<br>-GPCM- Read Access<br>or Write access when CSNT =<br>0 or write access when CSNT =<br>1 and ACS = 00 | 1    | 8   | 1    | 7                   | ns   |  |

| 21  | ADDR[8:31] to $\overline{CS}$ asserted<br>-GPCM- ACS = 10, TRLX = 0                                                                                      | 0.75 |     | 1    |                     | ns   |  |

| 21a | ADDR[8:31] to $\overline{CS}$ asserted<br>-GPCM- ACS = 11, TRLX = 0                                                                                      | 8    |     | 6    |                     | ns   |  |

| 22  | CLKOUT Rising Edge to<br>OE, WE[0:3]/BE[0:3]<br>asserted                                                                                                 | 1    | 8   | 1    | 6                   | ns   |  |

**Electrical Characteristics**

Figure F-22. External Bus Write Timing (GPCM Controlled – TRLX = '0', CSNT = '0')

| Signal Name | Pin Name               | Ball Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VSS         | VSS                    | A19, A2, A23, A24, A26, A3, A4, AA1, AA2,<br>AA23, AA24, AA25, AA3, AB1, AB2, AB24,<br>AB25, AB4, AC1, AC21, AC23, AC25, AC3,<br>AC5, AD2, AD22, AD24, AD4, AD5, AE1,<br>AE22, AE23, AE25, AE3, AE4, AE5, AF2,<br>AF22, AF23, AF24, AF26, AF3, AF4, AF6,<br>B1, B19, B23, B25, B3, B4, C1, C2, C24,<br>C26, C4, D1, D2, D23, D25, D26, D3, D5,<br>E2, E24, E25, E26, E3, E4, L11, L12, L13,<br>L14, L15, L16, M11, M12, M13, M14, M15,<br>M16, N11, N12, N13, N14, N15, N16, P11,<br>P12, P13, P14, P15, P16, R11, R12, R13,<br>R14, R15, R16, T11, T12, T13, T14, T15,<br>T16, V25 |  |  |

| KAPWR       | kapwr                  | W26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| IRAMSTBY    | IRAMSTBY               | М3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| QVDDL       | qvddl                  | AA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | AB23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|             |                        | AB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | AC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | AC24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|             |                        | AD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | AD25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|             |                        | AD6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | AE26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|             |                        | AE6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | B26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | C25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | D24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | E23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|             |                        | F4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|             | USIU Power Supplies    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| VDDSYN      | vddsyn                 | Y26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| VSSSYN      | vsssyn                 | AB26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|             | QADC64E Power Supplies | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| VRH         | vrh                    | C10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| VRL         | vrl                    | A10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

### Table G-28. MPC561/MPC563 Signal Names and Pin Names (continued)