Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                          |

|----------------------------|----------------------------------------------------------|

| Product Status             | Active                                                   |

| Core Processor             | PowerPC                                                  |

| Core Size                  | 32-Bit Single-Core                                       |

| Speed                      | 56MHz                                                    |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI, UART/USART                    |

| Peripherals                | POR, PWM, WDT                                            |

| Number of I/O              | 56                                                       |

| Program Memory Size        | 512KB (512K x 8)                                         |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                |                                                          |

| RAM Size                   | 32K x 8                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 2.7V                                              |

| Data Converters            | A/D 32x10b                                               |

| Oscillator Type            | External                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                       |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 388-BBGA                                                 |

| Supplier Device Package    | 388-PBGA (27x27)                                         |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc564mzp56 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| Signal Name                          | No. of<br>Signals                                                                                                                                                                                                                                                            | Туре | Function after<br>Reset <sup>1</sup>                    | Description                                                                                                                                                                                                                   |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                      | _                                                                                                                                                                                                                                                                            |      | Interrupt Co                                            | ontroller                                                                                                                                                                                                                     |  |  |

|                                      | 1                                                                                                                                                                                                                                                                            | I    | MDO4 if the<br>Nexus (READI)                            | Interrupt Request 0. One of the eight external signals that can request, by means of the internal interrupt controller, a service routine from the RCPU. IRQ0 is a non-maskable interrupt (NMI).                              |  |  |

| IRQ0 / SGPIOC0 / MDO4                |                                                                                                                                                                                                                                                                              | I/O  | port is enabled,<br>IRQ0 otherwise.<br>See Section 2.5. | Port SGPIOC0. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                 |  |  |

|                                      |                                                                                                                                                                                                                                                                              | 0    |                                                         | READI Message Data Out. Message data out (MDO4) are<br>output signals used for uploading OTM, BTM, DTM, and<br>read/write accesses. External latching of MDO occurs on<br>rising edge of MCKO. Eight signals are implemented. |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I    |                                                         | Interrupt Request 1. One of the eight external signals that can request, by means of the internal interrupt controller, a service routine from the RCPU.                                                                      |  |  |

| IRQ1 / RSV / SGPIOC1                 | 1                                                                                                                                                                                                                                                                            | 0    | IRQ1                                                    | Reservation. This signal is used, together with the address<br>bus, to indicate that the internal core initiated a transfer as a<br>result of a STWCX or a LWARX instruction.                                                 |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I/O  |                                                         | Port SGPIOC1. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                 |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I    | IRQ2                                                    | Interrupt Request 2. One of the eight external signals that can request, by means of the internal interrupt controller, a service routine from the RCPU.                                                                      |  |  |

| IRQ2/CR/SGPIOC2/<br>MTS <sup>2</sup> | 1                                                                                                                                                                                                                                                                            | I    |                                                         | Cancel Reservation. Instructs the MPC561/MPC563 to<br>clear its reservation because some other master has<br>touched its reserved space. An external bus snooper<br>asserts this signal.                                      |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I/O  |                                                         | Port SGPIOC2. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                 |  |  |

|                                      |                                                                                                                                                                                                                                                                              | 0    |                                                         | Memory Transfer Start. This is the transfer start signal from<br>the MPC561's memory controller that allows external<br>memory access by an external bus master.                                                              |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I    |                                                         | Interrupt Request 3. One of the eight external signals that can request, by means of the internal interrupt controller, a service routine from the RCPU.                                                                      |  |  |

| IRQ3/KR/RETRY/<br>SGPIOC3            | /RETRY /       I/O       IRQ3       Kill Reservation. In case of a bus cycle initiated by a STU instruction issued by the RCPU core to a non-local bus which the storage reservation has been lost, this signature used by the non-local bus interface to back-off the cycle |      |                                                         |                                                                                                                                                                                                                               |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I/O  |                                                         | Retry. Indicates to a master that the cycle is terminated but<br>should be repeated. As an input, it is driven by the external<br>slave to retry a cycle.                                                                     |  |  |

|                                      |                                                                                                                                                                                                                                                                              | I/O  |                                                         | Port SGPIOC3. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                 |  |  |

Signal Descriptions

| Signal Name                      | No. of<br>Signals | Туре | Function after<br>Reset <sup>1</sup>                                            | Description                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|----------------------------------|-------------------|------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                  |                   | I/O  |                                                                                 | MIOS14 GPIO 3. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                                                                                                         |  |  |  |  |  |

| MPIO32B3 / VFLS0 / MSEO          | 2                 | 0    | MPIO32B3<br>unless the<br>Nexus (READI)<br>port is enabled.<br>See Section 2.5. | Visible History Buffer Flush Status 0. This signal is output by<br>the MPC561/MPC563 to allow program instruction flow<br>tracking. It reports the number of instructions flushed from<br>the history buffer in the RCPU. See Chapter 23,<br>"Development Support," for details.                                       |  |  |  |  |  |

|                                  |                   | 0    |                                                                                 | $\overline{\text{MSEO}}$ . Message start/end out ( $\overline{\text{MSEO}}$ ) is an output signal which indicates when a message on the MDO signals has started, when a variable length packet has ended, and when the message has ended. External latching of $\overline{\text{MSEO}}$ occurs on rising edge of MCKO. |  |  |  |  |  |

|                                  |                   | I/O  |                                                                                 | MIOS14 GPIO 4. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                                                                                                         |  |  |  |  |  |

| MPIO32B4 / VFLS1                 | 1                 | 0    | MPIO32B4                                                                        | Visible History Buffer Flush Status 1. This signal is output by<br>the MPC561/MPC563 to allow program instruction flow<br>tracking. It reports the number of instructions flushed from<br>the history buffer in the RCPU. See Chapter 23,<br>"Development Support," for details.                                       |  |  |  |  |  |

|                                  |                   | I/O  | MPIO32B5<br>unless the                                                          | MIOS14 GPIO 5. Allows the signal to be used as a general-purpose input/output.                                                                                                                                                                                                                                         |  |  |  |  |  |

| MPIO32B5 / MDO5                  | 1                 | 0    | Nexus (READI)<br>port is enabled,<br>then MDO5.<br>See Section 2.5.             | READI Message Data Out. Message data out (MDO5) is an output signal used for uploading OTM, BTM, DTM, and read/write accesses. External latching of MDO occurs on rising edge of MCKO. Eight MDO signals are implemented.                                                                                              |  |  |  |  |  |

|                                  | 1                 | I/O  | MPIO32B6<br>unless the                                                          | MIOS14 GPIO 6. Allows the signal to be used as general-purpose input/output.                                                                                                                                                                                                                                           |  |  |  |  |  |

| MPIO32B6 / MPWM4 /<br>MDO6       |                   | I/O  | Nexus (READI)<br>port is enabled,<br>then MDO6.                                 | Pulse Width Modulation 4. These signals provide variable pulse width outputs at a wide range of frequencies.                                                                                                                                                                                                           |  |  |  |  |  |

|                                  |                   | 0    | See Section 2.5.                                                                | READI Message Data Out. Message data out (MDO6) is an output signal used for uploading OTM, BTM, DTM, and read/write accesses. External latching of MDO occurs on rising edge of MCKO. Eight MDO signals are implemented.                                                                                              |  |  |  |  |  |

| MPIO32B[7:9] /                   |                   | I/O  |                                                                                 | MIOS14 GPIO[7:9]. Allows these signals to be used as general-purpose input/outputs.                                                                                                                                                                                                                                    |  |  |  |  |  |

| MPWM[5, 20:21]                   | 3                 | I/O  | MPIO32B[7:9]                                                                    | Pulse Width Modulation [5, 20:21]. These signals provide variable pulse width outputs at a wide range of frequencies.                                                                                                                                                                                                  |  |  |  |  |  |

|                                  |                   | I/O  |                                                                                 | MIOS14 GPIO 10. This function allows the signals to be used as general-purpose inputs/outputs.                                                                                                                                                                                                                         |  |  |  |  |  |

| MPIO32B10 / PPM_TSYNC            | 1                 | 0    | MPIO32B10                                                                       | PPM_TSYNC. Synchronizes the data between the PPM and peripheral devices.                                                                                                                                                                                                                                               |  |  |  |  |  |

| MPIO32B11 / C_CNRX0 <sup>6</sup> | 1                 | I/O  | MPIO32B11                                                                       | MIOS14 GPIO 11. This function allows the signals to be used as general-purpose inputs/outputs.                                                                                                                                                                                                                         |  |  |  |  |  |

|                                  |                   | Ι    |                                                                                 | TouCAN_C Receive Data. This is the serial data input signal for the TouCAN_C module.                                                                                                                                                                                                                                   |  |  |  |  |  |

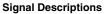

• Drive JCOMP/RSTI high

Nexus mode is exited by:

- Hold JCOMP/RSTI low to reset Nexus port

- Hold TMS/EVTI high to disable Nexus mode at least 4 clocks before driving JCOMP/RSTI high

- Drive JCOMP/RSTI high

Figure 2-6. Debug Mode Selection (Nexus)

# 2.6 Reset State

During reset, a 130-µA (maximum) resistor "weakly pulls" all input signals, with the exception of the power-supply and clock-related signals, to a value based on conditions described in Appendix F, "Electrical Characteristics." In reset state, all I/O signals become inputs, and all outputs (except for CLKOUT, HRESET, and SRESET) are pulled only by the pull-up/pull-down.

# 2.6.1 Signal Functionality Configuration Out of Reset

The reset configuration word (RCW) defines the post-reset functionality of some multiplexed signals. For details on these signals and how they are configured, refer to Section 7.5.2, "Hard Reset Configuration Word."

The 2.6-V bus related signals have selectable output buffer drive strengths that are controlled by the COM0 bit in the USIU's system clock and reset control register (SCCR). The control is as follows:

0 = 2.6-V bus signals full drive (50-pF load)

1 = 2.6-V bus signals reduced drive (25-pF load)

# 2.6.2 Signal State During Reset

While HRESET is asserted, the reset-configuration value is latched from the data bus into various bits on the part. The function of many signals depends upon the value latched. If the value on the data bus changes, then the function of various signals may also change. This is especially true if the reset configuration word (RCW) comes from the Flash, because the Flash does not drive the RCW until 256 clocks after the start of

**Central Processing Unit**

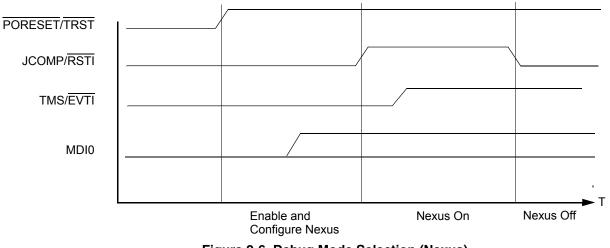

| Figure 3-15. Machine Status Save/Restore | e Register 1 | 1 (SRR1) |

|------------------------------------------|--------------|----------|

|------------------------------------------|--------------|----------|

In general, when an exception occurs, SRR1[0:15] are loaded with exception-specific information, and MSR[16:31] are placed into SRR1[16:31].

## 3.9.8 General SPRs (SPRG0–SPRG3)

SPRG0–SPRG3, SPRs 272-275, are provided for general operating system use, such as fast-state saves and multiprocessor-implementation support. SPRG0–SPRG3 are shown below.

|       | MSB<br>0 | 4 | 0 | 2 | 4 | E | 6 | 7 | 0 | 0 | 10 | <br>10 | 10 | 14 | 15  | 16   | 17  | 10 | 10 | 20 | 01 | 22 | 22 | 24 | 25 | 26 | 07 | 20 | 20 | 20 | LSB |

|-------|----------|---|---|---|---|---|---|---|---|---|----|--------|----|----|-----|------|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|

| Ī     | 0        |   | 2 | 3 | 4 | э | 0 | 1 | 0 | 9 | 10 | <br>12 | 13 | 14 |     |      |     | 10 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 20 | 21 | 20 | 29 | 30 | 31  |

|       |          |   |   |   |   |   |   |   |   |   |    |        |    |    | S   | PR   | G0  |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

|       |          |   |   |   |   |   |   |   |   |   |    |        |    |    | S   | PR   | G1  |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

|       | SPRG2    |   |   |   |   |   |   |   |   |   |    |        |    |    |     |      |     |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

|       |          |   |   |   |   |   |   |   |   |   |    |        |    |    | S   | PR   | G3  |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

| Reset |          |   |   |   |   |   |   |   |   |   |    |        |    |    | Unc | char | nge | d  |    |    |    |    |    |    |    |    |    |    |    |    |     |

Figure 3-16. SPRG0–SPRG3 — General Special-Purpose Registers 0–3

Uses for SPRG0–SPRG3 are shown in Table 3-13.

#### Table 3-13. Uses of SPRG0–SPRG3

| Register | Description                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRG0    | Software may load a unique physical address in this register to identify an area of memory reserved for use by the exception handler. This area must be unique for each processor in the system.        |

| SPRG1    | This register may be used as a scratch register by the exception handler to save the content of a GPR. That GPR then can be loaded from SPRG0 and used as a base register to save other GPRs to memory. |

| SPRG2    | This register may be used by the operating system as needed.                                                                                                                                            |

| SPRG3    | This register may be used by the operating system as needed.                                                                                                                                            |

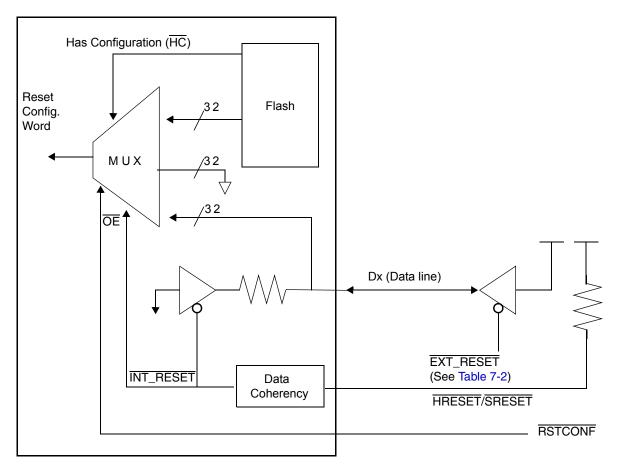

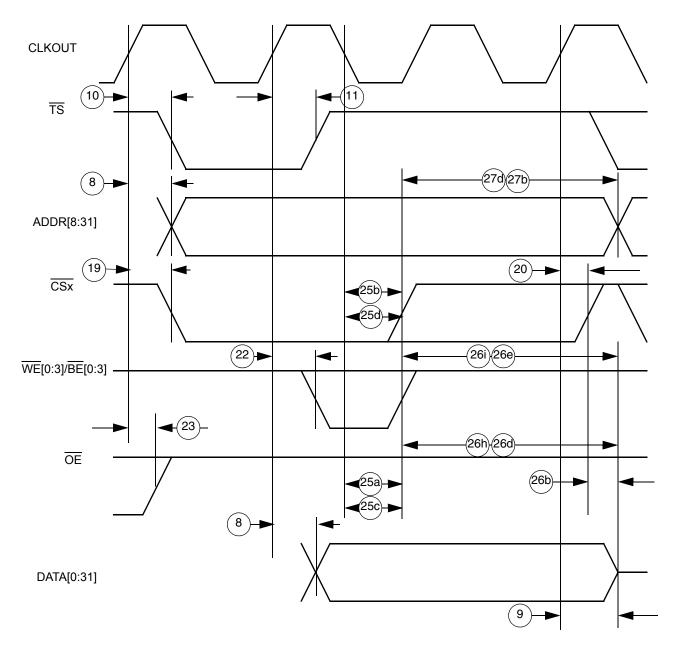

Figure 7-2. Reset Configuration Basic Scheme

During the assertion of the PORESET input signal, the chip assumes the default reset configuration. This assumed configuration changes if the input signal RSTCONF is asserted when the PORESET is negated or the CLKOUT starts to oscillate. To ensure that stable data is sampled, the hardware configuration is sampled every eight clock cycles on the rising edge of CLKOUT with a double buffer. The setup time required for the data bus is approximately 15 cycles (defined as Tsup in the following figures) and the maximum rise time of HRESET should be less than six clock cycles. In systems where an external reset configuration word and the TEXP output function are both required, RSTCONF should be asserted until SRESET is negated.

Figure 7-3 to Figure 7-6 provide sample reset configuration timings.

NOTE

Timing diagrams in the following figures are not to scale.

#### Table 7-5. RCW Bit Descriptions (continued)

| Bits  | Name | Description                                                                                                                                                                                                                                                                                               |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24:25 | OERC | Other Exceptions Relocation Control — These bits effect only if ETRE was enabled. See<br>Table 4-2. Relocation offset:<br>00 Offset 0<br>01 Offset 64 Kbytes<br>10 Offset 512 Kbytes<br>11 Offset to 0x003F E000                                                                                          |

| 26:27 | _    | Reserved                                                                                                                                                                                                                                                                                                  |

| 28:30 | ISB  | Internal Space Base Select — This field defines the initial value of the ISB field in the IMMR register. A detailed description is in Table 6-12. The default state is that the internal memory map is mapped to start at address 0x0000_0000. This bit must not be high in the reset configuration word. |

| 31    | DME  | <ul> <li>Dual Mapping Enable — This bit determines whether Dual mapping of the internal Flash is enabled. For a detailed description refer to Table 10-11. The default state is that dual mapping is disabled.</li> <li>0 Dual mapping disabled</li> <li>1 Dual mapping enabled</li> </ul>                |

<sup>1</sup> Bit 15 always comes from the internal Flash Reset Configuration Word (MPC563 only).

<sup>2</sup> This bit should not be set on the MPC561/MPC562.

<sup>3</sup> This bit is HC if read from the internal Flash Reset Configuration Word. See Section 21.2.3.1, "Reset Configuration Word (UC3FCFIG)."

<sup>4</sup> Available only on the MPC562/MPC564, software should write "0" to this bit for MPC561/MPC563.

## 7.5.3 Soft Reset Configuration

When a soft reset event occurs, the MPC561/MPC563 reconfigures the development port. Refer to Chapter 23, "Development Support," for details.

#### **QADC64E Enhanced Mode Operation**

indicating that the module is locked in legacy mode. In order to change the value of the FLIP bit, the operating mode must first be unlocked by setting the LOCK bit. Only then can the FLIP bit be changed. Finally, the LOCK bit must be cleared again to protect the state of the FLIP bit from future writes.

- 1. Write LOCK = 1 to unlock operating mode bit.

- 2. Modify the value of FLIP as required.

- FLIP = 0 legacy mode enabled

- FLIP = 1 enhanced mode enabled

- 3. Write LOCK = 0 and new FLIP bit value to preserve the value of FLIP bit

- Example 1: switching from legacy mode to enhanced mode

- QADCMCR = 0x280; LOCK =1, SUPV = 1

- QADCMCR = 0x380; LOCK =1, write FLIP = 1, SUPV = 1

- QADCMCR = 0x180; LOCK = 0, FLIP = 1, SUPV = 1

Subsequent writes to the FLIP bit will have no effect while LOCK = 0.

- Example 2: switching from enhanced mode to legacy mode

- QADCMCR = 0x280 or 0x380; LOCK = 1, SUPV =1 (Can write FLIP = x since value will not change)

- QADCMCR = 0x280; LOCK = 1, FLIP = 0, SUPV = 1

- QADCMCR = 0x080; LOCK = 0, FLIP = 0, SUPV =1

## 14.3.1.4 Supervisor/Unrestricted Address Space

The QADC64E memory map is divided into two segments: supervisor-only data space and assignable data space. Access to supervisor-only data space is permitted only when the software is operating in supervisor access mode. Assignable data space can be either restricted to supervisor-only access or unrestricted to both supervisor and user data space accesses. The SUPV bit in the QADCMCR designates the assignable space as supervisor or unrestricted.

The following information applies to accesses to address space located within the module's 16-bit boundaries and where the response is a bus error. See Table 14-6 for more information.

- Attempts to read a supervisor-only data space when not in the supervisor access mode and SUPV = 1, causes the bus master to assert a bus error condition. No data is returned. If SUPV = 0, the QADC64E asserts a bus error condition and no data is returned.

- Attempts to write to supervisor-only data space when not in the supervisor access mode and SUPV = 1, causes the bus master to assert a bus error condition. No data is written. If SUPV = 0, the QADC64E asserts a bus error condition and the register is not written.

- Attempts to read unimplemented data space in the unrestricted access mode and SUPV = 1, causes the bus master to assert a bus error condition and no data is returned. In all other attempts to read unimplemented data space, the QADC64E causes a bus error condition and no data is returned.

- Attempts to write unimplemented data space in the unrestricted access mode and SUPV= 1, causes the bus master to assert a bus error condition and no data is written. In all other

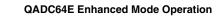

16-Bit Aligned Access (ISIZ = 10, A0 = 0)

QADC64E Bus CYC ACC

Figure 14-24. Bus Cycle Accesses

Byte access to an even address of a QADC64E location is shown in the top illustration of Figure 14-24. In the case of write cycles, byte 1 of the register is not disturbed. In the case of a read cycle, the QADC64E provides both byte 0 and byte 1.

Byte access to an odd address of a QADC64E location is shown in the center illustration of Figure 14-24. In the case of write cycles, byte 0 of the register is not disturbed. In the case of read cycles, the QADC64E provides both byte 0 and byte 1.

16-bit accesses to an even address read or write byte 0 and byte 1 as shown in the lowest illustration of Figure 14-24. The full 16 bits of data is written to and read from the QADC64E location with each access.

16-bit accesses to an odd address require two bus cycles; one byte of two different 16-bit QADC64E locations is accessed. The first bus cycle is treated by the QADC64E as an 8-bit read or write of an odd address. The second cycle is an 8-bit read or write of an even address. The QADC64E address space is organized into 16-bit even address locations, so a 16-bit read or write of an odd address obtains or provides the lower half of one QADC64E location, and the upper half of the following QADC64E location.

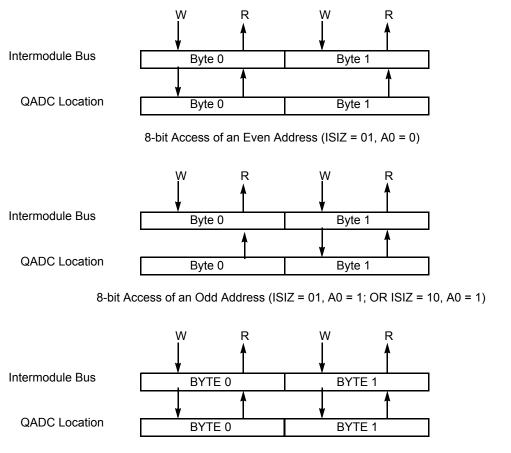

Since the sample amplifier is powered by  $V_{DDA}$  and  $V_{SSA}$ , it can accurately transfer input signal levels up to but not exceeding  $V_{DDA}$  and down to but not below  $V_{SSA}$ . If the input signal is outside of this range, the output from the sample amplifier is clipped.

In addition,  $V_{RH}$  and  $V_{RL}$  must be within the range defined by  $V_{DDA}$  and  $V_{SSA}$ . As long as  $V_{RH}$  is less than or equal to  $V_{DDA}$  and  $V_{RL}$  is greater than or equal to  $V_{SSA}$  and the sample amplifier has accurately transferred the input signal, resolution is ratiometric within the limits defined by  $V_{RL}$  and  $V_{RH}$ . If  $V_{RH}$  is greater than  $V_{DDA}$ , the sample amplifier can never transfer a full-scale value. If  $V_{RL}$  is less than  $V_{SSA}$ , the sample amplifier can never transfer a zero value.

Figure 14-48 shows the results of reference voltages outside the range defined by  $V_{DDA}$  and  $V_{SSA}$ . At the top of the input signal range,  $V_{DDA}$  is 10 mV lower than  $V_{RH}$ . This results in a maximum obtainable 10-bit conversion value of 0x3FE. At the bottom of the signal range,  $V_{SSA}$  is 15 mV higher than  $V_{RL}$ , resulting in a minimum obtainable 10-bit conversion value of three.

Figure 14-48. Errors Resulting from Clipping

## 14.6.3.1 Analog Supply Filtering and Grounding

Two important factors influencing performance in analog integrated circuits are supply filtering and grounding. Generally, digital circuits use bypass capacitors on every  $V_{DD}/V_{SS}$  signal pair. This applies to analog sub-modules also. The distribution of power and ground is equally important.

**Queued Serial Multi-Channel Module**

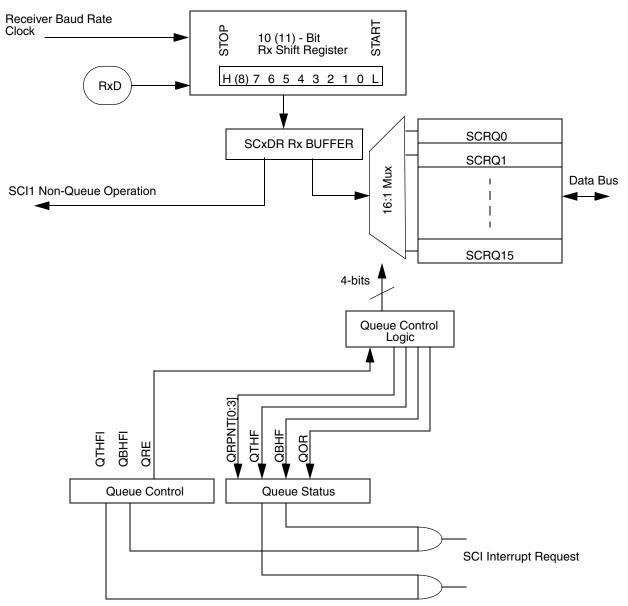

## 15.8.8 QSCI1 Receiver Block Diagram

The block diagram of the enhancements to the SCI receiver is shown below in Figure 15-38.

Figure 15-38. Queue Receiver Block Enhancements

## 15.8.9 QSCI1 Additional Receive Operation Features

Additional QSCI1 features include:

- Available on a single SCI channel (SCI1) implemented by the queue receiver enable (QRE) bit set by software. When the queue is enabled, software should ignore the RDRF bit.

- When the queue is disabled (QRE = 0), the SCI functions in single buffer receive mode (as originally designed) and RDRF and OR function as previously defined. Locations SCRQ[0:15] can

# 17.2 MIOS14 Key Features

The basic features of the MIOS14 are as follows:

- Modular architecture at the silicon implementation level

- Disable capability in each submodule to allow power saving when its function is not needed

- Six 16-bit counter buses to allow action submodules to use counter data

- When not used for timing functions, every channel signal can be used as a port signal: I/O, output only or input only, depending on the channel function.

- Submodules' signal status bits reflect the status of the signal

- MIOS14 counter prescaler submodule (MCPSM):

- Centralized counter clock generator

- Programmable 4-bit modulus down-counter

- Wide range of possible division ratios: 2 through 16

- Count inhibit under software control

- MIOS14 modulus counter submodule (MMCSM):

- Programmable 16-bit modulus up-counter with built-in programmable 8-bit prescaler clocked by MCPSM output.

- Maximum increment frequency of the counter:

- Clocked by the internal MCPSM output:  $f_{SYS} / 2$

- Clocked by the external signal:  $f_{SYS} / 4$

- Flag setting and possible interrupt generation on overflow of the up-counter

- Time counter on internal clock with interrupt capability after a pre-determined time

- Optional signal usable as an external event counter (pulse accumulator) with overflow and interrupt capability after a pre-determined number of external events.

- Usable as a regular free-running up-counter

- Capable of driving a dedicated 16-bit counter bus to provide timing information to action submodules (the value driven is the contents of the 16-bit up-counter register)

- Optional signal to externally force a load to the counter with modulus value

- MIOS14 double action submodule (MDASM):

- Versatile 16-bit dual action unit allowing two events to occur before software intervention is required

- Six software selectable modes allowing the MDASM to perform pulse width and period measurements, PWM generation, single input capture and output compare operations as well as port functions

- Software selection of one of the six possible 16-bit counter buses used for timing operations

- Flag setting and possible interrupt generation after MDASM action completion

- Software selection of output pulse polarity

- Software selection of totem-pole or open-drain output

- Software readable output signal status

MPC561/MPC563 Reference Manual, Rev. 1.2

Bits

Name

| Table 17-29. MPWMSCR Bit Descriptions                                                |

|--------------------------------------------------------------------------------------|

| Description                                                                          |

| Pin input status bit — The PIN bit reflects the state present on the MP <sup>1</sup> |

| 2.00 | Hame |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | PIN  | Pin input status bit — The PIN bit reflects the state present on the MPWMSM signal. The software can thus monitor the pin state.<br>The PIN bit is a read-only bit. Writing to the PIN bit has no effect.                                                                                                                                                                                                                         |

| 1    | DDR  | Data direction register — The DDR bit indicates the direction for the signal when the PWM<br>function is not used (disable mode).<br>0 signal is in input.<br>1 signal is in output.<br>The DDR bit is cleared by reset.<br>Table 17-30 lists the different uses for the polarity (POL) bit, the enable (EN) bit and the data<br>direction register (DDR) bit.                                                                    |

| 2    | FREN | <ul> <li>Freeze enable bit — This active high read/write control bit enables the MPWMSM to recognize the freeze signal on the MIOB.</li> <li>0 MPWMSM not frozen even if the MIOB freeze line is active.</li> <li>1 MPWMSM frozen if the MIOB freeze line is active.</li> <li>The FREN is cleared by reset.</li> </ul>                                                                                                            |

| 3    | TRSP | Transparent mode — The TRSP bit indicates that the MPWMSM is in transparent mode. In transparent mode, when the software writes to either the MPWMPERR or MPWMPULR1 register the value written is immediately transferred to the counter or register MPWMPULR2 respectively. 0 Double-buffered mode.<br>1 Transparent mode.<br>The TRSP bit is cleared by reset.                                                                  |

| 4    | POL  | Output polarity control bit — The POL bit works in conjunction with the EN bit and controls whether the MPWMSM drives the signal with the direct or the inverted value of the output flip-flop. Table 17-30 lists the different uses for the polarity (POL) bit, the enable (EN) bit and the data direction register (DDR) bit.                                                                                                   |

| 5    | EN   | <ul> <li>Enable PWM signal generation — The EN bit defines whether the MPWMSM generates a PWM signal or is used as an I/O channel:</li> <li>0 PWM generation disabled (signal can be used as I/O).</li> <li>1 PWM generation enabled (the signal is in output mode).</li> <li>Each time the submodule is enabled, the value of CP is loaded into the prescaler.</li> <li>The EN bit is cleared by reset.</li> </ul>               |

| 6:7  | —    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8:15 | СР   | Clock prescaler — This 8-bit read/write data register stores the modulus value for loading into the built-in 8-bit clock prescaler. The value loaded defines the divide ratio for the signal that clocks the MPWMSM. The new value is loaded into the prescaler counter on the prescaler counter overflow, or upon the EN bit of the MPWMSCR being set.<br>Table 17-31 gives the clock divide ratio according to the value of CP. |

| Table 17-30. PWMSM | Output Signal Polarity  | Selection |

|--------------------|-------------------------|-----------|

|                    | output orginal i olarit |           |

| Control Bits |    | Signal Signal State |           | Periodic Edge | Variable Edge | Optional      |              |  |

|--------------|----|---------------------|-----------|---------------|---------------|---------------|--------------|--|

| POL          | EN | DDR                 | Direction | Signal State  | Feriodic Edge | variable Euge | Interruption |  |

| 0            | 0  | 0                   | Input     | INPUT         | —             | —             | —            |  |

| 0            | 0  | 1                   | Output    | Always Low    | —             | —             | —            |  |

| 0            | 1  | Х                   | Output    | High Pulse    | Falling Edge  | Rising Edge   | Falling Edge |  |

| 1            | 0  | 0                   | Input     | INPUT         | —             | —             | —            |  |

CDR3 Flash (UC3F) EEPROM

| Table 21-4. UC3FMCRE Bit Descriptions ( | continued) |

|-----------------------------------------|------------|

|-----------------------------------------|------------|

| Bits  | Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:5   | SBDATA        | Small block data space. Each small array block of the UC3F EEPROM may be mapped into data<br>or both data and instruction address space. When a small array block is mapped into data<br>address space, SBDATA[M] = 1, only data accesses will be allowed. When a small array block<br>is mapped into both data and instruction address space, SBDATA[M] = 0, both data and<br>instruction accesses will be allowed.<br>If SBEN[M] = 0, the corresponding small block M is logically part of the host block and<br>SBDATA[M] has no effect. Instead, the corresponding DATA[M] bit will be used to determine if<br>the small block is mapped to Data or to both Data and Instruction address space.<br>Like the DATA bits, the SBDATA bits are not actually used in the UC3F EEPROM module but are<br>used by the BIU to determine access restrictions to the UC3F array. Block addresses are<br>decoded in the BIU to determine which small array block is selected, and the selected small<br>block's SBDATA bit is compared with the address space attributes to determine validity of an<br>array access.<br>0 small block M is placed in both Data and Instruction address spaces<br>1 small block M is placed in Data address space |

| 6:7   | SBPROTEC<br>T | Small block protect. Each small block of the UC3F EEPROM can be individually protected from program or erase operation. The UC3F will perform all program and erase interlocks and even complete the program or erase sequence, but the program and erase voltages are not applied to locations within the protected small block(s).<br>0 small block M is unprotected<br>1 small block M is protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8:9   | _             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10:15 | BIU           | BIU configuration bits. These register bits are reserved for BIU functionality and are strictly outputs from the UC3F EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16:18 | MEMSIZ        | Memory size. The MEMSIZ field is used to indicate the UC3F array size. The MEMSIZ bits are<br>read only and writes have no effect.<br>000 UC3F array is 64 Kbytes<br>001 UC3F array is 128 Kbytes<br>010 UC3F array is 192 Kbytes<br>011 UC3F array is 256 Kbytes<br>100 unused<br>101 UC3F array is 512 Kbytes<br>110 unused<br>111 unused<br>The Flash module on the MPC563 is 512 Kbytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19    | BLK           | Block size. The BLK bit is used to indicate the array block size used in the UC3F array. The BLK<br>bit is read only and writes have no effect.<br>0 array block size is 32 Kbytes<br>1 block size is 64 Kbytes NOTE: All blocks are 64 Kbytes (i.e. BLK is always set)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20    | MAP           | Array address mapping. The MAP bit is used to indicate the UC3F array address mapping within a $2^{N}$ address space. The MAP bit is read only and writes have no effect. The MAP bit is more useful when the UC3F array is a non- $2^{N}$ size.<br>When MAP = 0, the UC3F array is mapped to the bottom (starting at address 0) of the $2^{N}$ space in which the array resides. For modules with $2^{N}$ array sizes, the MAP bit is always set to 0.<br>When MAP = 1, the UC3F array is mapped to the top (ending at address all \$F's) of the $2^{N}$ space in which the array resides.<br>0 UC3F array is mapped to bottom of $2^{N}$ address space<br>1 UC3F array is mapped to top of $2^{N}$ address space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**Development Support**

| Dite Maximum |                      | Description                                                                              | Function                                                                                                                                                         |                                                 |  |  |

|--------------|----------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| Bits         | Mnemonic Description |                                                                                          | Non-compressed mode <sup>1</sup>                                                                                                                                 | Compressed Mode <sup>2</sup>                    |  |  |

| 20           | SIWP0EN              | Software trap enable selection of the 1st I-bus watchpoint                               | 0 = trap disabled (reset value)<br>1 = trap enabled                                                                                                              |                                                 |  |  |

| 21           | SIWP1EN              | Software trap enable selection of the 2nd I-bus watchpoint                               | *                                                                                                                                                                |                                                 |  |  |

| 22           | SIWP2EN              | Software trap enable selection of the 3rd I-bus watchpoint                               | *                                                                                                                                                                |                                                 |  |  |

| 23           | SIWP3EN              | Software trap enable selection of the 4th I-bus watchpoint                               |                                                                                                                                                                  |                                                 |  |  |

| 24           | DIWPOEN              | Development port trap enable<br>selection of the 1st I-bus<br>watchpoint (read only bit) | 0 = trap disabled (reset value)<br>1 = trap enabled                                                                                                              |                                                 |  |  |

| 25           | DIWP1EN              | Development port trap enable<br>selection of the 2nd I-bus<br>watchpoint (read only bit) | *                                                                                                                                                                |                                                 |  |  |

| 26           | DIWP2EN              | Development port trap enable<br>selection of the 3rd I-bus<br>watchpoint (read only bit) | *                                                                                                                                                                |                                                 |  |  |

| 27           | DIWP3EN              | Development port trap enable<br>selection of the 4th I-bus<br>watchpoint (read only bit) | *                                                                                                                                                                |                                                 |  |  |

| 28           | IFM                  | Ignore first match, only for I-bus breakpoints                                           | 0 = Do not ignore first match, u<br>1 = Ignore first match (used fo                                                                                              |                                                 |  |  |

| 29:31        | ISCT_SER             | RCPU serialize control and<br>Instruction fetch show cycle                               | These bits control serialization cycles. See Table 23-27 for th NOTE: Changing the instruction starts to take effect only from the actual <b>mtspr</b> to ICTRL. | e bit definitions.<br>on show cycle programming |  |  |

### Table 23-26. ICTRL Bit Descriptions (continued)

<sup>1</sup> Refer to Appendix A, "MPC562/MPC564 Compression Features," for code compression-specific functionality.

<sup>2</sup> MPC562/MPC564 only.

### Table 23-27. ISCT\_SER Bit Descriptions

| Serialize<br>Control<br>(SER) | Instruction<br>Fetch<br>(ISCTL) | Functions Selected                                                                                      |

|-------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------|

| 0                             | 00                              | RCPU is fully serialized and show cycles will be performed for all fetched instructions (reset value)   |

| 0                             | 01                              | RCPU is fully serialized and show cycles will be performed for all changes in the program flow          |

| 0                             | 10                              | RCPU is fully serialized and show cycles will be performed for all indirect changes in the program flow |

| 0                             | 11                              | RCPU is fully serialized and no show cycles will be performed for fetched instructions                  |

### MPC561/MPC563 Reference Manual, Rev. 1.2

| Message Name                                                          | MinimumMaximuPacketm PacketSizeSize(bits)(bits) |    | Direction |                                                                                                                                                                                                                                                                                                                                                                          |                  |  |

|-----------------------------------------------------------------------|-------------------------------------------------|----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| Program Trace —                                                       | 6                                               | 6  | Fixed     | TCODE number = 12 (0xC)                                                                                                                                                                                                                                                                                                                                                  | From<br>Device   |  |

| Indirect Branch<br>Synchronization <sup>2</sup><br>Message (PTSM = 1) | 1                                               | 8  | Variable  | number of sequential instructions executed since last taken branch                                                                                                                                                                                                                                                                                                       |                  |  |

|                                                                       | 1                                               | 23 | Variable  | full target address                                                                                                                                                                                                                                                                                                                                                      |                  |  |

| Data Trace —                                                          | 6                                               | 6  | Fixed     | TCODE number = 13 (0xD)                                                                                                                                                                                                                                                                                                                                                  | From             |  |

| Data Write<br>Synchronization                                         | 1                                               | 1  | Variable  | number of messages canceled                                                                                                                                                                                                                                                                                                                                              | Device           |  |

| Message                                                               | 1                                               | 25 | Variable  | full target address                                                                                                                                                                                                                                                                                                                                                      |                  |  |

|                                                                       | 8                                               | 32 | Variable  | data write value (8, 16, 32 bits)                                                                                                                                                                                                                                                                                                                                        |                  |  |

| Data Trace —                                                          | 6                                               | 6  | Fixed     | TCODE number = 14 (0xE)                                                                                                                                                                                                                                                                                                                                                  | From             |  |

| Data Read<br>Synchronization                                          | 1                                               | 1  | Variable  | number of messages canceled                                                                                                                                                                                                                                                                                                                                              | Device           |  |

| Message                                                               | 1                                               | 25 | Variable  | full target address                                                                                                                                                                                                                                                                                                                                                      |                  |  |

|                                                                       | 8                                               | 32 | Variable  | data read value (8, 16, 32 bits)                                                                                                                                                                                                                                                                                                                                         |                  |  |

| Watchpoint                                                            | 6 6 Fixed                                       |    | Fixed     | TCODE number = 15 (0xF)                                                                                                                                                                                                                                                                                                                                                  | From             |  |

| Message                                                               | 6                                               | 6  | Fixed     | number indicating watchpoint source                                                                                                                                                                                                                                                                                                                                      | Device           |  |

| Auxiliary Access —<br>Device Ready for<br>Upload/Download<br>Message  | 6                                               | 6  | Fixed     | TCODE number = 16 (0x10)                                                                                                                                                                                                                                                                                                                                                 | From<br>Device   |  |

| Auxiliary Access —                                                    | 6                                               | 6  | Fixed     | TCODE number = 17 (0x11)                                                                                                                                                                                                                                                                                                                                                 | From             |  |

| Upload Request<br>Message                                             | 8                                               | 8  | Fixed     | opcode to enable selected configuration, status or data upload from MCU                                                                                                                                                                                                                                                                                                  | Tool             |  |

| Auxiliary Access —                                                    | 6                                               | 6  | Fixed     | TCODE number = 18 (0x12)                                                                                                                                                                                                                                                                                                                                                 | From             |  |

| Download Request<br>Message                                           | 8                                               | 8  | Fixed     | opcode to enable selected configuration or data download to MCU                                                                                                                                                                                                                                                                                                          | Tool             |  |

|                                                                       | 8                                               | 80 | Variable  | Depending upon opcode selected for<br>download, information to be downloaded<br>to device will vary.                                                                                                                                                                                                                                                                     |                  |  |

| Auxiliary Access —                                                    | 6                                               | 6  | Fixed     | TCODE number = 19 (0x13)                                                                                                                                                                                                                                                                                                                                                 | From             |  |

| Upload/Download<br>Information Message                                | 8                                               | 80 | Variable  | <ol> <li>For an access, depending on word size<br/>selected (SZ field in RWA register),<br/>variable-length packets of information (10,<br/>18, or 34 bits) will be<br/>uploaded/downloaded from/to device.</li> <li>Depending upon opcode selected for<br/>upload from internal READI registers,<br/>information to be uploaded to the device<br/>will vary.</li> </ol> | Device /<br>Tool |  |

Table 24-19. Public Messages Supported (continued)

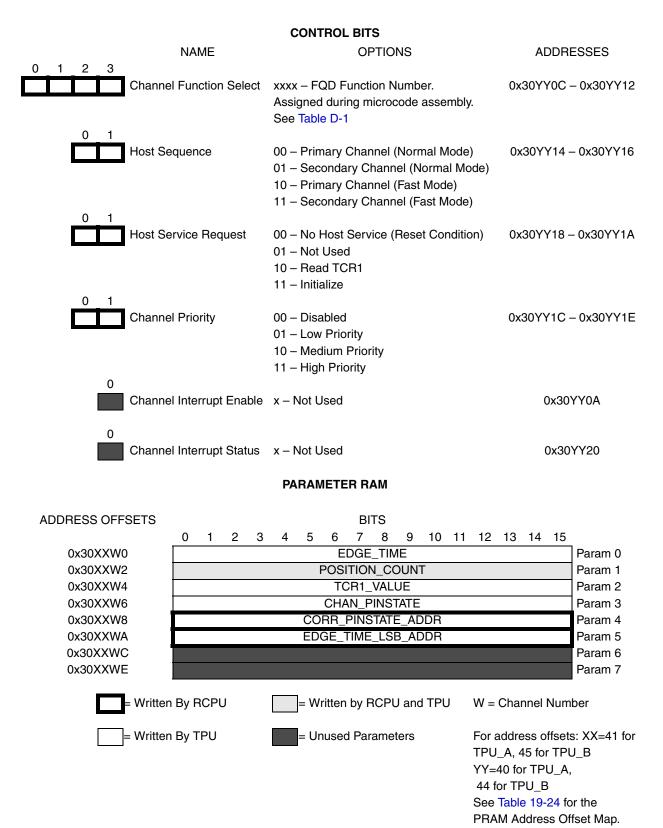

CONTROL BITS

See Table 19-24 for the PRAM Address Offset Map.

Figure D-9. NITC Parameters

## D.8 Multiphase Motor Commutation (COMM)

The COMM function generates phase commutation signals for a variety of brushless motors, including three-phase brushless direct current motors. It derives the commutation state directly from the position decoded in FQD, eliminating the need for hall effect sensors.

The state sequence is implemented as a user-configurable state machine, providing a flexible approach with other general applications. A RCPU offset parameter is provided to allow the RCPU to advance or retard all swtiching angles on the fly. This feature is useful for torque maintenance at high speeds. See Freescale TPU Progamming Note *Multiphase Motor Commutation TPU Function (COMM), (TPUPN09/D).*

Figure D-10 and Figure D-10 show all of the host interface areas for the COMM function.

**TPU3 ROM Functions**

Figure D-22. FQD Parameters — Primary Channel

MPC561/MPC563 Reference Manual, Rev. 1.2

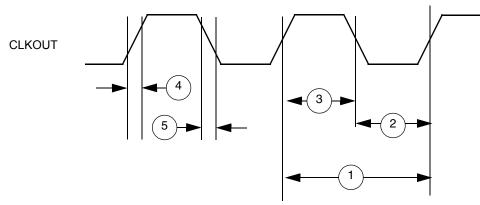

**Electrical Characteristics**

Electrical Characteristics

# F.15 **QSMCM Electrical Characteristics**

## Table F-17. QSPI Timing

Note: ( $T_A = T_L$  to  $T_{H_{,}}$  50 pF load on all QSPI pins unless otherwise noted)

| Num | Function                                                                                                                                       | Symbol                                                | Min                 | Max                                        | Unit           |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|--------------------------------------------|----------------|

| 108 | Operating Frequency <sup>1</sup><br>Master<br>Slave                                                                                            | f <sub>OP</sub>                                       |                     | f <sub>SYS</sub> /4<br>f <sub>SYS</sub> /4 | Hz<br>Hz       |

| 109 | Cycle Time<br>Master<br>Slave                                                                                                                  | t <sub>QCYC</sub>                                     | 4*TC<br>4*TC        | 510 * TC <sup>2</sup>                      | ns<br>ns       |

| 110 | Enable Lead Time<br>Master<br>Slave                                                                                                            | t <sub>LEAD</sub>                                     | 2*TC<br>2*TC        | 128 * TC                                   | ns<br>ns       |

| 111 | Enable Lag Time<br>Master<br>Slave                                                                                                             | t <sub>LAG</sub>                                      |                     | SCK/2                                      | ns<br>ns       |

| 112 | Clock (SCK) High or Low Time<br>Master<br>Slave <sup>3</sup>                                                                                   | t <sub>SW</sub>                                       | 2*TC– 60<br>2*TC– n | 255 * TC<br>—                              | ns<br>ns       |

| 113 | Sequential Transfer Delay<br>Master<br>Slave (Does Not Require Deselect)                                                                       | t <sub>TD</sub>                                       | 17*TC<br>13*TC      | 8192 * TC<br>-                             | ns<br>ns       |

| 114 | Data Setup Time (Inputs)<br>Master<br>Slave                                                                                                    | t <sub>SU</sub>                                       | 30<br>20            | -                                          | ns<br>ns       |

| 115 | Data Hold Time (Inputs)<br>Master<br>Slave                                                                                                     | t <sub>HI</sub>                                       | 0<br>20             | -                                          | ns<br>ns       |