# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | PowerPC                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 56MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI, UART/USART                                 |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 56                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 2.7V                                                           |

| Data Converters            | A/D 32x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 388-BBGA                                                              |

| Supplier Device Package    | 388-PBGA (27x27)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc564mzp56r2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Central Processing Unit**

| rlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwmm (rlwnm.)rA,rS,rB,MB,MERotate Left Word then AND with Masksc—System Callsiw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Mordsraw (sraw.)rA,rS,rBShift Right MordstburS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Floating-Point DoublestfdufrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single                                                                                                      | Mnemonic                      | Operand Syntax | Name                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|-------------------------------------------------|

| neg (neg. nego nego.)fD;rANegatenor (nor.)rA,rS,rBNORor (or.)rA,rS,rBORor (or.)rA,rS,rBOR with Complementoric (orc.)rA,rS,UIMMOR ImmediateorisrA,rS,UIMMOR Immediate Shiftedfi—Return from Interruptrlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwim (rlwinn.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with Maskrlwim (rlwinn.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with UpdatestbuxrS,rA,rBStore Floating-Point Double with UpdatestdurS,rA,rBStore Floating-Point Double with UpdatestduxfrS,rBStore Floating-Point Double with UpdatestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rB<                                                                                        | mullw (mullw. mullwo mullwo.) | rD,rA,rB       | Multiply Low                                    |

| norfA;fS;rBNORor(or)fA;fS;rBORor(orc.)fA;fS;rBORor(orc.)fA;fS;rBOR with ComplementorifA;fS;UIMMOR ImmediateorisfA;fS;UIMMOR Immediate Shiftedffi—Return from Interruptrtwimi (rlwimi.)rA;fS;SH,MB,MERotate Left Word Immediate then Mask Insertrtwimi (rlwimi.)rA;fS,GH,MB,MERotate Left Word Immediate then AND with<br>Maskftwmm (rlwinm.)rA;fS,rB,MB,MERotate Left Word Immediate then AND with Masksc—System Callslw (slw.)rA;fS,rBShift Left Wordsraw (sraw.)rA;fS,rBShift Right Algebraic Wordsrawi (srawi.)rA;fS,rBShift Right Algebraic Wordsrawi (srawi.)rA;fS,rBShift Right Algebraic WordstburS,d(rA)Store BytestburS,d(rA)Store BytestburS,d(rA)Store BytestburS,rA,rBStore Floating-Point DoublestdufrS,d(rA)Store Floating-Point DoublestdufrS,rBStore Floating-Point Double with UpdatestduxfrS,rBStore Floating-Point Double with UpdatestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point SinglestduxfrS,rBStore Floating-Point Singlestduxfr                                                                                                                                                  | nand (nand.)                  | rA,rS,rB       | NAND                                            |

| orrA,rS,rBORorc(orc.)rA,rS,rBOR with ComplementorirA,rS,UIMMOR ImmediateorisrA,rS,UIMMOR Immediate Shiftedfli—Return from Interruptrtwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrtwimi (rlwim.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrtwim (rlwinm.)rA,rS,rB,MB,MERotate Left Word then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic WordstburS,d(rA)Store BytestburS,d(rA)Store BytestburS,rA,rBStore BytestbuxrS,rA,rBStore Floating-Point DoublestfdurfS,rGStore Floating-Point DoublestfduxrfS,rBStore Floating-Point Double with UpdatestfduxrfS,rBStore Floating-Point Double with UpdatestfduxrfS,rBStore Floating-Point Double with UpdatestfduxrfS,rBStore Floating-Point Double with UpdatestfuxrfS,rBStore Floating-Point Double with UpdatestfuxrfS,rBStore Floating-Point Double with UpdatestfuxrfS,rBStore Floating-Point Double with UpdatestfuxrfS,rBStore Floating-Point SinglestfuxrfS,rBStore Floating-Point SinglestfuxrfS,rB<                                                                                                 | neg (neg. nego nego.)         | rD,rA          | Negate                                          |

| rd. rS,rBOR with ComplementorirA,rS,rBOR with ComplementorisrA,rS,UIMMOR Immediate Shiftedrli—Return from Interruptrlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrlwim (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwim (rlwim.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with<br>Maskrlwim (rlwim.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic WordstbrS,d(rA)Store BytestburS,d(rA)Store BytestburS,rA,rBStore Byte with UpdatestdurS,rA,rBStore Floating-Point DoublestdurS,d(rA)Store Floating-Point DoublestduxrS,rBStore Floating-Point Double with UpdatestduxrS,rBStore Floating-Point Double with UpdatestduxrS,rBStore Floating-Point Double with UpdatestduxrfS,rBStore Floating-Point Double IndexedstfsrfS,rBStore Floating-Point SinglestfsurfS,rBStore Floating-Point SinglestfsurfS,rBStore Floating-Point Single with UpdatestfsuxrfS,rBStore Floating-Point SinglestfsurfS,rBStore Floating-Point Single with Update <td>nor (nor.)</td> <td>rA,rS,rB</td> <td>NOR</td> | nor (nor.)                    | rA,rS,rB       | NOR                                             |

| orirA,rS,UIMMOR ImmediateorisrA,rS,UIMMOR Immediate Shiftedffi—Return from Interruptrlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrlwim (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwmm (rlwinm.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic WordstbrS,d(rA)Store BytestbuxrS,d(rA)Store BytestbuxrS,rA,rBShift Right UndatestdurS,d(rA)Store Byte with UpdatestdurS,rA,rBStore Floating-Point DoublestdurS,rA,rBStore Floating-Point DoublestduxrS,rBStore Floating-Point Double with UpdatestduxrS,rBStore Floating-Point Double with UpdatestduxrS,rBStore Floating-Point Double IndexedstfsrfS,rBStore Floating-Point Double IndexedstfsrfS,rBStore Floating-Point SinglestfsurfS,rBStore Floating-Point Single with UpdatestfsurfS,rBStore Floating-Point Single with UpdatestfsurfS,rBStore Floating-Point Single with UpdatestfsurfS,rBStore Floating-Point Single with UpdatestfsurfS,rBStore Floating-Point Single with Update </td <td>or (or.)</td> <td>rA,rS,rB</td> <td>OR</td>     | or (or.)                      | rA,rS,rB       | OR                                              |

| orisrA,rS,UIMMOR Immediate Shiftedrfi—Return from Interruptrikimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrikimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwinm (rlwinm.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with Maskrkwmm (rlwinm.)rA,rS,rB,RB,MERotate Left Word Immediate then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Word Immediatesrw (sraw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestbrS,d(rA)Store BytestbuxrS,rA,rBStore Byte with UpdatestbxrS,rA,rBStore Byte with Update IndexedstfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point DoublestfdufrS,rBStore Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point SinglestfuxfrS,rBStore Floating-Point SinglestfuxfrS,rBStore Floating-Point SinglestfuxfrS,rBStore Floating-Point Single with UpdatestfuxfrS,rBStore Floating-Point Single with UpdatestfuxfrS,rB                                                    | orc (orc.)                    | rA,rS,rB       | OR with Complement                              |

| rfi—Return from Interruptrlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrlwinm (rlwinm.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwinm (rlwinm.)rA,rS,rB,MB,MERotate Left Word Immediate then AND with Maskrlwinm (rlwinm.)rA,rS,rB,MB,MERotate Left Word then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstddrfS,d(rA)Store Floating-Point DoublestfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double IndexedstfixxfrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point Single                                                                                                                                                                                                                                                                                   | ori                           | rA,rS,UIMM     | OR Immediate                                    |

| rlwimi (rlwimi.)rA,rS,SH,MB,MERotate Left Word Immediate then Mask Insertrlwimm (rlwinm.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwmm (rlwnm.)rA,rS,rB,MB,MERotate Left Word then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store BytestburS,rA,rBStore Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point SinglestfaxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                         | oris                          | rA,rS,UIMM     | OR Immediate Shifted                            |

| rlwinn (rlwinn.)rA,rS,SH,MB,MERotate Left Word Immediate then AND with<br>Maskrlwinn (rlwinm.)rA,rS,rB,MB,MERotate Left Word then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right MordstbrS,d(rA)Store BytestbrS,d(rA)Store BytestbuxrS,rA,rBStore Byte with UpdatestbuxrS,rA,rBStore Byte with UpdatestbuxrS,rA,rBStore Floating-Point DoublestfdfrS,d(rA)Store Floating-Point Double with UpdatestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfuxfrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update                                                                          | rfi                           | _              | Return from Interrupt                           |

| ImageMaskrlwnm (rlwnm.)rA,rS,rB,MB,MERotate Left Word then AND with Masksc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Word Immediatesraw (sraw.)rA,rS,rBShift Right Mordsraw (sraw.)rA,rS,rBShift Right Mordsraw (sraw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestbrS,d(rA)Store BytestburS,rA,rBStore Byte with UpdatestbxrS,rA,rBStore Byte IndexedstddfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfsfrS,rBStore Floating-Point Double with UpdatestfsfrS,rBStore Floating-Point Double with UpdatestfsfrS,rBStore Floating-Point SinglestfsfrS,rBStore Floating-Point SinglestfsfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,d(rA)Store Floating-Point Single with Update                                                                                                                                                                                                                                                                       | rlwimi (rlwimi.)              | rA,rS,SH,MB,ME | Rotate Left Word Immediate then Mask Insert     |

| sc—System Callslw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsrawi (srawi.)rA,rS,rBShift Right Algebraic Word Immediatesrw (srw.)rA,rS,rBShift Right Algebraic Word Immediatesrw (srw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte IndexedstduxrS,rA,rBStore Floating-Point DoublestfdfrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double lindexedstfxfrS,rBStore Floating-Point Double lindexedstfxfrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point Single with UpdatestfsufrS,rBStore Floating-Point Single with Up                                                       | rlwinm (rlwinm.)              | rA,rS,SH,MB,ME |                                                 |

| slw (slw.)rA,rS,rBShift Left Wordsraw (sraw.)rA,rS,rBShift Right Algebraic Wordsrawi (srawi.)rA,rS,SHShift Right Algebraic Word Immediatesrw (srw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte with Update IndexedstdurS,d(rA)Store Byte indexedstdurS,d(rA)Store Byte indexedstduxrS,rA,rBStore Byte IndexedstduxfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfixxfrS,rBStore Floating-Point Double lndexedstfsfrS,rBStore Floating-Point SinglestfsfrS,rBStore Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,drAStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update                                                                                           | rlwnm (rlwnm.)                | rA,rS,rB,MB,ME | Rotate Left Word then AND with Mask             |

| sraw (sraw.)rA,rS,rBShift Right Algebraic Wordsrawi (srawi.)rA,rS,SHShift Right Algebraic Word Immediatesrw (srw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte IndexedstdurS,d(rA)Store Floating-Point DoublestdufrS,d(rA)Store Floating-Point DoublestdufrS,d(rA)Store Floating-Point Double with UpdatestduxfrS,d(rA)Store Floating-Point Double with UpdatestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double IndexedstfixxfrS,rBStore Floating-Point Double IndexedstfixxfrS,rBStore Floating-Point Double IndexedstfixxfrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point Single with UpdatestfsxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                              | SC                            | —              | System Call                                     |

| srawi(srawi.)rA,rS,SHShift Right Algebraic Word Immediatesrw(srw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte with Update IndexedstduxrS,rA,rBStore Byte IndexedstdufrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point DoublestfduxfrS,rBStore Floating-Point Double with UpdatestfdxxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfixxfrS,rBStore Floating-Point Double with UpdatestfixxfrS,rBStore Floating-Point Double IndexedstfixxfrS,rBStore Floating-Point Double Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | slw (slw.)                    | rA,rS,rB       | Shift Left Word                                 |

| srw (srw.)rA,rS,rBShift Right WordstbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte IndexedstdufrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double IndexedstfsuxfrS,rBStore Floating-Point Double IndexedstfsufrS,rBStore Floating-Point Double IndexedstfsuxfrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point Single with UpdatestfsufrS,rBStore Floating-Point SinglestfsufrS,rBStore Floating-Point Single with UpdatestfsufrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                     | sraw (sraw.)                  | rA,rS,rB       | Shift Right Algebraic Word                      |

| stbrS,d(rA)Store BytestburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte IndexedstdurS,rA,rBStore Floating-Point DoublestfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                                                                                                | srawi (srawi.)                | rA,rS,SH       | Shift Right Algebraic Word Immediate            |

| stburS,d(rA)Store Byte with UpdatestbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte IndexedstdxrS,rA,rBStore Byte IndexedstfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point as Integer Word IndexedstfsufrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                                                                                 | srw (srw.)                    | rA,rS,rB       | Shift Right Word                                |

| stbuxrS,rA,rBStore Byte with Update IndexedstbxrS,rA,rBStore Byte IndexedstfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,rBStore Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                                                                                       | stb                           | rS,d(rA)       | Store Byte                                      |

| stbxrS,rA,rBStore Byte IndexedstfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double with UpdatestfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                                                                           | stbu                          | rS,d(rA)       | Store Byte with Update                          |

| stfdfrS,d(rA)Store Floating-Point DoublestfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with Update<br>IndexedstfdxfrS,rBStore Floating-Point Double IndexedstfwxfrS,rBStore Floating-Point Double IndexedstfsfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,rBStore Floating-Point SinglestfsufrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsxfrS,rBStore Floating-Point Single Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | stbux                         | rS,rA,rB       | Store Byte with Update Indexed                  |

| stfdufrS,d(rA)Store Floating-Point Double with UpdatestfduxfrS,rBStore Floating-Point Double with Update<br>IndexedstfdxfrS,rBStore Floating-Point Double IndexedstfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | stbx                          | rS,rA,rB       | Store Byte Indexed                              |

| stfduxfrS,rBStore Floating-Point Double with Update<br>IndexedstfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with UpdatestfsxfrS,rBStore Floating-Point Single with Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | stfd                          | frS,d(rA)      | Store Floating-Point Double                     |

| IndexedstfdxfrS,rBStore Floating-Point Double IndexedstfiwxfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update IndexedstfsxfrS,rBStore Floating-Point Single with Update Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | stfdu                         | frS,d(rA)      | Store Floating-Point Double with Update         |

| stfiwxfrS,rBStore Floating-Point as Integer Word IndexedstfsfrS,d(rA)Store Floating-Point SinglestfsufrS,d(rA)Store Floating-Point Single with UpdatestfsuxfrS,rBStore Floating-Point Single with Update IndexedstfsxfrS,rBStore Floating-Point Single with Update Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | stfdux                        | frS,rB         | -                                               |

| stfs       frS,d(rA)       Store Floating-Point Single         stfsu       frS,d(rA)       Store Floating-Point Single with Update         stfsux       frS,rB       Store Floating-Point Single with Update Indexed         stfsx       frS,rB       Store Floating-Point Single Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | stfdx                         | frS,rB         | Store Floating-Point Double Indexed             |

| stfsu       frS,d(rA)       Store Floating-Point Single with Update         stfsux       frS,rB       Store Floating-Point Single with Update Indexed         stfsx       frS,r B       Store Floating-Point Single Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | stfiwx                        | frS,rB         | Store Floating-Point as Integer Word Indexed    |

| stfsux       frS,rB       Store Floating-Point Single with Update Indexed         stfsx       frS,r B       Store Floating-Point Single Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | stfs                          | frS,d(rA)      | Store Floating-Point Single                     |

| stfsx frS,r B Store Floating-Point Single Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | stfsu                         | frS,d(rA)      | Store Floating-Point Single with Update         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | stfsux                        | frS,rB         | Store Floating-Point Single with Update Indexed |

| sth rS,d(rA) Store Half-Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | stfsx                         | frS,r B        | Store Floating-Point Single Indexed             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | sth                           | rS,d(rA)       | Store Half-Word                                 |

## Table 3-17. Instruction Set Summary (continued)

Base Address Register (EIBADR)." This is the base address of a branch table. See Table 6-4 and Figure 4-3.

Each table entry must contain a branch absolute (ba) instruction to the first instruction of an interrupt service routine. Each table entry occupies two words (eight bytes) to support decompression on mode, where a branch instruction can be more than 32 bits long.

The memory space allocated for the external interrupt relocation table is up to 2 Kbytes. If part of the external interrupt relocation table entry is not used, it may be utilized for another purpose such as instruction code space or data space.

In order to activate the external interrupt relocation feature, the following steps are required:

- 1. Program the EIBADR register to the external interrupt branch table base address. See Section 4.6.2.5, "External Interrupt Relocation Table Base Address Register (EIBADR)."

- 2. Set the MSR[IP] bit.

- 3. Set the BBCMCR[EIR] bit. See Section 4.6.2.1, "BBC Module Configuration Register (BBCMCR)," for programming details.

## NOTE

If both the enhanced external interrupt relocation and exception table relocation functions are activated simultaneously, the final external interrupt vector is defined by EEIR mechanism.

When the EEIR function is activated, any branch instruction execution with the 0xFFF0 0500 target address may cause unpredictable program execution.

### Table 5-1. USIU Address Map

| Address                | Register                                                                                                                          |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0x2F C000              | USIU Module Configuration Register (SIUMCR)<br>See Table 6-7 for bit descriptions.                                                |

| 0x2F C004              | System Protection Control Register (SYPCR)<br>See Table 6-15 for bit descriptions.                                                |

| 0x2F C008              | Reserved                                                                                                                          |

| 0x2F C00E <sup>1</sup> | Software Service Register (SWSR)<br>See Table 6-16 for bit descriptions.                                                          |

| 0x2F C010              | Interrupt Pending Register (SIPEND).                                                                                              |

| 0x2F C014              | Interrupt Mask Register (SIMASK)<br>See Section 6.2.2.2.4, "SIU Interrupt Mask Register (SIMASK)," for bit descriptions.          |

| 0x2F C018              | Interrupt Edge Level Mask (SIEL)<br>See Section 6.2.2.2.7, "SIU Interrupt Edge Level Register (SIEL)," for bit descriptions.      |

| 0x2F C01C              | Interrupt Vector (SIVEC)<br>See Section 6.2.2.2.8, "SIU Interrupt Vector Register (SIVEC)," for bit descriptions.                 |

| 0x2F C020              | Transfer Error Status Register (TESR)<br>See Table 6-17 for bit descriptions.                                                     |

| 0x2F C024              | USIU General-Purpose I/O Data Register (SGPIODT1)<br>See Table 6-23 for bit descriptions.                                         |

| 0x2F C028              | USIU General-Purpose I/O Data Register 2 (SGPIODT2)<br>See Table 6-24 for bit descriptions.                                       |

| 0x2F C02C              | USIU General-Purpose I/O Control Register (SGPIOCR)<br>See Table 6-25 for bit descriptions.                                       |

| 0x2F C030              | External Master Mode Control Register (EMCR)<br>See Table 6-13 for bit descriptions.                                              |

| 0x2F C038              | Pads Module Configuration Register 2 (PDMCR2)<br>See Table 2-6 for bit descriptions.                                              |

| 0x2F C03C              | Pads Module Configuration Register (PDMCR)<br>See Table 2-5 for bit descriptions.                                                 |

| 0x2F C040              | Interrupt Pend2 Register (SIPEND2)<br>See Section 6.2.2.2.2, "SIU Interrupt Pending Register 2 (SIPEND2)," for bit descriptions.  |

| 0x2F C044              | Interrupt Pend3 Register (SIPEND3)<br>See Section 6.2.2.2.3, "SIU Interrupt Pending Register 3 (SIPEND3)," for bit descriptions.  |

| 0x2F C048              | Interrupt Mask2 Register (SIMASK2)<br>See Section 6.2.2.2.5, "SIU Interrupt Mask Register 2 (SIMASK2)," for details.              |

| 0x2F C04C              | Interrupt Mask3 Register (SIMASK3)<br>See Section 6.2.2.2.6, "SIU Interrupt Mask Register 3 (SIMASK3)," for details.              |

| 0x2F C050              | Interrupt In-Service2 Register (SISR2)<br>See Section 6.2.2.2.9, "Interrupt In-Service Registers (SISR2 and SISR3)," for details. |

| 0x2F C054              | Interrupt In-Service3 Register (SISR3)<br>See Section 6.2.2.2.9, "Interrupt In-Service Registers (SISR2 and SISR3)," for details. |

#### System Configuration and Protection

- Periodic Interrupt Timer (Section 6.1.9, "Periodic Interrupt Timer (PIT)")—The SIU provides a timer to generate periodic interrupts for use with a real-time operating system or the application software. The PIT provides a period from 1 µs to 4 seconds with a four-MHz crystal or 200 ns to 0.8 ms with a 20-MHz crystal. The PIT function can be disabled.

- Software Watchdog Timer (Section 6.1.10, "Software Watchdog Timer (SWT)")—The SWT asserts a reset or non-maskable interrupt, as selected by the system protection control register (SYPCR), if the software fails to service the SWT for a designated period of time (e.g., because the software is trapped in a loop or lost). After a system reset, this function is enabled with a maximum time-out period and asserts a system reset if the time-out is reached. The SWT can be disabled or its time-out period can be changed in the SYPCR. Once the SYPCR is written, it cannot be written again until a system reset.

- Freeze Support (Section 6.1.11, "Freeze Operation")—The SIU allows control of whether the SWT, PIT, TB, DEC, and RTC should continue to run during freeze mode.

- Low Power Stop (Section 6.1.12, "Low Power Stop Operation")—In low power modes, specific timers are frozen but others are not.

Figure 6-1 shows a block diagram of the system configuration and protection logic.

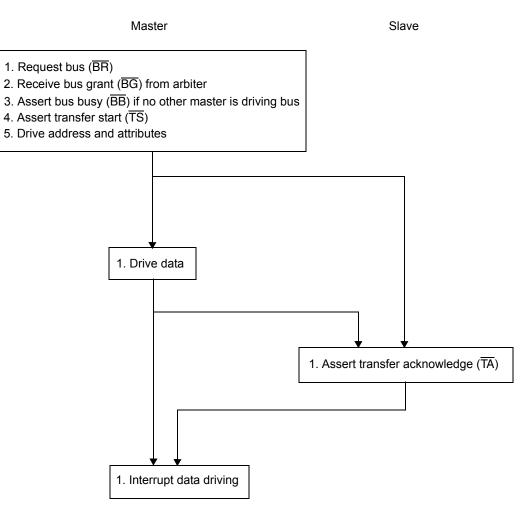

Figure 9-7. Basic Flow Diagram of a Single Beat Write Cycle

External Bus Interface

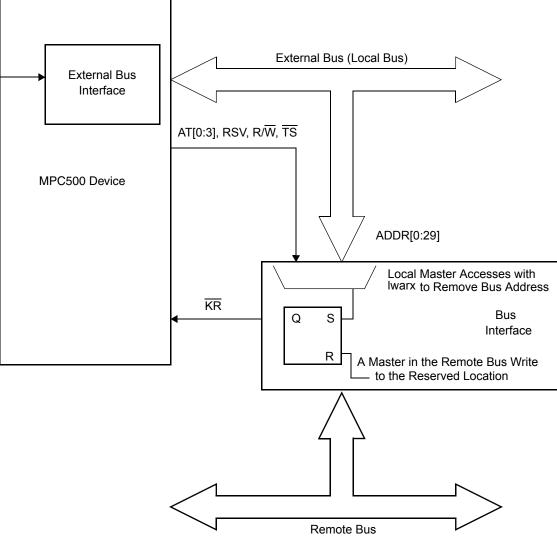

Figure 9-31. Reservation on Multi-level Bus Hierarchy

In this case, the bus interface block implements a reservation flag for the local bus master. The reservation flag is set by the bus interface when a load with reservation is issued by the local bus master and the reservation address is located on the remote bus. The flag is reset (negated) when an alternative master on the remote bus accesses the same location in a write cycle. If the MPC561/MPC563 begins a memory cycle to the previously reserved address (located in the remote bus) as a result of an stwcx instruction, the following two cases can occur:

- If the reservation flag is set, the buses interface acknowledges the cycle in a normal way

- If the reservation flag is reset, the bus interface should assert the  $\overline{\text{KR}}$ . However, the bus interface should not perform the remote bus write-access or abort it if the remote bus supports aborted cycles. In this case the failure of the stwcx instruction is reported to the RCPU.

## 13.2.2 Memory Map

The QADC64E occupies 1 Kbyte, or 512 16-bit entries, of address space. Ten 16-bit registers are control, port, and status registers, 64 16-bit entries are the CCW table, and 64 16-bit entries are the result table, and occupy 192 16-bit address locations because the result data is readable in three data alignment formats.

Each QADC64E module on the MPC561/MPC563 has its own memory space. Table 13-1 shows the memory map for QADC64E module A, it occupies 0x30 4800 to 0x30 4BFF. Table 13-2 displays the memory map for module B. Module B has the same offset scheme starting at 0x30 4C00. QADC64E B occupies 0x30 4C00 to 0x30 4FFF.

| Address                    | MSB                | MSB LSB  |          |         |          |          |                         |          |      |     |       |     |      |           |          | Register |                                |  |

|----------------------------|--------------------|----------|----------|---------|----------|----------|-------------------------|----------|------|-----|-------|-----|------|-----------|----------|----------|--------------------------------|--|

| Addless                    | 0                  | 1        | 2        | 3       | 4        | 5        | 6                       | 7        | 8    | 9   | 10    | 11  | 12   | 13        | 14       | 15       | negister                       |  |

| 0x30 4800                  | STOP               | FRZ      |          |         |          |          | LOC<br>K                | FLI<br>P | SUPV |     |       |     |      |           |          |          | Module<br>Config. <sup>1</sup> |  |

| 0x30 4802                  | Т                  | EST N    | NODE     |         |          |          |                         |          |      |     |       |     |      |           |          |          | Test <sup>1</sup>              |  |

| 0x30 4804                  |                    |          | IRL1     |         |          |          |                         | IRL2     |      |     |       |     |      |           |          |          | Interrupt <sup>1</sup>         |  |

| 0x30 4806                  |                    |          |          | POF     | RTQA     |          |                         |          |      |     | P     | ORT | QB   |           |          |          | Port Data                      |  |

| 0x30 4808                  |                    |          |          | DDI     | RQA      |          |                         |          |      |     |       |     |      |           |          |          | Port Direction                 |  |

| 0x30 480A                  | EMU<br>X           |          |          | TR<br>G |          |          |                         |          | PSF  | 1   |       |     | PSA  |           | PSL      | -        | Control 0                      |  |

| 0x30 480C                  | CIE1               | PIE<br>1 | SSE<br>1 |         |          | MQ1      |                         |          |      |     |       |     |      | Control 1 |          |          |                                |  |

| 0x30 480E                  | CIE2               | PIE<br>2 | SSE<br>2 |         |          | MQ2      | RESUM BQ2<br>E          |          |      |     |       | •   |      | Control 2 |          |          |                                |  |

| 0x30 4810                  | CF1                | PF1      | CF2      | PF2     | TOR<br>1 | TOR<br>2 |                         |          | QS   | CWP |       |     |      |           | Status 0 |          |                                |  |

| 0x30 4812                  |                    |          |          |         | CW       | PQ1      |                         |          |      |     | CWPQ2 |     |      |           | Status 1 |          |                                |  |

| 0x30 4814-<br>0x30 49FF    |                    |          |          |         |          |          |                         |          |      |     |       |     |      |           |          |          | Reserved                       |  |

| 0x30<br>4A00-<br>0x30 4A7F | P BY IST CHAN<br>P |          |          |         |          |          |                         |          | CCWs |     |       |     |      |           |          |          |                                |  |

| 0x30<br>4A80-<br>0x30 4AFF | 0000 00            |          |          |         |          |          | UNSIGNED RIGHT JUSTIFIE |          |      |     | D     |     |      | Results   |          |          |                                |  |

| 0x30<br>4B00-<br>0x30 4B7F | SIGN SIGNED LEFT J |          |          |         |          |          | JUSTIF                  | IED      |      |     |       |     | 00 0 | 000       |          |          | Results                        |  |

| 0x30 4B80<br>0x30 4BFF     | UNSIGNED LEFT JU   |          |          |         |          |          |                         | D        |      |     |       |     | 00 0 | 000       |          |          | Results                        |  |

<sup>1</sup> Registers are accessible only as supervisor data space

#### **Queued Serial Multi-Channel Module**

| Access <sup>1</sup> | Address                  | MSB <sup>2</sup><br>0 | LSB<br>15         |

|---------------------|--------------------------|-----------------------|-------------------|

| S/U                 | 0x30 5180 –<br>0x30 51BF | Transmit Data RA      | M (32 half-words) |

| S/U                 | 0x30 51C0 –<br>0x30 51DF | Command R/            | AM (32 bytes)     |

#### Table 15-12. QSPI Register Map (continued)

S = Supervisor access only

S/U = Supervisor access only or unrestricted user access (assignable data space).

<sup>2</sup> Eight-bit registers, such as SPCR3 and SPSR, are on 8-bit boundaries. 16-bit registers such as SPCR0 are on 16-bit boundaries.

To ensure proper operation, set the QSPI enable bit (SPE) in SPCR1 only after initializing the other control registers. Setting this bit starts the QSPI.

Rewriting the same value to a control register does not affect QSPI operation with the exception of writing NEWQP in SPCR2. Rewriting the same value to these bits causes the RAM queue pointer to restart execution at the designated location.

Before changing control bits, the QSPI should be halted. Writing a different value into a control register other than SPCR2 while the QSPI is enabled may disrupt operation. SPCR2 is buffered, preventing any disruption of the current serial transfer. After the current serial transfer is completed, the new SPCR2 value becomes effective.

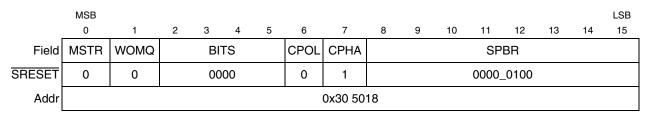

# 15.6.1.1 QSPI Control Register 0 (SPCR0)

SPCR0 contains parameters for configuring the QSPI before it is enabled. The CPU has read/write access to SPCR0, but the QSPI has read access only. SPCR0 must be initialized before QSPI operation begins. Writing a new value to SPCR0 while the QSPI is enableddisrupts operation.

Figure 15-11. QSPI Control Register 0 (SPCR0)

# 15.8.2.1 QSCI1 Control Register (QSCI1CR)

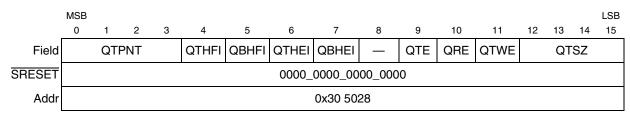

### Figure 15-31. QSCI1 Control Register (QSCI1CR)

| Bits | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:3  | QTPNT | Queue transmit pointer. QTPNT is a 4-bit counter used to indicate the next data frame within the transmit queue to be loaded into the SC1DR. This feature allows for ease of testability. This field is writable in test mode only; otherwise it is read-only.                                                                                                                                                                                                      |

| 4    | QTHFI | Receiver queue top-half full interrupt. When set, QTHFI enables an SCI1 interrupt whenever the QTHF flag in QSCI1SR is set. The interrupt is blocked by negating QTHFI. This bit refers to the queue locations SCRQ[0:7].<br>0 QTHF interrupt inhibited<br>1 Queue top-half full (QTHF) interrupt enabled                                                                                                                                                           |

| 5    | QBHFI | Receiver queue bottom-half full interrupt. When set, QBHFI enables an SCI1 interrupt whenever<br>the QBHF flag in QSCI1SR is set. The interrupt is blocked by negating QBHFI. This bit refers to<br>the queue locations SCRQ[8:15].<br>0 QBHF interrupt inhibited<br>1 Queue bottom-half full (QBHF) interrupt enabled                                                                                                                                              |

| 6    | QTHEI | Transmitter queue top-half empty interrupt. When set, QTHEI enables an SCI1 interrupt<br>whenever the QTHE flag in QSCI1SR is set. The interrupt is blocked by negating QTHEI. This bit<br>refers to the queue locations SCTQ[0:7].<br>0 QTHE interrupt inhibited<br>1 Queue top-half empty (QTHE) interrupt enabled                                                                                                                                                |

| 7    | QBHEI | Transmitter queue bottom-half empty interrupt. When set, QBHEI enables an SCI1 interrupt<br>whenever the QBHE flag in QSCI1SR is set. The interrupt is blocked by negating QBHEI. This<br>bit refers to the queue locations SCTQ[8:15].<br>0 QBHE interrupt inhibited<br>1 Queue bottom-half empty (QBHE) interrupt enabled                                                                                                                                         |

| 8    | —     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9    | QTE   | Queue transmit enable. When set, the transmit queue is enabled and the TDRE bit should be ignored by software. The TC bit is redefined to indicate when the entire queue is finished transmitting. When clear, the SCI1 functions as described in the previous sections and the bits related to the queue (Section 5.5 and its subsections) should be ignored by software with the exception of QTE.<br>0 Transmit queue is disabled<br>1 Transmit queue is enabled |

#### Table 15-32. QSCI1CR Bit Descriptions

CAN 2.0B Controller Module

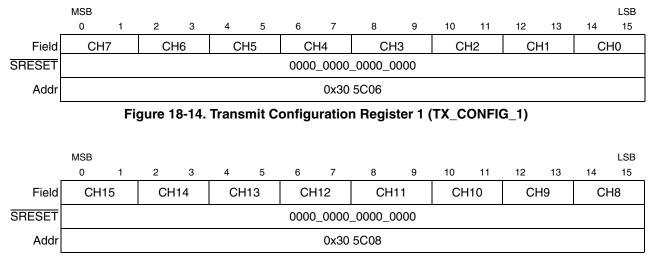

TX\_CONFIG\_1 and TX\_CONFIG\_2 can only be written while PPM transmit mode is disabled (PPMPCR[ENTX] = 0). While transmit is enabled these registers read as 0x00 and writing them will return TEA (bus error access).

Figure 18-15. Transmit Configuration Register 2 (TX\_CONFIG\_2)

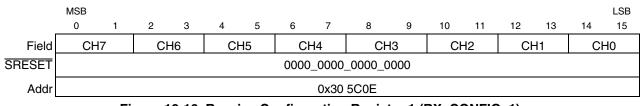

# 18.4.4 Receive Configuration Registers (RX\_CONFIG\_1 and RX\_CONFIG\_2)

The two receive configuration registers control which internal modules will receive data from the PPM. Each of the configuration registers contains eight separate 2-bit wide bit fields. Each of the 16 fields controls a multiplexer that selects a 1-bit channel from the PPM data receive register to an internal module. See Table 18-6 for more information on channel control and setting the channel values.

RX\_CONFIG\_1 and RX\_CONFIG\_2 can only be written while PPM receive mode is disabled (PPMPCR[ENRX] = 0). While receive mode is enabled these registers read as 0x00 and writing them will return TEA (bus error access).

# 19.4.1 TPU Module Configuration Register (TPUMCR)

|        | MSB  |                                     |   |     |     |     |      |     |      |      |      |       |    |    |    | LSB |

|--------|------|-------------------------------------|---|-----|-----|-----|------|-----|------|------|------|-------|----|----|----|-----|

|        | 0    | 1                                   | 2 | 3   | 4   | 5   | 6    | 7   | 8    | 9    | 10   | 11    | 12 | 13 | 14 | 15  |

| Field  | STOP | TCR1P                               |   | TCF | R2P | EMU | T2CG | STF | SUPV | PSCK | TPU3 | T2CSL |    | _  | _  |     |

| SRESET | 0    | 00                                  |   | 0   | 0   | 0   | 0    | 0   | 1    | 0    | 1    | 0     |    | 00 | 00 |     |

| Addr   |      | 0x30 4000(TPU_A), 0x30 4400 (TPU_B) |   |     |     |     |      |     |      |      |      |       |    |    |    |     |

Figure 19-5. TPUMCR — TPU Module Configuration Register

| Bits | Name  | Description                                                                                                                                                                                                                                                                                                                                                                       |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | STOP  | Low-power stop mode enable. If the STOP bit in TPUMCR is set, the TPU3 shuts down its internal clocks, shutting down the internal microengine. TCR1 and TCR2 cease to increment and retain the last value before the stop condition was entered. The TPU3 asserts the stop flag (STF) in TPUMCR to indicate that it has stopped.<br>0 Enable TPU3 clocks<br>1 Disable TPU3 clocks |

| 1:2  | TCR1P | Timer Count Register 1 prescaler control. TCR1 is clocked from the output of a prescaler. The prescaler divides its input by 1, 2, 4, or 8. This is a write-once field unless the PWOD bit in TPUMCR3 is set.<br>00 Divide by 1<br>01 Divide by 2<br>10 Divide by 4<br>11 Divide by 8<br>Refer to Section 19.3.8, "Prescaler Control for TCR1" for more information.              |

| 3:4  | TCR2P | Timer Count Register 2 prescaler control. TCR2 is clocked from the output of a prescaler. The prescaler divides this input by 1, 2, 4, or 8. This is a write-once field unless the PWOD bit in TPUMCR3 is set.<br>00 Divide by 1<br>01 Divide by 2<br>10 Divide by 4<br>11 Divide by 8<br>Refer to Section 19.3.9, "Prescaler Control for TCR2" for more information.             |

| 5    | EMU   | Emulation control. In emulation mode, the TPU3 executes microinstructions from DPTRAM exclusively. Access to the DPTRAM via the IMB3 is blocked, and the DPTRAM is dedicated for use by the TPU3. After reset, this bit can be written only once.<br>0 TPU3 and DPTRAM operate normally<br>1 TPU3 and DPTRAM operate in emulation mode <sup>1</sup>                               |

| 6    | T2CG  | <ul> <li>TCR2 clock/gate control</li> <li>TCR2 pin used as clock source for TCR2</li> <li>TCR2 pin used as gate of DIV8 clock for TCR2</li> <li>Refer to Section 19.3.9, "Prescaler Control for TCR2" for more information.</li> </ul>                                                                                                                                            |

| 7    | STF   | Stop flag.<br>0 TPU3 is operating normally<br>1 TPU3 is stopped (STOP bit has been set)                                                                                                                                                                                                                                                                                           |

| 8    | SUPV  | Supervisor data space<br>0 Assignable registers are accessible from user or supervisor privilege level<br>1 Assignable registers are accessible from supervisor privilege level only                                                                                                                                                                                              |

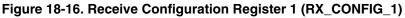

CDR3 Flash (UC3F) EEPROM

Figure 21-1. Block Diagram for a 512 Kbyte UC3F Module Configuration

The UC3F EEPROM module array is divided into array blocks to allow for independent erase, address attributes restrictions, and protection from program and erase for each array block. The size of a large array block in the UC3F module is fixed at 64 Kbytes. The size of a subdivided large block becomes the original large array block size minus 16 Kbytes (64 Kbytes – 16 Kbytes = 48 Kbytes). The size of the small block, which is the remainder of the large block, is always 16 Kbytes. The total UC3F EEPROM array is distributed into eight large blocks, two of which contain small blocks. Information is transferred to the UC3F EEPROM by long-word (64 bits), word (32 bits), half-word (16 bits), or byte (8 bits).

To improve system performance, each array read access retrieves 32 bytes of information. These 32 bytes may be copied into one of two read page buffers aligned to the low order addresses. The two read page buffers are independently updated by page management logic contained in the BIU which interfaces to the UC3F EEPROM module.

| Bits | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | STOP              | Array stop control. Writes to the STOP bit have no effect while in program or erase operation (SES = 1). The STOP bit is always readable whenever the registers are enabled.<br>When STOP = 1, the reset state of STOP is 1 and the UC3F array is disabled; internal circuits are switched into a low power state. The STOP bit may be used to implement low power standby modes or power management schemes. The UC3FMCR remains readable and writable when STOP = 1 so that the STOP bit may be deasserted. Attempts to program or erase the array while STOP = 1 have no effect. SES cannot be set to 1 when STOP = 1.<br>When STOP = 0, the reset state of STOP is 0 and the UC3F array is enabled for accesses. All registers that were disabled with STOP = 1 are now enabled. A STOP recovery time of 1 $\mu$ s is required for biases in the UC3F array to reach their appropriate states to resume normal operation. Operations to the UC3F array should be delayed for at least 1 $\mu$ s after clearing the STOP bit. 0 = UC3F array is disabled (low-power mode) |

| 1    | LOCK <sup>1</sup> | Lock control. The default reset state of $\overline{LOCK}$ is 1. This enables writing of all fields in the Flash registers.<br>Once the $\overline{LOCK}$ bit has been asserted ( $\overline{LOCK} = 0$ ) in normal operating mode, the write-lock can only be disabled again by a reset. When the device is in background debug mode and CSC = 0, the $\overline{LOCK}$ bit may be written from a 0 to a 1.<br>When the $\overline{LOCK}$ control bit is cleared to 0, the write-locked register bits: FIC, SUPV, SBSUPV[0:1], DATA, SBDATA, PROTECT, SBPROTECT, and SBEN[0:1] are locked. Writes to these bits while $\overline{LOCK}$ can be written to 0 once after reset when UC3FCTL[CSC] = 0 to allow protection of the write-locked register bits after initialization.<br>WARNING:<br>If the lock protection mechanism is enabled ( $\overline{LOCK} = 0$ ) before PROTECT and SBPROTECT are cleared, the device must use background debug mode to program or erase the UC3F EEPROM.                                                                                |

| 2    | —                 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3    | FIC               | Force information censorship. The default reset state of FIC is normal censorship operation (FIC = 0). The FIC bit is write protected by the $\overline{LOCK}$ bit and the UC3FCTL[CSC] bit. Writes will have no effect if $\overline{LOCK} = 0$ or CSC = 1. Once FIC is set (FIC = 1), it cannot be cleared except by a reset. The FIC bit can be read whenever the registers are enabled.<br>The FIC bit is a censorship emulation mode used to aid in the development of custom techniques for controlling the ACCESS bit without setting CENSOR[0:1] to the information censorship state.<br>Using FIC to force information censorship allows testing of the hardware and software for setting ACCESS without setting CENSOR[0:1] = 11 and risk permanently setting the device into an unusable information censorship state.<br>0 = normal uc3f censorship operation<br>1 = forces the uc3f into information censorship mode                                                                                                                                            |

| 4    | SIE               | Shadow information enable. The default reset state of SIE is 0. The SIE bit is write protected in program operation (SES = 1 and PE = 0). The SIE bit can be read whenever the registers are enabled.<br>When SIE = 1, normal array accesses are disabled, and the two shadow information rows are enabled. Array accesses are directed to the shadow row while SIE = 1. When an array location is read in this mode, only the lower 6 address bits are used to select which 64 bytes of the 512-byte shadow row are read. The upper address bits are not used for shadow row decoding. The read page buffer address monitor is reset whenever SIE is modified making the next UC3F array access an off page access.<br>0 = normal array access and selects the shadow information rows                                                                                                                                                                                                                                                                                      |

| BSDL<br>Bit | Cell<br>Type | Pin/Port Name | BSDL<br>Function | Safe<br>Value | Contro<br>I<br>Cell | Disable<br>Value | Disabl<br>e<br>Result | Pin<br>Functio<br>n | Pad<br>Type |

|-------------|--------------|---------------|------------------|---------------|---------------------|------------------|-----------------------|---------------------|-------------|

| 347         | BC_2         | *             | controlr         | 0             |                     |                  |                       |                     |             |

| 348         | BC_7         | ADDR_SGPIOA18 | bidir            | 0             | 347                 | 0                | Z                     | IO                  | 26v5vs      |

| 349         | BC_2         | *             | controlr         | 0             |                     |                  |                       |                     |             |

| 350         | BC_7         | ADDR_SGPIOA9  | bidir            | 0             | 349                 | 0                | Z                     | IO                  | 26v5vs      |

| 351         | BC_2         | *             | controlr         | 0             |                     |                  |                       |                     |             |

| 352         | BC_7         | ADDR_SGPIOA17 | bidir            | 0             | 351                 | 0                | Z                     | IO                  | 26v5vs      |