# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | e | τ | а | I | ļ | s |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| Product Status             | Obsolete                                               |

|----------------------------|--------------------------------------------------------|

| Core Processor             | ACE1202                                                |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 4MHz                                                   |

| Connectivity               | <u>.</u>                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT             |

| Number of I/O              | 8                                                      |

| Program Memory Size        | 2KB (2K x 8)                                           |

| Program Memory Type        | EEPROM                                                 |

| EEPROM Size                | 64 x 8                                                 |

| RAM Size                   | 64 x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                            |

| Data Converters            |                                                        |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                      |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                         |

| Supplier Device Package    | 14-SOIC                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/onsemi/ace1202emx |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 Electrical Characteristics Absolute Maximum Ratings

Ambient Storage Temperature Input Voltage not including G3 G3 Input Voltage Lead Temperature (10s max)

Electrostatic Discharge on all pins

| -65°C to +150°C                   |  |

|-----------------------------------|--|

| -0.3V to $V_{\rm CC}\text{+}0.3V$ |  |

| 0.3V to 13V                       |  |

| +300°C                            |  |

| 2000V min                         |  |

### **Operating Conditions**

| Relative Humidity (non-condensing) |  |

|------------------------------------|--|

| EEPROM write limits                |  |

95%

See DC Electrical Characteristics

| Part Number | Operating Voltage | Ambient Operating Temperature |

|-------------|-------------------|-------------------------------|

| ACE1202     | 2.2 to 5.5V       | 0°C to 70°C                   |

| ACE12022    | 2.2 to 5.5V       | 0°C to 70°C                   |

| ACE1202E    | 2.2 to 5.5V       | -40°C to +85°C                |

| ACE12022E   | 2.2 to 5.5V       | -40°C to +85°C                |

| ACE1202V    | 2.2 to 5.5V       | -40°C to +125°C               |

| ACE1202B    | 2.7 to 5.5V       | 0°C to 70°C                   |

| ACE12022B   | 2.7 to 5.5V       | 0°C to 70°C                   |

| ACE1202BE   | 2.7 to 5.5V       | -40°C to +85°C                |

| ACE12022BE  | 2.7 to 5.5V       | -40°C to +85°C                |

| ACE1202BV   | 2.7 to 5.5V       | -40°C to +125°C               |

| ACE12022BV  | 2.7 to 5.5V       | -40°C to +125°C               |

| ACE1202L    | 1.8 to 5.5V       | 0°C to 70°C                   |

### Preliminary ACE1202/ACE1202-2 AC Electrical Characteristics

$V_{CC} = 1.8/2.2/2.7$  to 5.5V

All measurements valid for ambient operating temperature range unless otherwise stated.

| Parameter                                                                            | Conditions                           | MIN | ТҮР | MAX  | Units  |

|--------------------------------------------------------------------------------------|--------------------------------------|-----|-----|------|--------|

| Instruction cycle time from<br>internal clock - setpoint                             | 5.0V at +25°C                        | 0.9 | 1.0 | 1.1  | μs     |

| Internal clock voltage dependent3.0V to 5.5V,frequency variationconstant temperature |                                      |     |     | +5   | %      |

| Internal clock temperature dependent frequency variation                             | 3.0V to 5.5V, full temperature range |     |     | +10  | %      |

| Internal clock frequency3.0V to 4.5V,deviation for 0.5V dropconstant temperature     |                                      |     |     | +2   | %      |

| Crystal oscillator frequency                                                         | (Note 6)                             |     |     | 4    | MHz    |

| External clock frequency                                                             | (Note 7)                             |     |     | 4    | MHz    |

| EEPROM write time                                                                    |                                      |     | 3   | 10   | ms     |

| Internal clock start up time                                                         | (Note 7)                             |     |     | 2    | ms     |

| Oscillator start up time (Note 7)                                                    |                                      |     |     | 2400 | cycles |

<sup>6</sup> The maximum permissible frequency is guaranteed by design but not 100% tested.

<sup>7</sup> The parameter is guaranteed by design but not 100% tested.

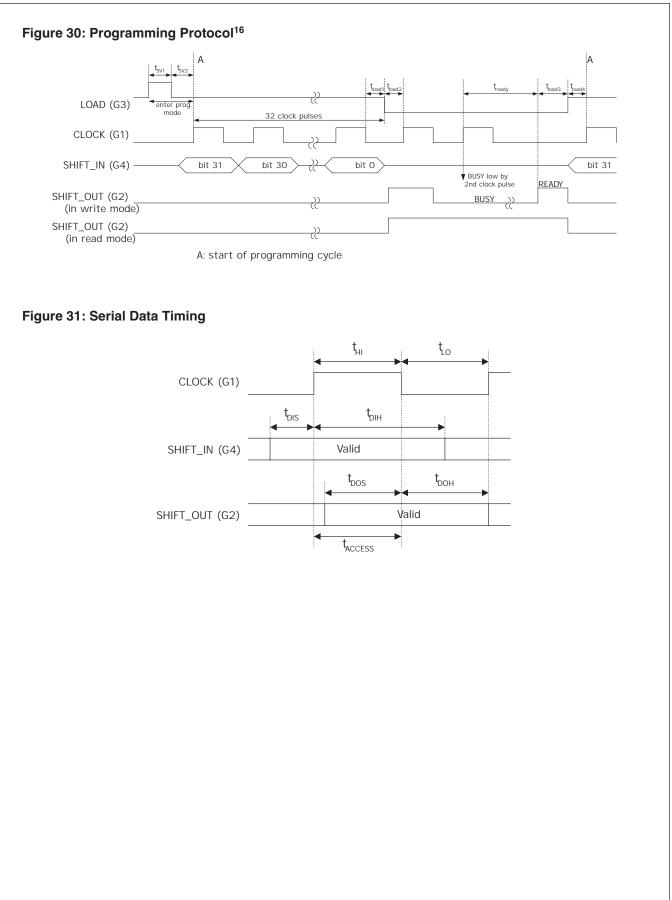

### Preliminary ACE1202/ACE1202-2 Electrical Characteristics for programming

All data following is valid between 4.5V and 5.5V at ambient temperature. The following characteristics are guaranteed by design but are not 100% tested. See "EEPROM write time" in the AC Electrical Characteristics for definition of the programming ready time.

| Parameter                                                             | Description              | MIN  | MAX  | Units |

|-----------------------------------------------------------------------|--------------------------|------|------|-------|

| t <sub>HI</sub>                                                       | CLOCK high time          | 500  | DC   | ns    |

| t <sub>LO</sub>                                                       | CLOCK low time           | 500  | DC   | ns    |

| t <sub>DIS</sub>                                                      | SHIFT_IN setup time      | 100  |      | ns    |

| t <sub>DIH</sub>                                                      | SHIFT_IN hold time       | 100  |      | ns    |

| t <sub>DOS</sub>                                                      | SHIFT_OUT setup time     | 100  |      | ns    |

| t <sub>DOH</sub>                                                      | SHIFT_OUT hold time      | 900  |      | ns    |

| t <sub>SV1</sub> , t <sub>SV2</sub>                                   | LOAD supervoltage timing | 50   |      | μs    |

| $t_{\text{LOAD1}},t_{\text{LOAD2}},t_{\text{LOAD3}},t_{\text{LOAD4}}$ | LOAD timing              | 5    |      | μs    |

| V <sub>SUPERVOLTAGE</sub>                                             | Supervoltage level       | 11.5 | 12.5 | V     |

# Figure 8: Power Supply Rise Time

t<sub>S actual</sub>

t<sub>S min</sub>

| Name                  | Parameter                                      | Unit   |

|-----------------------|------------------------------------------------|--------|

| V <sub>CC</sub>       | Supply Voltage                                 | [V]    |

| V <sub>BATT</sub>     | Battery Voltage (Nominal Operating Voltage)    | [V]    |

| t <sub>S min</sub>    | Minimum Time for V <sub>CC</sub> to Rise by 1V | [ms]   |

| t <sub>S actual</sub> | Actual Time for $V_{CC}$ to Rise by 1V         | [ms]   |

| t <sub>S max</sub>    | Maximum Time for V <sub>CC</sub> to Rise by 1V | [ms]   |

| S <sub>VCC</sub>      | Power Supply Slope                             | [ms/V] |

t<sub>S max</sub>

time

6.0 Timer 0 reset by software or system reset. Timer 0 is a 12-bit free running idle timer. Upon power-up or alige WKINTEN bit is used in the Multi-input Wakeup/Interrupt reset, the timer is reset to 0x000 and then counts up continuouslyk. See Section 8 for details. based on the instruction clock of 1MHzsl1 Software cannot read from or write to this timer. However, software can monitor the Watchdog timer timer's pending (TOPND) bit that is set every 8192 cycles (initially watchdog timer is used to reset the device and safely recovery 4096 cycles after a reset). The TOPND flag is set every other timethe rare event of a processomaway condition. The 12-bit the timer overflows (transitions from 0xFFF to 0x000) through one 0 is used as a pre-scaler for Watchdog timer. The Watchdog timer is some the last Watchdog reset. The Watchdog is set very other timethe rare event of a processomaway condition. The 12-bit the timer overflows (transitions from 0xFFF to 0x000) through one 0 is used as a pre-scaler for Watchdog timer. The Watchdog is set very other timethe rare event of a processom one every 61,440 cycles but no soone its counting sequence. Software can either poll the TOPND bit or vector to an interrupt of a tory by writing the value 0x1B to the subroutine. In order to interrupt on a TOPND, software must be serviced (WDSVR) register (see Figure 20). The part of the subroutine. In order to interrupt on a TOPND, software must be automatically if the Watchdog is serviced too frequent of the serviced too frequent of the top frequent of the top interrupt on a top of the top

subroutine. In order to interrupt on a TOPND, software must be sure to enable the Timer O interrupt enable (TOINTEN) bit in the

sure to enable the Timer O interrupt enable (TOINTEN) bit in the out attended in the outer the o Watchdog will always be powered-up enabled. Software cannot o

1. Exiting from IDLE mode (See Section 17.0 for details.)

2. Start up delay from HALT mode

3. Watchdog pre-scaler (See Section 7.0 for details.)

The TOINTEN bit is a read/write bit. If set to 0, interrupt reque from the Timer O are ignored. If set to 1, interrupt requests are accepted. Upon reset, the TOINTEN bit is reset to O.

The TOPND bit is a read/write bit. If set to 1, it indicates that a Timer O interrupt is pending. This bit is set by a Timer O overflow and is

### Figure 19: Timer 0 Control Register (T0CNTRL)

| Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | 2 Bit | 1 Bit   | 0 |

|---------|-------|-------|-------|-------|-------|-------|---------|---|

| WKINTEN | х     | x     | х     | х     | х     | TOPND | TOINTEN |   |

### Figure 20: Watchdog Server Register (WDSVR)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | 2 Bit | 1 Bit | 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|---|

| 0     | 0     | 0     | 1     | 1     | 0     | 1     | 1     |   |

only be set while the device is in programming mode. Once set, the Watchdog will always be powered-up enabled. Software cannot disable the Watchdog. The Watchdog timer can only be disabled in programming mode by resetting the WDEN bit as long as the memory write protect (WDIS) feature is not enabled.

Controller Control Control

### 8.0 Hardware Bit-Coder (ACE1202-2 only)

either port G2 or G5. If IOSEL is 1, G5 is selected as the output por III otherwise G2 is selected.

The ACE1202-2 contains a dedicated hardware bit-encoding peripheral block, Hardware Bit-Coder (HBC), for IR/RF dataThe TXBUSY signal is read only and is used to inform software transmission (see Figure 21.) The HBC is completely software hat a transmission is in progress. TXBUSY goes high when the programmable and can be configured to emulate various bitoncoded data begins to shift out of the output port and will remain encoding formats. The software developer has the freedom togh during each consecutive DATO frame bit transmission (see encode each bit of data into a desired pattern and output frigure 25). The HBC will clear the TXBUSY signal when the last encoded data at the desired frequency through either the G2 or DATO encoded bit of the frame is transmitted and the STOP signal is O output (TX) ports.

The HBC contains six 8-bit memory-mapped configuration regisThe START / STOP signal controls the encoding and transmission process for each data frame. When software sets the START ters PSCALE, HPATTERN, LPATTERN, BPSEL, HBCNTRL, and DATO. The registers are used to select the transmission frotop bit the DATO frame transmission process begins. The

parto. The registers are used to select the transmission frequery bit the DATO frame transmission process begins. The quency, store the data bit-encoding patterns, configure the dataRT signal will remain high until the beginning of the last bit-pattern/frame lengths, and control the data transmission flewcoded DATO frame bit transmission. The HBC then clears the START / STOP bit allowing software to either continue with a new start with the stransmission frequency, an 8-bit divide DATO frame transmission or stop the transmission all together constant must be written into the IR/RF Pre-scalar (PSCALE) see Figure 25). If TXBUSY is 0 when the START signal is register. The IR/RF transmission frequency generator divides the abled, a synchronization period occurs before any data is 1MHz instruction clock down by 4 and the PSCALE register like another the another transmission frequence of the stransmission of the stransmission of the stransmission frequence of the stransmission frequence of the stransmission frequence of the stransmission frequence of the stransmission of the stransm register. The IR/RF transmission frequency generator divides thenabled, a synchronization period occurs before any data is

register. The IR/RF transmission frequency generator unders transmitted a synchronization period occurs before any data is 1MHz instruction clock down by 4 and the PSCALE register is transmitted lasting the amount of time to transmit a 0 encoded used to select the desired IR/RF frequency shift. Together, there Figure 24). transmission frequency range can be configured between 976Hz (PSCALE = 0xFF) and 125kHz (PSCALE = 0xO1). Upon a reset, The OCFLAG signal is read only and goes high when the last the PSCALE register is initialized to zero disabling the IR/RF encoded bit of the DATO frame is transmitting. The OCFLAG transmission frequency generator. However, once the PSCALE signal is used to inform software that the DATO frame transmission frequency the desired IR/RF frequency is mainoperation is completing (see Figure 25). If multiple DATO frames register is programmed, the desired IR/RF frequency is mainoperation is completing (see Figure 25). If multiple DATO frames are to be transmitted consecutively, software should poll tained as long as the device is powered.

OccLAG signal for a 1. Once OCFLAG is 1, DATO must be reload ing patterns must be stored in the appropriate registers. The HBC contains two 2 bit bit encoding pattern registers. The HBC contains two 2 bit bit encoding pattern registers. The HBC contains two 2 bit bit encoding pattern registers. The HBC contains two 2 bit bit encoding pattern registers. The HBC contains two 2 bit bit encoding pattern registers. The HBC contains two 8-bit bit-encoding pattern registers, High-pattern zation period). Since OCFLAG remains high during the entire las (HPATTERN) and Low-pattern (LPATTERN). The encoding patencoded DATO frame bit transmission, software should wait f tern stored in the HPATTERN register is transmitted when the HBC to clear the OCFLAG signal before polling for the new data bit value to be encoded is a 1. Similarly, the pattern stored CFLAG high pulse. If new data is not reloaded into DATO and the the LPATTERN register is transmitted when the data bit value START signal (STOP is active) is not set before the OCFLAG is be encoded is a 0. The HBC transmits each encoded pattern MSB 0, the transmission process will end (TXBUSY is cleared) and a first.

So, the transmission process will end (TXBUSY is cleared) and a new process will begin starting with the synchronization period of Figure 24 and 25 shows how the HBC performs its data encoding of the example, two frames are encoded and transmitted consecutively with the following bit encoding format specification: B)1. Transmission frequency = 62.5KHz M<sup>2</sup>. Data to be encoded = 0x52, 0x92 (all 8-bits) OBE ach bit should be encoded as a 3-bit binary válue; Y O 110b and'O' = 100b ther 4. Transmission output port : G2 To perform the data transmission, software must first initialize M<sup>2</sup>. Descale, BPSEL, HPATTERN, LPATTERN, and DATO registers With the appropriate values. PILD PSCALE, #03H ; (1MHz 4) 4 = 62.5KHz VED PSCALE, #03H ; (1MHz 4) 4 = 62.5KHz The number of bits transmitted from the HPATTERN and Figure 24 and 25 shows how the HBC performs its data encode LPATTERN registers is software programmable through the Bit the example, two frames are encoded and transmitted consedu Period Configuration (BPSEL) register (see Figure 22). During the ively with the following bit encoding format specification: transmission of HPATTERN, the number of bits transmitted is configured by BPH[2:0] (BPSEL[2:0]) while BPL[2:0] (BPSEL[5:3])1. Transmission frequency = 62.5KHz

configures the number of transmitted bits for the LPATTERN. The Data to be encoded = 0x52, 0x92 (all 8-bits)

HBC allows from 2 (0x1) to 8 (0x7) encoding pattern bits to be chouded = 0x32, 0x72 (all 0-bits) transmitted from each register. Upon a reset, BPSEL is initially 0 table bit should be encoded as a 3-bit binary válue, disabling the HBC from transmitting pattern bits from either

register.

The Data (DATO) register is used to store up to 8 bits of data to be encoded and transmission, software must first initialized by the HBC. This data is shifted bit by SCALE, BPSEL, HPATTERN, LPATTERN, and DATO registers encoded and transmitted by the HBC. This data is shifted, bit by the APATTERN, LF bit, MSB to LSB into a 1-bit decision register. If the active bit shifted

| into the decision register is 1, the pattern in the HPATTERNLD PSCALE, #03H                                                                                     | ; (1MHz 4) 4 = 62.5KHz           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| register is shifted out of the output port. Similarly, if the active bit is 0 the pattern in the LPATTERN register is shifted out. LD BPSEL, #012H              | ; BPH = 2, BPL = 2 (3 bits each) |

| The HBC control (HBCNTRL) register is used to configure and LD HPATTERN, #OCOH                                                                                  | ; HPATTERN = OxCO                |

| control the data transmission. HBCNTRL is divided in <u>5</u> different <sub>LD</sub> LPATTERN, #090H controlling signal FRAME[2:0], IOSEL, TXBUSY, START/STOP, | ; LPATTERN = Ox90                |

| and OCELAG (see Figure 23) LD DATO, #052H                                                                                                                       | ; DATO = 0x52                    |

FRAME[2:0] selects the number of bits of DATO to encode an@nce the basic registers are initialized, the HBC can be started. transmit. The HBC allows from 2 (0x1) to 8 (0x7) DATO bits to (be the same time, software must set the number of data bits per encoded and transmitted. Upon a reset, FRAME is initialized todata frame and select the desired output port.) zero disabling the DATO decision register transmitting no data. LD HBCNTRL, #27H

The IOSEL signal selects the transmission to output (TX) through

; START / STOP = 1, FRAME = 7, IOSEL = 0