Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | RXv2                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 54MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SD/SDIO, SPI, SSI, USB OTG         |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 79                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 32K x 8                                                                          |

| /oltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TFLGA                                                                        |

| Supplier Device Package    | 100-TFLGA (5.5x5.5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52315adla-20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Overview

# 1.1 Outline of Specifications

Table 1.1 lists the specifications, and Table 1.2 gives a comparison of the functions of the products in different packages.

Table 1.1 is for products with the greatest number of functions, so the number of peripheral modules and channels will differ in accordance with the package type. For details, see Table 1.2, Comparison of Functions for Different Packages.

Table 1.1 Outline of Specifications (1/4)

| Classification    | Module/Function                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU               | CPU                               | <ul> <li>Maximum operating frequency: 54 MHz</li> <li>32-bit RX CPU (RX v2)</li> <li>Minimum instruction execution time: One instruction per clock cycle</li> <li>Address space: 4-Gbyte linear</li> <li>Register set General purpose: Sixteen 32-bit registers Control: Ten 32-bit registers Accumulator: Two 72-bit registers Accumulator: Two 72-bit registers Basic instructions: 75 (variable-length instruction format)</li> <li>Floating-point instructions: 11</li> <li>DSP instructions: 23</li> <li>Addressing modes: 10</li> <li>Data arrangement Instructions: Little endian Data: Selectable as little endian or big endian</li> <li>On-chip 32-bit multiplier: 32-bit → 32-bit → 64-bit</li> <li>On-chip divider: 32-bit + 32-bit → 32 bits</li> <li>Barrel shifter: 32 bits</li> <li>Memory protection unit (MPU)</li> </ul>                                                                                                                                                                                                                                                                                |

|                   | FPU                               | <ul> <li>Single precision (32-bit) floating point</li> <li>Data types and floating-point exceptions in conformance with the IEEE754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Memory            | ROM                               | <ul> <li>Capacity: 128/256/384/512 Kbytes</li> <li>Up to 32 MHz: No-wait memory access</li> <li>32 to 54 MHz: Wait state required. No wait state if the instruction is served by a ROM accelerator hit</li> <li>Programming/erasing method:</li> <li>Serial programming (asynchronous serial communication/USB communication), self-programming</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | RAM                               | <ul><li>Capacity: 32/64 Kbytes</li><li>54 MHz, no-wait memory access</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | E2 DataFlash                      | Capacity: 8 Kbytes     Number of erase/write cycles: 1,000,000 (typ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MCU operating m   | ode                               | Single-chip mode, on-chip ROM enabled expansion mode, and on-chip ROM disabled expansion mode (software switching)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

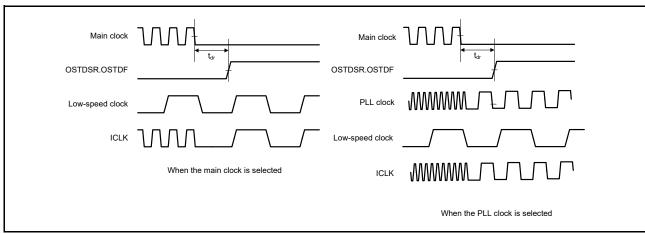

| Clock             | Clock generation circuit          | <ul> <li>Main clock oscillator, sub-clock oscillator, low-speed on-chip oscillator, high-speed on-chip oscillator, PLL frequency synthesizer, USB-dedicated PLL frequency synthesizer, and IWDT-dedicated on-chip oscillator</li> <li>Oscillation stop detection: Available</li> <li>Clock frequency accuracy measurement circuit (CAC)</li> <li>Independent settings for the system clock (ICLK), peripheral module clock (PCLK), external bus clock (BCLK), and FlashIF clock (FCLK)</li> <li>The CPU and system sections such as other bus masters run in synchronization with the system clock (ICLK): 54 MHz (at max.)</li> <li>MTU2a runs in synchronization with the PCLKA: 54 MHz (at max.)</li> <li>The ADCLK for the S12AD runs in synchronization with the PCLKD: 54 MHz (at max.)</li> <li>Peripheral modules other than MTU2a and S12ADE run in synchronization with the PCLKB: 32 MHz (at max.)</li> <li>Devices connected to external buses run in synchronization with the BCLK: 32 MHz (at max.)</li> <li>The flash peripheral circuit runs in synchronization with the FCLK: 32 MHz (at max.)</li> </ul> |

| Resets            |                                   | RES# pin reset, power-on reset, voltage monitoring reset, watchdog timer reset, independent watchdog timer reset, and software reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Voltage detection | Voltage detection circuit (LVDAb) | <ul> <li>When the voltage on VCC falls below the voltage detection level, an internal reset or internal interrupt is generated.</li> <li>Voltage detection circuit 0 is capable of selecting the detection voltage from 4 levels</li> <li>Voltage detection circuit 1 is capable of selecting the detection voltage from 14 levels</li> <li>Voltage detection circuit 2 is capable of selecting the detection voltage from 4 levels</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 1.1 Outline of Specifications (4/4)

| Classification          | Module/Function                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Communication functions | Serial Sound Interface (SSI)      | <ul> <li>1 channel</li> <li>Capable of duplex communications</li> <li>Various serial audio formats supported</li> <li>Master/slave function supported</li> <li>Programmable word clock or bit clock generation function</li> <li>8/16/18/20/22/24/32-bit data formats supported</li> <li>On-chip 8-stage FIFO for transmission/reception</li> <li>Supports WS continue mode in which the SSIWS signal is not stopped.</li> </ul>                                                                                                                                                                                                                                                                                                              |

|                         | SD Host Interface (SDHIa)         | 1 channel     Transfer speed : Default speed mode (8MB/s)     SD memory card interface (1 bit / 4bits SD bus)     MMC, eMMC Backward-compatible are supported.     SD Specifications     Part 1: Compliant with Physical Layer Specification Ver.3.01 (Not support DDR)     Part E1: SDIO Specification Ver. 3.00     Error check function: CRC7 (command), CRC16 (data)     Interrupt Source: Card access interrupt, SDIO access interrupt, Card detection interrupt, SD buffer access interrupt     DMA transfer sources: SD_BUF write, SD_BUF read     Card detection, Write protection                                                                                                                                                    |

| Encryption<br>functions | Trusted Secure IP (TSIP-<br>Lite) | <ul> <li>Access management circuit</li> <li>Encryption engine 128- or 256-bit key sizes of AES Block cipher mode of operation: GCM, ECB, CBC, CMAC, XTS, CTR, GCTR</li> <li>Hash function</li> <li>True random number generator</li> <li>Prevention from illicit copying of a key</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12-bit A/D converte     | er (S12ADE)                       | <ul> <li>12 bits (24 channels × 1 unit)</li> <li>12-bit resolution</li> <li>Minimum conversion time: 0.83 µs per channel when the ADCLK is operating at 54 MHz</li> <li>Operating modes     Scan mode (single scan mode, continuous scan mode, and group scan mode)     Group A priority control (only for group scan mode)</li> <li>Sampling variable     Sampling time can be set up for each channel.</li> <li>Self-diagnostic function</li> <li>Double trigger mode (A/D conversion data duplicated)</li> <li>Detection of analog input disconnection</li> <li>A/D conversion start conditions     A software trigger, a trigger from a timer (MTU, TPU), an external trigger signal, or ELC</li> <li>Event linking by the ELC</li> </ul> |

| Temperature senso       | or (TEMPSA)                       | <ul> <li>1 channel</li> <li>The voltage output from the temperature sensor is converted into a digital value by the 12-bit A/D converter.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12-bit D/A converte     | er (R12DAA)                       | <ul> <li>2 channels</li> <li>12-bit resolution</li> <li>Output voltage: 0.4 to AVCC0-0.5V</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CRC calculator (Cl      | RC)                               | <ul> <li>CRC code generation for arbitrary amounts of data in 8-bit units</li> <li>Select any of three generating polynomials:         X<sup>8</sup> + X<sup>2</sup> + X + 1, X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1, or X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1</li> <li>Generation of CRC codes for use with LSB-first or MSB-first communications is selectable.</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

| Comparator B (CN        | IPBa)                             | 2 channels × 2 units     Function to compare the reference voltage and the analog input voltage     Window comparator operation or standard comparator operation is selectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Capacitive touch s      | ensing unit (CTSU)                | Detection pin: 24 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Data operation circ     | cuit (DOC)                        | Comparison, addition, and subtraction of 16-bit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Power supply volta      | ages/Operating frequencies        | VCC = 1.8 to 2.4 V: 8 MHz, VCC = 2.4 to 2.7 V: 16 MHz, VCC = 2.7 to 5.5 V: 54 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operating tempera       | ture range                        | D version: -40 to +85°C, G version: -40 to +105°C  100-pin TFLGA (PTLG0100KA-A) 5.5 × 5.5 mm, 0.5 mm pitch 100-pin LFQFP (PLQP0100KB-B) 14 × 14 mm, 0.5 mm pitch 64-pin WFLGA (PWLG0064KA-A) 5 × 5 mm, 0.5 mm pitch 64-pin HWQFN (PWQN0064KC-A) 9 × 9 mm, 0.5 mm pitch 64-pin LFQFP (PLQP0064KB-C) 10 × 10 mm, 0.5 mm pitch 48-pin HWQFN (PWQN0048KB-A) 7 × 7 mm, 0.5 mm pitch                                                                                                                                                                                                                                                                                                                                                                |

|                         |                                   | 48-pin LFQFP (PLQP0048KB-B) 7 × 7 mm, 0.5 mm pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 1.2 Comparison of Functions for Different Packages

|                                       |                                         | RX230 Group RX231 Group                                                                            |                                                       |                                        |                                      |                                                       |                                    |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------|--|

| Module/Functions                      |                                         | 100 Pins                                                                                           | 64 Pins                                               | 48 Pins                                | 100 Pins                             | 64 Pins                                               | 48 Pins                            |  |

| External bus                          | External bus                            | 16 bit                                                                                             | Not sup                                               | oported                                | 16 bit                               | Not sup                                               | ported                             |  |

| Interrupts                            | External interrupts                     | NMI, IRQ0<br>to IRQ7                                                                               | NMI, IRQ0,<br>IRQ1, IRQ4<br>to IRQ7                   | NMI, IRQ0,<br>IRQ1, IRQ4<br>to IRQ7    | NMI, IRQ0<br>to IRQ7                 | NMI, IRQ0,<br>IRQ1, IRQ4<br>to IRQ7                   | NMI, IRQ0<br>IRQ1, IRQ4<br>to IRQ7 |  |

| DMA                                   | DMA controller                          | 4 channe                                                                                           | els (DMAC0 to                                         | DMAC3)                                 | 4 channe                             | els (DMAC0 to                                         | DMAC3)                             |  |

|                                       | Data transfer controller                |                                                                                                    | Available                                             |                                        |                                      | Available                                             |                                    |  |

| Timers                                | 16-bit timer pulse unit                 | 6 chan                                                                                             | nels (TPU0 to                                         | TPU5)                                  | 6 chan                               | nels (TPU0 to                                         | TPU5)                              |  |

|                                       | Multi-function timer pulse unit 2       | 6 chanı                                                                                            | nels (MTU0 to                                         | MTU5)                                  | 6 chan                               | nels (MTU0 to                                         | MTU5)                              |  |

|                                       | Port output enable 2                    | POE0# to POE3#, POE8#                                                                              |                                                       |                                        | POE0                                 | # to POE3#, F                                         | OE8#                               |  |

|                                       | 8-bit timer                             | 2 0                                                                                                | channels× 2 ur                                        | nits                                   | 2 0                                  | channels× 2 ur                                        | nits                               |  |

|                                       | Compare match timer                     | 2 c                                                                                                | hannels× 2 ur                                         | nits                                   | 2 0                                  | hannels× 2 ur                                         | nits                               |  |

|                                       | Low power timer                         |                                                                                                    | 1 channel                                             |                                        |                                      | 1 channel                                             |                                    |  |

|                                       | Realtime clock                          | Available Not supported                                                                            |                                                       | Avai                                   | lable                                | Not<br>supported                                      |                                    |  |

|                                       | Watchdog timer                          |                                                                                                    | Available                                             |                                        |                                      | Available                                             |                                    |  |

|                                       | Independent watchdog timer              | Available                                                                                          |                                                       |                                        |                                      | Available                                             |                                    |  |

| Communication functions               | Serial communications interfaces (SCIg) | 6 channels (SCI0, 1, 5, 6, 8, 9) 5 channels (SCI1, 5, 6, 8, 9) 8) 4 channels (SCI1, 5, 6, 8, 9) 8) |                                                       | 6 channels<br>(SCI0, 1, 5,<br>6, 8, 9) | 5 channels<br>(SCI1, 5, 6,<br>8, 9)  | 4 channels<br>(SCI1, 5, 6<br>8)                       |                                    |  |

|                                       | IrDA interface                          | 1                                                                                                  | channel (SCI                                          | 5)                                     | 1                                    | channel (SCI                                          | 5)                                 |  |

|                                       | Serial communications interfaces (SCIh) | 1                                                                                                  | channel (SCI1                                         | 2)                                     | 1 channel (SCI12)                    |                                                       |                                    |  |

|                                       | I <sup>2</sup> C bus interface          | 1 channel                                                                                          |                                                       |                                        | 1 channel                            |                                                       |                                    |  |

|                                       | CAN module                              |                                                                                                    | Not supported                                         |                                        | 1 channel*1                          |                                                       |                                    |  |

|                                       | Serial peripheral interface             |                                                                                                    | 1 channel                                             |                                        | 1 channel                            |                                                       |                                    |  |

|                                       | USB 2.0 host/function module            |                                                                                                    | Not supported                                         |                                        | 1 channel                            |                                                       |                                    |  |

|                                       | Serial sound interface                  |                                                                                                    | 1 channel                                             |                                        | 1 channel                            |                                                       |                                    |  |

|                                       | SD Host Interface                       |                                                                                                    | Not supported                                         |                                        | 1 channel*1                          |                                                       | Not<br>supported                   |  |

| Capacitive touch                      | sensing unit                            | 24 channels                                                                                        | 10 channels                                           | 6 channels                             | 24 channels                          | 10 channels                                           | 6 channels                         |  |

| 12-bit A/D conve<br>(including high-p | erter<br>recision channels)             | 24 channels<br>(8<br>channels)                                                                     | 12 channels<br>(6<br>channels)                        | 8 channels<br>(4<br>channels)          | 24 channels<br>(8<br>channels)       | 12 channels<br>(6<br>channels)                        | 8 channels<br>(4<br>channels)      |  |

| Temperature ser                       | nsor                                    |                                                                                                    | Available                                             |                                        |                                      | Available                                             |                                    |  |

| D/A converter                         |                                         | 2 cha                                                                                              | nnels                                                 | Not<br>supported                       | 2 cha                                | nnels                                                 | Not<br>supported                   |  |

| CRC calculator                        |                                         |                                                                                                    | Available                                             | l .                                    |                                      | Available                                             | I.                                 |  |

| Event link controller                 |                                         |                                                                                                    | Available                                             |                                        |                                      | Available                                             |                                    |  |

| Comparator B Packages                 |                                         |                                                                                                    | 4 channels                                            |                                        |                                      | 4 channels                                            |                                    |  |

|                                       |                                         | 100-pin<br>TFLGA<br>100-pin<br>LFQFP                                                               | 64-pin<br>WFLGA<br>64-pin<br>HWQFN<br>64-pin<br>LFQFP | 48-pin<br>HWQFN<br>48-pin<br>LFQFP     | 100-pin<br>TFLGA<br>100-pin<br>LFQFP | 64-pin<br>WFLGA<br>64-pin<br>HWQFN<br>64-pin<br>LFQFP | 48-pin<br>HWQFN<br>48-pin<br>LFQFP |  |

Note 1. Only for chip version B

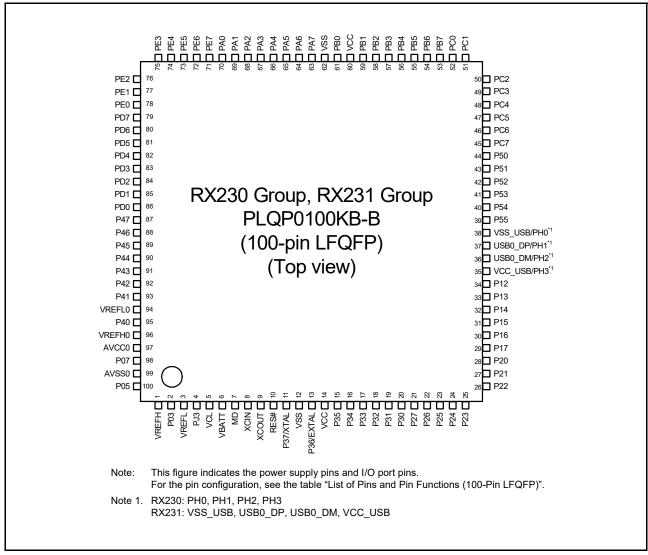

Figure 1.4 Pin Assignments of the 100-Pin LFQFP

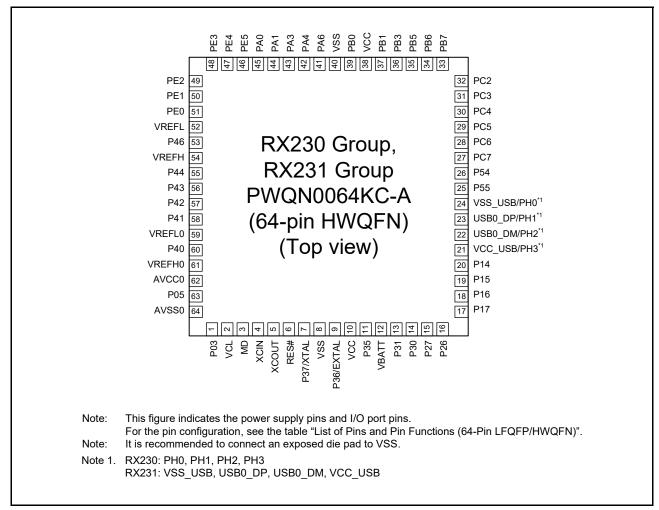

Figure 1.6 Pin Assignments of the 64-Pin HWQFN

### (9) Floating-point status word (FPSW)

The floating-point status word (FPSW) indicates the results of floating-point operations.

When an exception handling enable bit (Ej) enables the exception handling (Ej = 1), the exception cause can be identified by checking the corresponding Cj flag in the exception handling routine. If the exception handling is masked (Ej = 0), the occurrence of exception can be checked by reading the Fj flag at the end of a series of processing. Once the Fj flag has been set to 1, this value is retained until it is cleared to 0 by software (j = X, U, Z, O, or V).

#### 2.3 Accumulator

The accumulator (ACC0 or ACC1) is a 72-bit register used for DSP instructions. The accumulator is handled as a 96-bit register for reading and writing. At this time, when bits 95 to 72 of the accumulator are read, the value where the value of bit 71 is sign extended is read. Writing to bits 95 to 72 of the accumulator is ignored. ACC0 is also used for the multiply and multiply-and-accumulate instructions; EMUL, EMULU, FMUL, MUL, and RMPA, in which case the prior value in ACC0 is modified by execution of the instruction.

Use the MVTACGU, MVTACHI, and MVTACLO instructions for writing to the accumulator. The MVTACGU, MVTACHI, and MVTACLO instructions write data to bits 95 to 64, the higher-order 32 bits (bits 63 to 32), and the lower-order 32 bits (bits 31 to 0), respectively.

Use the MVFACGU, MVFACHI, MVFACMI, and MVFACLO instructions for reading data from the accumulator. The MVFACGU, MVFACHI, MVFACMI, and MVFACLO instructions read data from the guard bits (bits 95 to 64), higher-order 32 bits (bits 63 to 32), the middle 32 bits (bits 47 to 16), and the lower-order 32 bits (bits 31 to 0), respectively.

Table 4.1 List of I/O Registers (Address Order) (17/33)

| Module    |        | ule                               |                    | Number  | Access | Number of Access Cycles |                            |  |

|-----------|--------|-----------------------------------|--------------------|---------|--------|-------------------------|----------------------------|--|

| ddress    | Symbol | Register Name                     | Register<br>Symbol | of Bits | Size   | ICLK ≥ PCLK             | ICLK <pclk< th=""></pclk<> |  |

| 08 C0A4h  | PORTJ  | Open Drain Control Register 0     | ODR0               | 8       | 8, 16  | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0C0h  | PORT0  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0C1h  | PORT1  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0C2h  | PORT2  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0C3h  | PORT3  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C0C4h | PORT4  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0C5h  | PORT5  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0CAh  | PORTA  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0CBh  | PORTB  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C0CCh | PORTC  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0CDh  | PORTD  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0CEh  | PORTE  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0D1h  | PORTH  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0D2h  | PORTJ  | Pull-Up Control Register          | PCR                | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0E1h  | PORT1  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0E2h  | PORT2  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0E3h  | PORT3  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0E5h  | PORT5  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0EAh  | PORTA  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0EBh  | PORTB  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C0ECh | PORTC  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0EDh  | PORTD  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C0EEh | PORTE  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C0F1h | PORTH  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C0F2h  | PORTJ  | Drive Capacity Control Register   | DSCR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C100h | MPC    | CS Output Enable Register         | PFCSE              | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C104h  | MPC    | Address Output Enable Register 0  | PFAOE0             | 8       | 8, 16  | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C105h  | MPC    | Address Output Enable Register 1  | PFAOE1             | 8       | 8, 16  | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C106h | MPC    | External Bus Control Register 0   | PFBCR0             | 8       | 8, 16  | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C107h  | MPC    | External Bus Control Register 1   | PFBCR1             | 8       | 8, 16  | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C11Fh  | MPC    | Write-Protect Register            | PWPR               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C120h | PORT   | <u> </u>                          | PSRB               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

|           |        | Port Switching Register B         |                    |         |        |                         |                            |  |

| 08 C121h  | PORT   | Port Switching Register A         | PSRA               | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C143h | MPC    | P03 Pin Function Control Register | P03PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C145h | MPC    | P05 Pin Function Control Register | P05PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C147h | MPC    | P07 Pin Function Control Register | P07PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C14Ah | MPC    | P12 Pin Function Control Register | P12PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C14Bh  | MPC    | P13 Pin Function Control Register | P13PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C14Ch  | MPC    | P14 Pin Function Control Register | P14PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C14Dh | MPC    | P15 Pin Function Control Register | P15PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C14Eh | MPC    | P16 Pin Function Control Register | P16PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C14Fh  | MPC    | P17 Pin Function Control Register | P17PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C150h  | MPC    | P20 Pin Function Control Register | P20PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C151h  | MPC    | P21 Pin Function Control Register | P21PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C152h  | MPC    | P22 Pin Function Control Register | P22PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C153h  | MPC    | P23 Pin Function Control Register | P23PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C154h  | MPC    | P24 Pin Function Control Register | P24PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C155h  | MPC    | P25 Pin Function Control Register | P25PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C156h  | MPC    | P26 Pin Function Control Register | P26PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C157h  | MPC    | P27 Pin Function Control Register | P27PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 08 C158h  | MPC    | P30 Pin Function Control Register | P30PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C159h | MPC    | P31 Pin Function Control Register | P31PFS             | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

Table 4.1 List of I/O Registers (Address Order) (19/33)

|           | Module |                                                             | Register  | Number  | Access | Number of Access Cycles |                            |  |

|-----------|--------|-------------------------------------------------------------|-----------|---------|--------|-------------------------|----------------------------|--|

| Address   | Symbol | Register Name                                               | Symbol    | of Bits | Size   | ICLK ≥ PCLK             | ICLK <pclk< th=""></pclk<> |  |

| 008 C1B3h | MPC    | PE3 Pin Function Control Register                           | PE3PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1B4h | MPC    | PE4 Pin Function Control Register                           | PE4PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1B5h | MPC    | PE5 Pin Function Control Register                           | PE5PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1B6h | MPC    | PE6 Pin Function Control Register                           | PE6PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1B7h | MPC    | PE7 Pin Function Control Register                           | PE7PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1C8h | MPC    | PH0 Pin Function Control Register                           | PH0PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1C9h | MPC    | PH1 Pin Function Control Register                           | PH1PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1CAh | MPC    | PH2 Pin Function Control Register                           | PH2PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1CBh | MPC    | PH3 Pin Function Control Register                           | PH3PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C1D3h | MPC    | PJ3 Pin Function Control Register                           | PJ3PFS    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C290h | SYSTEM | Reset Status Register 0                                     | RSTSR0    | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C291h | SYSTEM | Reset Status Register 1                                     | RSTSR1    | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C293h | SYSTEM | Main Clock Oscillator Forced Oscillation Control Register   | MOFCR     | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C297h | SYSTEM | Voltage Monitoring Circuit Control Register                 | LVCMPCR   | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C298h | SYSTEM | Voltage Detection Level Select Register                     | LVDLVLR   | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C29Ah | SYSTEM | Voltage Monitoring 1 Circuit Control Register 0             | LVD1CR0   | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C29Bh | SYSTEM | Voltage Monitoring 2 Circuit Control Register 0             | LVD2CR0   | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C29Dh | SYSTEM | VBATT Control Register                                      | VBATTCR   | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C29Eh | SYSTEM | VBATT Status Register                                       | VBATTSR   | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICLI                |  |

| 008 C29Fh | SYSTEM | VBATT Pin Voltage Drop Detection Interrupt Control Register | VBTLVDICR | 8       | 8      | 4 or 5 PCLKB            | 2 or 3 ICL                 |  |

| 008 C400h | RTC    | 64-Hz Counter                                               | R64CNT    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C402h | RTC    | Second Counter                                              | RSECCNT   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C402h | RTC    | Binary Counter 0                                            | BCNT0     | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C404h | RTC    | Minute Counter                                              | RMINCNT   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C404h | RTC    | Binary Counter 1                                            | BCNT1     | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C406h | RTC    | Hour Counter                                                | RHRCNT    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C406h | RTC    | Binary Counter 2                                            | BCNT2     | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C408h | RTC    | Day-of-Week Counter                                         | RWKCNT    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C408h | RTC    | Binary Counter 3                                            | BCNT3     | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C40Ah | RTC    | Date Counter                                                | RDAYCNT   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C40Ch | RTC    | Month Counter                                               | RMONCNT   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C40Eh | RTC    | Year Counter                                                | RYRCNT    | 16      | 16     | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C410h | RTC    | Second Alarm Register                                       | RSECAR    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C410h | RTC    | Binary Counter 0 Alarm Register                             | BCNT0AR   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C412h | RTC    | Minute Alarm Register                                       | RMINAR    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C412h | RTC    | Binary Counter 1 Alarm Register                             | BCNT1AR   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C414h | RTC    | Hour Alarm Register                                         | RHRAR     | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C414h | RTC    | Binary Counter 2 Alarm Register                             | BCNT2AR   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C416h | RTC    | Day-of-Week Alarm Register                                  | RWKAR     | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C416h | RTC    | Binary Counter 3 Alarm Register                             | BCNT3AR   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C418h | RTC    | Date Alarm Register                                         | RDAYAR    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C418h | RTC    | Binary Counter 0 Alarm Enable Register                      | BCNT0AER  | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C41Ah | RTC    | Month Alarm Register                                        | RMONAR    | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C41Ah | RTC    | Binary Counter 1 Alarm Enable Register                      | BCNT1AER  | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C41Ch | RTC    | •                                                           | RYRAR     | 16      | 16     |                         | 2 ICLK                     |  |

|           | RTC    | Year Alarm Register  Binary Counter 2 Alarm Enable Register |           |         |        | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C41Ch |        | Binary Counter 2 Alarm Enable Register                      | BCNT2AER  | 16      | 16     | 2 or 3 PCLKB            |                            |  |

| 008 C41Eh | RTC    | Year Alarm Enable Register                                  | RYRAREN   | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C41Eh | RTC    | Binary Counter 3 Alarm Enable Register                      | BCNT3AER  | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C422h | RTC    | RTC Control Register 1                                      | RCR1      | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

| 008 C424h | RTC    | RTC Control Register 2                                      | RCR2      | 8       | 8      | 2 or 3 PCLKB            | 2 ICLK                     |  |

### 5.2 DC Characteristics

Table 5.3 DC Characteristics (1)

Conditions:  $2.7 \text{ V} \le \text{VCC} = \text{VCC\_USB} \le 5.5 \text{ V}, 2.7 \text{ V} \le \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS\_USB} = 0 \text{ V}, \text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

|                               | Item                                                                                                                                                            |                        | Symbol          | Min.        | Тур.      | Max.        | Unit | Test<br>Conditions |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-------------|-----------|-------------|------|--------------------|

| Schmitt trigger input voltage | RIIC input pin (except for SMB)                                                                                                                                 | ıs, 5 V tolerant)      | V <sub>IH</sub> | VCC × 0.7   | _         | 5.8         | V    |                    |

|                               | Ports 12, 13, 16, (5 V tolerant)                                                                                                                                | 17, port B5            |                 | VCC × 0.8   | _         | 5.8         |      |                    |

|                               | Ports 14 to 15, pports 33 to 37, ports A0 to A7, ports B0 to B4, B ports C0 to C7, ports D0 to D7, ports E0 to E7, port J3, Ports 30 to 32 (wevent input is not |                        | VCC × 0.8       | _           | VCC + 0.3 |             |      |                    |

|                               | Ports 03, 05, 07,                                                                                                                                               | ports 40 to 47         |                 | AVCC0 × 0.8 | _         | AVCC0 + 0.3 |      |                    |

|                               | Ports 30 to 32<br>(when time                                                                                                                                    | When VCC is supplied   |                 | VCC × 0.8   | _         | VCC + 0.3   |      |                    |

|                               | capture event input is selected)                                                                                                                                | When VBATT is supplied |                 | VBATT × 0.8 | _         | VBATT + 0.3 |      |                    |

|                               | Ports 03, 05, 07,                                                                                                                                               | ports 40 to 47         | $V_{IL}$        | -0.3        | _         | AVCC0 × 0.2 |      |                    |

|                               | RIIC input pin (ex                                                                                                                                              | ccept for SMBus)       |                 | -0.3        | _         | VCC × 0.3   |      |                    |

|                               | Other than RIIC i<br>30 to 32                                                                                                                                   | nput pin or ports      |                 | -0.3        | _         | VCC × 0.2   |      |                    |

|                               | Ports 30 to 32<br>(when time                                                                                                                                    | When VCC is supplied   |                 | -0.3        | _         | VCC × 0.3   |      |                    |

|                               | capture event input is selected)                                                                                                                                | When VBATT is supplied |                 | -0.3        | _         | VBATT × 0.3 |      |                    |

|                               | Ports 03, 05, 07,                                                                                                                                               | ports 40 to 47         | $\Delta V_{T}$  | AVCC0 × 0.1 | _         | _           |      |                    |

|                               | RIIC input pin (ex                                                                                                                                              | (cept for SMBus)       |                 | VCC × 0.05  | _         | _           |      |                    |

|                               | Ports 12, 13, 16,                                                                                                                                               | 17, Port B5            |                 | VCC × 0.05  | _         | _           |      |                    |

|                               | Other than RIIC i                                                                                                                                               | nput pin               |                 | VCC × 0.1   | _         | _           |      |                    |

| Input level                   | MD                                                                                                                                                              |                        | $V_{IH}$        | VCC × 0.9   | _         | VCC + 0.3   | V    |                    |

| voltage (except for Schmitt   | EXTAL (external                                                                                                                                                 | clock input)           |                 | VCC × 0.8   | _         | VCC + 0.3   |      |                    |

| trigger input                 | RIIC input pin (S                                                                                                                                               | MBus)                  |                 | 2.1         | _         | VCC + 0.3   |      |                    |

| pins)                         | MD                                                                                                                                                              |                        | V <sub>IL</sub> | -0.3        | _         | VCC × 0.1   |      |                    |

|                               | EXTAL (external                                                                                                                                                 | clock input)           |                 | -0.3        |           | VCC × 0.2   |      |                    |

|                               | RIIC input pin (S                                                                                                                                               | MBus)                  |                 | -0.3        | 1         | 0.8         |      |                    |

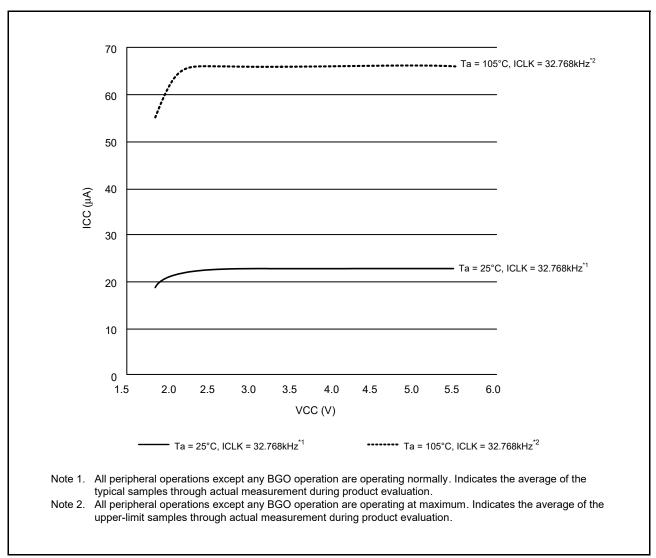

Figure 5.3 Voltage Dependency in Low-Speed Operating Mode (Reference Data)

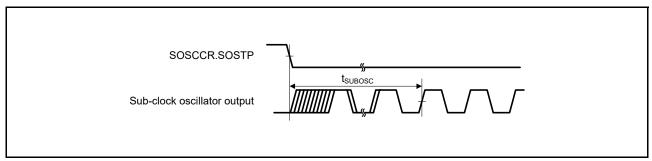

Figure 5.30 Sub-Clock Oscillation Start Timing

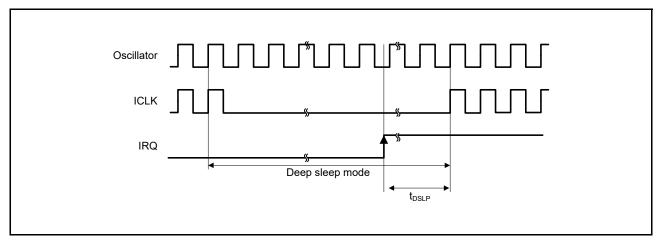

Figure 5.35 Deep Sleep Mode Recovery Timing

Table 5.32 Operating Mode Transition Time

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC\_USB} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS\_USB} = 0 \text{ V}$ ,  $\text{T}_a = -40 \text{ to } +105 ^{\circ}\text{C}$

| Mode before Transition                                 | Mode after Transition                                  | ICLK Frequency | Tra  | Unit |      |       |

|--------------------------------------------------------|--------------------------------------------------------|----------------|------|------|------|-------|

| Wode before Transition                                 | Wode after Transition                                  | ICLK Frequency | Min. | Тур. | Max. | Offic |

| High-speed operating mode                              | Middle-speed operating modes                           | 8 MHz          | _    | 10   | _    | μs    |

| Middle-speed operating modes                           | High-speed operating mode                              | 8 MHz          | _    | 37.5 | _    | μs    |

| Low-speed operating mode                               | Middle-speed operating mode, high-speed operating mode | 32.768 kHz     | _    | 215  | _    | μs    |

| Middle-speed operating mode, high-speed operating mode | Low-speed operating mode                               | 32.768 kHz     | _    | 185  | _    | μs    |

Note: Values when the frequencies of PCLKA, PCLKB, PCLKD, FCLK, and BCLK are not divided.

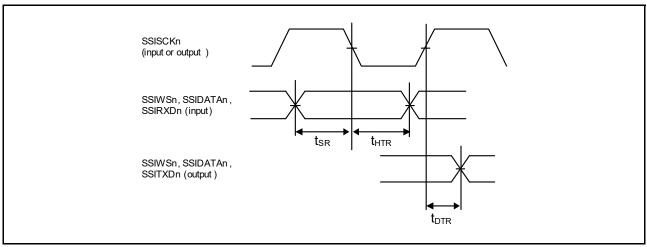

Figure 5.62 SSI Transmission/Reception Timing (SSICR.SCKP=1)

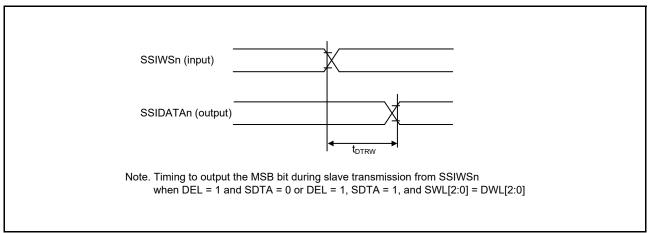

Figure 5.63 SSIDATA Output Delay After SSIWSn Changing Edge

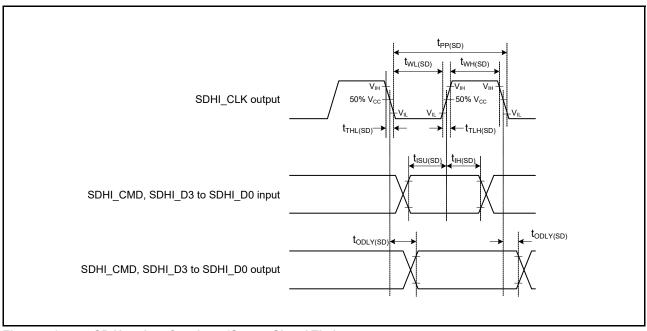

Figure 5.64 SD Host Interface Input/Output Signal Timing

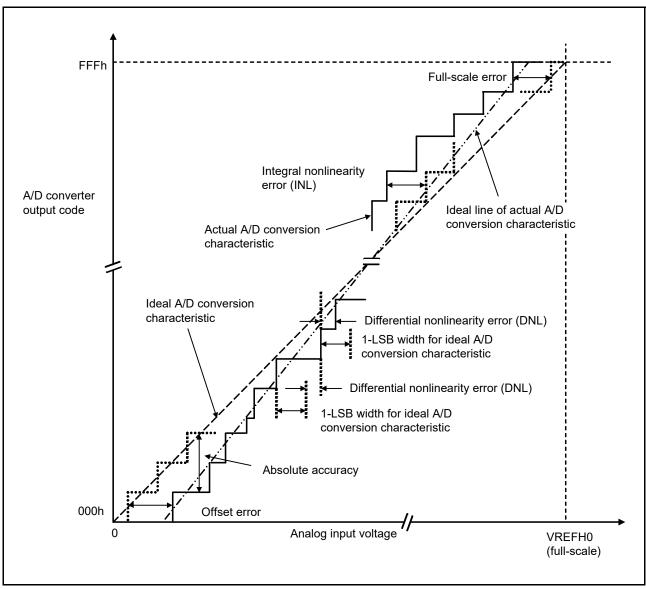

Figure 5.69 Illustration of A/D Converter Characteristic Terms

### **Absolute accuracy**

Absolute accuracy is the difference between output code based on the theoretical A/D conversion characteristics and the actual A/D conversion result. When measuring absolute accuracy, the voltage at the midpoint of the width of analog input voltage (1-LSB width), that can meet the expectation of outputting an equal code based on the theoretical A/D conversion characteristics, is used as an analog input voltage. For example, if 12-bit resolution is used and if reference voltage (VREFH0 = 3.072 V), then 1-LSB width becomes 0.75 mV, and 0 mV, 0.75 mV, 1.5 mV, ... are used as analog input voltages.

If analog input voltage is 6 mV, absolute accuracy =  $\pm 5$  LSB means that the actual A/D conversion result is in the range of 003h to 00Dh, although an output code, 008h, can be expected from the theoretical A/D conversion characteristics.

#### Integral non-linearity error (INL)

The integral non-linearity error is the maximum deviation between the ideal line when the measured offset and full-scale errors are zeroed, and the actual output code.

Table 5.59 Characteristics of Power-On Reset Circuit and Voltage Detection Circuit (2)

Conditions: 1.8 V  $\leq$  VCC0 = VCC\_USB = AVCC0  $\leq$  5.5 V, VSS = AVSS0 = VSS\_USB = 0 V,  $T_a = -40$  to +105°C

|                                                                    | Item                                                |                     | Min. | Тур. | Max. | Unit        | Test Conditions                     |

|--------------------------------------------------------------------|-----------------------------------------------------|---------------------|------|------|------|-------------|-------------------------------------|

| Wait time after                                                    | At normal startup*1                                 | t <sub>POR</sub>    | _    | 9.1  | _    | ms          | Figure 5.74                         |

| power-on reset cancellation  During fast startup time*2            |                                                     | t <sub>POR</sub>    | _    | 1.6  | _    |             |                                     |

| Wait time after voltage monitoring 0 monitoring 0 reset disabled*1 |                                                     | t <sub>LVD0</sub>   | _    | 568  | _    | μs          | Figure 5.75                         |

|                                                                    | Power-on voltage<br>monitoring 0 reset<br>enabled*2 |                     | _    | 100  | _    |             |                                     |

| Wait time after voltage cancellation                               | e monitoring 1 reset                                | t <sub>LVD1</sub>   | _    | 100  | _    | μs          | Figure 5.76                         |

| Wait time after voltage cancellation                               | e monitoring 2 reset                                | t <sub>LVD2</sub>   | _    | 100  | _    | μs          | Figure 5.77                         |

| Response delay time                                                | t <sub>det</sub>                                    | _                   | _    | 350  | μs   | Figure 5.73 |                                     |

| Minimum VCC down to                                                | ime* <sup>3</sup>                                   | t <sub>VOFF</sub>   | 350  | _    | _    | μs          | Figure 5.73, VCC = 1.0 V or above   |

| Power-on reset enabl                                               | e time                                              | t <sub>W(POR)</sub> | 1    | _    | _    | ms          | Figure 5.74, VCC = below 1.0<br>V   |

| LVD operation stabilizenabled)                                     | ation time (after LVD is                            | Td <sub>(E-A)</sub> | _    | _    | 300  | μs          | Figure 5.76, Figure 5.77            |

| Hysteresis width (pow                                              | rer-on rest (POR))                                  | V <sub>PORH</sub>   | _    | 110  | _    | mV          |                                     |

| Hysteresis width (volta and LVD2)                                  | age detection circuit: LVD1                         | $V_{LVH}$           | _    | 70   | _    | mV          | When Vdet1_0 to Vdet1_4 is selected |

|                                                                    |                                                     |                     | _    | 60   | _    |             | When Vdet1_5 to Vdet1_9 is selected |

|                                                                    |                                                     |                     | _    | 50   | _    |             | When Vdet1_A or Vdet1_B is selected |

|                                                                    |                                                     |                     | _    | 40   | _    |             | When Vdet1_C or Vdet1_D is selected |

|                                                                    |                                                     |                     | _    | 60   | _    | 1           | When LVD2 is selected               |

Note: These characteristics apply when noise is not superimposed on the power supply. When a setting is made so that the voltage detection level overlaps with that of the voltage detection circuit (LVD1), it cannot be specified which of LVD1 and LVD2 is used for voltage detection.

Note 1. When OFS1.(LVDAS, FASTSTUP) = 11b.

Note 2. When OFS1 (LVDAS, FASTSTUP) ≠ 11b.

Note 3. The minimum VCC down time indicates the time when VCC is below the minimum value of voltage detection levels  $V_{POR}$ ,  $V_{det0}$ ,  $V_{det1}$ , and  $V_{det2}$  for the POR/LVD.

# 5.11 Oscillation Stop Detection Timing

Table 5.60 Oscillation Stop Detection Timing

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC\_USB} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS\_USB} = 0 \text{ V}$ ,  $\text{T}_a = -40 \text{ to } +105 ^{\circ}\text{C}$

| Item           | Symbol          | Min. | Тур. | Max. | Unit | Test Conditions |

|----------------|-----------------|------|------|------|------|-----------------|

| Detection time | t <sub>dr</sub> | _    | _    | 1    | ms   | Figure 5.78     |

Figure 5.78 Oscillation Stop Detection Timing

Table 5.64 ROM (Flash Memory for Code Storage) Characteristics (3) Middle-Speed Operating Mode

Conditions: 1.8  $V \le VCC = VCC\_USB = AVCC0 \le 5.5 V$ ,  $VSS = AVSS0 = VSS\_USB = 0 V$

Temperature range for the programming/erasure operation:  $T_a = -40$  to +85°C

| Item                                 | Item                                                          |                     | F    | CLK = 1 MH | łz    | F    | Unit |       |    |

|--------------------------------------|---------------------------------------------------------------|---------------------|------|------------|-------|------|------|-------|----|