Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RXv2                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 54MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SD/SDIO, SPI, SSI, USB OTG                          |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 30                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-WFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-HWQFN (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52315cdne-u0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification             | Module/Function                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timers                     | Independent watchdog<br>timer (IWDTa)            | <ul> <li>14 bits × 1 channel</li> <li>Count clock: Dedicated low-speed on-chip oscillator for the IWDT<br/>Frequency divided by 1, 16, 32, 64, 128, or 256</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | Realtime clock (RTCe)                            | <ul> <li>Clock source: Sub-clock</li> <li>Time/calendar</li> <li>Interrupts: Alarm interrupt, periodic interrupt, and carry interrupt</li> <li>Time-capture facility for three values</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | Low power timer (LPT)                            | <ul> <li>16 bits × 1 channel</li> <li>Clock source: Sub-clock, Dedicated low-speed on-chip oscillator for the IWDT Frequency divided by 2, 4, 8, 16, or 32</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | 8-bit timer (TMR)                                | <ul> <li>(8 bits × 2 channels) × 2 units</li> <li>Seven internal clocks (PCLK/1, PCLK/2, PCLK/8, PCLK/32, PCLK/64, PCLK/1024, and PCLK/8192) and an external clock can be selected</li> <li>Pulse output and PWM output with any duty cycle are available</li> <li>Two channels can be cascaded and used as a 16-bit timer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Communication<br>functions | Serial communications<br>interfaces (SCIg, SCIh) | <ul> <li>7 channels (channel 0, 1, 5, 6, 8, 9: SCIg, channel 12: SCIh)</li> <li>SCIg Serial communications modes: Asynchronous, clock synchronous, and smart-card interface Multi-processor function On-chip baud rate generator allows selection of the desired bit rate Choice of LSB-first or MSB-first transfer Average transfer rate clock can be input from TMR timers for SCI5, SCI6, and SCI12 Start-bit detection: Level or edge detection is selectable. Simple I<sup>2</sup>C Simple SPI 9-bit transfer mode Bit rate modulation Event linking by the ELC (only on channel 5)</li> <li>SCIh (The following functions are added to SCIg) Supports the serial communications protocol, which contains the start frame and information frame Supports the LIN format</li> </ul> |

|                            | IrDA interface (IRDA)                            | <ul> <li>1 channel (SCI5 used)</li> <li>Supports encoding/decoding of waveforms conforming to IrDA standard 1.0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            | I <sup>2</sup> C bus interface (RIICa)           | <ul> <li>1 channel</li> <li>Communications formats: I<sup>2</sup>C bus format/SMBus format</li> <li>Master mode or slave mode selectable</li> <li>Supports fast mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | Serial peripheral interface<br>(RSPIa)           | <ul> <li>1 channel</li> <li>Transfer facility Using the MOSI (master out, slave in), MISO (master in, slave out), SSL (slave select), and RSPCF (RSPI clock) enables serial transfer through SPI operation (four lines) or clock-synchronous operation (three lines)</li> <li>Capable of handling serial transfer as a master or slave</li> <li>Data formats</li> <li>Choice of LSB-first or MSB-first transfer The number of bits in each transfer can be changed to 8, 9, 10, 11, 12, 13, 14, 15, 16, 20, 24, or 32 bits. 128-bit buffers for transmission and reception Up to four frames can be transmitted or received in a single transfer operation (with each frame having up to 32 bits)</li> <li>Double buffers for both transmission and reception</li> </ul>                |

|                            | USB 2.0 host/function<br>module (USBd)           | <ul> <li>USB Device Controller (UDC) and transceiver for USB 2.0 are incorporated.</li> <li>Host/function module: 1 port</li> <li>Compliant with USB version 2.0</li> <li>Transfer speed: Full-speed (12 Mbps), low-speed (1.5 Mbps)</li> <li>OTG (ON-The-Go) is supported.</li> <li>Isochronous transfer is supported.</li> <li>BC1.2 (Battery Charging Specification Revision 1.2) is supported.</li> <li>Internal power supply for USB (allows operation without external power input to the VCC_USB pin when VCC = 4.0 to 5.5V)</li> </ul>                                                                                                                                                                                                                                          |

|                            | CAN module (RSCAN)                               | <ul> <li>1 channel</li> <li>Compliance with the ISO11898-1 specification (standard frame and extended frame)</li> <li>16 Message boxes</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 1.1Outline of Specifications (3/4)

# 2. CPU

Figure 2.1 shows register set of the CPU.

|                | General-purpose register | Control register                       |

|----------------|--------------------------|----------------------------------------|

|                | b31 b0                   | b31 t                                  |

|                | R0 (SP) <sup>*1</sup>    | ISP (Interrupt stack pointer)          |

|                | R1                       | USP (User stack pointer)               |

|                | R2                       | INITE (Interrupt table register)       |

|                | R3                       | INTB (Interrupt table register)        |

|                | R4                       | PC (Program counter)                   |

|                | R5                       |                                        |

|                | R6                       | PSW (Processor status word)            |

|                | R7                       | BPC (Backup PC)                        |

|                | R8                       |                                        |

|                | R9                       | BPSW (Backup PSW)                      |

|                | R10                      | FINTV (Fast interrupt vector register) |

|                | R11                      |                                        |

|                | R12                      | FPSW (Floating-point status word)      |

|                | R13                      | EXTB (Exception table register)        |

|                | R14                      |                                        |

|                | R15                      |                                        |

| DSP ins<br>b71 | truction register        | b                                      |

|                | ACC0 (Accumul            | ator 0)                                |

|                | ACC1 (Accumul            | ator 1)                                |

Figure 2.1 Register Set of the CPU

# 3. Address Space

## 3.1 Address Space

This LSI has a 4-Gbyte address space, consisting of the range of addresses from 0000 0000h to FFFF FFFFh. That is, linear access to an address space of up to 4 Gbytes is possible, and this contains both program and data areas. Figure 3.1 shows the memory maps in the respective operating modes. Accessible areas will differ according to the operating mode and states of control bits.

#### Number of Access Cycles Register Symbol Number Access Size Module ICLK ≥ PCLK ICLK <PCLK Address Symbol Register Name of Bits 0008 AC44h SDHI SD Interrupt Mask Register 2 SDIMSK2 32 32 3 or 4 PCLKB 3 ICLK cycles when reading, 2 ICLK cycles when cycles when reading, 2 or 3 PCLKB writing cycles when writing 0008 AC48h SDHI SDHI Clock Control Register SDCLKCR 3 or 4 PCLKB 3 ICLK cycles when 32 32 cycles when reading, 2 or 3 PCLKB reading, 2 ICLK cycles when writing cycles when writing 0008 AC4Ch SDHI Transfer Data Size Register SDSIZE 32 32 3 or 4 PCLKB 3 ICLK cycles when reading, 2 ICLK cycles when cycles when reading, 2 or 3 PCLKB writing cycles when writing 0008 AC50h SDHI Card Access Option Register SDOPT 32 32 3 or 4 PCLKB 3 ICLK cycles when cycles when reading, 2 ICLK cycles when reading, 2 or 3 PCLKB writing cycles when writing 0008 AC58h SDHI SD Error Status Register 1 SDERSTS1 32 32 3 or 4 PCLKB 3 ICLK cycles when reading, 2 ICLK cycles when cycles when reading, 2 or 3 PCLKB writing cycles when writing 0008 AC5Ch SDHI SD Error Status Register 2 SDERSTS2 32 32 3 or 4 PCLKB 3 ICLK cycles when cycles when reading, reading, 2 or 3 PCLKB 2 ICLK cycles when writing cycles when writing 0008 AC60h 3 or 4 PCLKB SDHI SD Buffer Register SDBUFR 32 32 3 ICLK cycles when cycles when reading, 2 ICLK cycles when writing reading, 2 or 3 PCLKB cycles when writing 0008 AC68h SDHI SDIO Mode Control Register SDIOMD 32 32 3 or 4 PCLKB 3 ICLK cycles when cvcles when reading, 2 ICLK cycles when reading, 2 or 3 PCLKB writing cycles when writing 0008 AC6Ch 3 or 4 PCLKB SDHI SDIO Status Register SDIOSTS 32 32 3 ICLK cycles when cycles when reading, 2 ICLK cycles when writing reading, 2 or 3 PCLKB cycles when writing 0008 AC70h SDHI SDIO Interrupt Mask Register SDIOIMSK 32 32 3 or 4 PCLKB 3 ICLK cycles when cycles when reading, 2 ICLK cycles when reading, 2 or 3 PCLKB writing cycles when writing 3 or 4 PCLKB 0008 ADB0h SDHI DMA Transfer Enable Register SDDMAEN 32 32 3 ICLK cycles when cycles when reading, 2 ICLK cycles when writing reading, 2 or 3 PCLKB cycles when writing 0008 ADC0h SDHI SDRST 3 or 4 PCLKB SDHI Software Reset Register 32 32 3 ICLK cycles when reading, 2 ICLK cycles when writing cycles when reading, 2 or 3 PCLKB cycles when writing 3 or 4 PCLKB 0008 ADE0h SDHI SDSWAP 32 32 3 ICLK cycles when Swap Control Register cycles when reading. 2 ICLK cycles when writing reading, 2 or 3 PCLKB cycles when writing 0008 B000h CAC Control Register 0 CACR0 8 2 or 3 PCLKB 2 ICLK CAC 8 0008 B001h CAC CAC Control Register 1 CACR1 8 8 2 or 3 PCLKB 2 ICLK

#### Table 4.1 List of I/O Registers (Address Order) (13/33)

CAC

CAC Control Register 2

0008 B002h

CACR2

8

8

2 or 3 PCLKB

2 ICLK

## Table 4.1 List of I/O Registers (Address Order) (28/33)

|           | Module |                                  | Register  | Number  | Access | Number of Access Cycles            |                            |  |

|-----------|--------|----------------------------------|-----------|---------|--------|------------------------------------|----------------------------|--|

| ddress    | Symbol | Register Name                    | Symbol    | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |  |

| 0A 8446h  | RSCAN  | Receive Rule Entry Register 13CH | GAFLPH13  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8446h  | RSCAN  | Receive Buffer Register 10BH     | RMPTR10   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8448h  | RSCAN  | Receive Rule Entry Register 14AL | GAFLIDL14 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8448h | RSCAN  | Receive Buffer Register 10CL     | RMDF010   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 844Ah | RSCAN  | Receive Rule Entry Register 14AH | GAFLIDH14 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 844Ah | RSCAN  | Receive Buffer Register 10CH     | RMDF110   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 844Ch | RSCAN  | Receive Rule Entry Register 14BL | GAFLML14  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 844Ch | RSCAN  | Receive Buffer Register 10DL     | RMDF210   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 844Eh | RSCAN  | Receive Rule Entry Register 14BH | GAFLMH14  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 844Eh | RSCAN  | Receive Buffer Register 10DH     | RMDF310   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8450h  | RSCAN  | Receive Rule Entry Register 14CL | GAFLPL14  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8450h | RSCAN  | Receive Buffer Register 11AL     | RMIDL11   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8452h  | RSCAN  | Receive Rule Entry Register 14CH | GAFLPH14  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8452h  | RSCAN  | Receive Buffer Register 11AH     | RMIDH11   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8454h  | RSCAN  | Receive Rule Entry Register 15AL | GAFLIDL15 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8454h  | RSCAN  | Receive Buffer Register 11BL     | RMTS11    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8456h | RSCAN  | Receive Rule Entry Register 15AH | GAFLIDH15 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8456h  | RSCAN  | Receive Buffer Register 11BH     | RMPTR11   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8458h  | RSCAN  | Receive Rule Entry Register 15BL | GAFLML15  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8458h | RSCAN  | Receive Buffer Register 11CL     | RMDF011   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 845Ah | RSCAN  | Receive Rule Entry Register 15BH | GAFLMH15  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 845Ah  | RSCAN  | Receive Buffer Register 11CH     | RMDF111   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 845Ch | RSCAN  | Receive Rule Entry Register 15CL | GAFLPL15  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 845Ch | RSCAN  | Receive Buffer Register 11DL     | RMDF211   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 845Eh | RSCAN  | Receive Rule Entry Register 15CH | GAFLPH15  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 845Eh | RSCAN  | Receive Buffer Register 11DH     | RMDF311   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8460h | RSCAN  | Receive Buffer Register 12AL     | RMIDL12   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8462h | RSCAN  | Receive Buffer Register 12AH     | RMIDH12   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8464h  | RSCAN  | Receive Buffer Register 12BL     | RMTS12    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8466h | RSCAN  | Receive Buffer Register 12BH     | RMPTR12   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8468h | RSCAN  | Receive Buffer Register 12CL     | RMDF012   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 846Ah  | RSCAN  | Receive Buffer Register 12CH     | RMDF112   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 846Ch | RSCAN  | Receive Buffer Register 12DL     | RMDF212   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 846Eh  | RSCAN  | Receive Buffer Register 12DH     | RMDF312   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8470h  | RSCAN  | Receive Buffer Register 13AL     | RMIDL13   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 8472h | RSCAN  | Receive Buffer Register 13AH     | RMIDH13   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8474h  | RSCAN  | Receive Buffer Register 13BL     | RMTS13    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8476h  | RSCAN  | Receive Buffer Register 13BH     | RMPTR13   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8478h  | RSCAN  | Receive Buffer Register 13CL     | RMDF013   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 847Ah | RSCAN  | Receive Buffer Register 13CH     | RMDF113   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 847Ch | RSCAN  | Receive Buffer Register 13DL     | RMDF213   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 847Eh  | RSCAN  | Receive Buffer Register 13DH     | RMDF313   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8480h  | RSCAN  | Receive Buffer Register 14AL     | RMIDL14   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8482h  | RSCAN  | Receive Buffer Register 14AH     | RMIDH14   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8484h  | RSCAN  | Receive Buffer Register 14BL     | RMTS14    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8486h  | RSCAN  | Receive Buffer Register 14BH     | RMPTR14   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 8488h  | RSCAN  | Receive Buffer Register 14CL     | RMDF014   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 848Ah  | RSCAN  | Receive Buffer Register 14CH     | RMDF114   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 00A 848Ch | RSCAN  | Receive Buffer Register 14DL     | RMDF214   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

| 0A 848Eh  | RSCAN  | Receive Buffer Register 14DH     | RMDF314   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

|           |        |                                  |           |         | 10     | 2 31 01 0110                       | 2 1011                     |  |

| 0A 8490h  | RSCAN  | Receive Buffer Register 15AL     | RMIDL15   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |

## Table 4.1 List of I/O Registers (Address Order) (29/33)

|                                | Module |                                              | Register                | Number  | Access | Number of Access                   | Cycles                     |

|--------------------------------|--------|----------------------------------------------|-------------------------|---------|--------|------------------------------------|----------------------------|

| Address                        | Symbol | Register Name                                | Symbol                  | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |

| 00A 8494h                      | RSCAN  | Receive Buffer Register 15BL                 | RMTS15                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8496h                      | RSCAN  | Receive Buffer Register 15BH                 | RMPTR15                 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 8498h                     | RSCAN  | Receive Buffer Register 15CL                 | RMDF015                 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 849Ah                     | RSCAN  | Receive Buffer Register 15CH                 | RMDF115                 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 849Ch                     | RSCAN  | Receive Buffer Register 15DL                 | RMDF215                 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 849Eh                     | RSCAN  | Receive Buffer Register 15DH                 | RMDF315                 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 8580h<br>to<br>000A 859Fh | RSCAN  | RAM Test Register 0 to RAM Test Register 15  | RPGACC0 to<br>RPGACC15  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 85A0h                     | RSCAN  | Receive FIFO Access Register 0AL             | RFIDL0                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 85A0h                     | RSCAN  | RAM Test Register 16                         | RPGACC16                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A2h                      | RSCAN  | Receive FIFO Access Register 0AH             | RFIDH0                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A2h                      | RSCAN  | RAM Test Register 17                         | RPGACC17                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A4h                      | RSCAN  | Receive FIFO Access Register 0BL             | RFTS0                   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A4h                      | RSCAN  | RAM Test Register 18                         | RPGACC18                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A6h                      | RSCAN  | Receive FIFO Access Register 0BH             | RFPTR0                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A6h                      | RSCAN  | RAM Test Register 19                         | RPGACC19                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A8h                      | RSCAN  | Receive FIFO Access Register 0CL             | RFDF00                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85A8h                      | RSCAN  | RAM Test Register 20                         | RPGACC20                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85AAh                      | RSCAN  | Receive FIFO Access Register 0CH             | RFDF10                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 100A 85AAh                     | RSCAN  | RAM Test Register 21                         | RPGACC21                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85ACh                      | RSCAN  | Receive FIFO Access Register 0DL             | RFDF20                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85ACh                      | RSCAN  | RAM Test Register 22                         | RPGACC22                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85AEh                      | RSCAN  | Receive FIFO Access Register 0DH             | RFDF30                  | 16      | 16     | 2 or 3 PCLKB                       | 2 IOLK                     |

| 00A 85AEh                      | RSCAN  | RAM Test Register 23                         | RPGACC23                | 16      | 16     | 2 or 3 PCLKB                       | 2 IOLIK<br>2 ICLK          |

| 00A 85B0h                      | RSCAN  | Receive FIFO Access Register 1AL             | RFIDL1                  | 16      | 16     | 2 or 3 PCLKB                       | 2 IOLIK<br>2 ICLK          |

| 00A 85B0h                      | RSCAN  | RAM Test Register 24                         | RPGACC24                | 16      | 16     | 2 or 3 PCLKB                       | 2 IOLK                     |

| 00A 85B2h                      | RSCAN  | •                                            | RFIDH1                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK<br>2 ICLK           |

|                                |        | Receive FIFO Access Register 1AH             |                         | 16      | 16     |                                    | 2 ICLK<br>2 ICLK           |

| 00A 85B2h                      | RSCAN  | RAM Test Register 25                         | RPGACC25                |         |        | 2 or 3 PCLKB                       |                            |

| 00A 85B4h                      | RSCAN  | Receive FIFO Access Register 1BL             | RFTS1                   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85B4h                      | RSCAN  | RAM Test Register 26                         | RPGACC26                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85B6h                      | RSCAN  | Receive FIFO Access Register 1BH             | RFPTR1                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85B6h                      | RSCAN  | RAM Test Register 27                         | RPGACC27                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85B8h                      | RSCAN  | Receive FIFO Access Register 1CL             | RFDF01                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85B8h                      | RSCAN  | RAM Test Register 28                         | RPGACC28                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85BAh                      | RSCAN  | Receive FIFO Access Register 1CH             | RFDF11                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85BAh                      | RSCAN  | RAM Test Register 29                         | RPGACC29                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85BCh                      | RSCAN  | Receive FIFO Access Register 1DL             | RFDF21                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85BCh                      | RSCAN  | RAM Test Register 30                         | RPGACC30                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85BEh                      | RSCAN  | Receive FIFO Access Register 1DH             | RFDF31                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 85BEh                     | RSCAN  | RAM Test Register 31                         | RPGACC31                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 000A 85C0h                     | RSCAN  | RAM Test Register 32 to RAM Test Register 47 | RPGACC32 to<br>RPGACC47 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0<br>100A 85DEh                |        |                                              | ILE GAGG41              |         |        |                                    |                            |

| 00A 85E0h                      | RSCAN0 | Transmit/Receive FIFO Access Register 0AL    | CFIDL0                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E0h                      | RSCAN  | RAM Test Register 48                         | RPGACC48                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E2h                      | RSCAN0 | Transmit/Receive FIFO Access Register 0AH    | CFIDH0                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E2h                      | RSCAN  | RAM Test Register 49                         | RPGACC49                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E4h                      | RSCAN0 | Transmit/Receive FIFO Access Register 0BL    | CFTS0                   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E4h                      | RSCAN  | RAM Test Register 50                         | RPGACC50                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E6h                      | RSCAN0 | Transmit/Receive FIFO Access Register 0BH    | CFPTR0                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E6h                      | RSCAN  | RAM Test Register 51                         | RPGACC51                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 85E8h                      | RSCAN0 | Transmit/Receive FIFO Access Register 0CL    | CFDF00                  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

|                                | -      | RAM Test Register 52                         | RPGACC52                | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

# 5. Electrical Characteristics

## 5.1 Absolute Maximum Ratings

#### Table 5.1 Absolute Maximum Ratings

Conditions: VSS = AVSS0 = VREFL0 = VREFL= VSS\_USB = 0 V

|                                | Item                         | Symbol           | Value                     | Unit |  |

|--------------------------------|------------------------------|------------------|---------------------------|------|--|

| Power supply vo                | bltage                       | VCC, VCC_USB     | -0.3 to +6.5              | V    |  |

| VBATT power si                 | upply voltage                | Vbatt            | -0.3 to +6.5              | V    |  |

| Input voltage                  | Ports for 5 V tolerant*1     | V <sub>in</sub>  | -0.3 to +6.5              | V    |  |

|                                | P03, P05, P07, P40 to P47    |                  | -0.3 to AVCC0 +0.3        |      |  |

|                                | Ports other than above       |                  | -0.3 to VCC +0.3          |      |  |

| Reference power supply voltage |                              | VREFH0           | -0.3 to AVCC0 +0.3        | V    |  |

|                                |                              | VREFH            |                           |      |  |

| Analog power su                | upply voltage                | AVCC0            | -0.3 to +6.5              | V    |  |

| Analog input                   | When AN000 to AN007 are used | V <sub>AN</sub>  | -0.3 to AVCC0 +0.3        | V    |  |

| voltage                        | When AN016 to AN031 are used |                  | -0.3 to VCC +0.3          |      |  |

| Operating temperature*2        |                              | T <sub>opr</sub> | -40 to +85<br>-40 to +105 | °C   |  |

| Storage tempera                | ature                        | T <sub>stg</sub> | –55 to +125               | °C   |  |

Caution: Permanent damage to the MCU may be caused if absolute maximum ratings are exceeded.

To preclude any malfunctions due to noise interference, insert capacitors with high frequency characteristics between the VCC and VSS pins, between the AVCC0 and AVSS0 pins, between the VCC\_USB and VSS\_USB pins, between the VREFH0 and VREFL0 pins, and between the VREFH and VREFL pins. Place capacitors of about 0.1 µF as close as possible to every power supply pin and use the shortest and heaviest possible traces.

Connect the VCL pin to a VSS pin via a 4.7 µF capacitor. The capacitor must be placed close to the pin. For details, refer to section 5.15.1, Connecting VCL Capacitor and Bypass Capacitors.

Do not input signals or an I/O pull-up power supply to ports other than 5-V tolerant ports while the device is not powered. The current injection that results from input of such a signal or I/O pull-up may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Even if –0.3 to +6.5 V is input to 5-V tolerant ports, it will not cause problems such as damage to the MCU.

Note 1. Ports 12, 13, 16, 17, 30, 31, 32, and B5 are 5 V tolerant.

Note 2. The upper limit of operating temperature is 85°C or 105°C, depending on the product. For details, refer to section 1.2, List of Products.

## 5.2 DC Characteristics

## Table 5.3DC Characteristics (1)

Conditions:  $2.7 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 5.5 \text{ V}, 2.7 \text{ V} \le \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| ltem                             |                                                                                                                                                                                                                                                                 |                           | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger<br>input voltage | RIIC input pin<br>(except for SMB                                                                                                                                                                                                                               | us, 5 V tolerant)         | V <sub>IH</sub> | VCC × 0.7   | _    | 5.8         | V    |                    |

|                                  | Ports 12, 13, 16,<br>(5 V tolerant)                                                                                                                                                                                                                             | 17, port B5               |                 | VCC × 0.8   |      | 5.8         |      |                    |

|                                  | Ports 14 to 15, ports 20 to 27,<br>ports 33 to 37, ports 50 to 55,<br>ports A0 to A7,<br>ports B0 to B4, B6, B7<br>ports C0 to C7,<br>ports D0 to D7,<br>ports E0 to E7,<br>port J3,<br>Ports 30 to 32 (when time capture<br>event input is not selected), RES# |                           |                 | VCC × 0.8   |      | VCC + 0.3   |      |                    |

|                                  | Ports 03, 05, 07,                                                                                                                                                                                                                                               | ports 40 to 47            |                 | AVCC0 × 0.8 | _    | AVCC0 + 0.3 |      |                    |

|                                  | Ports 30 to 32<br>(when time<br>capture event<br>input is<br>selected)                                                                                                                                                                                          | When VCC is supplied      |                 | VCC × 0.8   |      | VCC + 0.3   |      |                    |

|                                  |                                                                                                                                                                                                                                                                 | When VBATT is supplied    |                 | VBATT × 0.8 | _    | VBATT + 0.3 |      |                    |

|                                  | Ports 03, 05, 07,                                                                                                                                                                                                                                               | ports 40 to 47            | V <sub>IL</sub> | -0.3        | _    | AVCC0 × 0.2 |      |                    |

|                                  | RIIC input pin (e                                                                                                                                                                                                                                               | cept for SMBus)           |                 | -0.3        | _    | VCC × 0.3   |      |                    |

|                                  | Other than RIIC input pin or ports 30 to 32                                                                                                                                                                                                                     |                           |                 | -0.3        |      | VCC × 0.2   |      |                    |

|                                  | Ports 30 to 32<br>(when time                                                                                                                                                                                                                                    | When VCC is supplied      |                 | -0.3        | —    | VCC × 0.3   |      |                    |

|                                  | capture event<br>input is<br>selected)                                                                                                                                                                                                                          | When VBATT is<br>supplied |                 | -0.3        | _    | VBATT × 0.3 |      |                    |

|                                  | Ports 03, 05, 07,                                                                                                                                                                                                                                               | ports 40 to 47            | $\Delta V_T$    | AVCC0 × 0.1 | _    | -           |      |                    |

|                                  | RIIC input pin (e:                                                                                                                                                                                                                                              | cept for SMBus)           |                 | VCC × 0.05  | _    | -           |      |                    |

|                                  | Ports 12, 13, 16,                                                                                                                                                                                                                                               | 17, Port B5               |                 | VCC × 0.05  | _    | -           |      |                    |

|                                  | Other than RIIC                                                                                                                                                                                                                                                 | nput pin                  |                 | VCC × 0.1   | —    | —           |      |                    |

| Input level                      | MD                                                                                                                                                                                                                                                              |                           | V <sub>IH</sub> | VCC × 0.9   |      | VCC + 0.3   | V    |                    |

| voltage (except for Schmitt      | EXTAL (external                                                                                                                                                                                                                                                 | clock input)              |                 | VCC × 0.8   |      | VCC + 0.3   |      |                    |

| trigger input                    | RIIC input pin (S                                                                                                                                                                                                                                               | RIIC input pin (SMBus)    |                 | 2.1         | _    | VCC + 0.3   |      |                    |

| pins)                            | MD                                                                                                                                                                                                                                                              |                           | V <sub>IL</sub> | -0.3        |      | VCC × 0.1   |      |                    |

|                                  | EXTAL (external                                                                                                                                                                                                                                                 | clock input)              |                 | -0.3        |      | VCC × 0.2   |      |                    |

|                                  | RIIC input pin (S                                                                                                                                                                                                                                               | MBus)                     |                 | -0.3        | _    | 0.8         |      |                    |

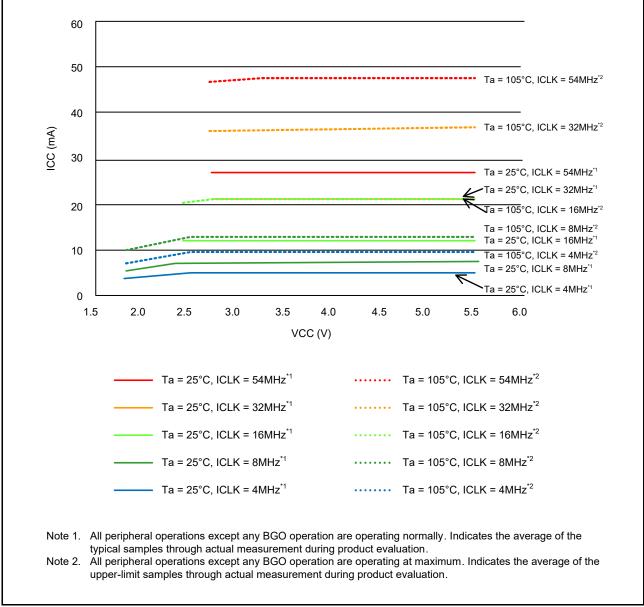

Figure 5.1 Voltage Dependency in High-Speed Operating Mode (Reference Data)

Table 5.17Permissible Output Currents (2)Conditions: $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}$ ,  $\text{T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                 | Item                           |                                                                   | Symbol           | Max. | Unit |

|---------------------------------|--------------------------------|-------------------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Ports 40 to 47, ports 03, 05,  | Ports 40 to 47, ports 03, 05, 07, port 36, 37                     |                  |      | mA   |

| (average value per pin)         | Ports other than above         | Normal output mode                                                |                  | 4.0  |      |

|                                 |                                | High-drive output mode                                            |                  | 8.0  |      |

| Permissible output low current  | Ports 40 to 47, ports 03, 05,  | 07, ports 36, 37                                                  |                  | 4.0  |      |

| (maximum value per pin)         | Ports other than above         | Normal output mode                                                |                  | 4.0  |      |

|                                 |                                | High-drive output mode                                            |                  | 8.0  |      |

| Permissible output low current  | Total of ports 40 to 47, ports | 03, 05, 07                                                        | Σl <sub>OL</sub> | 30   |      |

|                                 | Total of ports 12 to 17, ports | 20 to 27, ports 30 to 37, port PJ3                                |                  | 30   |      |

|                                 | Total of ports 50 to 55, ports |                                                                   | 30               |      |      |

|                                 | Total of ports E0 to E7, ports |                                                                   | 30               |      |      |

|                                 | Total of all output pins       |                                                                   | 60               |      |      |

| Permissible output high current | Ports 40 to 47, ports 03, 05,  | I <sub>ОН</sub>                                                   | -4.0             |      |      |

| (average value per pin)         | Ports other than above         | Normal output mode                                                |                  | -4.0 |      |

|                                 |                                | High-drive output mode                                            |                  | -8.0 |      |

| Permissible output high current | Ports 40 to 47, ports 03, 05,  | Ports 40 to 47, ports 03, 05, 07, ports 36, 37                    |                  |      |      |

| (maximum value per pin)         | Ports other than above         | Normal output mode                                                |                  | -4.0 |      |

|                                 |                                | High-drive output mode                                            |                  | -8.0 |      |

| Permissible output high current | Total of ports 40 to 47, ports | 03, 05, 07                                                        | Σl <sub>OH</sub> | -30  |      |

|                                 | Total of ports 12 to 17, ports | Total of ports 12 to 17, ports 20 to 27, ports 30 to 37, port PJ3 |                  |      |      |

|                                 | Total of ports 50 to 55, ports | Total of ports 50 to 55, ports C0 to C7, ports B0 to B7           |                  |      |      |

|                                 | Total of ports E0 to E7, ports | s A0 to A7, ports D0 to D4                                        | 1                | -30  |      |

|                                 | Total of all output pins       | 1                                                                 | -60              |      |      |

Note: Do not exceed the permissible total supply current.

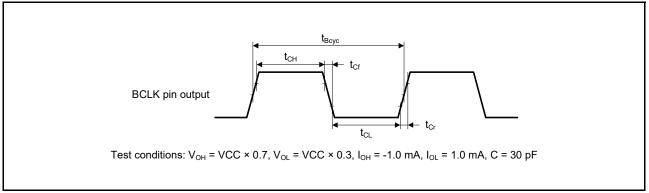

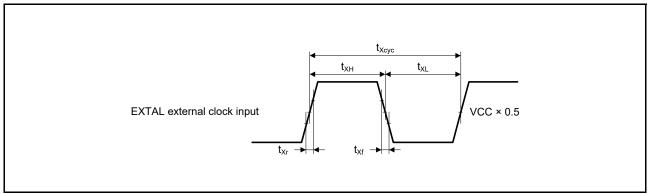

#### Table 5.26 Clock Timing

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS}_{\text{USB}} = 0 \text{ V}$ ,  $\text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                              | Symbol              | Min.                 | Тур.               | Max.  | Unit  | Test Conditions |                                              |

|---------------------------------------------------|---------------------|----------------------|--------------------|-------|-------|-----------------|----------------------------------------------|

| EXTAL external clock input cycle                  | t <sub>Xcyc</sub>   | 50                   | —                  | _     | ns    | Figure 5.23     |                                              |

| EXTAL external clock input high p                 | t <sub>XH</sub>     | 20                   | —                  |       | ns    | -               |                                              |

| EXTAL external clock input low p                  | ulse width          | t <sub>XL</sub>      | 20                 | —     |       | ns              | -                                            |

| EXTAL external clock rise time                    |                     | t <sub>Xr</sub>      | _                  | —     | 5     | ns              | -                                            |

| EXTAL external clock fall time                    |                     | t <sub>Xf</sub>      | _                  | —     | 5     | ns              | -                                            |

| EXTAL external clock input wait to                | ime*1               | t <sub>XWT</sub>     | 0.5                | —     |       | μs              |                                              |

| Main clock oscillator oscillation                 | 2.4 ≤ VCC ≤ 5.5     | f <sub>MAIN</sub>    | 1                  | —     | 20    | MHz             | -                                            |

| frequency*2                                       | 1.8 ≤ VCC < 2.4     |                      | 1                  | _     | 8     |                 |                                              |

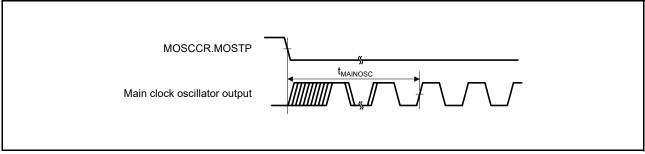

| Main clock oscillation stabilization              | n time (crystal)*2  | t <sub>MAINOSC</sub> |                    | 3     |       | ms              | Figure 5.24                                  |

| Main clock oscillation stabilization resonator)*2 | n time (ceramic     | t <sub>MAINOSC</sub> | _                  | 50    | _     | μs              |                                              |

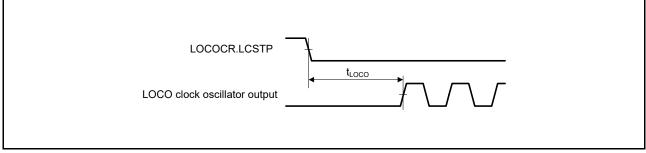

| LOCO clock oscillation frequency                  | ,                   | f <sub>LOCO</sub>    | 3.44               | 4.0   | 4.56  | MHz             |                                              |

| LOCO clock oscillation stabilization              | on time             | t <sub>LOCO</sub>    |                    | _     | 0.5   | μs              | Figure 5.25                                  |

| IWDT-dedicated clock oscillation                  | f <sub>ILOCO</sub>  | 12.75                | 15                 | 17.25 | kHz   |                 |                                              |

| IWDT-dedicated clock oscillation                  | stabilization time  | t <sub>ILOCO</sub>   | _                  | —     | 50    | μs              | Figure 5.26                                  |

| HOCO clock oscillation frequency                  | /                   | f <sub>HOCO</sub>    | 31.52              | 32    | 32.48 | MHz             | $T_a = -40 \text{ to } + 85^{\circ}\text{C}$ |

|                                                   |                     | (32 MHz)             | 31.68              | 32    | 32.32 | 1               | $T_a = 0$ to + 55°C                          |

|                                                   |                     |                      | 31.36              | 32    | 32.64 |                 | $T_a = -40 \text{ to } +105^{\circ}\text{C}$ |

|                                                   |                     | f <sub>HOCO</sub>    | 53.19              | 54    | 54.81 | MHz             | $T_a = -40 \text{ to } + 85^{\circ}\text{C}$ |

|                                                   |                     | (54 MHz)             | 53.46              | 54    | 54.54 |                 | $T_a = 0$ to + 55°C                          |

|                                                   |                     |                      | 52.92              | 54    | 55.08 |                 | $T_a = -40 \text{ to } +105^{\circ}\text{C}$ |

| HOCO clock oscillation stabilizati                | on time             | t <sub>HOCO</sub>    | _                  | —     | 30    | μs              | Figure 5.28                                  |

| PLL input frequency*3                             |                     | f <sub>PLLIN</sub>   | 4                  | —     | 12.5  | MHz             |                                              |

| PLL circuit oscillation frequency*3               | 3                   | f <sub>PLL</sub>     | 24                 | —     | 54    | MHz             |                                              |

| PLL clock oscillation stabilization               | time                | t <sub>PLL</sub>     | _                  | —     | 50    | μs              | Figure 5.29                                  |

| PLL free-running oscillation frequ                | ency                | f <sub>PLLFR</sub>   | _                  | 8     | _     | MHz             |                                              |

| USBPLL input frequency*5                          | f <sub>PLLIN</sub>  |                      | 6, 8* <sup>6</sup> | _     | MHz   |                 |                                              |

| USBPLL circuit oscillation freque                 | f <sub>PLL</sub>    |                      | 48* <sup>6</sup>   | _     | MHz   |                 |                                              |

| USBPLL clock oscillation stabilization            | t <sub>PLL</sub>    |                      | —                  | 50    | μs    | Figure 5.29     |                                              |

| Sub-clock oscillator oscillation fre              | f <sub>SUB</sub>    |                      | 32.768             |       | kHz   |                 |                                              |

| Sub-clock oscillation stabilization               | t <sub>SUBOSC</sub> |                      | 0.5                |       | s     | Figure 5.30     |                                              |

Note 1. Time until the clock can be used after the main clock oscillator stop bit (MOSCCR.MOSTP) is set to 0 (operating).

Note 2. Reference values when an 8-MHz resonator is used.

When specifying the main clock oscillator stabilization time, set the MOSCWTCR register with a stabilization time value that is equal to or greater than the resonator-manufacturer-recommended value.

After the MOSCCR.MOSTP bit is changed to enable the main clock oscillator, confirm that the OSCOVFSR.MOOVF flag has become 1, and then start using the main clock.

Note 3. The VCC range should be 2.4 to 5.5 V when the PLL is used.

Note 4. Reference values when a 32.768-kHz resonator is used. After the setting of the SOSCCR.SOSTP bit or RCR3.RTCEN bit is changed to operate the sub-clock oscillator, only start using the sub-clock after the sub-clock oscillation stabilization wait time that is equal to or greater than the oscillator-manufacturerrecommended value has elapsed.

Note 5. The VCC range should be 3.0 to 5.5 V when the USBPLL is used.

Note 6. The input frequency can be set to 6 or 8 MHz and the oscillation frequency can be set to 48 MHz only.

Note 7. Only 32.768 kHz can be used.

Figure 5.23 EXTAL External Clock Input Timing

Figure 5.24 Main Clock Oscillation Start Timing

Figure 5.25 LOCO Clock Oscillation Start Timing

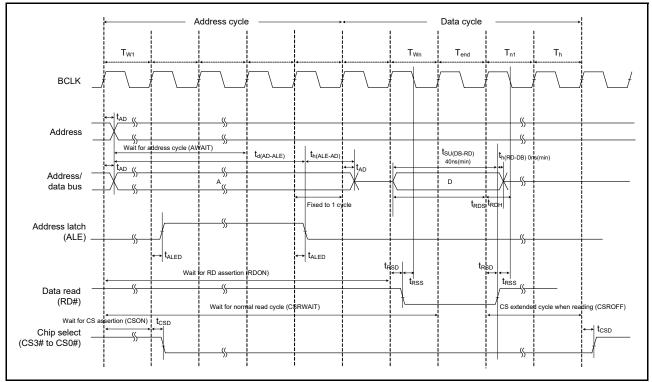

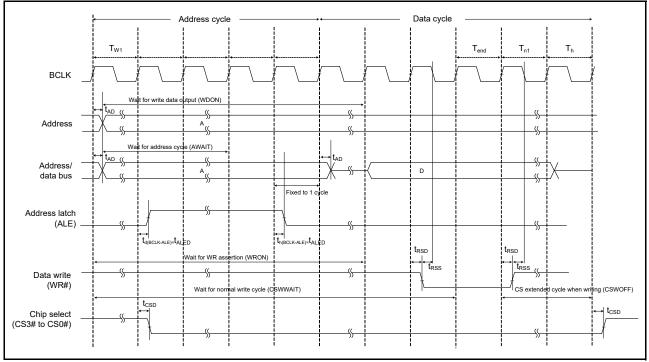

External Bus Timing/Write Access Operation Example (Multiplex)

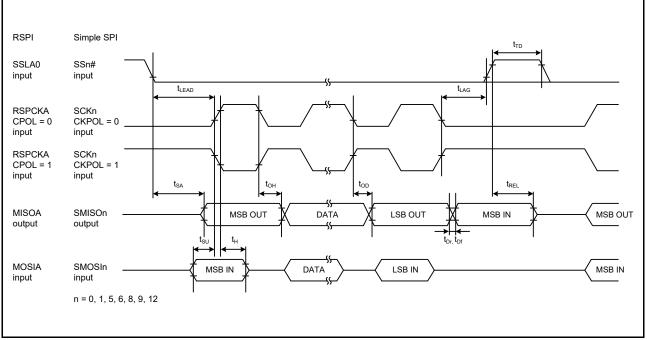

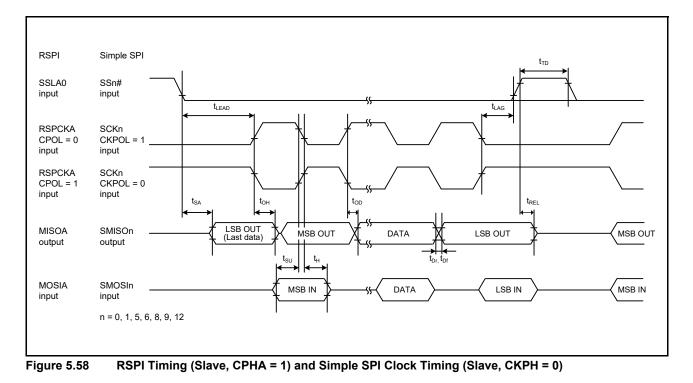

#### Table 5.39 **Timing of On-Chip Peripheral Modules (2)**

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}$ ,  $\text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$ , C = 30 pF, when high-drive output is selected by the drive capacity control register

|   |                                 | Ite    | m                                                           | Symbol                            | Min.                                                                     | Max.                                              | Unit                 | Test<br>Conditions |

|---|---------------------------------|--------|-------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|---------------------------------------------------|----------------------|--------------------|

|   | RSPCK clock                     | Master |                                                             | t <sub>SPcyc</sub>                | 2                                                                        | 4096                                              | t <sub>Pcyc</sub> *1 | Figure 5.54        |

| 1 | cycle                           | Slave  |                                                             |                                   | 8                                                                        | 4096                                              |                      |                    |

|   | RSPCK clock<br>high pulse width | Master |                                                             | t <sub>SPCKWH</sub>               | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | _                                                 | ns                   |                    |

|   |                                 | Slave  |                                                             |                                   | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | _                                                 |                      |                    |

|   | RSPCK clock<br>low pulse width  | Master |                                                             | t <sub>SPCKWL</sub>               | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | _                                                 | ns                   |                    |

|   |                                 | Slave  |                                                             |                                   | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     |                                                   |                      |                    |

|   | RSPCK clock                     | Output | 2.7 V or above                                              | t <sub>SPCKr</sub> ,              | _                                                                        | 10                                                | ns                   |                    |

|   | rise/fall time                  |        | 1.8 V or above                                              | t <sub>SPCKf</sub>                | _                                                                        | 15                                                |                      |                    |

|   |                                 | Input  |                                                             |                                   | _                                                                        | 1                                                 | μs                   |                    |

|   |                                 | Master | 2.7 V or above                                              | t <sub>SU</sub>                   | 10                                                                       | _                                                 | ns                   | Figure 5.55        |

|   | time                            |        | 1.8 V or above                                              |                                   | 30                                                                       | _                                                 |                      | to<br>Figure 5.58  |

|   |                                 | Slave  |                                                             |                                   | 25 – t <sub>Pcyc</sub>                                                   |                                                   |                      | r igure 0.00       |

|   | Data input hold<br>time         | Master | RSPCK set to a division ratio other than PCLKB divided by 2 | t <sub>H</sub>                    | t <sub>Pcyc</sub>                                                        | _                                                 | ns                   |                    |

|   |                                 |        | RSPCK set to PCLKB divided by 2                             | t <sub>HF</sub>                   | 0                                                                        | _                                                 |                      |                    |

|   |                                 | Slave  | •                                                           | t <sub>H</sub>                    | 20 + 2 × t <sub>Pcyc</sub>                                               | _                                                 |                      |                    |

|   | SSL setup time                  | Master |                                                             | t <sub>LEAD</sub>                 | $-30 + N^{*2} \times t_{SPcyc}$                                          | _                                                 | ns                   |                    |

|   |                                 | Slave  |                                                             |                                   | 2                                                                        | _                                                 | t <sub>Pcyc</sub>    |                    |

|   | SSL hold time                   | Master |                                                             | t <sub>LAG</sub>                  | $-30 + N^{*3} \times t_{SPcyc}$                                          | _                                                 | ns                   |                    |

|   |                                 | Slave  |                                                             |                                   | 2                                                                        | _                                                 | t <sub>Pcyc</sub>    |                    |

|   | Data output                     | Master | 2.7 V or above                                              | t <sub>OD</sub>                   | _                                                                        | 14                                                | ns                   |                    |

| ľ | delay time                      |        | 1.8 V or above                                              |                                   | _                                                                        | 30                                                |                      |                    |

|   |                                 | Slave  | 2.7 V or above                                              |                                   | _                                                                        | 3 × t <sub>Pcyc</sub> + 65                        |                      |                    |

|   |                                 |        | 1.8 V or above                                              |                                   | _                                                                        | 3 × t <sub>Pcyc</sub> +105                        |                      |                    |

|   | Data output hold                | Master |                                                             | t <sub>OH</sub>                   | 0                                                                        | _                                                 | ns                   |                    |

|   | time                            | Slave  |                                                             |                                   | 0                                                                        | _                                                 |                      |                    |

| • | transmission                    | Master |                                                             | t <sub>TD</sub>                   | t <sub>SPcyc</sub> + 2 × t <sub>Pcyc</sub>                               | 8 × t <sub>SPcyc</sub> + 2 ×<br>t <sub>Pcyc</sub> | ns                   |                    |

| ' | delay time                      | Slave  |                                                             |                                   | 4 × t <sub>Pcyc</sub>                                                    | _                                                 |                      |                    |

|   | MOSI and MISO                   | Output | 2.7 V or above                                              | t <sub>Dr</sub> , t <sub>Df</sub> | _                                                                        | 10                                                | ns                   |                    |

|   | rise/fall time                  |        | 1.8 V or above                                              |                                   | _                                                                        | 15                                                |                      |                    |

|   |                                 | Input  |                                                             |                                   | _                                                                        | 1                                                 | μs                   |                    |

| L | SSL rise/fall<br>time           | Output | 2.7 V or above                                              | t <sub>SSLr</sub> ,               | _                                                                        | 10                                                | ns                   |                    |

|   |                                 |        | 1.8 V or above                                              | t <sub>SSLf</sub>                 | _                                                                        | 15                                                | ns                   |                    |

|   |                                 | Input  |                                                             |                                   | _                                                                        | 1                                                 | μs                   |                    |

|   | Slave access tim                | е      | 2.7 V or above                                              | t <sub>SA</sub>                   | _                                                                        | 6                                                 | t <sub>Pcyc</sub>    | Figure 5.57        |

| I |                                 |        | 1.8 V or above                                              |                                   |                                                                          | 7                                                 |                      | Figure 5.58        |

|   | Slave output rele               | ase    | 2.7 V or above                                              | t <sub>REL</sub>                  |                                                                          | 5                                                 | t <sub>Pcyc</sub>    | _                  |

| ľ | time                            |        | 1.8 V or above                                              |                                   | —                                                                        | 6                                                 | 1                    |                    |

Note 1. t<sub>Pcyc</sub>: PCLK cycle Note 2. N: An integer from 1 to 8 that can be set by the RSPI clock delay register (SPCKD) Note 3. N: An integer from 1 to 8 that can be set by the RSPI slave select negation delay register (SSLND)

RENESAS

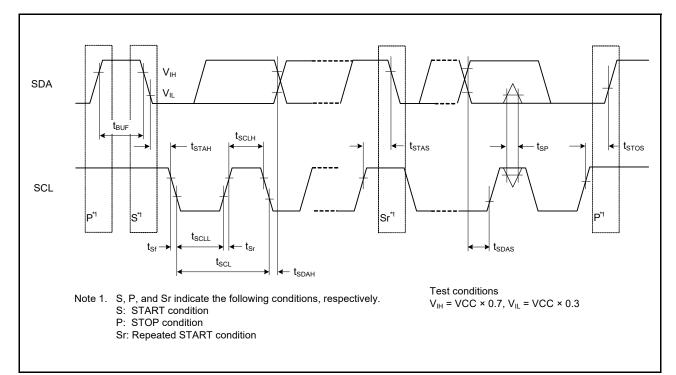

Figure 5.59 RIIC Bus Interface Input/Output Timing and Simple I<sup>2</sup>C Bus Interface Input/Output Timing

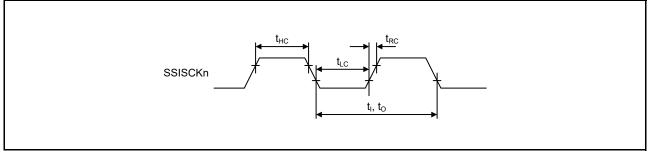

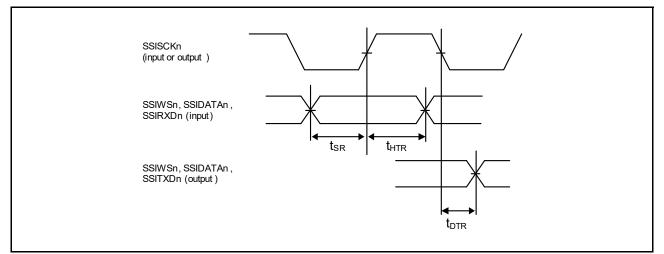

Figure 5.60 SSI Clock Input/Output Timing

Figure 5.61 SSI Transmission/Reception Timing (SSICR.SCKP=0)

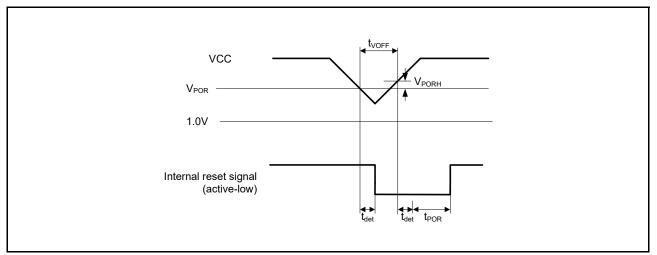

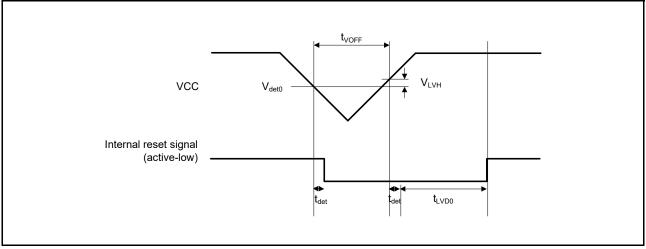

Figure 5.73 Voltage Detection Reset Timing

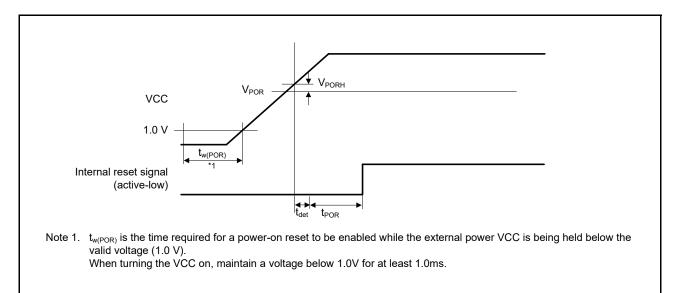

Figure 5.74 Power-On Reset Timing

Figure 5.75 Voltage Detection Circuit Timing (Vdet0)

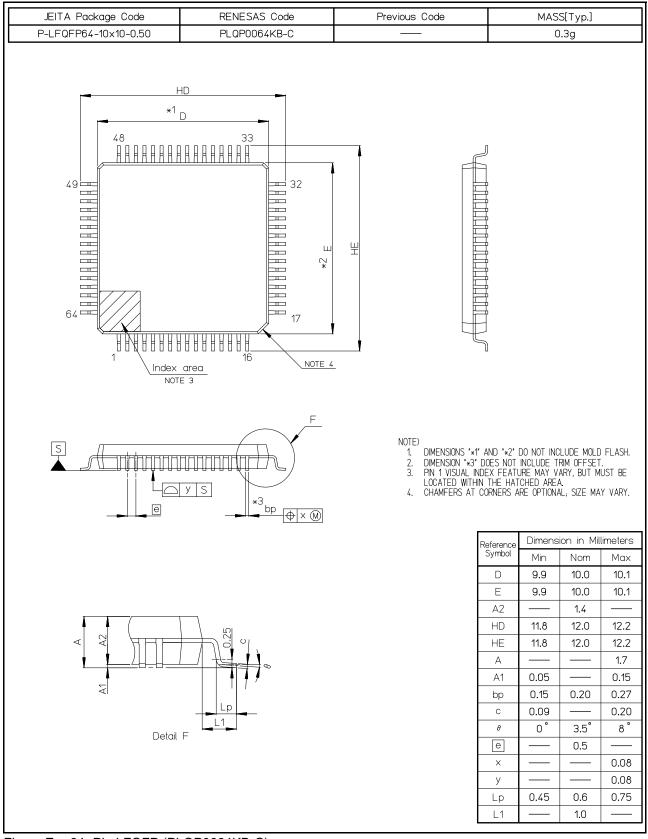

Figure E 64 -Pin LFQFP (PLQP0064KB-C)

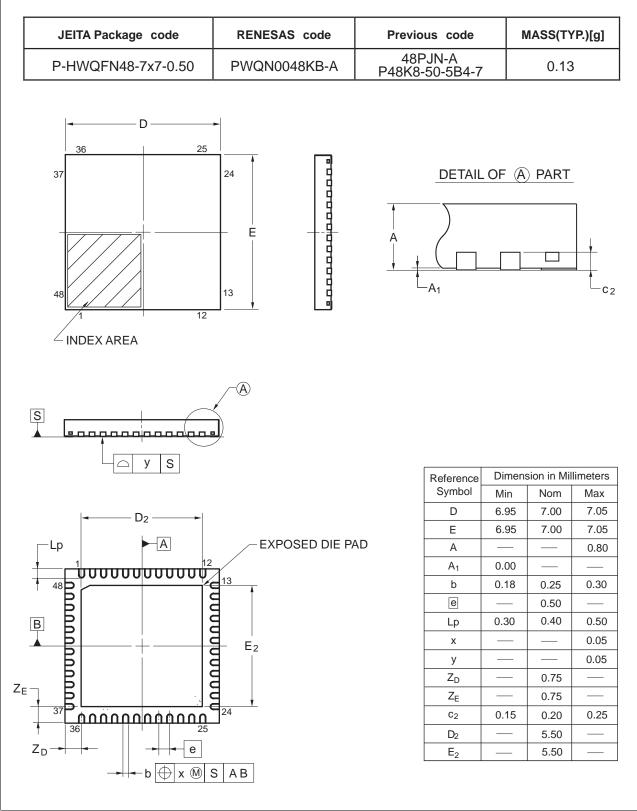

Figure F 48 -Pin HWQFN (PWQN0048KB-A)

# **REVISION HISTORY**

## RX230 Group, RX231 Group Datasheet

Classifications

- Items with Technical Update document number: Changes according to the corresponding issued Technical Update

- Items without Technical Update document number: Minor changes that do not require Technical Update to be issued

| Rev. | Date         |                 | Description                                                                                                                                            | Classification |