#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RXv2                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 54MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SD/SDIO, SPI, SSI, USB OTG                 |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 79                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TFLGA                                                                        |

| Supplier Device Package    | 100-TFLGA (5.5x5.5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52316cdla-20 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.4 Pin Functions

Table 1.5 lists the pin functions.

## Table 1.5Pin Functions (1/4)

| Classifications        | Pin Name         | I/O    | Description                                                                                                                                                                    |  |  |  |  |

|------------------------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power supply           | VCC              | Input  | Power supply pin. Connect it to the system power supply.                                                                                                                       |  |  |  |  |

|                        | VCL              | _      | Connect this pin to the VSS pin via a 4.7 $\mu F$ smoothing capacitor used to stabilize the internal power supply. Place the capacitor close to the pin.                       |  |  |  |  |

|                        | VSS              | Input  | Ground pin. Connect it to the system power supply (0 V).                                                                                                                       |  |  |  |  |

|                        | VBATT            | Input  | Backup power pin                                                                                                                                                               |  |  |  |  |

| Clock                  | XTAL             | Output | Pins for connecting a crystal. An external clock can be input through the                                                                                                      |  |  |  |  |

|                        | EXTAL            | Input  | EXTAL pin.                                                                                                                                                                     |  |  |  |  |

|                        | BCLK             | Output | Outputs the external bus clock for external devices.                                                                                                                           |  |  |  |  |

|                        | XCIN             | Input  | Input/output pins for the sub-clock oscillator. Connect a crystal between                                                                                                      |  |  |  |  |

|                        | XCOUT            | Output | XCIN and XCOUT.                                                                                                                                                                |  |  |  |  |

|                        | CLKOUT           | Output | Clock output pin.                                                                                                                                                              |  |  |  |  |

| Operating mode control | MD               | Input  | Pin for setting the operating mode. The signal levels on this pin must not be changed during operation.                                                                        |  |  |  |  |

|                        | UB               | Input  | Pin used for boot mode (USB interface).                                                                                                                                        |  |  |  |  |

|                        | UPSEL            | Input  | Pin used for boot mode (USB interface).                                                                                                                                        |  |  |  |  |

| System control         | RES#             | Input  | Reset pin. This MCU enters the reset state when this signal goes low.                                                                                                          |  |  |  |  |

| CAC                    | CACREF           | Input  | Input pin for the clock frequency accuracy measurement circuit.                                                                                                                |  |  |  |  |

| On-chip<br>emulator    | FINED            | I/O    | FINE interface pin.                                                                                                                                                            |  |  |  |  |

| Address bus            | A0 to A23        | Output | Output pins for the address.                                                                                                                                                   |  |  |  |  |

| Data bus               | D0 to D15        | I/O    | Input and output pins for the bidirectional data bus.                                                                                                                          |  |  |  |  |

| Multiplexed bus        | A0/D0 to A15/D15 | I/O    | Address/data multiplexed bus                                                                                                                                                   |  |  |  |  |

| Bus control            | RD#              | Output | Strobe signal which indicates that reading from the external bus interface space is in progress.                                                                               |  |  |  |  |

|                        | WR#              | Output | Strobe signal which indicates that writing to the external bus interface space is in progress, in single-write strobe mode.                                                    |  |  |  |  |

|                        | WR0#, WR1#       | Output | Strobe signals which indicate that either group of data bus pins (D7 to D0, and D15 to D8) is valid in writing to the external bus interface space, in byte strobe mode.       |  |  |  |  |

|                        | BC0#, BC1#       | Output | Strobe signals which indicate that either group of data bus pins (D7 to D0 and D15 to D8) is valid in access to the external bus interface space, in single-write strobe mode. |  |  |  |  |

|                        | CS0# to CS3#     | Output | Select signals for areas 0 to 3.                                                                                                                                               |  |  |  |  |

|                        | WAIT#            | Input  | Input pin for wait request signals in access to the external space.                                                                                                            |  |  |  |  |

|                        | ALE              | Output | Address latch signal when address/data multiplexed bus is selected.                                                                                                            |  |  |  |  |

| LVD                    | CMPA2            | Input  | Detection target voltage pin for voltage detection 2.                                                                                                                          |  |  |  |  |

| Interrupts             | NMI              | Input  | Non-maskable interrupt request pin.                                                                                                                                            |  |  |  |  |

| Interrupts             |                  | •      |                                                                                                                                                                                |  |  |  |  |

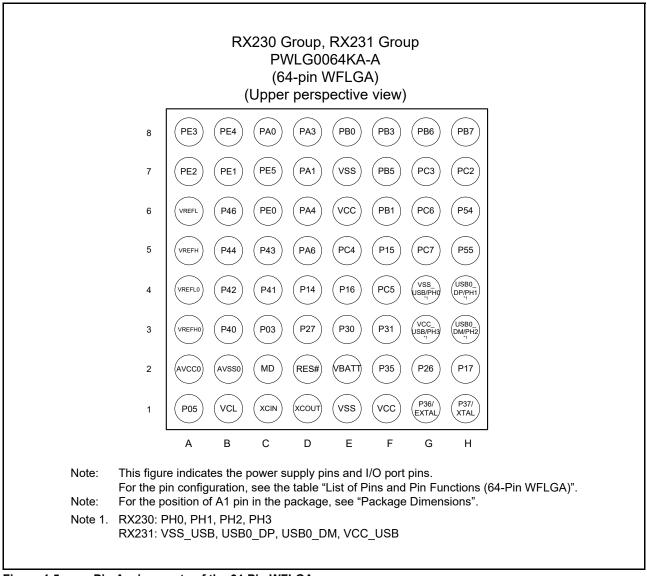

Figure 1.5 Pin Assignments of the 64-Pin WFLGA

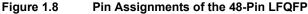

Figure 1.9 Pin Assignments of the 48-Pin HWQFN

RENESAS

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TPU, TMR, RTC, CMT,<br>POE, CAC) | Communications<br>(SCI, RSPI, RIIC, RSCAN, USB,<br>SSI)                    | Memory<br>Interface<br>(SDHI) | Touch<br>sensing | Others                 |

|------------|-------------------------------------------|----------|--------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|------------------|------------------------|

| 1          | VCL                                       |          |                                                  |                                                                            |                               |                  |                        |

| 2          | MD                                        |          |                                                  |                                                                            |                               |                  | FINED                  |

| 3          | RES#                                      |          |                                                  |                                                                            |                               |                  |                        |

| 1          | XTAL                                      | P37      |                                                  |                                                                            |                               |                  |                        |

| 5          | VSS                                       |          |                                                  |                                                                            |                               |                  |                        |

| 6          | EXTAL                                     | P36      |                                                  |                                                                            |                               |                  |                        |

| 7          | VCC                                       |          |                                                  |                                                                            |                               |                  |                        |

| 3          | UPSEL                                     | P35      |                                                  |                                                                            |                               |                  | NMI                    |

| 9          |                                           | P31      | MTIOC4D/TMCI2                                    | CTS1#/RTS1#/SS1#/SSISCK0                                                   |                               |                  | IRQ1                   |

| 10         |                                           | P30      | MTIOC4B/TMRI3/POE8#                              | RXD1/SMISO1/SSCL1/<br>AUDIO_MCLK                                           |                               |                  | IRQ0/CMPOB3            |

| 11         |                                           | P27      | MTIOC2B/TMCI3                                    | SCK1/SSIWS0                                                                |                               | TS2              | CVREFB3                |

| 12         |                                           | P26      | MTIOC2A/TMO1                                     | TXD1/SMOSI1/SSDA1/<br>USB0_VBUSEN/SSIRXD0                                  |                               | TS3              | CMPB3                  |

| 13         |                                           | P17      | MTIOC3A/MTIOC3B/TMO1/<br>POE8#/TIOCB0/TCLKD      | SCK1/MISOA/SDA/ SSITXD0                                                    |                               |                  | IRQ7/ CMPOB2           |

| 14         |                                           | P16      | MTIOC3C/MTIOC3D/TMO2/<br>TIOCB1/TCLKC            | TXD1/SMOSI1/SSDA1/MOSIA/<br>SCL/USB0_VBUS/<br>USB0_VBUSEN/<br>USB0_OVRCURB |                               |                  | IRQ6/ADTRG0#           |

| 15         |                                           | P15      | MTIOC0B/MTCLKB/TMCI2/<br>TIOCB2/TCLKB            | RXD1/SMISO1/SSCL1/CRXD0                                                    |                               | TS12             | IRQ5/CMPB2             |

| 16         |                                           | P14      | MTIOC3A/MTCLKA/TMRI2/<br>TIOCB5/TCLKA            | CTS1#/RTS1#/SS1#/CTXD0/<br>USB0_OVRCURA                                    |                               | TS13             | IRQ4/CVREFB2           |

| 17         | VCC_USB*1                                 | PH3*1    | TMCI0*1                                          |                                                                            |                               |                  |                        |

| 18         |                                           | PH2*1    | TMRI0*1                                          | USB0_DM*1                                                                  |                               |                  | IRQ1*1                 |

| 19         |                                           | PH1*1    | TMO0*1                                           | USB0_DP*1                                                                  |                               |                  | IRQ0*1                 |

| 20         | VSS_USB*1                                 | PH0*1    |                                                  |                                                                            |                               |                  | CACREF*1               |

| 21         | UB                                        | PC7      | MTIOC3A/MTCLKB/TMO2                              | TXD8/SMOSI8/SSDA8/MISOA                                                    |                               |                  | CACREF                 |

| 22         |                                           | PC6      | MTIOC3C/MTCLKA/TMCI2                             | RXD8/SMISO8/SSCL8/MOSIA/<br>USB0_EXICEN                                    |                               | TS22             |                        |

| 23         |                                           | PC5      | MTIOC3B/MTCLKD/TMRI2                             | SCK8/RSPCKA/USB0_ID                                                        |                               | TS23             |                        |

| 24         |                                           | PC4      | MTIOC3D/MTCLKC/TMCI1/<br>POE0#                   | SCK5/CTS8#/RTS8#/SS8#/<br>SSLA0                                            |                               | TSCAP            |                        |

| 25         |                                           | PB5/PC3  | MTIOC2A/MTIOC1B/TMRI1/<br>POE1#/TIOCB4           | USB0_VBUS                                                                  |                               |                  |                        |

| 26         |                                           | PB3/PC2  | MTIOC0A/MTIOC4A/TMO0/<br>POE3#/TIOCD3/TCLKD      | SCK6                                                                       |                               |                  |                        |

| 27         |                                           | PB1/PC1  | MTIOC0C/MTIOC4C/TMCI0/<br>TIOCB3                 | TXD6/SMOSI6/SSDA6                                                          |                               |                  | IRQ4/ CMPOB1           |

| 28         | VCC                                       |          |                                                  |                                                                            | 1                             |                  | 1                      |

| 29         |                                           | PB0/PC0  | MTIC5W/TIOCA3                                    | RXD6/SMISO6/SSCL6/RSPCKA                                                   |                               |                  |                        |

| 30         | VSS                                       |          |                                                  |                                                                            | 1                             | 1                | 1                      |

| 31         |                                           | PA6      | MTIC5V/MTCLKB/TMCI3/POE2#/<br>TIOCA2             | CTS5#/RTS5#/SS5#/MOSIA/<br>SSIWS0                                          |                               |                  |                        |

| 32         |                                           | PA4      | MTIC5U/MTCLKA/TMRI0/TIOCA1                       | TXD5/SMOSI5/SSDA5/SSLA0/<br>SSITXD0/IRTXD5                                 |                               |                  | IRQ5 /CVREFB           |

| 33         |                                           | PA3      | MTIOC0D/MTCLKD/TIOCD0/<br>TCLKB                  | RXD5/SMISO5/SSCL5/SSIRXD0/<br>IRRXD5                                       |                               |                  | IRQ6 /CMPB1            |

| 34         |                                           | PA1      | MTIOC0B/MTCLKC/TIOCB0                            | SCK5/SSLA2/SSISCK0                                                         |                               | 1                | 1                      |

| 35         |                                           | PE4      | MTIOC4D/MTIOC1A                                  |                                                                            |                               |                  | AN020/CMPA2/<br>CLKOUT |

| 36         |                                           | PE3      | MTIOC4B/POE8#                                    | CTS12#/RTS12#/AUDIO_MCLK                                                   |                               | 1                | AN019/CLKOUT           |

| 37         |                                           | PE2      | MTIOC4A                                          | RXD12/RXDX12/SSCL12                                                        |                               |                  | IRQ7/AN018/<br>CVREFB0 |

| 38         |                                           | PE1      | MTIOC4C                                          | TXD12/TXDX12/SIOX12/SSDA12                                                 | 1                             | 1                | AN017/CMPB0            |

| 39         | VREFL                                     | ł        |                                                  |                                                                            | 1                             | 1                | 1                      |

| 40         |                                           | P46      |                                                  |                                                                            | 1                             | 1                | AN006                  |

| 41         | VREFH                                     | T        |                                                  |                                                                            | 1                             |                  | 1                      |

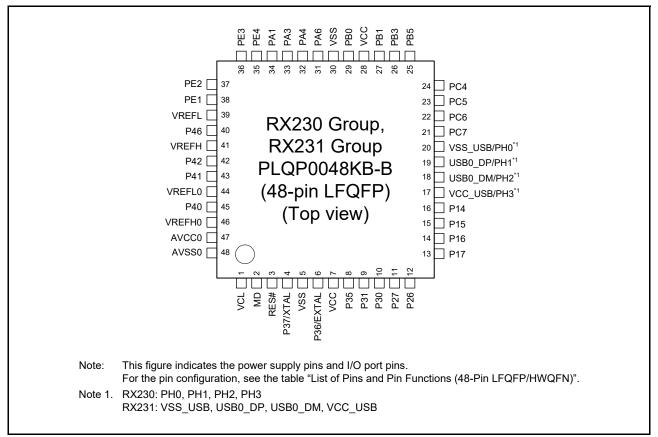

### Table 1.10 List of Pins and Pin Functions (48-Pin LFQFP/HWQFN) (1/2)

# 3. Address Space

## 3.1 Address Space

This LSI has a 4-Gbyte address space, consisting of the range of addresses from 0000 0000h to FFFF FFFFh. That is, linear access to an address space of up to 4 Gbytes is possible, and this contains both program and data areas. Figure 3.1 shows the memory maps in the respective operating modes. Accessible areas will differ according to the operating mode and states of control bits.

### Table 4.1 List of I/O Registers (Address Order) (6/33)

|           | Module |                                                | Register | Number  | Access          | Number of Access Cy                |                            |

|-----------|--------|------------------------------------------------|----------|---------|-----------------|------------------------------------|----------------------------|

| ddress    | Symbol | Register Name                                  | Symbol   | of Bits | Size            | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |

| )08 8158h | TPU4   | Timer General Register A                       | TGRA     | 16      | 16              | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 815Ah  | TPU4   | Timer General Register B                       | TGRB     | 16      | 16              | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8160h | TPU5   | Timer Control Register                         | TCR      | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8161h | TPU5   | Timer Mode Register                            | TMDR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8162h | TPU5   | Timer I/O Control Register                     | TIOR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8164h | TPU5   | Timer Interrupt Enable Register                | TIER     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8165h | TPU5   | Timer Status Register                          | TSR      | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8166h | TPU5   | Timer Counter                                  | TCNT     | 16      | 16              | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8168h | TPU5   | Timer General Register A                       | TGRA     | 16      | 16              | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 816Ah | TPU5   | Timer General Register B                       | TGRB     | 16      | 16              | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8200h | TMR0   | Timer Control Register                         | TCR      | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8201h | TMR1   | Timer Control Register                         | TCR      | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8202h | TMR0   | Timer Control/Status Register                  | TCSR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8203h  | TMR1   | Timer Control/Status Register                  | TCSR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8204h  | TMR0   | Time Constant Register A                       | TCORA    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8205h  | TMR1   | Time Constant Register A                       | TCORA    | 8       | 8* <sup>1</sup> | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8206h  | TMR0   | Time Constant Register B                       | TCORB    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8207h  | TMR1   | Time Constant Register B                       | TCORB    | 8       | 8* <sup>1</sup> | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8208h  | TMR0   | Timer Counter                                  | TCNT     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8209h | TMR1   | Timer Counter                                  | TCNT     | 8       | 8* <sup>1</sup> | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 820Ah | TMR0   | Timer Counter Control Register                 | TCCR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 820Bh  | TMR1   | Timer Counter Control Register                 | TCCR     | 8       | 8* <sup>1</sup> | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 820Ch  | TMR0   | Timer Count Start Register                     | TCSTR    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8210h | TMR2   | Timer Control Register                         | TCR      | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8211h | TMR3   | Timer Control Register                         | TCR      | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8212h  | TMR2   | Timer Control/Status Register                  | TCSR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8213h | TMR3   | Timer Control/Status Register                  | TCSR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8214h | TMR2   | Time Constant Register A                       | TCORA    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8215h  | TMR3   | Time Constant Register A                       | TCORA    | 8       | 8*1             | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8216h  | TMR2   | Time Constant Register B                       | TCORB    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8217h | TMR3   | Time Constant Register B                       | TCORB    | 8       | 8* <sup>1</sup> | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8218h | TMR2   | Timer Counter                                  | TCNT     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8219h | TMR3   | Timer Counter                                  | TCNT     | 8       | 8*1             | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 821Ah | TMR2   | Timer Counter Control Register                 | TCCR     | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 821Bh | TMR3   | Timer Counter Control Register                 | TCCR     | 8       | 8* <sup>1</sup> | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 821Ch  | TMR2   | Timer Count Start Register                     | TCSTR    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8280h  | CRC    | CRC Control Register                           | CRCCR    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8281h  | CRC    | CRC Data Input Register                        | CRCDIR   | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8282h  | CRC    | CRC Data Output Register                       | CRCDOR   | 16      | 16              | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8300h  | RIIC0  | I <sup>2</sup> C-Bus Control Register 1        | ICCR1    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8301h | RIIC0  | I <sup>2</sup> C-Bus Control Register 2        | ICCR2    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8302h  | RIIC0  | I <sup>2</sup> C-Bus Mode Register 1           | ICMR1    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8303h | RIIC0  | I <sup>2</sup> C-Bus Mode Register 2           | ICMR2    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8304h | RIIC0  | I <sup>2</sup> C-Bus Mode Register 3           | ICMR3    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8305h  | RIIC0  | I <sup>2</sup> C-Bus Function Enable Register  | ICFER    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8306h  | RIIC0  | I <sup>2</sup> C-Bus Status Enable Register    | ICSER    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 8307h | RIIC0  | I <sup>2</sup> C-Bus Interrupt Enable Register | ICIER    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 8308h  | RIICO  | I <sup>2</sup> C-Bus Status Register 1         | ICSR1    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| )08 8309h | RIICO  | I <sup>2</sup> C-Bus Status Register 2         | ICSR2    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

| 08 830Ah  | RIICO  | Slave Address Register L0                      | SARLO    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

|           |        | ·g                                             |          | ~       | -               |                                    |                            |

| 08 830Bh  | RIIC0  | Slave Address Register U0                      | SARU0    | 8       | 8               | 2 or 3 PCLKB                       | 2 ICLK                     |

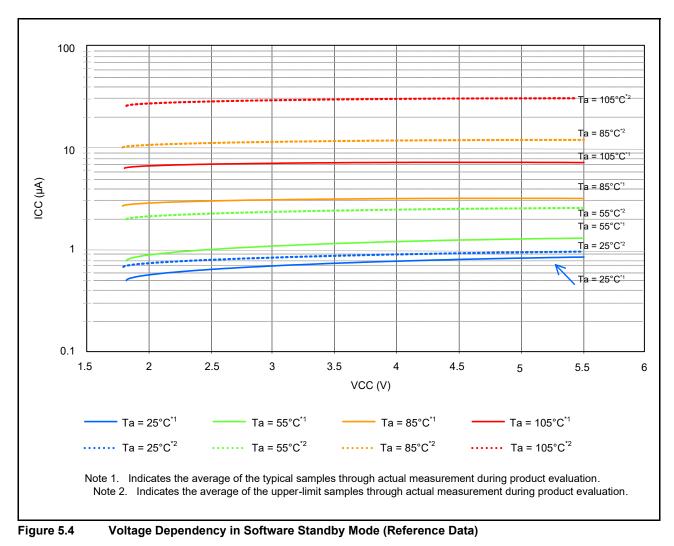

#### Table 5.8DC Characteristics (6)

Conditions: 1.8 V  $\leq$  VCC= VCC\_USB = AVCC0  $\leq$  5.5 V, VSS = AVSS0 = VSS\_USB = 0 V, T<sub>a</sub> = -40 to +105°C

|           | ltem              |                        | Symbol          | Typ.*3                                                    | Max. | Unit | Test Conditions                              |

|-----------|-------------------|------------------------|-----------------|-----------------------------------------------------------|------|------|----------------------------------------------|

| Supply    |                   |                        | I <sub>CC</sub> | 0.8                                                       | 3.7  | μA   |                                              |

| current*1 | current*1 mode*2  | T <sub>a</sub> = 55°C  |                 | 1.2                                                       | 4.3  |      |                                              |

|           |                   | T <sub>a</sub> = 85°C  |                 | 3.5                                                       | 18.6 |      |                                              |

|           |                   | T <sub>a</sub> = 105°C |                 | 7.9                                                       | 45.2 |      |                                              |

|           | Increment for IWD | T operation            |                 | 0.4                                                       | —    |      |                                              |

|           | Increment for LPT | operation              | tion 0.4 —      | Use IWDT-Dedicated On-Chip Oscillator for<br>clock source |      |      |                                              |

|           | Increment for RTC | operation*4            |                 | 0.4                                                       | —    |      | RCR3.RTCDV[2:0] set to low drive capacity    |

|           |                   |                        |                 | 1.2                                                       | _    |      | RCR3.RTCDV[2:0] set to normal drive capacity |

Note 1. Supply current values are with all output pins unloaded and all input pull-up MOSs in the off state.

Note 2. The IWDT, LVD, and CMPB are stopped.

Note 3. When VCC is 3.3 V.

Note 4. This increment includes the oscillation circuit.

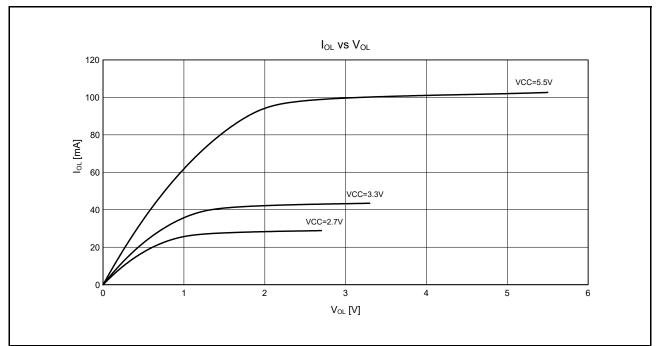

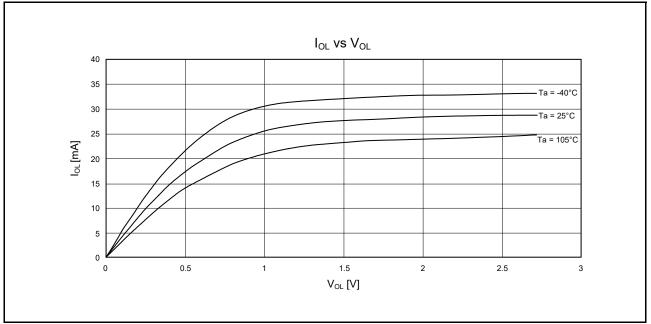

# 5.2.3 Normal I/O Pin Output Characteristics (3)

Figure 5.18 to Figure 5.21 show the characteristics of the RIIC output pin.

### Table 5.23 Operating Frequency Value (Low-Speed Operating Mode)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS}_{\text{USB}} = 0 \text{ V}$ ,  $\text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

|                                      |                                          |                  |                        | VCC                    |                        |      |  |

|--------------------------------------|------------------------------------------|------------------|------------------------|------------------------|------------------------|------|--|

|                                      | Item                                     | Symbol           | 1.8 V ≤ VCC <<br>2.4 V | 2.4 V ≤ VCC <<br>2.7 V | 2.7 V ≤ VCC ≤<br>5.5 V | Unit |  |

| Maximum                              | System clock (ICLK)                      | f <sub>max</sub> |                        | 32.768                 | •                      | kHz  |  |

| operating<br>frequency* <sup>3</sup> | FlashIF clock (FCLK)*1                   | 32.768           |                        |                        |                        |      |  |

| nequency                             | Peripheral module clock (PCLKA)          |                  | 32.768                 |                        |                        |      |  |

|                                      | Peripheral module clock (PCLKB)          |                  |                        | 32.768                 |                        |      |  |

|                                      | Peripheral module clock (PCLKD)*2 32.768 |                  |                        | 7                      |                        |      |  |

|                                      | External bus clock (BCLK)                |                  |                        | 32.768                 |                        |      |  |

|                                      | BCLK pin output                          |                  | 32.768                 |                        |                        |      |  |

Note 1. Programming and erasing the flash memory is impossible.

Note 2. The A/D converter cannot be used.

Note 3. The maximum operating frequency listed above does not include errors of the external oscillator. For details on the range for the guaranteed operation, see Table 5.26, Clock Timing.

#### Table 5.24BCLK Clock Timing (1)

Conditions:  $2.7 \text{ V} \le \text{VCC} = \text{VCC} \text{ USB} = \text{AVCC0} \le 5.5 \text{ V}$ , VSS = AVSS0 = VREFL0 = VSS USB = 0 V, fBCLK  $\le 32 \text{ MHz}$  (BCLK pin output frequency  $\le 16 \text{ MHz}$ ),  $\text{T}_{a} = -40 \text{ to} + 105^{\circ}\text{C}$

| Item                             | Symbol            | Min. | Тур. | Max. | Unit | Test Conditions |

|----------------------------------|-------------------|------|------|------|------|-----------------|

| BCLK pin output cycle time       | t <sub>Bcyc</sub> | 62.5 | _    | —    | ns   | Figure 5.22     |

| BCLK pin output high pulse width | t <sub>CH</sub>   | 15   |      | —    | ns   |                 |

| BCLK pin output low pulse width  | t <sub>CL</sub>   | 15   | -    | —    | ns   |                 |

| BCLK pin output rise time        | t <sub>Cr</sub>   | _    | _    | 12   | ns   |                 |

| BCLK pin output fall time        | t <sub>Cf</sub>   | —    | —    | 12   | ns   |                 |

#### Table 5.25BCLK Clock Timing (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} = \text{AVCC0} < 2.7 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ fBCLK} \le 16 \text{ MHz} (\text{BCLK pin output frequency} \le 8 \text{ MHz}), \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| Item                             | Symbol            | Min. | Тур. | Max. | Unit | Test Conditions |

|----------------------------------|-------------------|------|------|------|------|-----------------|

| BCLK pin output cycle time       | t <sub>Bcyc</sub> | 125  | —    | —    | ns   | Figure 5.22     |

| BCLK pin output high pulse width | t <sub>CH</sub>   | 30   | —    | —    | ns   |                 |

| BCLK pin output low pulse width  | t <sub>CL</sub>   | 30   | —    | —    | ns   |                 |

| BCLK pin output rise time        | t <sub>Cr</sub>   | _    | —    | 25   | ns   | -               |

| BCLK pin output fall time        | t <sub>Cf</sub>   | _    | —    | 25   | ns   | -               |

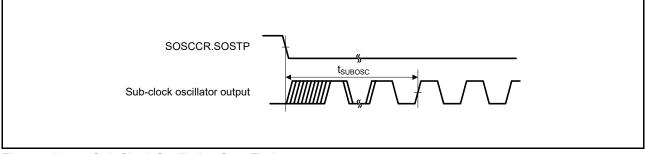

Figure 5.30 Sub-Clock Oscillation Start Timing

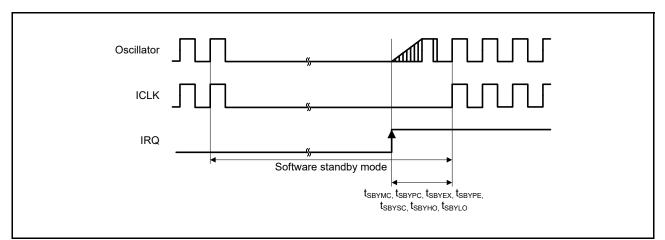

#### Table 5.30 Timing of Recovery from Low Power Consumption Modes (3)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS}_{USB} = 0 \text{ V}$ ,  $\text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

|                                                              | Item              |                                |                    | Min. | Тур. | Max. | Unit | Test<br>Conditions |

|--------------------------------------------------------------|-------------------|--------------------------------|--------------------|------|------|------|------|--------------------|

| Recovery time<br>from software<br>standby mode* <sup>1</sup> | Low-speed<br>mode | Sub-clock oscillator operating | t <sub>SBYSC</sub> | _    | 600  | 750  | μs   | Figure 5.34        |

Note 1. The sub-clock continues oscillating in software standby mode during low-speed mode.

#### Table 5.31 Timing of Recovery from Low Power Consumption Modes (4)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS}_{USB} = 0 \text{ V}$ ,  $\text{T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Ite                     | Symbol              | Min.              | Тур. | Max. | Unit | Test Conditions |             |

|-------------------------|---------------------|-------------------|------|------|------|-----------------|-------------|

| Recovery time from deep | High-speed mode*2   | t <sub>DSLP</sub> | —    | 2    | 3.5  | μs              | Figure 5.35 |

| sleep mode*1            | Middle-speed mode*3 | t <sub>DSLP</sub> | —    | 3    | 4    | μs              |             |

|                         | Low-speed mode*4    |                   | —    | 400  | 500  | μs              |             |

Note 1. Oscillators continue oscillating in deep sleep mode.

Note 2. When the frequency of the system clock is 32 MHz.

Note 3. When the frequency of the system clock is 12 MHz.

Note 4. When the frequency of the system clock is 32 kHz.

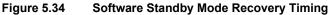

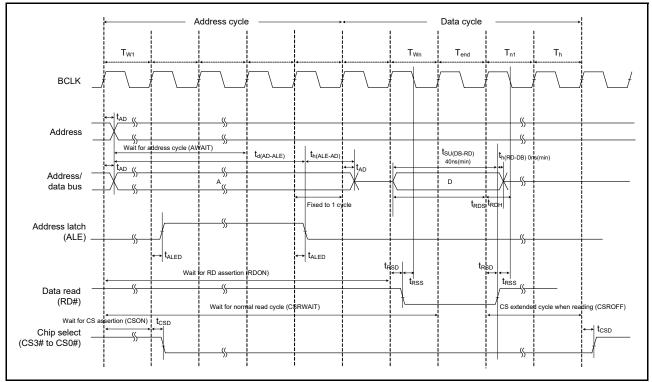

Figure 5.38 External Bus Timing/Normal Read Cycle (Bus Clock Synchronization)

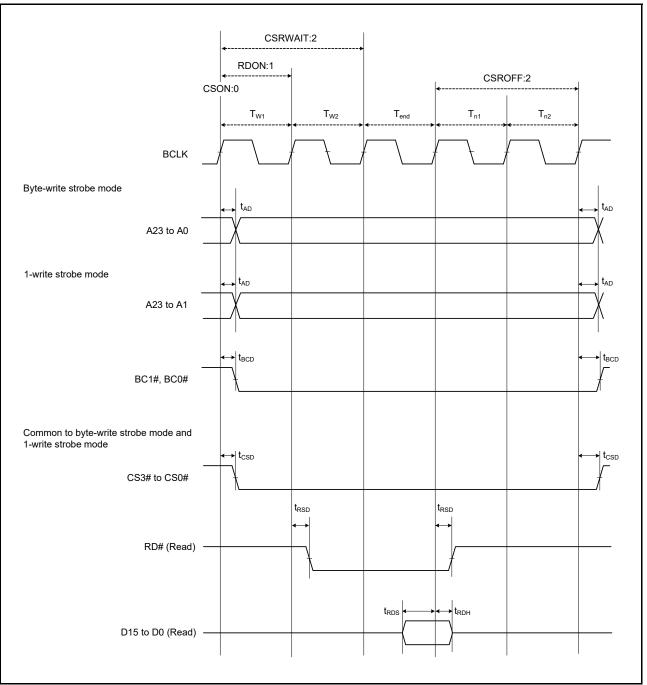

Figure 5.39 External Bus Timing/Normal Write Cycle (Bus Clock Synchronization)

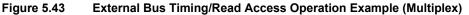

External Bus Timing/Write Access Operation Example (Multiplex)

### Differential non-linearity error (DNL)

The differential non-linearity error is the difference between 1-LSB width based on the ideal A/D conversion characteristics and the width of the actual output code.

#### Offset error

An offset error is the difference between a transition point of the ideal first output code and the actual first output code.

#### Full-scale error

A full-scale error is the difference between a transition point of the ideal last output code and the actual last output code.

Figure C 64 -Pin WFLGA (PWLG0064KA-A)

| Rev. | Date         |                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Classification |

|------|--------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|      | 0.100.0015   | Page                             | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 1.10 | Oct 30, 2015 | 142                              | Table 5.45 A/D Conversion Characteristics (1):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|      |              | 4.40                             | Conditions and Voltage Range of Analog Input (Max.), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|      |              | 143                              | Table 5.46 A/D Conversion Characteristics (2): Conditions changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|      |              | 144                              | Table 5.47 A/D Conversion Characteristics (3): Conditions changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|      |              | 145                              | Table 5.48 A/D Conversion Characteristics (4): Conditions changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|      |              | 146                              | Table 5.49 A/D Conversion Characteristics (5): Conditions changed and           Absolute accuracy (Test Conditions) deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

|      |              | 153                              | Table 5.57 Characteristics of Power-On Reset Circuit and Voltage Detection Circuit (1), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TN-RX*-A137A/E |

|      |              | 154                              | Table 5.58 Characteristics of Power-On Reset Circuit and Voltage Detection Circuit (2), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|      |              | 155                              | Figure 5.73 Power-On Reset Timing and Figure 5.74 Voltage Detection<br>Circuit Timing (Vdet0), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|      |              | 159                              | Table 5.62 ROM (Flash Memory for Code Storage) Characteristics (2) High-<br>Speed Operating Mode: Note changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|      |              | 160                              | Table 5.63 ROM (Flash Memory for Code Storage) Characteristics (3)           Middle-Speed Operating Mode: Note changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|      |              | 161                              | Table 5.65 E2 DataFlash Characteristics (2): high-speed operating mode, Note changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|      |              | 161                              | Table 5.66 E2 DataFlash Characteristics (3): middle-speed operating mode,           Conditions and Note changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|      |              | 163                              | Figure 5.79 Connecting Capacitors (100 Pins), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

|      |              | 164                              | Figure 5.80 Connecting Capacitors (64 Pins), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|      |              | 165                              | Figure 5.81 Connecting Capacitors (48 Pins), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

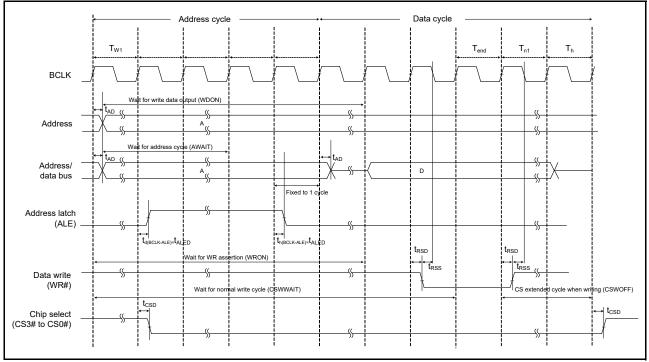

|      |              | Appendix 1.                      | Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|      |              | 167                              | Figure B 100 -Pin LQFP (PLQP0100KB-B), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TN-RX*-A137A/I |

|      |              | 170                              | Figure E 64 -Pin LQFP (PLQP0064KB-C), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TN-RX*-A137A/I |

|      |              | 172                              | Figure G 48 -Pin LQFP (PLQP0048KB-B), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TN-RX*-A137A/I |

| 1.20 | Sep 28, 2018 | Features                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|      | 000 20, 2010 | 1                                | SD host interface (optional: one channel) SD memory/ SDIO 1-bit or<br>4-bit SD bus supported, Note deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TN-RX*-A145A/E |

|      |              | 1. Overview                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|      |              | 6                                | Table 1.2 Comparison of Functions for Different Packages, changed<br>(deletion of IRQ2 on 64-pin package)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

|      |              | 6                                | Table 1.2 Comparison of Functions for Different Packages, Note 1 added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TN-RX*-A145A/  |

|      |              | 7                                | Table 1.3 List of Products: D Version (Ta = -40 to +85°C) (1/2), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TN-RX*-A145A/  |

|      |              | 9                                | Table 1.4 List of Products: G Version (Ta = $-40$ to $+105^{\circ}$ C) (1/2), changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TN-RX*-A145A/  |

|      |              | 11                               | Figure 1.1 How to Read the Product Part Number, changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TN-RX*-A145A/  |

|      |              | 16                               | Table 1.5 Pin Functions (4/4), changed (changes in description for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TN-RX*-A201A/I |

|      |              | 04                               | VCC_USB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|      |              | 24                               | Table 1.6 List of Pins and Pin Functions (100-Pin TFLGA) (2/3), changed (UPSEL was added to the column of P35)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |