Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RXv2                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 54MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SD/SDIO, SPI, SSI, USB OTG                          |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 43                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-WFLGA                                                                         |

| Supplier Device Package    | 64-FLGA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52316cdlf-20 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification             | Module/Function                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timers                     | Independent watchdog<br>timer (IWDTa)            | <ul> <li>14 bits × 1 channel</li> <li>Count clock: Dedicated low-speed on-chip oscillator for the IWDT<br/>Frequency divided by 1, 16, 32, 64, 128, or 256</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | Realtime clock (RTCe)                            | <ul> <li>Clock source: Sub-clock</li> <li>Time/calendar</li> <li>Interrupts: Alarm interrupt, periodic interrupt, and carry interrupt</li> <li>Time-capture facility for three values</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                            | Low power timer (LPT)                            | <ul> <li>16 bits × 1 channel</li> <li>Clock source: Sub-clock, Dedicated low-speed on-chip oscillator for the IWDT Frequency divided by 2, 4, 8, 16, or 32</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | 8-bit timer (TMR)                                | <ul> <li>(8 bits × 2 channels) × 2 units</li> <li>Seven internal clocks (PCLK/1, PCLK/2, PCLK/8, PCLK/32, PCLK/64, PCLK/1024, and PCLK/8192) and an external clock can be selected</li> <li>Pulse output and PWM output with any duty cycle are available</li> <li>Two channels can be cascaded and used as a 16-bit timer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Communication<br>functions | Serial communications<br>interfaces (SCIg, SCIh) | <ul> <li>7 channels (channel 0, 1, 5, 6, 8, 9: SCIg, channel 12: SCIh)</li> <li>SCIg Serial communications modes: Asynchronous, clock synchronous, and smart-card interface Multi-processor function On-chip baud rate generator allows selection of the desired bit rate Choice of LSB-first or MSB-first transfer Average transfer rate clock can be input from TMR timers for SCI5, SCI6, and SCI12 Start-bit detection: Level or edge detection is selectable. Simple I<sup>2</sup>C Simple SPI 9-bit transfer mode Bit rate modulation Event linking by the ELC (only on channel 5)</li> <li>SCIh (The following functions are added to SCIg) Supports the serial communications protocol, which contains the start frame and information frame Supports the LIN format</li> </ul>                      |

|                            | IrDA interface (IRDA)                            | <ul> <li>1 channel (SCI5 used)</li> <li>Supports encoding/decoding of waveforms conforming to IrDA standard 1.0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | I <sup>2</sup> C bus interface (RIICa)           | <ul> <li>1 channel</li> <li>Communications formats: I<sup>2</sup>C bus format/SMBus format</li> <li>Master mode or slave mode selectable</li> <li>Supports fast mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            | Serial peripheral interface<br>(RSPIa)           | <ul> <li>1 channel</li> <li>Transfer facility</li> <li>Using the MOSI (master out, slave in), MISO (master in, slave out), SSL (slave select), and RSPCF (RSPI clock) enables serial transfer through SPI operation (four lines) or clock-synchronous operation (three lines)</li> <li>Capable of handling serial transfer as a master or slave</li> <li>Data formats</li> <li>Choice of LSB-first or MSB-first transfer</li> <li>The number of bits in each transfer can be changed to 8, 9, 10, 11, 12, 13, 14, 15, 16, 20, 24, or 32 bits.</li> <li>128-bit buffers for transmission and reception</li> <li>Up to four frames can be transmitted or received in a single transfer operation (with each frame having up to 32 bits)</li> <li>Double buffers for both transmission and reception</li> </ul> |

|                            | USB 2.0 host/function<br>module (USBd)           | <ul> <li>USB Device Controller (UDC) and transceiver for USB 2.0 are incorporated.</li> <li>Host/function module: 1 port</li> <li>Compliant with USB version 2.0</li> <li>Transfer speed: Full-speed (12 Mbps), low-speed (1.5 Mbps)</li> <li>OTG (ON-The-Go) is supported.</li> <li>Isochronous transfer is supported.</li> <li>BC1.2 (Battery Charging Specification Revision 1.2) is supported.</li> <li>Internal power supply for USB (allows operation without external power input to the VCC_USB pin when VCC = 4.0 to 5.5V)</li> </ul>                                                                                                                                                                                                                                                               |

|                            | CAN module (RSCAN)                               | <ul> <li>1 channel</li> <li>Compliance with the ISO11898-1 specification (standard frame and extended frame)</li> <li>16 Message boxes</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 1.1Outline of Specifications (3/4)

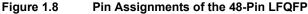

Figure 1.9 Pin Assignments of the 48-Pin HWQFN

RENESAS

# Table 4.1 List of I/O Registers (Address Order) (17/33)

|            | Module     |                                   | Register         | Number  | Access | Number of Access                   | Cycles                     |

|------------|------------|-----------------------------------|------------------|---------|--------|------------------------------------|----------------------------|

| ddress     | Symbol     | Register Name                     | Symbol           | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |

| 008 C0A4h  | PORTJ      | Open Drain Control Register 0     | ODR0             | 8       | 8, 16  | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0C0h  | PORT0      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0C1h  | PORT1      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0C2h  | PORT2      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0C3h  | PORT3      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0C4h  | PORT4      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0C5h  | PORT5      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0CAh  | PORTA      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0CBh  | PORTB      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0CCh  | PORTC      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0CDh  | PORTD      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0CEh  | PORTE      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0D1h  | PORTH      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0D2h  | PORTJ      | Pull-Up Control Register          | PCR              | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0E1h  | PORT1      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0E2h  | PORT2      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0E3h  | PORT3      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0E5h  | PORT5      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0EAh  | PORTA      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0EBh  | PORTB      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0ECh  | PORTC      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0EDh  | PORTD      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 COEEh  | PORTE      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0F1h  | PORTH      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C0F2h  | PORTJ      | Drive Capacity Control Register   | DSCR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C100h  | MPC        | CS Output Enable Register         | PFCSE            | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C104h  | MPC        | Address Output Enable Register 0  | PFAOE0           | 8       | 8, 16  | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C105h  | MPC        | Address Output Enable Register 1  | PFAOE1           | 8       | 8, 16  | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C106h  | MPC        | External Bus Control Register 0   | PFBCR0           | 8       | 8, 16  | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C107h  | MPC        | External Bus Control Register 1   | PFBCR1           | 8       | 8, 16  | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C11Fh  | MPC        | Write-Protect Register            | PWPR             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C120h  | PORT       | Port Switching Register B         | PSRB             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C121h  | PORT       | Port Switching Register A         | PSRA             | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C143h  | MPC        | P03 Pin Function Control Register | P03PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C145h  | MPC        | P05 Pin Function Control Register | P05PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 IOLK                     |

| 008 C145h  | MPC        | P07 Pin Function Control Register | P07PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 IOLK                     |

| 008 C14711 | MPC        | P12 Pin Function Control Register | P12PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C14An  | MPC        | P13 Pin Function Control Register | P13PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C14Bh  | MPC        | P13 Pin Function Control Register | P13PFS<br>P14PFS | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK<br>2 ICLK           |

| 008 C14Ch  | MPC        | •                                 | P14PFS<br>P15PFS | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK<br>2 ICLK           |

| 008 C14Dh  | MPC        | P15 Pin Function Control Register | P15PFS<br>P16PFS | 8       | 8      |                                    | 2 ICLK<br>2 ICLK           |

| 008 C14En  | MPC        | P16 Pin Function Control Register | P16PFS<br>P17PFS | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK<br>2 ICLK           |

|            |            | P17 Pin Function Control Register |                  |         |        | 2 or 3 PCLKB                       |                            |

| 008 C150h  | MPC        | P20 Pin Function Control Register | P20PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C151h  | MPC        | P21 Pin Function Control Register | P21PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C152h  | MPC        | P22 Pin Function Control Register | P22PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C153h  | MPC        | P23 Pin Function Control Register | P23PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C154h  | MPC        | P24 Pin Function Control Register | P24PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C155h  | MPC        | P25 Pin Function Control Register | P25PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C156h  | MPC        | P26 Pin Function Control Register | P26PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

|            | MDC        | P27 Pin Function Control Register | P27PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

| 008 C157h  | MPC<br>MPC | P30 Pin Function Control Register | P30PFS           | 8       | 8      | 2 or 3 PCLKB                       | 2 ICLK                     |

# Table 4.1 List of I/O Registers (Address Order) (25/33)

|           | Module |                                 | Register | Number  | Access | Number of Access                   | Cycles                     |

|-----------|--------|---------------------------------|----------|---------|--------|------------------------------------|----------------------------|

| ddress    | Symbol | Register Name                   | Symbol   | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |

| 0A 83AAh  | RSCAN  | Receive Rule Entry Register 0CH | GAFLPH0  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83AAh  | RSCAN  | Receive Buffer Register 0CH     | RMDF10   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83ACh  | RSCAN  | Receive Rule Entry Register 1AL | GAFLIDL1 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83ACh  | RSCAN  | Receive Buffer Register 0DL     | RMDF20   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83AEh  | RSCAN  | Receive Rule Entry Register 1AH | GAFLIDH1 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83AEh  | RSCAN  | Receive Buffer Register 0DH     | RMDF30   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83B0h | RSCAN  | Receive Rule Entry Register 1BL | GAFLML1  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83B0h | RSCAN  | Receive Buffer Register 1AL     | RMIDL1   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83B2h | RSCAN  | Receive Rule Entry Register 1BH | GAFLMH1  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83B2h | RSCAN  | Receive Buffer Register 1AH     | RMIDH1   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83B4h  | RSCAN  | Receive Rule Entry Register 1CL | GAFLPL1  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83B4h | RSCAN  | Receive Buffer Register 1BL     | RMTS1    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83B6h  | RSCAN  | Receive Rule Entry Register 1CH | GAFLPH1  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83B6h  | RSCAN  | Receive Buffer Register 1BH     | RMPTR1   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83B8h  | RSCAN  | Receive Rule Entry Register 2AL | GAFLIDL2 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83B8h  | RSCAN  | Receive Buffer Register 1CL     | RMDF01   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83BAh | RSCAN  | Receive Rule Entry Register 2AH | GAFLIDH2 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83BAh  | RSCAN  | Receive Buffer Register 1CH     | RMDF11   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83BCh  | RSCAN  | Receive Rule Entry Register 2BL | GAFLML2  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83BCh | RSCAN  | Receive Buffer Register 1DL     | RMDF21   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83BEh  | RSCAN  | Receive Rule Entry Register 2BH | GAFLMH2  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83BEh  | RSCAN  | Receive Buffer Register 1DH     | RMDF31   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C0h | RSCAN  | Receive Rule Entry Register 2CL | GAFLPL2  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C0h | RSCAN  | Receive Buffer Register 2AL     | RMIDL2   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C2h | RSCAN  | Receive Rule Entry Register 2CH | GAFLPH2  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C2h | RSCAN  | Receive Buffer Register 2AH     | RMIDH2   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C4h | RSCAN  | Receive Rule Entry Register 3AL | GAFLIDL3 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C4h | RSCAN  | Receive Buffer Register 2BL     | RMTS2    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83C6h  | RSCAN  | Receive Rule Entry Register 3AH | GAFLIDH3 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C6h | RSCAN  | Receive Buffer Register 2BH     | RMPTR2   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C8h | RSCAN  | Receive Rule Entry Register 3BL | GAFLML3  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83C8h | RSCAN  | Receive Buffer Register 2CL     | RMDF02   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83CAh | RSCAN  | Receive Rule Entry Register 3BH | GAFLMH3  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83CAh | RSCAN  | Receive Buffer Register 2CH     | RMDF12   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83CCh | RSCAN  | Receive Rule Entry Register 3CL | GAFLPL3  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83CCh | RSCAN  | Receive Buffer Register 2DL     | RMDF22   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83CEh  | RSCAN  | Receive Rule Entry Register 3CH | GAFLPH3  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83CEh  | RSCAN  | Receive Buffer Register 2DH     | RMDF32   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D0h  | RSCAN  | Receive Rule Entry Register 4AL | GAFLIDL4 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D0h  | RSCAN  | Receive Buffer Register 3AL     | RMIDL3   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83D2h | RSCAN  | Receive Rule Entry Register 4AH | GAFLIDH4 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83D2h | RSCAN  | Receive Buffer Register 3AH     | RMIDH3   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D4h  | RSCAN  | Receive Rule Entry Register 4BL | GAFLML4  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D4h  | RSCAN  | Receive Buffer Register 3BL     | RMTS3    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D6h  | RSCAN  | Receive Rule Entry Register 4BH | GAFLMH4  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D6h  | RSCAN  | Receive Buffer Register 3BH     | RMPTR3   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D8h  | RSCAN  | Receive Rule Entry Register 4CL | GAFLPL4  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83D8h  | RSCAN  | Receive Buffer Register 3CL     | RMDF03   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83DAh  | RSCAN  | Receive Rule Entry Register 4CH | GAFLPH4  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83DAh  | RSCAN  | Receive Buffer Register 3CH     | RMDF13   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

|           |        | -                               |          |         |        |                                    |                            |

| 0A 83DCh  | RSCAN  | Receive Rule Entry Register 5AL | GAFLIDL5 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

# Table 4.1 List of I/O Registers (Address Order) (26/33)

|           | Module |                                 | Register | Number  | Access | Number of Access                   | Cycles                     |

|-----------|--------|---------------------------------|----------|---------|--------|------------------------------------|----------------------------|

| ddress    | Symbol | Register Name                   | Symbol   | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |

| 00A 83DEh | RSCAN  | Receive Rule Entry Register 5AH | GAFLIDH5 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83DEh  | RSCAN  | Receive Buffer Register 3DH     | RMDF33   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83E0h  | RSCAN  | Receive Rule Entry Register 5BL | GAFLML5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E0h | RSCAN  | Receive Buffer Register 4AL     | RMIDL4   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E2h | RSCAN  | Receive Rule Entry Register 5BH | GAFLMH5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E2h | RSCAN  | Receive Buffer Register 4AH     | RMIDH4   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E4h | RSCAN  | Receive Rule Entry Register 5CL | GAFLPL5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E4h | RSCAN  | Receive Buffer Register 4BL     | RMTS4    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E6h | RSCAN  | Receive Rule Entry Register 5CH | GAFLPH5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E6h | RSCAN  | Receive Buffer Register 4BH     | RMPTR4   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83E8h  | RSCAN  | Receive Rule Entry Register 6AL | GAFLIDL6 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83E8h | RSCAN  | Receive Buffer Register 4CL     | RMDF04   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83EAh | RSCAN  | Receive Rule Entry Register 6AH | GAFLIDH6 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83EAh  | RSCAN  | Receive Buffer Register 4CH     | RMDF14   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83ECh  | RSCAN  | Receive Rule Entry Register 6BL | GAFLML6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83ECh  | RSCAN  | Receive Buffer Register 4DL     | RMDF24   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83EEh | RSCAN  | Receive Rule Entry Register 6BH | GAFLMH6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83EEh | RSCAN  | Receive Buffer Register 4DH     | RMDF34   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F0h | RSCAN  | Receive Rule Entry Register 6CL | GAFLPL6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F0h | RSCAN  | Receive Buffer Register 5AL     | RMIDL5   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F2h | RSCAN  | Receive Rule Entry Register 6CH | GAFLPH6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F2h | RSCAN  | Receive Buffer Register 5AH     | RMIDH5   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F4h | RSCAN  | Receive Rule Entry Register 7AL | GAFLIDL7 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F4h | RSCAN  | Receive Buffer Register 5BL     | RMTS5    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F6h | RSCAN  | Receive Rule Entry Register 7AH | GAFLIDH7 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F6h | RSCAN  | Receive Buffer Register 5BH     | RMPTR5   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F8h | RSCAN  | Receive Rule Entry Register 7BL | GAFLML7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83F8h | RSCAN  | Receive Buffer Register 5CL     | RMDF05   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83FAh | RSCAN  | Receive Rule Entry Register 7BH | GAFLMH7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83FAh | RSCAN  | Receive Buffer Register 5CH     | RMDF15   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83FCh | RSCAN  | Receive Rule Entry Register 7CL | GAFLPL7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 83FCh | RSCAN  | Receive Buffer Register 5DL     | RMDF25   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83FEh  | RSCAN  | Receive Rule Entry Register 7CH | GAFLPH7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 83FEh  | RSCAN  | Receive Buffer Register 5DH     | RMDF35   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8400h | RSCAN  | Receive Rule Entry Register 8AL | GAFLIDL8 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8400h | RSCAN  | Receive Buffer Register 6AL     | RMIDL6   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8402h | RSCAN  | Receive Rule Entry Register 8AH | GAFLIDH8 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8402h | RSCAN  | Receive Buffer Register 6AH     | RMIDH6   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8404h | RSCAN  | Receive Rule Entry Register 8BL | GAFLML8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8404h | RSCAN  | Receive Buffer Register 6BL     | RMTS6    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8406h | RSCAN  | Receive Rule Entry Register 8BH | GAFLMH8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8406h | RSCAN  | Receive Buffer Register 6BH     | RMPTR6   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 8408h | RSCAN  | Receive Rule Entry Register 8CL | GAFLPL8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 8408h  | RSCAN  | Receive Buffer Register 6CL     | RMDF06   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 840Ah  | RSCAN  | Receive Rule Entry Register 8CH | GAFLPH8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 840Ah  | RSCAN  | Receive Buffer Register 6CH     | RMDF16   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 0A 840Ch  | RSCAN  | Receive Rule Entry Register 9AL | GAFLIDL9 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 840Ch | RSCAN  | Receive Buffer Register 6DL     | RMDF26   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 840Eh | RSCAN  | Receive Rule Entry Register 9AH | GAFLIDH9 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

| 00A 840Eh | RSCAN  | Receive Buffer Register 6DH     | RMDF36   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

|           |        | -                               |          |         |        |                                    | 2.0210                     |

| 0A 8410h  | RSCAN  | Receive Rule Entry Register 9BL | GAFLML9  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |

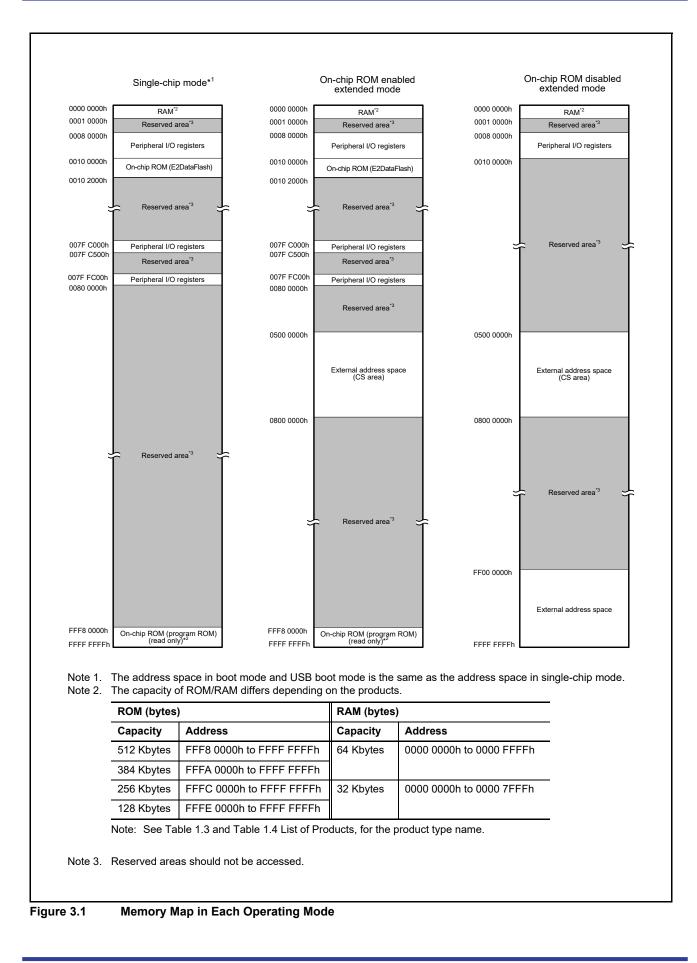

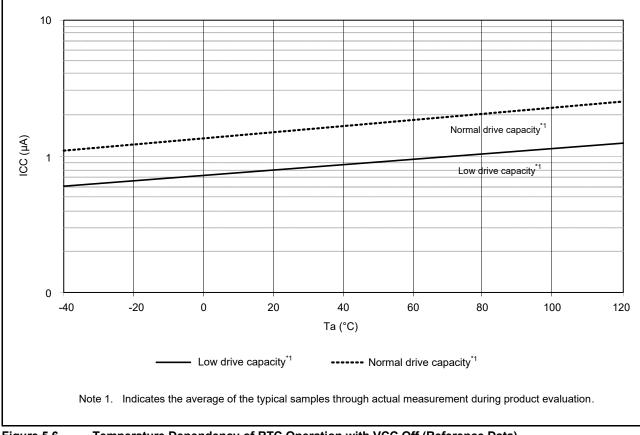

# Figure 5.6 Temperature Dependency of RTC Operation with VCC Off (Reference Data)

#### Table 5.10DC Characteristics (8)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V}$

| Item                                  | Symbol | Min. | Тур. | Max. | Unit | Test Conditions   |

|---------------------------------------|--------|------|------|------|------|-------------------|

| Permissible total power consumption*1 | Pd     | —    | —    | 350  | mW   | D-version product |

| Permissible total power consumption*1 | Pd     | _    | —    | 130  | mW   | G-version product |

Note: Please contact a Renesas Electronics sales office for information on the derating of the G-version product. Derating is the systematic reduction of load to improve reliability.

Note 1. Total power dissipated by the entire chip (including output currents)

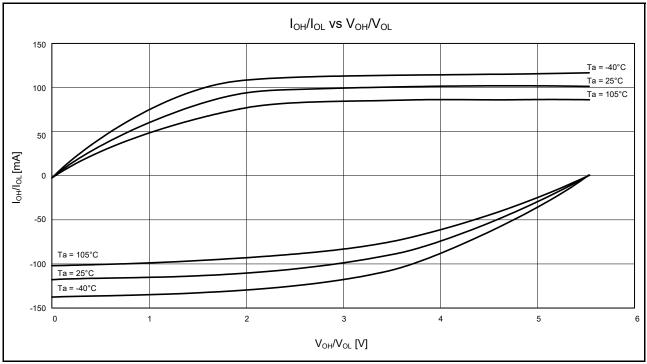

Figure 5.17 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Temperature Characteristics at VCC = 5.5 V When High-Drive Output is Selected (Reference Data)

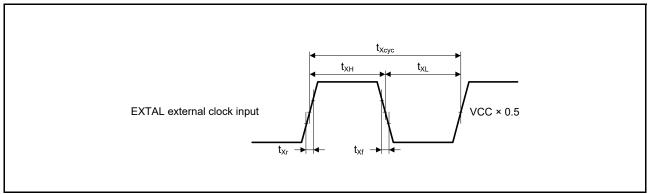

Figure 5.23 EXTAL External Clock Input Timing

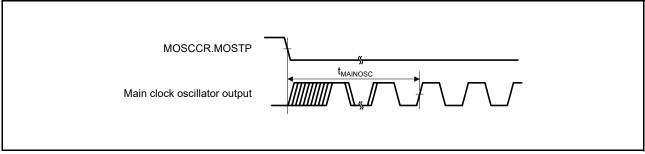

Figure 5.24 Main Clock Oscillation Start Timing

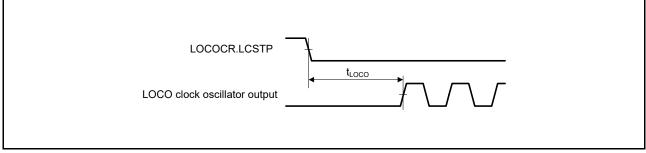

Figure 5.25 LOCO Clock Oscillation Start Timing

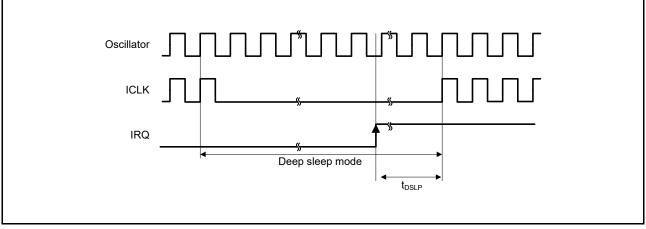

# Table 5.32 Operating Mode Transition Time

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VREFL0} = \text{VSS}_{\text{USB}} = 0 \text{ V}$ ,  $\text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| Mode before Transition                                 | Mode after Transition                                     | ICLK Frequency | Tra  | Unit |      |       |

|--------------------------------------------------------|-----------------------------------------------------------|----------------|------|------|------|-------|

| Mode before Transition                                 |                                                           | ICEN Frequency | Min. | Тур. | Max. | Offic |

| High-speed operating mode                              | Middle-speed operating modes                              | 8 MHz          | —    | 10   | —    | μs    |

| Middle-speed operating modes                           | High-speed operating mode                                 | 8 MHz          | —    | 37.5 | —    | μs    |

| Low-speed operating mode                               | Middle-speed operating mode,<br>high-speed operating mode | 32.768 kHz     | _    | 215  | —    | μs    |

| Middle-speed operating mode, high-speed operating mode | Low-speed operating mode                                  | 32.768 kHz     | —    | 185  | —    | μs    |

Note: Values when the frequencies of PCLKA, PCLKB, PCLKD, FCLK, and BCLK are not divided.

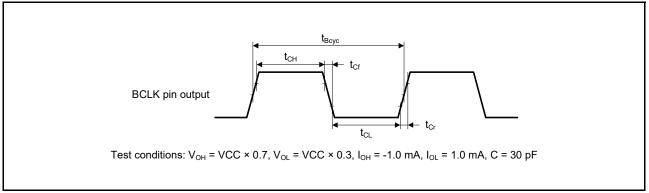

Figure 5.40 External Bus Timing/Page Read Cycle (Bus Clock Synchronization)

Figure 5.41 External Bus Timing/Page Write Cycle (Bus Clock Synchronization)

#### Table 5.42 **Timing of On-Chip Peripheral Modules (5)**

Conditions: 2.7 V ≤ VCC = VCC\_USB = AVCC0 ≤ 5.5 V, VSS = AVSS0 = VSS\_USB = 0 V, fPCLKB ≤ 32 MHz,  $T_a = -40 \text{ to } +105^{\circ}\text{C}$

|                         | Item                         | Symbol            | Min.*1 | Max.                  | Unit | Test<br>Conditions |

|-------------------------|------------------------------|-------------------|--------|-----------------------|------|--------------------|

| Simple I <sup>2</sup> C | SDA rise time                | t <sub>Sr</sub>   | —      | 1000                  | ns   | Figure 5.59        |

| (Standard mode)         | SDA fall time                | t <sub>Sf</sub>   | —      | 300                   | ns   |                    |

|                         | SDA spike pulse removal time | t <sub>SP</sub>   | 0      | 4 × t <sub>Pcyc</sub> | ns   |                    |

|                         | Data setup time              | t <sub>SDAS</sub> | 250    | —                     | ns   |                    |

|                         | Data hold time               | t <sub>SDAH</sub> | 0      | —                     | ns   |                    |

|                         | SCL, SDA capacitive load     | Cb                | —      | 400                   | pF   |                    |

| Simple I <sup>2</sup> C | SDA rise time                | t <sub>Sr</sub>   | —      | 300                   | ns   | Figure 5.59        |

| (Fast mode)             | SDA fall time                | t <sub>Sf</sub>   | —      | 300                   | ns   |                    |

|                         | SDA spike pulse removal time | t <sub>SP</sub>   | 0      | 4 × t <sub>Pcyc</sub> | ns   |                    |

|                         | Data setup time              | t <sub>SDAS</sub> | 100    | —                     | ns   |                    |

|                         | Data hold time               | t <sub>SDAH</sub> | 0      | _                     | ns   |                    |

|                         | SCL, SDA capacitive load     | Cb                | _      | 400                   | pF   |                    |

Note:  $t_{Pcyc}$ : PCLK cycle Note 1.  $C_b$  is the total capacitance of the bus lines.

#### Table 5.43 Timing of On-Chip Peripheral Modules (6)

Conditions: 1.8 V ≤ VCC = VCC\_USB = AVCC0 ≤ 5.5 V, VSS = AVSS0 = VSS\_USB = 0 V, fPCLKB ≤ 32 MHz,  $T_a = -40 \text{ to } +105^{\circ}\text{C}$

|     | Item                 |                   | Symbol             | Min. | Max. | Unit   | Test<br>Conditions |

|-----|----------------------|-------------------|--------------------|------|------|--------|--------------------|

| SSI | AUDIO_MCLK input     | 2.7 V or above    | t <sub>AUDIO</sub> | 1    | 25   | MHz    |                    |

|     | frequency            | 1.8 V or above    |                    | 1    | 4    |        |                    |

|     | Output clock cycle   |                   | t <sub>O</sub>     | 250  | —    | ns     | Figure 5.60        |

|     | Input clock cycle    |                   | t <sub>l</sub>     | 250  | —    | ns     |                    |

|     | Clock high level     |                   | t <sub>HC</sub>    | 0.4  | 0.6  | to, ti |                    |

|     | Clock low level      | Clock low level   |                    | 0.4  | 0.6  | to, ti |                    |

|     | Clock rise time      | Clock rise time   |                    | —    | 20   | ns     |                    |

|     | Data delay time      | 2.7 V or above    | t <sub>DTR</sub>   | —    | 65   | ns     | Figure 5.61        |

|     |                      | 1.8 V or above    |                    | _    | 105  |        | Figure 5.62        |

|     | Setup time           | 2.7 V or above    | t <sub>SR</sub>    | 65   | _    | ns     |                    |

|     |                      | 1.8 V or above    |                    | 90   | _    |        |                    |

|     | Hold time            |                   | t <sub>HTR</sub>   | 40   | —    | ns     | 1                  |

|     | WS changing edge SSI | DATA output delay | t <sub>DTRW</sub>  | _    | 105  | ns     | Figure 5.63        |

#### Table 5.49 A/D Conversion Characteristics (4)

Conditions: 2.4V ≤ VCC = VCC\_USB = AVCC0 ≤ 5.5V, 2.4V ≤ VREFH0 ≤ AVCC0, VSS = AVSS0 = VSS\_USB = 0V, reference voltage = VREFH0 selected, Ta = -40 to +105°C

| Item                                                              | Min.                                                              | Тур. | Max.  | Unit | Test Conditions |                                                                                     |

|-------------------------------------------------------------------|-------------------------------------------------------------------|------|-------|------|-----------------|-------------------------------------------------------------------------------------|

| Frequency                                                         | 1                                                                 | —    | 16    | MHz  |                 |                                                                                     |

| Resolution                                                        |                                                                   | _    | —     | 12   | Bit             |                                                                                     |

| Conversion time <sup>*1</sup><br>(Operation at<br>PCLKD = 16 MHz) | Permissible signal<br>source impedance<br>(Max.) = 2.2 k $\Omega$ | 3.38 | _     | _    | μs              | High-precision channel<br>The ADCSR.ADHSC bit is 1<br>The ADSSTRn register is 0Dh   |

|                                                                   |                                                                   | 5.06 | _     | _    |                 | Normal-precision channel<br>The ADCSR.ADHSC bit is 1<br>The ADSSTRn register is 28h |

| Analog input capacitance                                          | Cs                                                                | _    | —     | 15   | pF              | Pin capacitance included<br>Figure 5.68                                             |

| Analog input resistance                                           | Rs                                                                | _    | —     | 2.5  | kΩ              | Figure 5.68                                                                         |

| Offset error                                                      | ·                                                                 | _    | ±0.5  | ±4.5 | LSB             |                                                                                     |

| Full-scale error                                                  |                                                                   | _    | ±0.75 | ±4.5 | LSB             |                                                                                     |

| Quantization error                                                |                                                                   | —    | ±0.5  | —    | LSB             |                                                                                     |

| Absolute accuracy                                                 |                                                                   | —    | ±1.25 | ±5.0 | LSB             | High-precision channel                                                              |

|                                                                   |                                                                   |      |       | ±8.0 | LSB             | Other than above                                                                    |

| DNL differential non-linearit                                     | ty error                                                          | _    | ±1.0  | —    | LSB             |                                                                                     |

| INL integral non-linearity error                                  |                                                                   | _    | ±1.0  | ±3.0 | LSB             |                                                                                     |

Note: The characteristics apply when no pin functions other than A/D converter input are used. Absolute accuracy includes quantization errors. Offset error, full-scale error, DNL differential non-linearity error, and INL integral non-linearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. As the test conditions, the number of sampling states is indicated.

## Differential non-linearity error (DNL)

The differential non-linearity error is the difference between 1-LSB width based on the ideal A/D conversion characteristics and the width of the actual output code.

### Offset error

An offset error is the difference between a transition point of the ideal first output code and the actual first output code.

#### Full-scale error

A full-scale error is the difference between a transition point of the ideal last output code and the actual last output code.

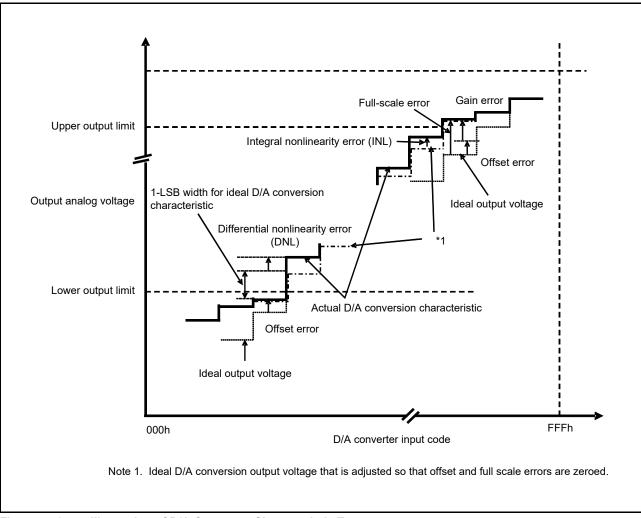

Figure 5.70 Illustration of D/A Converter Characteristic Terms

# Integral non-linearity error (INL)

The integral non-linearity error is the maximum deviation between the ideal line when the measured offset and full-scale errors are zeroed, and the actual output code.

### Differential non-linearity error (DNL)

The differential non-linearity error is the difference between 1-LSB width based on the ideal D/A conversion characteristics and the width of the actually output code.

### Offset error

An offset error is the difference between a transition point of the ideal first output code and the actual first output code.

### Full-scale error

A full-scale error is the difference between a transition point of the ideal last output code and the actual last output code.

# 5.9 CTSU Characteristics

#### Table 5.57 CTSU Characteristics

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V}$ ,  $\text{T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                        | Symbol             | Min. | Тур. | Max. | Unit | Test Conditions                                     |

|---------------------------------------------|--------------------|------|------|------|------|-----------------------------------------------------|

| External capacitance connected to TSCAP pin | C <sub>tscap</sub> | 9    | 10   | 11   | nF   |                                                     |

| TS pin capacitive load                      | C <sub>base</sub>  | —    | —    | 50   | pF   |                                                     |

| Permissible output high current             | Σl <sub>OH</sub>   | _    | _    | -24  | mA   | When the mutual<br>capacitance method is<br>applied |

# 5.10 Characteristics of Power-On Reset Circuit and Voltage Detection Circuit

| Table 5.58  | Characteristics of Power-On Reset Circuit and Voltage Detection Circuit (1)                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conditions: | $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V}, \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$ |

| Item                       |                                                   | Symbol              | Min. | Тур. | Max. | Unit | Test Conditions                    |

|----------------------------|---------------------------------------------------|---------------------|------|------|------|------|------------------------------------|

| Voltage detection<br>level | Power-on reset (POR)                              | V <sub>POR</sub>    | 1.35 | 1.50 | 1.65 | V    | Figure 5.73, Figure 5.74           |

|                            | Voltage detection circuit<br>(LVD0)*1             | V <sub>det0_0</sub> | 3.67 | 3.84 | 3.97 | V    | Figure 5.75<br>At falling edge VCC |

|                            |                                                   | V <sub>det0_1</sub> | 2.70 | 2.82 | 3.00 |      |                                    |

|                            |                                                   | V <sub>det0_2</sub> | 2.37 | 2.51 | 2.67 |      |                                    |

|                            |                                                   | V <sub>det0_3</sub> | 1.80 | 1.90 | 1.99 |      |                                    |

|                            | Voltage detection circuit<br>(LVD1)*2             | V <sub>det1_0</sub> | 4.12 | 4.29 | 4.42 |      | Figure 5.76<br>At falling edge VCC |

|                            |                                                   | V <sub>det1_1</sub> | 3.98 | 4.14 | 4.28 |      |                                    |

|                            |                                                   | V <sub>det1_2</sub> | 3.86 | 4.02 | 4.16 |      |                                    |

|                            |                                                   | V <sub>det1_3</sub> | 3.68 | 3.84 | 3.98 |      |                                    |

|                            |                                                   | V <sub>det1_4</sub> | 2.99 | 3.10 | 3.29 |      |                                    |

|                            |                                                   | V <sub>det1_5</sub> | 2.89 | 3.00 | 3.19 |      |                                    |

|                            |                                                   | V <sub>det1_6</sub> | 2.79 | 2.90 | 3.09 |      |                                    |

|                            |                                                   | V <sub>det1_7</sub> | 2.68 | 2.79 | 2.98 |      |                                    |

|                            |                                                   | V <sub>det1_8</sub> | 2.57 | 2.68 | 2.87 |      |                                    |

|                            |                                                   | V <sub>det1_9</sub> | 2.47 | 2.58 | 2.67 |      |                                    |

|                            |                                                   | V <sub>det1_A</sub> | 2.37 | 2.48 | 2.57 |      |                                    |

|                            |                                                   | $V_{det1_B}$        | 2.10 | 2.20 | 2.30 |      |                                    |

|                            |                                                   | V <sub>det1_C</sub> | 1.86 | 1.96 | 2.06 |      |                                    |

|                            |                                                   | V <sub>det1_D</sub> | 1.80 | 1.86 | 1.96 |      |                                    |

|                            | Voltage detection circuit<br>(LVD2)* <sup>3</sup> | V <sub>det2_0</sub> | 4.08 | 4.29 | 4.48 | V    | Figure 5.77<br>At falling edge VCC |

|                            |                                                   | V <sub>det2_1</sub> | 3.95 | 4.14 | 4.35 |      |                                    |

|                            |                                                   | V <sub>det2_2</sub> | 3.82 | 4.02 | 4.22 |      |                                    |

|                            |                                                   | V <sub>det2_3</sub> | 3.62 | 3.84 | 4.02 |      |                                    |

Note: These characteristics apply when noise is not superimposed on the power supply. When a setting is made so that the voltage detection level overlaps with that of the voltage detection circuit (LVD2), it cannot be specified which of LVD1 and LVD2 is used for voltage detection.

Note 1. n in the symbol Vdet0\_n denotes the value of the OFS1.VDSEL[1:0] bits.

Note 2. n in the symbol Vdet1\_n denotes the value of the LVDLVLR.LVD1LVL[3:0] bits.

Note 3. n in the symbol Vdet2\_n denotes the value of the LVDLVLR.LVD2LVL[1:0] bits.

# Table 5.59 Characteristics of Power-On Reset Circuit and Voltage Detection Circuit (2)

Conditions:  $1.8 \text{ V} \le \text{VCC0} = \text{VCC}_{\text{USB}} = \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V}, \text{ T}_{\text{a}} = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                                          |                                                                  | Symbol              | Min. | Тур. | Max. | Unit | Test Conditions                     |

|---------------------------------------------------------------|------------------------------------------------------------------|---------------------|------|------|------|------|-------------------------------------|

| Wait time after                                               | At normal startup*1                                              | t <sub>POR</sub>    | —    | 9.1  | —    | ms   | Figure 5.74                         |

| power-on reset cancellation                                   | During fast startup<br>time <sup>*2</sup>                        | t <sub>POR</sub>    | —    | 1.6  | —    |      |                                     |

| Wait time after<br>voltage monitoring 0<br>reset cancellation | Power-on voltage<br>monitoring 0 reset<br>disabled* <sup>1</sup> | t <sub>LVD0</sub>   | _    | 568  | _    | μs   | Figure 5.75                         |

|                                                               | Power-on voltage<br>monitoring 0 reset<br>enabled* <sup>2</sup>  |                     | _    | 100  | _    |      |                                     |

| Wait time after voltage monitoring 1 reset cancellation       |                                                                  | t <sub>LVD1</sub>   | —    | 100  | —    | μs   | Figure 5.76                         |

| Wait time after voltage monitoring 2 reset cancellation       |                                                                  | t <sub>LVD2</sub>   | —    | 100  | —    | μs   | Figure 5.77                         |

| Response delay time                                           |                                                                  | t <sub>det</sub>    | —    | _    | 350  | μs   | Figure 5.73                         |

| Minimum VCC down time*3                                       |                                                                  | t <sub>VOFF</sub>   | 350  | _    | —    | μs   | Figure 5.73, VCC = 1.0 V or above   |

| Power-on reset enable time                                    |                                                                  | t <sub>W(POR)</sub> | 1    | _    | —    | ms   | Figure 5.74, VCC = below 1.0<br>V   |

| LVD operation stabilization time (after LVD is enabled)       |                                                                  | $Td_{(E-A)}$        | _    | _    | 300  | μs   | Figure 5.76, Figure 5.77            |

| Hysteresis width (power-on rest (POR))                        |                                                                  | V <sub>PORH</sub>   | —    | 110  | —    | mV   |                                     |

| Hysteresis width (voltage detection circuit: LVD1 and LVD2)   |                                                                  | V <sub>LVH</sub>    | —    | 70   | —    | mV   | When Vdet1_0 to Vdet1_4 is selected |

|                                                               |                                                                  |                     | —    | 60   | —    |      | When Vdet1_5 to Vdet1_9 is selected |

|                                                               |                                                                  |                     | —    | 50   | —    |      | When Vdet1_A or Vdet1_B is selected |

|                                                               |                                                                  |                     | —    | 40   | —    |      | When Vdet1_C or Vdet1_D is selected |

|                                                               |                                                                  |                     | —    | 60   | —    | 1    | When LVD2 is selected               |

Note: These characteristics apply when noise is not superimposed on the power supply. When a setting is made so that the voltage detection level overlaps with that of the voltage detection circuit (LVD1), it cannot be specified which of LVD1 and LVD2 is used for voltage detection.

Note 1. When OFS1.(LVDAS, FASTSTUP) = 11b.

Note 2. When OFS1.(LVDAS, FASTSTUP)  $\neq$  11b.

Note 3. The minimum VCC down time indicates the time when VCC is below the minimum value of voltage detection levels  $V_{POR}$ ,  $V_{det0}$ ,  $V_{det1}$ , and  $V_{det2}$  for the POR/LVD.

# Appendix 1. Package Dimensions

Information on the latest version of the package dimensions or mountings has been displayed in "Packages" on Renesas Electronics Corporation website.

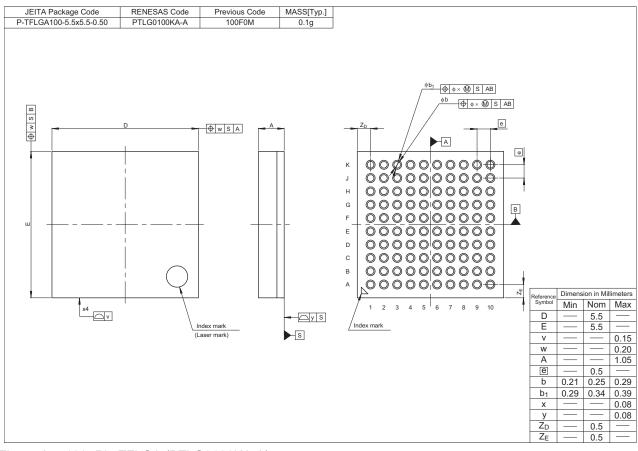

Figure A 100 -Pin TFLGA (PTLG0100KA-A)

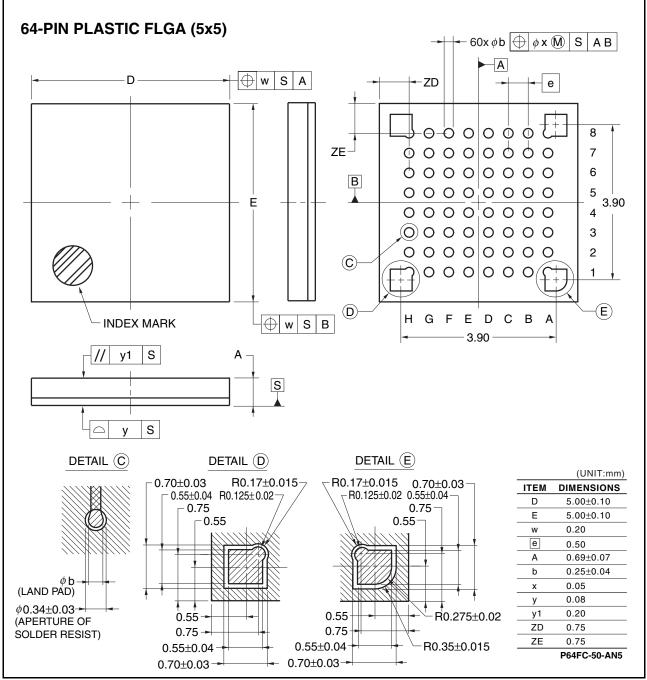

Figure C 64 -Pin WFLGA (PWLG0064KA-A)

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Handling of Unused Pins

Handle unused pins in accordance with the directions given under Handling of Unused Pins in the manual.

- <sup>3</sup>⁄<sub>4</sub> The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- <sup>3</sup>⁄<sub>4</sub> The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- <sup>3</sup>⁄<sub>4</sub> The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to a product with a different part number, confirm that the change will not lead to problems.

<sup>3</sup>⁄<sub>4</sub> The characteristics of Microprocessing unit or Microcontroller unit products in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.