Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RXv2                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 54MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, SCI, SD/SDIO, SPI, SSI, USB OTG                  |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 43                                                                               |

| Program Memory Size        | 384КВ (384К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-WFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-HWQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52317bdnd-u0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification           | Module/Function                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low power<br>consumption | Low power consumption<br>functions             | <ul> <li>Module stop function</li> <li>Three low power consumption modes</li> <li>Sleep mode, deep sleep mode, and software standby mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                          | Function for lower operating power consumption | <ul> <li>Low power timer that operates during the software standby state</li> <li>Operating power control modes         High-speed operating mode, middle-speed operating mode, and low-speed operating mode     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Interrupt                | Interrupt controller (ICUb)                    | <ul> <li>Interrupt vectors: 167</li> <li>External interrupts: 9 (NMI, IRQ0 to IRQ7 pins)</li> <li>Non-maskable interrupts: 7 (NMI pin, oscillation stop detection interrupt, voltage monitoring 1 interrupt, voltage monitoring 2 interrupt, WDT interrupt, IWDT interrupt, and VBATT power monitorin interrupt)</li> <li>16 levels specifiable for the order of priority</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| External bus exte        | nsion                                          | <ul> <li>The external address space can be divided into four areas (CS0 to CS3), each with independent control of access settings.</li> <li>Capacity of each area: 16 Mbytes (CS0 to CS3)</li> <li>A chip-select signal (CS0# to CS3#) can be output for each area.</li> <li>Each area is specifiable as an 8-bit or 16-bit bus space</li> <li>The data arrangement in each area is selectable as little or big endian (only for data).</li> <li>Bus format: Separate bus, multiplex bus</li> <li>Wait control</li> <li>Write buffer facility</li> </ul>                                                                                                                                                |

| DMA                      | DMA controller (DMACA)                         | <ul> <li>4 channels</li> <li>Three transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Software trigger, external interrupts, and interrupt requests from peripheral functions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          | Data transfer controller<br>(DTCa)             | <ul> <li>Transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Interrupts</li> <li>Chain transfer function</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O ports                | General I/O ports                              | 100-pin/64-pin/48-pin<br>I/O: 79/43/30 (RX231 Group), 83/47/34 (RX230 Group)<br>• Input: 1/1/1<br>Pull-up resistors: 79/43/30(RX231 Group), 83/47/34 (RX230 Group)<br>• Open-drain outputs: 58/34/26<br>• 5-V tolerance: 8/5/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Event link control       | ler (ELC)                                      | <ul> <li>Event signals of 61 types can be directly connected to the module</li> <li>Operations of timer modules are selectable at event input</li> <li>Capable of event link operation for port B and port E</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Multi-function pin       | controller (MPC)                               | Capable of selecting the input/output function from multiple pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timers                   | 16-bit timer pulse unit<br>(TPUa)              | <ul> <li>(16 bits × 6 channels) × 1 unit</li> <li>Maximum of 16 pulse-input/output possible</li> <li>Select from among seven or eight counter-input clock signals for each channel</li> <li>Supports the input capture/output compare function</li> <li>Output of PWM waveforms in up to 15 phases in PWM mode</li> <li>Support for buffered operation, phase-counting mode (two-phase encoder input) and cascade connected operation (32 bits × 2 channels) depending on the channel.</li> <li>Capable of generating conversion start triggers for the A/D converters</li> <li>Signals from the input capture pins are input via a digital filter</li> <li>Clock frequency measuring method</li> </ul> |

|                          | Multi-function timer pulse<br>unit 2 (MTU2a)   | <ul> <li>(16 bits × 6 channels) × 1 unit</li> <li>Up to 16 pulse-input/output lines and three pulse-input lines are available based on the six 16-bit timer channels</li> <li>Select from among eight or seven counter-input clock signals for each channel (PCLK/1, PCLK/4, PCLK/16, PCLK/64, PCLK/256, PCLK/1024, MTCLKA, MTCLKB, MTCLKC, MTCLKD) other than channel 5, for which only four signals are available.</li> <li>Input capture function</li> <li>21 output compare/input capture registers</li> <li>Pulse output mode</li> <li>Reset synchronous PWM mode</li> <li>Phase-counting mode</li> <li>Capable of generating conversion start triggers for the A/D converter</li> </ul>           |

|                          | Port output enable 2<br>(POE2a)                | Controls the high-impedance state of the MTU's waveform output pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                          | Compare match timer<br>(CMT)                   | <ul> <li>(16 bits × 2 channels) × 2 units</li> <li>Select from among four clock signals (PCLK/8, PCLK/32, PCLK/128, PCLK/512)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | Watchdog timer (WDTA)                          | <ul> <li>14 bits x 1 channel</li> <li>Select from among six counter-input clock signals (PCLK/4, PCLK/64, PCLK/128, PCLK/512, PCLK 2048, PCLK/8192)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## Table 1.1Outline of Specifications (2/4)

| Group | Part No.     | Order Part No.  | Package      | ROM<br>Capacity | RAM<br>Capacity | E2<br>DataFlash | Operating<br>Frequency | Security<br>Function | SDHI             | CAN              | Operating<br>Temperature |

|-------|--------------|-----------------|--------------|-----------------|-----------------|-----------------|------------------------|----------------------|------------------|------------------|--------------------------|

| RX231 | R5F52316ADFL | R5F52316ADFL#30 | PLQP0048KB-B | 256 Kbytes      | 32 Kbytes       | 8 Kbytes        | 54 MHz                 | Not<br>available     | Not<br>available | Available        | –40 to +85°C             |

|       | R5F52316CDFL | R5F52316CDFL#30 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52315ADLA | R5F52315ADLA#20 | PTLG0100KA-A | 128 Kbytes      | 32 Kbytes       | 8 Kbytes        | 54 MHz                 | Not<br>available     | Not<br>available | Available        | -40 to +85°C             |

|       | R5F52315CDLA | R5F52315CDLA#20 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52315ADFP | R5F52315ADFP#30 | PLQP0100KB-B |                 |                 |                 |                        | Not<br>available     | Not<br>available | Available        |                          |

|       | R5F52315CDFP | R5F52315CDFP#30 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52315CDLF | R5F52315CDLF#20 | PWLG0064KA-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52315ADND | R5F52315ADND#U0 | PWQN0064KC-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Available        | -                        |

|       | R5F52315CDND | R5F52315CDND#U0 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52315ADFM | R5F52315ADFM#30 | PLQP0064KB-C |                 |                 |                 |                        | Not<br>available     | Not<br>available | Available        | -                        |

|       | R5F52315CDFM | R5F52315CDFM#30 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52315ADNE | R5F52315ADNE#U0 | PWQN0048KB-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Available        |                          |

|       | R5F52315CDNE | R5F52315CDNE#U0 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52315ADFL | R5F52315ADFL#30 | PLQP0048KB-B |                 |                 |                 |                        | Not<br>available     | Not<br>available | Available        |                          |

|       | R5F52315CDFL | R5F52315CDFL#30 |              |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

| RX230 | R5F52306ADLA | R5F52306ADLA#20 | PTLG0100KA-A | 256 Kbytes      | 32 Kbytes       | 8 Kbytes        | 54 MHz                 | Not<br>available     | Not<br>available | Not<br>available | -40 to +85°C             |

|       | R5F52306ADFP | R5F52306ADFP#30 | PLQP0100KB-B |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52306ADLF | R5F52306ADLF#20 | PWLG0064KA-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52306ADND | R5F52306ADND#U0 | PWQN0064KC-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52306ADFM | R5F52306ADFM#30 | PLQP0064KB-C |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52306ADNE | R5F52306ADNE#U0 | PWQN0048KB-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52306ADFL | R5F52306ADFL#30 | PLQP0048KB-B |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52305ADLA | R5F52305ADLA#20 | PTLG0100KA-A | 128 Kbytes      |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52305ADFP | R5F52305ADFP#30 | PLQP0100KB-B |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | -                        |

|       | R5F52305ADLF | R5F52305ADLF#20 | PWLG0064KA-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52305ADND | R5F52305ADND#U0 | PWQN0064KC-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52305ADFM | R5F52305ADFM#30 | PLQP0064KB-C |                 |                 |                 | Not<br>available       | Not<br>available     | Not<br>available |                  |                          |

|       | R5F52305ADNE | R5F52305ADNE#U0 | PWQN0048KB-A |                 |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available |                          |

|       | R5F52305ADFL | R5F52305ADFL#30 | PLQP0048KB-B | 1               |                 |                 |                        | Not<br>available     | Not<br>available | Not<br>available | 1                        |

Table 1.3List of Products: D Version ( $T_a = -40$  to +85°C) (2/2)

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port   | External Bus        | Timers<br>(MTU, TPU, TMR, RTC,<br>CMT, POE, CAC) | Communications<br>(SCI, RSPI, RIIC, RSCAN,<br>USB, SSI) | Memory<br>Interface<br>(SDHI) | Touch<br>sensing | Others                              |

|------------|-------------------------------------------|------------|---------------------|--------------------------------------------------|---------------------------------------------------------|-------------------------------|------------------|-------------------------------------|

| 42         |                                           | P52        | RD#                 |                                                  |                                                         |                               | TS18             |                                     |

| 43         |                                           | P51        | WR1#/BC1#/<br>WAIT# |                                                  |                                                         |                               | TS19             |                                     |

| 44         |                                           | P50        | WR0#/WR#            |                                                  |                                                         |                               | TS20             |                                     |

| 45         | UB                                        | PC7        | A23/CS0#            | MTIOC3A/MTCLKB/TMO2                              | TXD8/SMOSI8/SSDA8/<br>MISOA                             |                               |                  | CACREF                              |

| 46         |                                           | PC6        | A22/CS1#            | MTIOC3C/MTCLKA/TMCI2                             | RXD8/SMISO8/SSCL8/<br>MOSIA                             |                               | TS22             |                                     |

| 47         |                                           | PC5        | A21/CS2#/<br>WAIT#  | MTIOC3B/MTCLKD/TMRI2                             | SCK8/RSPCKA                                             |                               | TS23             |                                     |

| 48         |                                           | PC4        | A20/CS3#            | MTIOC3D/MTCLKC/TMCI1/<br>POE0#                   | SCK5/CTS8#/RTS8#/<br>SS8#/SSLA0                         | SDHI_D1                       | TSCAP            |                                     |

| 49         |                                           | PC3        | A19                 | MTIOC4D/TCLKB                                    | TXD5/SMOSI5/SSDA5/<br>IRTXD5                            | SDHI_D0                       | TS27             |                                     |

| 50         |                                           | PC2        | A18                 | MTIOC4B/TCLKA                                    | RXD5/SMISO5/SSCL5/<br>SSLA3/ IRRXD5                     | SDHI_D3                       | TS30             |                                     |

| 51         |                                           | PC1        | A17                 | MTIOC3A/TCLKD                                    | SCK5/SSLA2                                              |                               | TS33             |                                     |

| 52         |                                           | PC0        | A16                 | MTIOC3C/TCLKC                                    | CTS5#/RTS5#/SS5#/<br>SSLA1                              |                               | TS35             |                                     |

| 53         |                                           | PB7        | A15                 | MTIOC3B/TIOCB5                                   | TXD9/SMOSI9/SSDA9                                       | SDHI_D2                       |                  |                                     |

| 54         |                                           | PB6        | A14                 | MTIOC3D/TIOCA5                                   | RXD9/SMISO9/SSCL9                                       | SDHI_D1                       |                  |                                     |

| 55         |                                           | PB5        | A13                 | MTIOC2A/MTIOC1B/<br>TMRI1/POE1#/TIOCB4           | SCK9/USB0_VBUS                                          | SDHI_CD                       |                  |                                     |

| 56         |                                           | PB4        | A12                 | TIOCA4                                           | CTS9#/RTS9#/SS9#                                        |                               |                  |                                     |

| 57         |                                           | PB3        | A11                 | MTIOC0A/MTIOC4A/TMO0/<br>POE3#/TIOCD3/TCLKD      | SCK6                                                    | SDHI_W<br>P                   |                  |                                     |

| 58         |                                           | PB2        | A10                 | TIOCC3/TCLKC                                     | CTS6#/RTS6#/SS6#                                        |                               |                  |                                     |

| 59         |                                           | PB1        | A9                  | MTIOC0C/MTIOC4C/<br>TMCI0/TIOCB3                 | TXD6/SMOSI6/SSDA6                                       | SDHI_CL<br>K                  |                  | IRQ4/<br>CMPOB1                     |

| 60         | VCC                                       |            |                     |                                                  |                                                         |                               |                  |                                     |

| 61         |                                           | PB0        | A8                  | MTIC5W/TIOCA3                                    | RXD6/SMISO6/SSCL6/<br>RSPCKA                            | SDHI_C<br>MD                  |                  |                                     |

| 62         | VSS                                       |            |                     |                                                  |                                                         |                               |                  |                                     |

| 63         |                                           | PA7        | A7                  | TIOCB2                                           | MISOA                                                   |                               |                  |                                     |

| 64         |                                           | PA6        | A6                  | MTIC5V/MTCLKB/TMCI3/<br>POE2#/TIOCA2             | CTS5#/RTS5#/SS5#/<br>MOSIA/SSIWS0                       |                               |                  |                                     |

| 65         |                                           | PA5        | A5                  | TIOCB1                                           | RSPCKA                                                  |                               |                  |                                     |

| 66         |                                           | PA4        | A4                  | MTIC5U/MTCLKA/TMRI0/<br>TIOCA1                   | TXD5/SMOSI5/SSDA5/<br>SSLA0/SSITXD0/IRTXD5              |                               |                  | IRQ5 /<br>CVREFB1                   |

| 67         |                                           | PA3        | A3                  | MTIOC0D/MTCLKD/<br>TIOCD0/TCLKB                  | RXD5/SMISO5/SSCL5/<br>SSIRXD0/IRRXD5                    |                               |                  | IRQ6 /CMPB <sup>*</sup>             |

| 68         |                                           | PA2        | A2                  |                                                  | RXD5/SMISO5/SSCL5/<br>SSLA3/IRRXD5                      |                               |                  |                                     |

| 69         |                                           | PA1        | A1                  | MTIOC0B/MTCLKC/<br>TIOCB0                        | SCK5/SSLA2/SSISCK0                                      |                               |                  | 040055                              |

| 70<br>71   |                                           | PA0        | A0/BC0#             | MTIOC4A/TIOCA0                                   | SSLA1                                                   |                               |                  | CACREF                              |

| 71<br>72   |                                           | PE7<br>PE6 | D15[A15/D15]        |                                                  |                                                         |                               |                  | IRQ7/AN023<br>IRQ6/AN022            |

| 72         |                                           | PE5        | D13[A13/D13]        | MTIOC4C/MTIOC2B                                  |                                                         |                               |                  | IRQ5/AN022<br>IRQ5/AN021/<br>CMPOB0 |

| 74         |                                           | PE4        | D12[A12/D12]        | MTIOC4D/MTIOC1A                                  |                                                         |                               |                  | AN020/<br>CMPA2/<br>CLKOUT          |

| 75         |                                           | PE3        | D11[A11/D11]        | MTIOC4B/POE8#                                    | CTS12#/RTS12#/SS12#/<br>AUDIO_MCLK                      |                               |                  | AN019/<br>CLKOUT                    |

| 76         |                                           | PE2        | D10[A10/D10]        | MTIOC4A                                          | RXD12/RXDX12/<br>SMISO12/SSCL12                         |                               |                  | IRQ7/AN018/<br>CVREFB0              |

| 77         |                                           | PE1        | D9[A9/D9]           | MTIOC4C                                          | TXD12/TXDX12/SIOX12/<br>SMOSI12/SSDA12                  |                               |                  | AN017/<br>CMPB0                     |

| 78         |                                           | PE0        | D8[A8/D8]           |                                                  | SCK12                                                   |                               |                  | AN016                               |

Table 1.7

List of Pins and Pin Functions (100-Pin LFQFP) (2/3)

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TPU, TMR, RTC, CMT,<br>POE, CAC) | Communications<br>(SCI, RSPI, RIIC, RSCAN, USB,<br>SSI)                    | Memory<br>Interface<br>(SDHI) | Touch<br>sensing | Others                    |

|------------|-------------------------------------------|----------|--------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|------------------|---------------------------|

| A1         |                                           | P05      |                                                  |                                                                            |                               |                  | DA1                       |

| 42         | AVCC0                                     |          |                                                  |                                                                            |                               |                  |                           |

| 43         | VREFH0                                    |          |                                                  |                                                                            |                               |                  |                           |

| 44         | VREFL0                                    |          |                                                  |                                                                            |                               |                  |                           |

| A5         | VREFH                                     |          |                                                  |                                                                            |                               |                  |                           |

| A6         | VREFL                                     |          |                                                  |                                                                            |                               |                  |                           |

| A7         |                                           | PE2      | MTIOC4A                                          | RXD12/RXDX12/SMISO12/<br>SSCL12                                            |                               |                  | IRQ7/AN018/<br>CVREFB0    |

| 48         |                                           | PE3      | MTIOC4B/POE8#                                    | CTS12#/RTS12#/SS12#/<br>AUDIO_MCLK                                         |                               |                  | AN019/CLKOUT              |

| 31         | VCL                                       |          |                                                  |                                                                            |                               |                  |                           |

| 32         | AVSS0                                     |          |                                                  |                                                                            |                               |                  |                           |

| 33         |                                           | P40      |                                                  |                                                                            |                               |                  | AN000                     |

| 34         |                                           | P42      |                                                  |                                                                            |                               |                  | AN002                     |

| 35         |                                           | P44      |                                                  |                                                                            |                               |                  | AN004                     |

| B6         |                                           | P46      |                                                  |                                                                            |                               |                  | AN006                     |

| B7         |                                           | PE1      | MTIOC4C                                          | TXD12/TXDX12/SIOX12/<br>SMOSI12/SSDA12                                     |                               |                  | AN017/CMPB0               |

| B8         |                                           | PE4      | MTIOC4D/MTIOC1A                                  |                                                                            |                               |                  | AN020/CMPA2/<br>CLKOUT    |

| C1         | XCIN                                      |          |                                                  |                                                                            |                               |                  |                           |

| C2         | MD                                        |          |                                                  |                                                                            |                               |                  | FINED                     |

| 23         |                                           | P03      |                                                  |                                                                            |                               |                  | DA0                       |

| 24         |                                           | P41      |                                                  |                                                                            |                               |                  | AN001                     |

| C5         |                                           | P43      |                                                  |                                                                            |                               |                  | AN003                     |

| 26         |                                           | PE0      |                                                  | SCK12                                                                      |                               |                  | AN016                     |

| C7         |                                           | PE5      | MTIOC4C/MTIOC2B                                  |                                                                            |                               |                  | IRQ5/AN021/<br>CMPOB0     |

| C8         |                                           | PA0      | MTIOC4A/TIOCA0                                   | SSLA1                                                                      |                               |                  | CACREF                    |

| D1         | XCOUT                                     |          |                                                  |                                                                            |                               |                  |                           |

| D2         | RES#                                      |          |                                                  |                                                                            |                               |                  |                           |

| D3         |                                           | P27      | MTIOC2B/TMCI3                                    | SCK1/ SSIWS0                                                               |                               | TS2              | CVREFB3                   |

| D4         |                                           | P14      | MTIOC3A/MTCLKA/TMRI2/<br>TIOCB5/TCLKA            | CTS1#/RTS1#/SS1#/CTXD0/<br>USB0_OVRCURA                                    |                               | TS13             | IRQ4/CVREFB2              |

| D5         |                                           | PA6      | MTIC5V/MTCLKB/TMCI3/POE2#/<br>TIOCA2             | CTS5#/RTS5#/SS5#/MOSIA/<br>SSIWS0                                          |                               |                  |                           |

| D6         |                                           | PA4      | MTIC5U/MTCLKA/TMRI0/TIOCA1                       | TXD5/SMOSI5/SSDA5/SSLA0/<br>SSITXD0/IRTXD5                                 |                               |                  | IRQ5 /CVREFB <sup>2</sup> |

| D7         | 1                                         | PA1      | MTIOC0B/MTCLKC/TIOCB0                            | SCK5/SSLA2/SSISCK0                                                         |                               | 1                |                           |

| D8         |                                           | PA3      | MTIOC0D/MTCLKD/TIOCD0/<br>TCLKB                  | RXD5/SMISO5/SSCL5/SSIRXD0/<br>IRRXD5                                       |                               |                  | IRQ6 /CMPB1               |

| E1         | VSS                                       |          |                                                  |                                                                            |                               |                  |                           |

| E2         | VBATT                                     |          |                                                  |                                                                            |                               |                  |                           |

| E3         |                                           | P30      | MTIOC4B/TMRI3/POE8#/RTCIC0                       | RXD1/SMISO1/SSCL1/<br>AUDIO_MCLK                                           |                               |                  | IRQ0/CMPOB3               |

| Ξ4         |                                           | P16      | MTIOC3C/MTIOC3D/TMO2/<br>TIOCB1/TCLKC/RTCOUT     | TXD1/SMOSI1/SSDA1/MOSIA/<br>SCL/USB0_VBUS/<br>USB0_VBUSEN/<br>USB0_OVRCURB |                               |                  | IRQ6/ADTRG0#              |

| E5         |                                           | PC4      | MTIOC3D/MTCLKC/TMCI1/<br>POE0#                   | SCK5/CTS8#/RTS8#/SS8#/<br>SSLA0                                            | SDHI_D1                       | TSCAP            |                           |

| Ξ6         | VCC                                       | 1        |                                                  |                                                                            |                               | 1                |                           |

| E7         | VSS                                       | 1        |                                                  |                                                                            | ł                             | ł                |                           |

| E8         |                                           | PB0      | MTIC5W/TIOCA3                                    | RXD6/SMISO6/SSCL6/RSPCKA                                                   | SDHI_C<br>MD                  |                  |                           |

| F1         | VCC                                       |          |                                                  |                                                                            |                               | <u> </u>         |                           |

| -2         | UPSEL                                     | P35      |                                                  |                                                                            |                               |                  | NMI                       |

| F3         | 1                                         | P31      | MTIOC4D/TMCI2/RTCIC1                             | CTS1#/RTS1#/SS1#/SSISCK0                                                   |                               | 1                | IRQ1                      |

## Table 1.8 List of Pins and Pin Functions (64-Pin WFLGA) (1/2)

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port                                                                   | Timers<br>(MTU, TPU, TMR, RTC, CMT,<br>POE, CAC) | Communications<br>(SCI, RSPI, RIIC, RSCAN, USB,<br>SSI)                    | Memory<br>Interface<br>(SDHI) | Touch<br>sensing | Others       |

|------------|-------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|------------------|--------------|

|            |                                           | P03                                                                        |                                                  |                                                                            |                               |                  | DA0          |

|            | VCL                                       |                                                                            |                                                  |                                                                            |                               |                  |              |

|            | MD                                        |                                                                            |                                                  |                                                                            |                               |                  | FINED        |

|            | XCIN                                      |                                                                            |                                                  |                                                                            |                               |                  |              |

|            | XCOUT                                     |                                                                            |                                                  |                                                                            |                               |                  |              |

|            | RES#                                      |                                                                            |                                                  |                                                                            |                               |                  |              |

|            | XTAL                                      | P37                                                                        |                                                  |                                                                            |                               |                  |              |

| ;          | VSS                                       |                                                                            |                                                  |                                                                            |                               |                  |              |

| 1          | EXTAL                                     | P36                                                                        |                                                  |                                                                            |                               |                  |              |

| 0          | VCC                                       |                                                                            |                                                  |                                                                            |                               |                  |              |

| 1          | UPSEL                                     | P35                                                                        |                                                  |                                                                            |                               |                  | NMI          |

| 2          | VBATT                                     |                                                                            |                                                  |                                                                            |                               |                  |              |

| 3          |                                           | P31                                                                        | MTIOC4D/TMCI2/RTCIC1                             | CTS1#/RTS1#/SS1#/SSISCK0                                                   |                               |                  | IRQ1         |

| 4          |                                           | P30                                                                        | MTIOC4B/TMRI3/POE8#/RTCIC0                       | RXD1/SMISO1/SSCL1/<br>AUDIO MCLK                                           |                               |                  | IRQ0/CMPOB3  |

| 5          |                                           |                                                                            |                                                  | SCK1/SSIWS0                                                                |                               | TS2              | CVREFB3      |

| 6          |                                           | P26         MTIOC2A/TMO1         TXD1/SMOSI1/SSDA1/<br>USB0_VBUSEN/SSIRXD0 |                                                  |                                                                            | TS3                           | CMPB3            |              |

| 7          |                                           | P17 MTIOC3A/MTIOC3B/TMO1/<br>POE8#/TIOCB0/TCLKD SCK1/MISOA/SDA/SSITXD0     |                                                  |                                                                            |                               | IRQ7/ CMPOB2     |              |

| 18         |                                           | P16                                                                        | MTIOC3C/MTIOC3D/TMO2/<br>TIOCB1/TCLKC/RTCOUT     | TXD1/SMOSI1/SSDA1/MOSIA/<br>SCL/USB0_VBUS/<br>USB0_VBUSEN/<br>USB0_OVRCURB |                               |                  | IRQ6/ADTRG0  |

| 9          |                                           | P15 MTIOC0B/MTCLKB/TMCl2/<br>TIOCB2/TCLKB                                  |                                                  | RXD1/SMISO1/SSCL1/CRXD0                                                    |                               | TS12             | IRQ5/CMPB2   |

| 20         |                                           | P14                                                                        | MTIOC3A/MTCLKA/TMRI2/<br>TIOCB5/TCLKA            | CTS1#/RTS1#/SS1#/CTXD0/<br>USB0_OVRCURA                                    |                               | TS13             | IRQ4/CVREFB2 |

| 21         | VCC_USB*1                                 | PH3*1                                                                      | TMCI0*1                                          |                                                                            |                               |                  |              |

| 2          |                                           | PH2*1                                                                      | TMRI0*1                                          | USB0_DM*1                                                                  |                               |                  | IRQ1*1       |

| 3          |                                           | PH1*1                                                                      | TMO0*1                                           | USB0_DP*1                                                                  |                               |                  | IRQ0*1       |

| 4          | VSS_USB*1                                 | PH0*1                                                                      |                                                  |                                                                            |                               |                  | CACREF*1     |

| 5          |                                           | P55                                                                        | MTIOC4D/TMO3                                     | CRXD0                                                                      |                               | TS15             |              |

| 6          |                                           | P54                                                                        | MTIOC4B/TMCI1                                    | CTXD0                                                                      |                               | TS16             |              |

| 27         | UB                                        | PC7                                                                        | MTIOC3A/MTCLKB/TMO2                              | TXD8/SMOSI8/SSDA8/MISOA                                                    |                               |                  | CACREF       |

| 8          |                                           | PC6                                                                        | MTIOC3C/MTCLKA/TMCI2                             | RXD8/SMISO8/SSCL8/MOSIA/<br>USB0_EXICEN                                    |                               | TS22             |              |

| 9          |                                           | PC5                                                                        | MTIOC3B/MTCLKD/TMRI2                             | SCK8/RSPCKA/USB0_ID                                                        |                               | TS23             |              |

| 0          |                                           | PC4                                                                        | MTIOC3D/MTCLKC/TMCI1/<br>POE0#                   | SCK5/CTS8#/RTS8#/SS8#/<br>SSLA0                                            | SDHI_D1                       | TSCAP            |              |

| 1          |                                           | PC3                                                                        | MTIOC4D/TCLKB                                    | TXD5/SMOSI5/SSDA5/ IRTXD5                                                  | SDHI_D0                       | TS27             | 1            |

| 32         |                                           | PC2                                                                        | MTIOC4B/TCLKA                                    | RXD5/SMISO5/SSCL5/SSLA3/<br>IRRXD5                                         | SDHI_D3                       | TS30             |              |

| 3          |                                           | PB7/PC1                                                                    | MTIOC3B/TIOCB5                                   | TXD9/SMOSI9/SSDA9                                                          | SDHI_D2                       |                  |              |

| 4          | 1                                         | PB6/PC0                                                                    | MTIOC3D/TIOCA5                                   | RXD9/SMISO9/SSCL9                                                          | <br>SDHI_D1                   |                  |              |

| 5          |                                           | PB5                                                                        | MTIOC2A/MTIOC1B/TMRI1/<br>POE1#/TIOCB4           | SCK9/USB0_VBUS                                                             | SDHI_CD                       |                  |              |

| 6          |                                           | PB3                                                                        | MTIOC0A/MTIOC4A/TMO0/<br>POE3#/TIOCD3/TCLKD      | SCK6                                                                       | SDHI_W<br>P                   |                  |              |

| 37         |                                           | PB1                                                                        | MTIOC0C/MTIOC4C/TMCI0/<br>TIOCB3                 | TXD6/SMOSI6/SSDA6                                                          | SDHI_CL<br>K                  |                  | IRQ4/ CMPOB1 |

| 88         | VCC                                       | 1                                                                          |                                                  |                                                                            | 1                             | 1                | 1            |

| 9          |                                           | PB0                                                                        | MTIC5W/TIOCA3                                    | RXD6/SMISO6/SSCL6/RSPCKA                                                   | SDHI_C<br>MD                  |                  |              |

| 0          | VSS                                       |                                                                            |                                                  |                                                                            | 1                             |                  | 1            |

| 1          |                                           | PA6                                                                        | MTIC5V/MTCLKB/TMCI3/POE2#/<br>TIOCA2             | CTS5#/RTS5#/SS5#/MOSIA/<br>SSIWS0                                          | 1                             |                  |              |

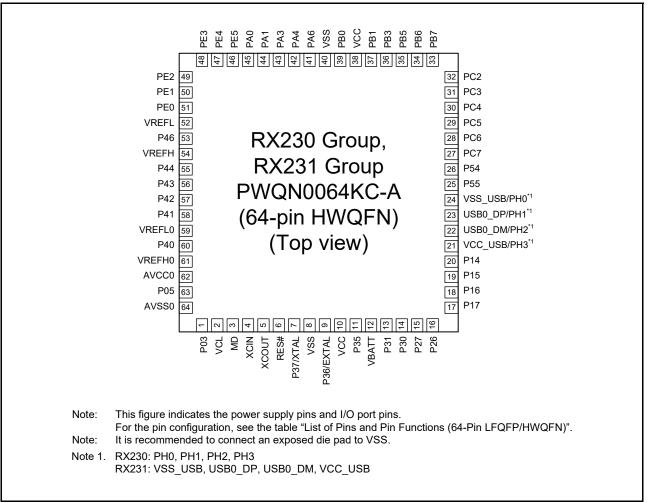

## Table 1.9 List of Pins and Pin Functions (64-Pin LFQFP/HWQFN) (1/2)

# 2. CPU

Figure 2.1 shows register set of the CPU.

|                | General-purpose register | Control register                       |

|----------------|--------------------------|----------------------------------------|

|                | b31 b0                   | b31 b                                  |

|                | R0 (SP) <sup>*1</sup>    | ISP (Interrupt stack pointer)          |

|                | R1                       | USP (User stack pointer)               |

|                | R2                       | INTR (Interrupt toble register)        |

|                | R3                       | INTB (Interrupt table register)        |

|                | R4                       | PC (Program counter)                   |

|                | R5                       |                                        |

|                | R6                       | PSW (Processor status word)            |

|                | R7                       | BPC (Backup PC)                        |

|                | R8                       |                                        |

|                | R9                       | BPSW (Backup PSW)                      |

|                | R10                      | FINTV (Fast interrupt vector register) |

|                | R11                      |                                        |

|                | R12                      | FPSW (Floating-point status word)      |

|                | R13                      | EXTB (Exception table register)        |

|                | R14                      |                                        |

|                | R15                      |                                        |

| DSP ins<br>p71 | truction register        | b                                      |

|                | ACC0 (Accumul            | ator 0)                                |

|                | ACC1 (Accumul            | ator 1)                                |

Figure 2.1 Register Set of the CPU

## Table 4.1 List of I/O Registers (Address Order) (26/33)

|           | Module |                                 | Register | Number  | Access | Number of Access Cycles            |                            |  |  |

|-----------|--------|---------------------------------|----------|---------|--------|------------------------------------|----------------------------|--|--|

| ddress    | Symbol | Register Name                   | Symbol   | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK <pclk< th=""></pclk<> |  |  |

| 00A 83DEh | RSCAN  | Receive Rule Entry Register 5AH | GAFLIDH5 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83DEh  | RSCAN  | Receive Buffer Register 3DH     | RMDF33   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83E0h  | RSCAN  | Receive Rule Entry Register 5BL | GAFLML5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E0h | RSCAN  | Receive Buffer Register 4AL     | RMIDL4   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E2h | RSCAN  | Receive Rule Entry Register 5BH | GAFLMH5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E2h | RSCAN  | Receive Buffer Register 4AH     | RMIDH4   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E4h | RSCAN  | Receive Rule Entry Register 5CL | GAFLPL5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E4h | RSCAN  | Receive Buffer Register 4BL     | RMTS4    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E6h | RSCAN  | Receive Rule Entry Register 5CH | GAFLPH5  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E6h | RSCAN  | Receive Buffer Register 4BH     | RMPTR4   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83E8h  | RSCAN  | Receive Rule Entry Register 6AL | GAFLIDL6 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83E8h | RSCAN  | Receive Buffer Register 4CL     | RMDF04   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83EAh | RSCAN  | Receive Rule Entry Register 6AH | GAFLIDH6 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83EAh  | RSCAN  | Receive Buffer Register 4CH     | RMDF14   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83ECh  | RSCAN  | Receive Rule Entry Register 6BL | GAFLML6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83ECh  | RSCAN  | Receive Buffer Register 4DL     | RMDF24   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83EEh | RSCAN  | Receive Rule Entry Register 6BH | GAFLMH6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83EEh | RSCAN  | Receive Buffer Register 4DH     | RMDF34   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F0h | RSCAN  | Receive Rule Entry Register 6CL | GAFLPL6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F0h | RSCAN  | Receive Buffer Register 5AL     | RMIDL5   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F2h | RSCAN  | Receive Rule Entry Register 6CH | GAFLPH6  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F2h | RSCAN  | Receive Buffer Register 5AH     | RMIDH5   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F4h | RSCAN  | Receive Rule Entry Register 7AL | GAFLIDL7 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F4h | RSCAN  | Receive Buffer Register 5BL     | RMTS5    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F6h | RSCAN  | Receive Rule Entry Register 7AH | GAFLIDH7 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F6h | RSCAN  | Receive Buffer Register 5BH     | RMPTR5   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F8h | RSCAN  | Receive Rule Entry Register 7BL | GAFLML7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83F8h | RSCAN  | Receive Buffer Register 5CL     | RMDF05   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83FAh | RSCAN  | Receive Rule Entry Register 7BH | GAFLMH7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83FAh | RSCAN  | Receive Buffer Register 5CH     | RMDF15   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83FCh | RSCAN  | Receive Rule Entry Register 7CL | GAFLPL7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 83FCh | RSCAN  | Receive Buffer Register 5DL     | RMDF25   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83FEh  | RSCAN  | Receive Rule Entry Register 7CH | GAFLPH7  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 83FEh  | RSCAN  | Receive Buffer Register 5DH     | RMDF35   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8400h | RSCAN  | Receive Rule Entry Register 8AL | GAFLIDL8 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8400h | RSCAN  | Receive Buffer Register 6AL     | RMIDL6   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8402h | RSCAN  | Receive Rule Entry Register 8AH | GAFLIDH8 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8402h | RSCAN  | Receive Buffer Register 6AH     | RMIDH6   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8404h | RSCAN  | Receive Rule Entry Register 8BL | GAFLML8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8404h | RSCAN  | Receive Buffer Register 6BL     | RMTS6    | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8406h | RSCAN  | Receive Rule Entry Register 8BH | GAFLMH8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8406h | RSCAN  | Receive Buffer Register 6BH     | RMPTR6   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 8408h | RSCAN  | Receive Rule Entry Register 8CL | GAFLPL8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 8408h  | RSCAN  | Receive Buffer Register 6CL     | RMDF06   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 840Ah  | RSCAN  | Receive Rule Entry Register 8CH | GAFLPH8  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 840Ah  | RSCAN  | Receive Buffer Register 6CH     | RMDF16   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 0A 840Ch  | RSCAN  | Receive Rule Entry Register 9AL | GAFLIDL9 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 840Ch | RSCAN  | Receive Buffer Register 6DL     | RMDF26   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 840Eh | RSCAN  | Receive Rule Entry Register 9AH | GAFLIDH9 | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

| 00A 840Eh | RSCAN  | Receive Buffer Register 6DH     | RMDF36   | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

|           |        | -                               |          |         |        |                                    | 2.0210                     |  |  |

| 0A 8410h  | RSCAN  | Receive Rule Entry Register 9BL | GAFLML9  | 16      | 16     | 2 or 3 PCLKB                       | 2 ICLK                     |  |  |

|                |                             | Iter                            | m                                                 |               | Symbol          | Тур.<br>*4 | Max. | Unit | Test<br>Conditions |

|----------------|-----------------------------|---------------------------------|---------------------------------------------------|---------------|-----------------|------------|------|------|--------------------|

| Supply current | Middle-speed operating mode | Normal operating mode           | All peripheral operation: Max.*7                  | ICLK = 12 MHz | I <sub>CC</sub> | _          | 16.7 | mA   |                    |

|                |                             | Sleep mode                      | No peripheral                                     | ICLK = 12 MHz |                 | 1.9        |      |      |                    |

|                |                             |                                 | operation* <sup>6</sup>                           | ICLK = 8 MHz  |                 | 1.2        |      |      |                    |

|                |                             |                                 |                                                   | ICLK = 4 MHz  |                 | 1.1        |      |      |                    |

|                |                             |                                 |                                                   | ICLK = 1 MHz  |                 | 1.0        | —    |      |                    |

|                |                             |                                 | All peripheral                                    | ICLK = 12 MHz |                 | 6.1        | —    |      |                    |

|                |                             |                                 | operation: Normal* <sup>7</sup>                   | ICLK = 8 MHz  |                 | 4.4        |      |      |                    |

|                |                             |                                 |                                                   | ICLK = 4 MHz  |                 | 3.0        |      |      |                    |

|                |                             |                                 |                                                   | ICLK = 1 MHz  |                 | 2.0        | —    |      |                    |

|                |                             | Deep sleep                      | No peripheral                                     | ICLK = 12 MHz |                 | 1.6        | —    |      |                    |

|                |                             | mode                            | operation* <sup>6</sup>                           | ICLK = 8 MHz  |                 | 1.0        | —    | -    |                    |

|                |                             |                                 |                                                   | ICLK = 4 MHz  |                 | 0.9        | —    |      |                    |

|                |                             |                                 |                                                   | ICLK = 1 MHz  |                 | 0.8        | —    |      |                    |

|                |                             |                                 | All peripheral                                    | ICLK = 12 MHz |                 | 5.1        | —    |      |                    |

|                |                             |                                 | operation: Normal* <sup>7</sup>                   | ICLK = 8 MHz  |                 | 3.7        |      |      |                    |

|                |                             |                                 |                                                   | ICLK = 4 MHz  |                 | 2.6        |      |      |                    |

|                |                             |                                 |                                                   | ICLK = 1 MHz  |                 | 1.8        |      |      |                    |

|                |                             | Increase during BGO operation*5 |                                                   |               |                 | 2.5        |      |      |                    |

|                | Low-speed<br>operating mode |                                 | No peripheral operation* <sup>8</sup>             | ICLK = 32 kHz | I <sub>CC</sub> | 5.2        |      | μA   |                    |

|                |                             |                                 | All peripheral<br>operation: Normal<br>*9, *10    | ICLK = 32 kHz |                 | 22.3       | _    | -    |                    |

|                |                             |                                 | All peripheral operation: Max.* <sup>9, *10</sup> | ICLK = 32 kHz |                 | —          | 74.4 |      |                    |

|                |                             | Sleep mode                      | No peripheral operation* <sup>8</sup>             | ICLK = 32 kHz |                 | 3.0        |      |      |                    |

|                |                             | Deep sleep<br>mode              | All peripheral operation: Normal* <sup>9</sup>    | ICLK = 32 kHz |                 | 13.1       | _    |      |                    |

|                |                             |                                 | No peripheral operation* <sup>8</sup>             | ICLK = 32 kHz |                 | 2.4        |      |      |                    |

|                |                             |                                 | All peripheral operation: Normal* <sup>9</sup>    | ICLK = 32 kHz |                 | 10.5       | _    |      |                    |

Note 1. Supply current values do not include the output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL. BCLK, FCLK, and PCLK are set to divided by 64.

Note 4. Values when VCC is 3.3 V.

Note 5. This is the increase when data is programmed to or erased from the ROM or E2 DataFlash during program execution.

Note 6. Clock supply to the peripheral functions is stopped. The clock source is PLL when ICLK is 12 MHz and HOCO for other cases. BCLK, FCLK, and PCLK are set to divided by 64.

Note 7. Clocks are supplied to the peripheral functions. The clock source is PLL when ICLK is 12 MHz and HOCO for other cases. BCLK, FCLK, and PCLK are the same frequency of that of the ICLK.

Note 8. Clock supply to the peripheral functions is stopped. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are set to divided by 64.