Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessorARM® Cortex®-M3Core Size32-Bit Single-CoreSpeed36MHzConnectivityIPC, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O26Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-Nudsize - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN (Ex6)Supplier Device Package36-VFQFN (Kc6) | betans                     |                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed36MHzConnectivityPC, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O26Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-Nutage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN (Exposed PadSupplier Device Package36-VFQFN (6x6)  | Product Status             | Active                                                                 |

| Speed36MHzConnectivityIPC, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O26Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFPN (6x6)                                                                               | Core Processor             | ARM® Cortex®-M3                                                        |

| ProductivityP2C, IrDA, LINbus, SPI, UART/USARTPeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O26Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed Pad                                                             | Core Size                  | 32-Bit Single-Core                                                     |

| PeripheralsDMA, PDR, POR, PVD, PWM, Temp Sensor, WDTNumber of I/O26Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFPN (6x6)                                                                                                                | Speed                      | 36MHz                                                                  |

| Number of I/O26Program Memory Size16KB (16K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K × 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN (6x6)                                                                                                                                                                     | Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFPN (6x6)                                                                                                                                        | Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                              |

| Program Memory TypeFLASHEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFNN (6x6)                                                                                                                                                                                                                    | Number of I/O              | 26                                                                     |

| EEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFPN (6x6)                                                                                                                                                                                                 | Program Memory Size        | 16KB (16K x 8)                                                         |

| RAM Size4K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFPN (6x6)                                                                                                                                                                                                             | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFN (6x6)                                                                                                                                                                                                                            | EEPROM Size                | -                                                                      |

| Data ConvertersA/D 10x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFPN (6x6)                                                                                                                                                                                                                                                              | RAM Size                   | 4K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFN (6x6)                                                                                                                                                                                                                                                                                        | Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-VFQFN Exposed PadSupplier Device Package36-VFQFN (6x6)                                                                                                                                                                                                                                                                                                               | Data Converters            | A/D 10x12b                                                             |

| Mounting Type     Surface Mount       Package / Case     36-VFQFN Exposed Pad       Supplier Device Package     36-VFQFN (6x6)                                                                                                                                                                                                                                                                                                                        | Oscillator Type            | Internal                                                               |

| Package / Case     36-VFQFN Exposed Pad       Supplier Device Package     36-VFQFPN (6x6)                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Supplier Device Package 36-VFQFPN (6x6)                                                                                                                                                                                                                                                                                                                                                                                                               | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Package / Case             | 36-VFQFN Exposed Pad                                                   |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101t4u6a                                                                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | 36-VFQFPN (6x6)                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101t4u6a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### STM32F101x4, STM32F101x6

| 4 | Memo   | ory map   | ping                                                   |

|---|--------|-----------|--------------------------------------------------------|

| 5 | Electr | rical cha | aracteristics                                          |

|   | 5.1    | Paramet   | ter conditions                                         |

|   |        | 5.1.1     | Minimum and maximum values                             |

|   |        | 5.1.2     | Typical values                                         |

|   |        | 5.1.3     | Typical curves                                         |

|   |        | 5.1.4     | Loading capacitor                                      |

|   |        | 5.1.5     | Pin input voltage                                      |

|   |        | 5.1.6     | Power supply scheme                                    |

|   |        | 5.1.7     | Current consumption measurement                        |

|   | 5.2    | Absolute  | e maximum ratings                                      |

|   | 5.3    | Operatir  | ng conditions                                          |

|   |        | 5.3.1     | General operating conditions                           |

|   |        | 5.3.2     | Operating conditions at power-up / power-down          |

|   |        | 5.3.3     | Embedded reset and power control block characteristics |

|   |        | 5.3.4     | Embedded reference voltage                             |

|   |        | 5.3.5     | Supply current characteristics                         |

|   |        | 5.3.6     | External clock source characteristics                  |

|   |        | 5.3.7     | Internal clock source characteristics                  |

|   |        | 5.3.8     | PLL characteristics                                    |

|   |        | 5.3.9     | Memory characteristics                                 |

|   |        | 5.3.10    | EMC characteristics                                    |

|   |        | 5.3.11    | Absolute maximum ratings (electrical sensitivity)51    |

|   |        | 5.3.12    | I/O current injection characteristics                  |

|   |        | 5.3.13    | I/O port characteristics                               |

|   |        | 5.3.14    | NRST pin characteristics                               |

|   |        | 5.3.15    | TIM timer characteristics                              |

|   |        | 5.3.16    | Communications interfaces                              |

|   |        | 5.3.17    | 12-bit ADC characteristics                             |

|   |        | 5.3.18    | Temperature sensor characteristics                     |

| 6 | Packa  | ige chai  | racteristics                                           |

|   | 6.1    | Package   | e mechanical data                                      |

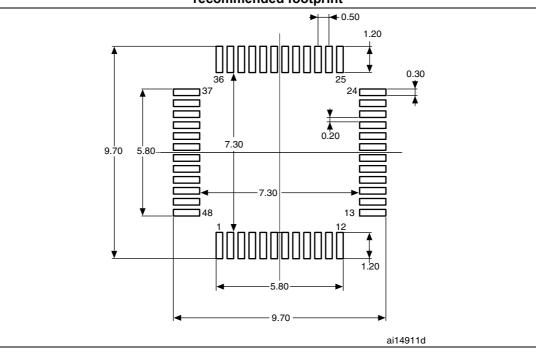

|   | 6.2    | VFQFP     | N36 package information                                |

|   | 6.3    | LQFP64    | package information                                    |

| Table 45. | TS characteristics                                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------|

| Table 46. | VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad flat package mechanical data |

| Table 47. | LQFP64 - 64-pin, 10 x 10 mm low-profile guad flat                                                      |

|           | package mechanical data                                                                                |

| Table 48. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                                                |

|           | mechanical data                                                                                        |

| Table 49. | Package thermal characteristics                                                                        |

| Table 50. | Ordering information scheme                                                                            |

| Table 51. | Document revision history                                                                              |

| Figure 40. | LQFP64 marking example (package top view)77                     |

|------------|-----------------------------------------------------------------|

| Figure 41. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline |

| Figure 42. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package         |

|            | recommended footprint                                           |

| Figure 43. | LQFP48 marking example (package top view)81                     |

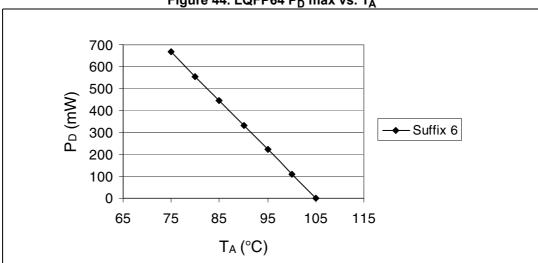

| Figure 44. | LQFP64 P <sub>D</sub> max vs. T <sub>A</sub>                    |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F101x4 and STM32F101x6 low-density access line microcontrollers. For more details on the whole STMicroelectronics STM32F101xx family, please refer to *Section 2.2: Full compatibility throughout the family*.

The Low-density STM32F101xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual. For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx Flash programming manual*. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

## 2 Description

The STM32F101x4 and STM32F101x6 Low-density access line family incorporates the high-performance ARM Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 36 MHz frequency, high-speed embedded memories (Flash memory of 16 to 32 Kbytes and SRAM of 4 to 6 Kbytes), and an extensive range of enhanced peripherals and I/Os connected to two APB buses. All devices offer standard communication interfaces (one I<sup>2</sup>C, one SPI, and two USARTs), one 12-bit ADC and up to two general-purpose 16-bit timers.

The STM32F101xx Low-density access line family operates in the –40 to +85 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F101xx Low-density access line family includes devices in three different packages ranging from 36 pins to 64 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F101xx Low-density access line microcontroller family suitable for a wide range of applications such as application control and user interface, medical and handheld equipment, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, Video intercoms, and HVACs.

## 2.2 Full compatibility throughout the family

The STM32F101xx is a complete family whose members are fully pin-to-pin, software and feature compatible. In the reference manual, the STM32F101x4 and STM32F101x6 are referred to as low-density devices, the STM32F101x8 and STM32F101xB are referred to as medium-density devices, and the STM32F101xC, STM32F101xD and STM32F101xE are referred to as high-density devices.

Low- and high-density devices are an extension of the STM32F101x8/B devices, they are specified in the STM32F101x4/6 and STM32F101xC/D/E datasheets, respectively. Low-density devices feature lower Flash memory and RAM capacities and a timer less. High-density devices have higher Flash memory and RAM capacities, and additional peripherals like FSMC and DAC, while remaining fully compatible with the other members of the STM32F101xx family.

The STM32F101x4, STM32F101x6, STM32F101xC, STM32F101xD and STM32F101xE are a drop-in replacement for the STM32F101x8/B medium-density devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.

Moreover, the STM32F101xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.

|        | Memory size                               |   |                                                 |       |                      |                                                                              |                 |  |  |

|--------|-------------------------------------------|---|-------------------------------------------------|-------|----------------------|------------------------------------------------------------------------------|-----------------|--|--|

|        | Low-density devices Medium-density device |   |                                                 |       | High-density devices |                                                                              |                 |  |  |

| Pinout | 16 KB32 KBFlashFlash(1)4 KB RAM6 KB RAM   |   | 64 KB<br>Flash128 KB<br>Flash10 KB RAM16 KB RAM |       | 256 KB<br>Flash      | 384 KB<br>Flash                                                              | 512 KB<br>Flash |  |  |

|        |                                           |   |                                                 |       | 32 KB<br>RAM         | 48 KB<br>RAM                                                                 | 48 KB<br>RAM    |  |  |

| 144    | -                                         | - | -                                               | -     | 5 × USARTs           |                                                                              |                 |  |  |

| 100    | -                                         | - | 3 × USARTs                                      |       |                      | × 16-bit timers, 2 × basic timers<br>× SPIs, 2 × I <sup>2</sup> Cs, 1 × ADC, |                 |  |  |

| 64     | 2 × USART                                 | - |                                                 |       |                      | 2 × DACs, FSMC (100 and 144                                                  |                 |  |  |

| 48     | 2 × 16-bit tii<br>1 × SPI, 1 ×            |   | 2 × SPIs, 2 ×<br>1 × ADC                        | I2Cs, | -                    | -                                                                            | -               |  |  |

| 36     | 1 × ADC                                   |   |                                                 |       | -                    | -                                                                            | -               |  |  |

Table 3. STM32F101xx family

1. For orderable part numbers that do not show the A internal code after the temperature range code (6), the reference datasheet for electrical characteristics is that of the STM32F101x8/B medium-density devices.

### 2.3.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

#### 2.3.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 36 MHz. See *Figure 2* for details on the clock tree.

#### 2.3.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

#### 2.3.9 Power supply schemes

- $V_{DD}$  = 2.0 to 3.6 V: External power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 2.0 to 3.6 V: External analog power supplies for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: Power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 10: Power supply scheme*.

#### 2.3.10 Power supply supervisor

The device has an integrated power on reset (POR)/power down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is

## 3 Pinouts and pin description

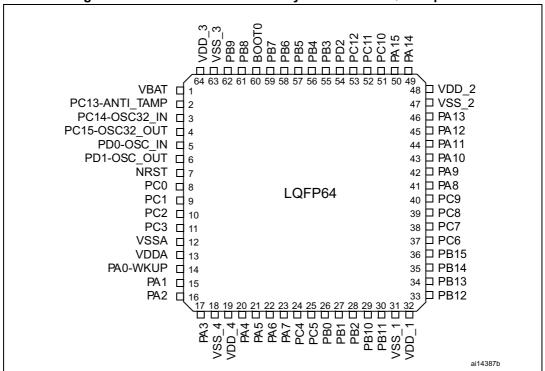

#### Figure 3. STM32F101xx Low-density access line LQFP64 pinout

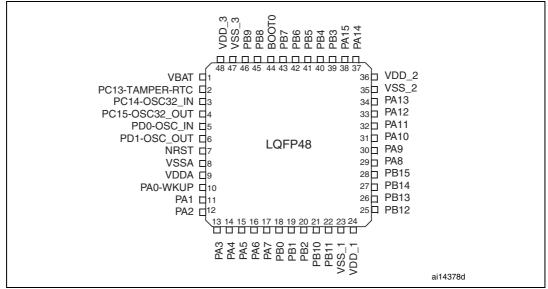

#### Figure 4. STM32F101xx Low-density access line LQFP48 pinout

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. This alternate function can be remapped by software to some other port pins (if available on the used package). For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- The pins number 2 and 3 in the VFQFPN36 package, and 5 and 6 in the LQFP48 and LQFP64 packages are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

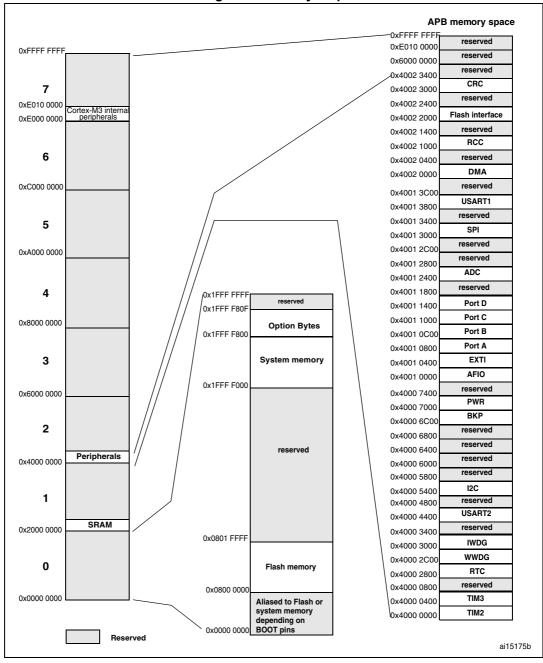

## 4 Memory mapping

The memory map is shown in Figure 7.

Figure 7. Memory map

| Symbol                               | Ratings                                                                                  | Max.  | Unit |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------|-------|------|--|--|--|

| I <sub>VDD</sub>                     | Total current into V <sub>DD</sub> /V <sub>DDA</sub> power lines (source) <sup>(1)</sup> | 150   |      |  |  |  |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>                         | 150   |      |  |  |  |

| Ι <sub>ΙΟ</sub>                      | Output current sunk by any I/O and control pin                                           | 25    |      |  |  |  |

|                                      | Output current source by any I/Os and control pin                                        | -25   | mA   |  |  |  |

| L (2)                                | Injected current on five volt tolerant pins <sup>(3)</sup>                               | -5/+0 |      |  |  |  |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                                         | ± 5   |      |  |  |  |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>                  | ± 25  |      |  |  |  |

#### Table 6. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 5.3.17: 12-bit ADC characteristics.

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 5: Voltage characteristics* for the maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 5: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 7. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

## 5.3 Operating conditions

#### 5.3.1 General operating conditions

#### Table 8. General operating conditions

| Symbol                          | Parameter                                  | Conditions                        | Min | Мах | Unit |

|---------------------------------|--------------------------------------------|-----------------------------------|-----|-----|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency               | -                                 | 0   | 36  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency              | -                                 | 0   | 36  | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency              | -                                 | 0   | 36  |      |

| V <sub>DD</sub>                 | Standard operating voltage                 | -                                 | 2   | 3.6 |      |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used) | Must be the same potential        | 2   | 3.6 | V    |

| VDDA <sup>(1)</sup>             | Analog operating voltage<br>(ADC used)     | as V <sub>DD</sub> <sup>(2)</sup> | 2.4 | 3.6 | v    |

| V <sub>BAT</sub>                | Backup operating voltage                   | -                                 | 1.8 | 3.6 |      |

| Symbol         | Parameter                                                  | Conditions                           | Min | Max  | Unit |  |  |

|----------------|------------------------------------------------------------|--------------------------------------|-----|------|------|--|--|

|                |                                                            | LQFP64                               | -   | 444  |      |  |  |

| P <sub>D</sub> | Power dissipation at T <sub>A</sub> = 85 °C <sup>(3)</sup> | LQFP48                               | -   | 363  | mW   |  |  |

|                |                                                            | VFQFPN36                             | -   | 1000 |      |  |  |

| Та             | Ambient temperature                                        | Maximum power dissipation            | -40 | 85   |      |  |  |

| IA             |                                                            | Low power dissipation <sup>(4)</sup> | -40 | 105  | °C   |  |  |

| TJ             | Junction temperature range                                 | -                                    | -40 | 105  |      |  |  |

Table 8. General operating conditions (continued)

1. When the ADC is used, refer to *Table 41: ADC characteristics*.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

3. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_J$ max (see *Table 6.5: Thermal characteristics on page 82*).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub>max (see Table 6.5: Thermal characteristics on page 82).

#### 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

| Symbol           | Parameter                         | Conditions | Min | Max | Unit  |  |

|------------------|-----------------------------------|------------|-----|-----|-------|--|

| t <sub>VDD</sub> | V <sub>DD</sub> rise time<br>rate | _          | 0   | 8   | µs/V  |  |

|                  | V <sub>DD</sub> fall time<br>rate |            | 20  | 8   | μ5/ ν |  |

Table 9. Operating conditions at power-up / power-down

#### 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 10* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                               | Parameter                                        | Conditions                  | Min                | Тур  | Max  | Unit |

|--------------------------------------|--------------------------------------------------|-----------------------------|--------------------|------|------|------|

|                                      |                                                  | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 |      |

|                                      |                                                  | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 |      |

|                                      |                                                  | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 |      |

|                                      |                                                  | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 |      |

|                                      |                                                  | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 |      |

|                                      |                                                  | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 |      |

|                                      |                                                  | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 |      |

| V <sub>PVD</sub>                     | Programmable voltage<br>detector level selection | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

|                                      |                                                  | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 |      |

|                                      |                                                  | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 |      |

|                                      |                                                  | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 |      |

|                                      |                                                  | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 |      |

|                                      |                                                  | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  |      |

|                                      |                                                  | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  |      |

|                                      |                                                  | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    |      |

|                                      |                                                  | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  |      |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                   | -                           | -                  | 100  | -    | mV   |

|                                      | Power on/power down                              | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| V <sub>POR/PDR</sub>                 | reset threshold                                  | Rising edge                 | 1.84               | 1.92 | 2.0  | v    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                   | -                           | -                  | 40   | -    | mV   |

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                              | -                           | 1.5                | 2.5  | 4.5  | ms   |

1. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

2. Guaranteed by design, not tested in production.

|                 |                                    |                                                                                                    |         | Typ <sup>(1)</sup>                        | Typ <sup>(1)</sup>       |      |  |

|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------|---------|-------------------------------------------|--------------------------|------|--|

| Symbol          | Parameter                          | Conditions                                                                                         | fhclk   | All peripherals<br>enabled <sup>(2)</sup> | All peripherals disabled | Unit |  |

|                 | Supply<br>current in<br>Sleep mode | External clock <sup>(3)</sup>                                                                      | 36 MHz  | 6.7                                       | 3.1                      |      |  |

|                 |                                    |                                                                                                    | 24 MHz  | 4.8                                       | 2.3                      |      |  |

|                 |                                    |                                                                                                    | 16 MHz  | 3.4                                       | 1.8                      |      |  |

|                 |                                    |                                                                                                    | 8 MHz   | 2                                         | 1.2                      |      |  |

|                 |                                    |                                                                                                    | 4 MHz   | 1.5                                       | 1.1                      |      |  |

|                 |                                    |                                                                                                    | 2 MHz   | 1.25                                      | 1                        |      |  |

|                 |                                    |                                                                                                    | 1 MHz   | 1.1                                       | 0.98                     | mA   |  |

|                 |                                    |                                                                                                    | 500 kHz | 1.05                                      | 0.96                     |      |  |

|                 |                                    |                                                                                                    | 125 kHz | 1                                         | 0.95                     |      |  |

| I <sub>DD</sub> |                                    | Running on High<br>Speed Internal RC<br>(HSI), AHB<br>prescaler used to<br>reduce the<br>frequency | 36 MHz  | 6.1                                       | 2.5                      |      |  |

|                 |                                    |                                                                                                    | 24 MHz  | 4.2                                       | 1.7                      |      |  |

|                 |                                    |                                                                                                    | 16 MHz  | 2.8                                       | 1.2                      |      |  |

|                 |                                    |                                                                                                    | 8 MHz   | 1.4                                       | 0.55                     |      |  |

|                 |                                    |                                                                                                    | 4 MHz   | 0.9                                       | 0.5                      |      |  |

|                 |                                    |                                                                                                    | 2 MHz   | 0.7                                       | 0.45                     |      |  |

|                 |                                    |                                                                                                    | 1 MHz   | 0.55                                      | 0.42                     |      |  |

|                 |                                    |                                                                                                    | 500 kHz | 0.48                                      | 0.4                      |      |  |

|                 |                                    |                                                                                                    | 125 kHz | 0.4                                       | 0.38                     |      |  |

| Table 17. Typical current consumption in Sleep mode, code running from Flash or |

|---------------------------------------------------------------------------------|

| RAM                                                                             |

1. Typical values are measures at T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 18*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 5.

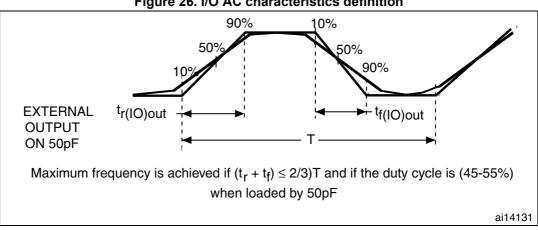

#### Figure 26. I/O AC characteristics definition

#### 5.3.14 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 33).

Unless otherwise specified, the parameters given in Table 36 are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 8.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |  |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|--|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | v    |  |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | v    |  |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                 | -    | 200 | -                    | mV   |  |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ   |  |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns   |  |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | _                 | 300  | -   | -                    | ns   |  |

Table 36. NRST pin characteristics

1. Guaranteed by design, not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to 2. the series resistance must be minimum (~10% order).

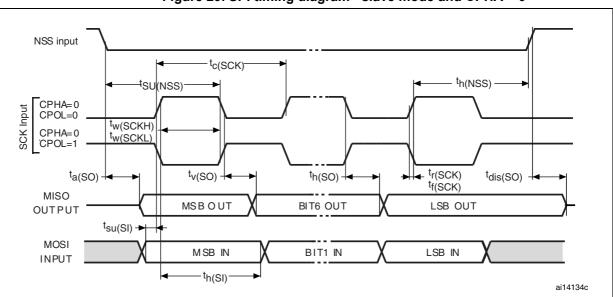

Figure 29. SPI timing diagram - slave mode and CPHA = 0

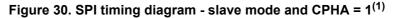

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

### 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 41* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 8*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                          | Conditions                                            | Min                                                                        | Тур | Мах               | Unit               |

|----------------------------------|----------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----|-------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                       | -                                                     | 2.4                                                                        | -   | 3.6               | V                  |

| f <sub>ADC</sub>                 | ADC clock frequency                                | -                                                     | 0.6                                                                        | -   | 14                | MHz                |

| f <sub>S</sub> <sup>(1)</sup>    | Sampling rate                                      | -                                                     | 0.043                                                                      | -   | 1                 | MHz                |

| f <sub>TRIG</sub> <sup>(1)</sup> | External trigger frequency                         | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -   | 823               | kHz                |

| ITRIG` ′                         | External ingger requercy                           | -                                                     | -                                                                          | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(2)</sup>            | -                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground)                | -   | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(1)</sup>  | External input impedance                           | See <i>Equation 1</i> and <i>Table 42</i> for details | -                                                                          | -   | 50                | κΩ                 |

| R <sub>ADC</sub> <sup>(1)</sup>  | Sampling switch resistance                         | -                                                     | -                                                                          | -   | 1                 | кΩ                 |

| C <sub>ADC</sub> <sup>(1)</sup>  | Internal sample and hold capacitor                 | -                                                     | -                                                                          | -   | 8                 | pF                 |

| + (1)                            | Calibration time                                   | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                                        |     |                   | μs                 |

| $t_{CAL}^{(1)}$                  |                                                    | -                                                     | 83                                                                         |     |                   | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (1)             | Injection trigger conversion                       | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -   | 0.214             | μs                 |

| <sup>u</sup> lat` '              | latency                                            | -                                                     | -                                                                          | -   | 3 <sup>(3)</sup>  | 1/f <sub>ADC</sub> |

| + (1)                            | Regular trigger conversion                         | f <sub>ADC</sub> = 14 MHz                             | -                                                                          | -   | 0.143             | μs                 |

| t <sub>latr</sub> <sup>(1)</sup> | latency                                            | -                                                     | -                                                                          | -   | 2 <sup>(3)</sup>  | 1/f <sub>ADC</sub> |

| ts <sup>(1)</sup>                | Sampling time                                      | f - 14 MU7                                            | 0.107                                                                      | -   | 17.1              | μs                 |

|                                  | Sampling une                                       | f <sub>ADC</sub> = 14 MHz                             | 1.5                                                                        | -   | 239.5             | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(1)</sup> | Stabilization time                                 | -                                                     | 14                                                                         |     |                   | 1/f <sub>ADC</sub> |

| t <sub>CONV</sub> <sup>(1)</sup> |                                                    | f <sub>ADC</sub> = 14 MHz                             | 1                                                                          | -   | 18                | μs                 |

|                                  | Total conversion time<br>(including sampling time) | -                                                     | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     |                   | 1/f <sub>ADC</sub> |

| Table | 41. | ADC | characteristics |

|-------|-----|-----|-----------------|

| Iabio |     |     |                 |

1. Guaranteed by design, not tested in production.

2.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is be internally connected to  $V_{SSA}$ .

3. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 41.

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol |             |       |       | inches ··             |        |        |  |

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| А      | 0.800       | 0.900 | 1.000 | 0.0315                | 0.0354 | 0.0394 |  |

| A1     | -           | 0.020 | 0.050 | -                     | 0.0008 | 0.0020 |  |

| A2     | -           | 0.650 | 1.000 | -                     | 0.0256 | 0.0394 |  |

| A3     | -           | 0.200 | -     | -                     | 0.0079 | -      |  |

| b      | 0.180       | 0.230 | 0.300 | 0.0071                | 0.0091 | 0.0118 |  |

| D      | 5.875       | 6.000 | 6.125 | 0.2313                | 0.2362 | 0.2411 |  |

| D2     | 1.750       | 3.700 | 4.250 | 0.0689                | 0.1457 | 0.1673 |  |

| Е      | 5.875       | 6.000 | 6.125 | 0.2313                | 0.2362 | 0.2411 |  |

| E2     | 1.750       | 3.700 | 4.250 | 0.0689                | 0.1457 | 0.1673 |  |

| е      | 0.450       | 0.500 | 0.550 | 0.0177                | 0.0197 | 0.0217 |  |

| L      | 0.350       | 0.550 | 0.750 | 0.0138                | 0.0217 | 0.0295 |  |

| К      | 0.250       | -     | -     | 0.0098                | -      | -      |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

# Table 46. VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitchquad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

#### 6.5.2 Evaluating the maximum junction temperature for an application

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in Table 50: Ordering information scheme.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature. Here, only temperature range 6 is available (-40 to 85 °C).

The following example shows how to calculate the temperature range needed for a given application, making it possible to check whether the required temperature range is compatible with the STM32F101xx junction temperature range.

#### Example: high-performance application

Assuming the following application conditions:

Maximum ambient temperature T<sub>Amax</sub> = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$  = 0.4 V and maximum 8 I/Os used at the same time in output mode at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax = 20</sub> × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 272 mW

P<sub>Dmax =</sub> 175 + 272 = 447 mW

Thus: P<sub>Dmax</sub> = 447 mW

Using the values obtained in Table 49  $T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.1 °C = 102.1 °C

This is within the junction temperature range of the STM32F101xx ( $-40 < T_J < 105 \text{ °C}$ ).

Figure 44. LQFP64 P<sub>D</sub> max vs. T<sub>A</sub>