Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2525-e-so |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

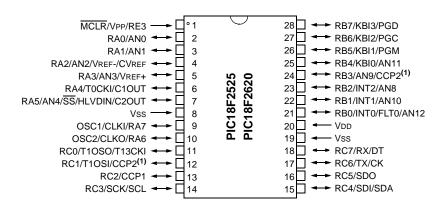

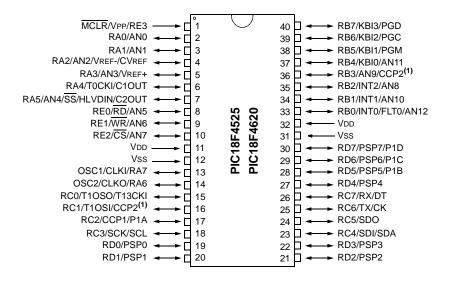

#### **Pin Diagrams**

#### 28-Pin SPDIP, SOIC

#### 40-Pin PDIP

Note 1: RB3 is the alternate pin for CCP2 multiplexing.

## 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval Tcsp following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

TABLE 3-2: EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE (BY CLOCK SOURCES)

| Clock Source<br>Before Wake-up | Clock Source<br>After Wake-up | Exit Delay                 | Clock Ready Status<br>Bit (OSCCON) |

|--------------------------------|-------------------------------|----------------------------|------------------------------------|

|                                | LP, XT, HS                    |                            |                                    |

| Primary Device Clock           | HSPLL                         | TCSD <sup>(1)</sup>        | OSTS                               |

| (PRI_IDLE mode)                | EC, RC                        | ICSD( )                    |                                    |

|                                | INTOSC <sup>(2)</sup>         |                            | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>        |                                    |

| T4000                          | HSPLL                         | Tost + t <sub>rc</sub> (3) | OSTS                               |

| T1OSC                          | EC, RC                        | Tcsp <sup>(1)</sup>        |                                    |

|                                | INTOSC <sup>(2)</sup>         | Tiobst <sup>(4)</sup>      | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>        |                                    |

| INTOSC <sup>(3)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> (3) | OSTS                               |

| INTOSC                         | EC, RC                        | Tcsp <sup>(1)</sup>        |                                    |

|                                | INTOSC <sup>(2)</sup>         | None                       | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>        |                                    |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> (3) | OSTS                               |

| (Sleep mode)                   | EC, RC                        | Tcsp <sup>(1)</sup>        |                                    |

|                                | INTOSC <sup>(2)</sup>         | Tiobst <sup>(4)</sup>      | IOFS                               |

- Note 1: TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see **Section 3.4 "Idle Modes"**). On Reset, INTOSC defaults to 1 MHz.

- 2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

- **3:** Tost is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

- 4: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2525/2620/4525/4620)

| File Name | Bit 7                                                                                                                                                                                                                       | Bit 6                                    | Bit 5           | Bit 4          | Bit 3          | Bit 2          | Bit 1            | Bit 0       | Value on  | Details on |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|----------------|----------------|----------------|------------------|-------------|-----------|------------|

|           | <b>Dit 7</b>                                                                                                                                                                                                                | Dit 0                                    | <b>D</b> it 0   |                |                |                | Dit 1            | Dit 0       | POR, BOR  | page:      |

| TOSU      | _                                                                                                                                                                                                                           | — — Top-of-Stack Upper Byte (TOS<20:16>) |                 |                |                |                |                  |             |           | 49, 54     |

| TOSH      | Top-of-Stack High Byte (TOS<15:8>)                                                                                                                                                                                          |                                          |                 |                |                |                |                  |             | 0000 0000 | 49, 54     |

| TOSL      |                                                                                                                                                                                                                             | Low Byte (TOS                            | S<7:0>)         | ı              | 1              | T              | T                | ı           | 0000 0000 | 49, 54     |

| STKPTR    | STKFUL <sup>(6)</sup>                                                                                                                                                                                                       | STKUNF <sup>(6)</sup>                    | _               | SP4            | SP3            | SP2            | SP1              | SP0         | 00-0 0000 | 49, 55     |

| PCLATU    | _                                                                                                                                                                                                                           | _                                        |                 | Holding Regi   | ster for PC<20 | ):16>          |                  |             | 0 0000    | 49, 54     |

| PCLATH    | Holding Regis                                                                                                                                                                                                               | ster for PC<15                           | :8>             |                |                |                |                  |             | 0000 0000 | 49, 54     |

| PCL       | PC Low Byte                                                                                                                                                                                                                 | (PC<7:0>)                                |                 |                |                |                |                  |             | 0000 0000 | 49, 54     |

| TBLPTRU   | 1                                                                                                                                                                                                                           |                                          | bit 21          | Program Mer    | mory Table Poi | inter Upper By | te (TBLPTR<20    | ):16>)      | 00 0000   | 49, 82     |

| TBLPTRH   | Program Men                                                                                                                                                                                                                 | nory Table Poi                           | nter High Byte  | (TBLPTR<15     | 5:8>)          |                |                  |             | 0000 0000 | 49, 82     |

| TBLPTRL   | Program Men                                                                                                                                                                                                                 | nory Table Poi                           | nter Low Byte   | (TBLPTR<7:0    | 0>)            |                |                  |             | 0000 0000 | 49, 82     |

| TABLAT    | Program Men                                                                                                                                                                                                                 | nory Table Lat                           | ch              |                |                |                |                  |             | 0000 0000 | 49, 82     |

| PRODH     | Product Regis                                                                                                                                                                                                               | ster High Byte                           |                 |                |                |                |                  |             | xxxx xxxx | 49, 89     |

| PRODL     | Product Regis                                                                                                                                                                                                               | ster Low Byte                            |                 |                |                |                |                  |             | xxxx xxxx | 49, 89     |

| INTCON    | GIE/GIEH                                                                                                                                                                                                                    | PEIE/GIEL                                | TMR0IE          | INT0IE         | RBIE           | TMR0IF         | INT0IF           | RBIF        | 0000 000x | 49, 111    |

| INTCON2   | RBPU                                                                                                                                                                                                                        | INTEDG0                                  | INTEDG1         | INTEDG2        | _              | TMR0IP         | _                | RBIP        | 1111 -1-1 | 49, 112    |

| INTCON3   | INT2IP                                                                                                                                                                                                                      | INT1IP                                   | _               | INT2IE         | INT1IE         | _              | INT2IF           | INT1IF      | 11-0 0-00 | 49, 113    |

| INDF0     | Uses content                                                                                                                                                                                                                | s of FSR0 to a                           | ddress data m   | nemory – valu  | e of FSR0 not  | changed (not   | a physical regis | ter)        | N/A       | 49, 68     |

| POSTINC0  | Uses contents of FSR0 to address data memory – value of FSR0 not changed (not a physical register)  N/A  Uses contents of FSR0 to address data memory – value of FSR0 post-incremented (not a physical register)  N/A       |                                          |                 |                |                |                |                  |             | 49, 68    |            |

| POSTDEC0  |                                                                                                                                                                                                                             |                                          |                 |                |                |                |                  | 49, 68      |           |            |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)                                                                                                                      |                                          |                 |                |                |                |                  | N/A         | 49, 68    |            |

| PLUSW0    | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W                                                                                          |                                          |                 |                |                |                |                  | N/A         | 49, 68    |            |

| FSR0H     | _                                                                                                                                                                                                                           | _                                        | _               | _              | Indirect Data  | Memory Addre   | ess Pointer 0 H  | igh Byte    | 0000      | 49, 68     |

| FSR0L     | Indirect Data                                                                                                                                                                                                               | Memory Addre                             | ess Pointer 0 I | Low Byte       | •              |                |                  |             | xxxx xxxx | 49, 68     |

| WREG      | Working Regi                                                                                                                                                                                                                | ster                                     |                 |                |                |                |                  |             | xxxx xxxx | 49         |

| INDF1     | Uses content                                                                                                                                                                                                                | s of FSR1 to a                           | ddress data m   | nemory – valu  | e of FSR1 not  | changed (not   | a physical regis | ter)        | N/A       | 49, 68     |

| POSTINC1  | Uses content                                                                                                                                                                                                                | s of FSR1 to a                           | ddress data m   | nemory – valu  | e of FSR1 pos  | t-incremented  | (not a physical  | register)   | N/A       | 49, 68     |

| POSTDEC1  | Uses content                                                                                                                                                                                                                | s of FSR1 to a                           | ddress data m   | nemory – valu  | e of FSR1 pos  | t-decremented  | d (not a physica | l register) | N/A       | 49, 68     |

| PREINC1   | Uses content                                                                                                                                                                                                                | s of FSR1 to a                           | ddress data m   | nemory – valu  | e of FSR1 pre- | incremented (  | not a physical r | egister)    | N/A       | 49, 68     |

| PLUSW1    | Uses content value of FSR                                                                                                                                                                                                   |                                          | ddress data m   | nemory – valu  | e of FSR1 pre- | -incremented ( | not a physical r | egister) –  | N/A       | 49, 68     |

| FSR1H     | -                                                                                                                                                                                                                           | _                                        | -               | _              | Indirect Data  | Memory Addre   | ess Pointer 1 H  | igh Byte    | 0000      | 50, 68     |

| FSR1L     | Indirect Data                                                                                                                                                                                                               | Memory Addre                             | ess Pointer 1 I | Low Byte       |                |                |                  |             | xxxx xxxx | 50, 68     |

| BSR       | _                                                                                                                                                                                                                           | _                                        | _               | _              | Bank Select F  | Register       |                  |             | 0000      | 50, 59     |

| INDF2     | Uses content                                                                                                                                                                                                                | s of FSR2 to a                           | ddress data m   | nemory – valu  | e of FSR2 not  | changed (not   | a physical regis | iter)       | N/A       | 50, 68     |

| POSTINC2  | Uses contents of FSR2 to address data memory – value of FSR2 post-incremented (not a physical register)  N/A                                                                                                                |                                          |                 |                |                |                |                  | 50, 68      |           |            |

| POSTDEC2  | Uses content                                                                                                                                                                                                                | s of FSR2 to a                           | ddress data m   | nemory – value | e of FSR2 pos  | t-decremented  | d (not a physica | l register) | N/A       | 50, 68     |

| PREINC2   | 2 Uses contents of FSR2 to address data memory – value of FSR2 post-decremented (not a physical register)  N/A  Uses contents of FSR2 to address data memory – value of FSR2 pre-incremented (not a physical register)  N/A |                                          |                 |                |                |                | 50, 68           |             |           |            |

| PLUSW2    |                                                                                                                                                                                                                             | s of FSR2 to a                           |                 |                |                |                | not a physical r |             | N/A       | 50, 68     |

| FSR2H     | _                                                                                                                                                                                                                           | _                                        | _               | _              | Indirect Data  | Memory Addre   | ess Pointer 2 H  | igh Byte    | 0000      | 50, 68     |

| FSR2L     | Indirect Data                                                                                                                                                                                                               | Memory Addre                             | ess Pointer 2 I | Low Byte       | •              |                |                  |             | xxxx xxxx | 50, 68     |

| STATUS    | _                                                                                                                                                                                                                           | _                                        | _               | N              | OV             | Z              | DC               | С           | x xxxx    | 50, 66     |

Legend:

- $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged, = unimplemented,  $\mathbf{q}$  = value depends on condition

- Note 1: The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

- 2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

- 3: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

- 4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

- 5: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

- **6:** Bit 7 and bit 6 are cleared by user software or by a POR.

#### TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7                                                    | Bit 6                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|-------|----------------------------------------------------------|---------------------------------------|-------|-------|-------|-------|-------|-------|----------------------------|

| PORTC | RC7                                                      | RC6                                   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | 52                         |

| LATC  | PORTC Data Latch Register (Read and Write to Data Latch) |                                       |       |       |       |       |       | 52    |                            |

| TRISC | PORTC Da                                                 | PORTC Data Direction Control Register |       |       |       |       |       |       | 52                         |

#### REGISTER 10-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| R/W-1  | R/W-1 | U-0 | R/W-1 | R/W-1 | R/W-1  | R/W-1  | R/W-1  |

|--------|-------|-----|-------|-------|--------|--------|--------|

| OSCFIP | CMIP  | _   | EEIP  | BCLIP | HLVDIP | TMR3IP | CCP2IP |

| bit 7  |       |     |       |       |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIP: Oscillator Fail Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6 CMIP: Comparator Interrupt Priority bit

1 = High priority0 = Low priority

bit 5 Unimplemented: Read as '0'

bit 4 **EEIP:** Data EEPROM/Flash Write Operation Interrupt Priority bit

1 = High priority0 = Low priority

bit 3 BCLIP: Bus Collision Interrupt Priority bit

1 = High priority0 = Low priority

bit 2 **HLVDIP:** High/Low-Voltage Detect Interrupt Priority bit

1 = High priority0 = Low priority

bit 1 TMR3IP: TMR3 Overflow Interrupt Priority bit

1 = High priority0 = Low priority

bit 0 CCP2IP: CCP2 Interrupt Priority bit

1 = High priority0 = Low priority

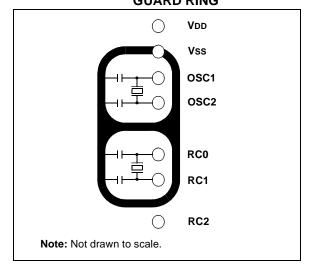

## 12.3.3 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 12-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator (such as the CCP1 pin in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit, as shown in Figure 12-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

FIGURE 12-4: OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

#### 12.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

# 12.5 Resetting Timer1 Using the CCP Special Event Trigger

If either of the CCP modules is configured to use Timer1 and generate a Special Event Trigger in Compare mode (CCP1M3:CCP1M0 or CCP2M3:CCP2M0 = 1011), this signal will reset Timer1. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 15.3.4 "Special Event Trigger"** for more information).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRH:CCPRL register pair effectively becomes a period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

**Note:** The Special Event Triggers from the CCP2 module will not set the TMR1IF interrupt flag bit (PIR1<0>).

#### 12.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 12.3** "Timer1 Oscillator" above) gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 12-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered. Doing so may introduce cumulative errors over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

The CCPR2H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP2 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### **EQUATION 15-3:**

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP2 pin will not be cleared.

#### TABLE 15-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

# 15.4.3 PWM AUTO-SHUTDOWN (CCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP module are also available to CCP1 in 28-pin devices. The operation of this feature is discussed in detail in **Section 16.4.7 "Enhanced PWM Auto-Shutdown"**.

Auto-shutdown features are not available for CCP2.

#### 15.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCPx module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPRxL register and CCPxCON<5:4> bits.

- Make the CCPx pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCPx module for PWM operation.

#### 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

**Note:** The ECCP module is implemented only in 40/44-pin devices.

In PIC18F4525/4620 devices, CCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The

Enhanced features are discussed in detail in **Section 16.4 "Enhanced PWM Mode"**. Capture, Compare and single-output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 16-1. It differs from the CCPxCON registers in PIC18F2525/2620 devices in that the two Most Significant bits are implemented to control PWM functionality.

#### REGISTER 16-1: CCP1CON: ECCP CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 7-6 P1M1:P1M0: Enhanced PWM Output Configuration bits

If CCP1M3:CCP1M2 = 00, 01, 10:

xx = P1A assigned as capture/compare input/output; P1B, P1C, P1D assigned as port pins

#### If CCP1M3:CCP1M2 = 11:

00 = Single output, P1A modulated; P1B, P1C, P1D assigned as port pins

01 = Full-bridge output forward, P1D modulated; P1A active; P1B, P1C inactive

10 = Half-bridge output, P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins

11 = Full-bridge output reverse, P1B modulated; P1C active; P1A, P1D inactive

#### bit 5-4 **DC1B1:DC1B0**: PWM Duty Cycle bit 1 and bit 0

Capture mode:

Unused.

Compare mode:

Unused.

#### PWM mode:

These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L.

#### bit 3-0 CCP1M3:CCP1M0: Enhanced CCP Mode Select bits

0000 = Capture/Compare/PWM off (resets ECCP module)

0001 = Reserved

0010 = Compare mode, toggle output on match

0011 = Capture mode

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge

1000 = Compare mode, initialize CCP1 pin low; set output on compare match (set CCP1IF)

1001 = Compare mode, initialize CCP1 pin high; clear output on compare match (set CCP1IF)

1010 = Compare mode, generate software interrupt only; CCP1 pin reverts to I/O state

1011 = Compare mode, trigger special event (ECCP resets TMR1 or TMR3, sets CCP1IF bit)

1100 = PWM mode, P1A, P1C active-high; P1B, P1D active-high

1101 = PWM mode, P1A, P1C active-high; P1B, P1D active-low

1110 = PWM mode, P1A, P1C active-low; P1B, P1D active-high

1111 = PWM mode, P1A, P1C active-low; P1B, P1D active-low

In addition to the expanded range of modes available through the CCP1CON and ECCP1AS registers, the ECCP module has an additional register associated with Enhanced PWM operation and auto-shutdown features; it is:

• PWM1CON (PWM Configuration)

#### **16.1** ECCP Outputs and Configuration

The Enhanced CCP module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated P1A through P1D, are multiplexed with I/O pins on PORTC and PORTD. The outputs that are active depend on the CCP operating mode selected. The pin assignments are summarized in Table 16-1.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the P1M1:P1M0 and CCP1M3:CCP1M0 bits. The appropriate TRISC and TRISD direction bits for the port pins must also be set as outputs.

# 16.1.1 ECCP MODULES AND TIMER RESOURCES

Like the standard CCP modules, the ECCP module can utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available for modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode. Interactions between the standard and Enhanced CCP modules are identical to those described for standard CCP modules. Additional details on timer resources are provided in Section 15.1.1 "CCP Modules and Timer Resources".

#### 16.2 Capture and Compare Modes

Except for the operation of the Special Event Trigger discussed below, the Capture and Compare modes of the ECCP module are identical in operation to that of CCP2. These are discussed in detail in **Section 15.2** "Capture Mode" and Section 15.3 "Compare Mode". No changes are required when moving between 28-pin and 40/44-pin devices.

#### 16.2.1 SPECIAL EVENT TRIGGER

The Special Event Trigger output of ECCP1 resets the TMR1 or TMR3 register pair, depending on which timer resource is currently selected. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1 or Timer3.

#### 16.3 Standard PWM Mode

When configured in Single Output mode, the ECCP module functions identically to the standard CCP module in PWM mode, as described in **Section 15.4** "**PWM Mode**". This is also sometimes referred to as "Compatible CCP" mode, as in Table 16-1.

Note: When setting up single output PWM operations, users are free to use either of the processes described in Section 15.4.4 "Setup for PWM Operation" or Section 16.4.9 "Setup for PWM Operation". The latter is more generic and will work for either single or multi-output PWM.

TABLE 16-1: PIN ASSIGNMENTS FOR VARIOUS ECCP1 MODES

| ECCP Mode              | CCP1CON<br>Configuration | RC2  | RD5      | RD6      | RD7      |  |  |

|------------------------|--------------------------|------|----------|----------|----------|--|--|

| All 40/44-pin devices: |                          |      |          |          |          |  |  |

| Compatible CCP         | 00xx 11xx                | CCP1 | RD5/PSP5 | RD6/PSP6 | RD7/PSP7 |  |  |

| Dual PWM               | 10xx 11xx                | P1A  | P1B      | RD6/PSP6 | RD7/PSP7 |  |  |

| Quad PWM               | x1xx 11xx                | P1A  | P1B      | P1C      | P1D      |  |  |

**Legend:** x = Don't care. Shaded cells indicate pin assignments not used by ECCP1 in a given mode.

## 16.4.6 PROGRAMMABLE DEAD-BAND DELAY

**Note:** Programmable dead-band delay is not implemented in 28-pin devices with standard CCP modules.

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (shoot-through current) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the nonactive state to the active state. See Figure 16-4 for illustration. Bits PDC6:PDC0 of the PWM1CON register (Register 16-2) set the delay period in terms of microcontroller instruction cycles (Tcy or 4 Tosc). These bits are not available on 28-pin devices as the standard CCP module does not support half-bridge operation.

#### 16.4.7 ENHANCED PWM AUTO-SHUTDOWN

When the CCP1 is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the comparator modules, a low level on the Fault input pin (FLT0) or any combination of these three sources. The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a low digital signal on FLT0 can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS2:ECCPAS0 bits (ECCP1AS<6:4>).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits (ECCP1AS<3:0>). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

#### REGISTER 16-2: PWM1CON: PWM CONFIGURATION REGISTER

| R/W-0 | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| PRSEN | PDC6 <sup>(1)</sup> | PDC5 <sup>(1)</sup> | PDC4 <sup>(1)</sup> | PDC3 <sup>(1)</sup> | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |

| bit 7 |                     |                     |                     |                     |                     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 PRSEN: PWM Restart Enable bit

1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically

0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM

bit 6-0 **PDC6:PDC0:** PWM Delay Count bits<sup>(1)</sup>

Delay time, in number of Fosc/4 (4 \* Tosc) cycles, between the scheduled and actual time for a PWM signal to transition to active.

Note 1: Unimplemented on 28-pin devices; bits read as '0'.

NOTES:

#### REGISTER 23-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0   | U-0 | U-0 | R/P-1                | R/P-1                | R/P-1                 | R/P-1                 | R/P-1                 |

|-------|-----|-----|----------------------|----------------------|-----------------------|-----------------------|-----------------------|

| _     | _   | _   | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BORENO <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7 |     |     |                      |                      |                       |                       | bit 0                 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7-5 **Unimplemented:** Read as '0'

bit 4-3 BORV1:BORV0: Brown-out Reset Voltage bits<sup>(1)</sup>

11 = Minimum setting

•

00 = Maximum setting

bit 2-1 BOREN1:BOREN0: Brown-out Reset Enable bits<sup>(2)</sup>

11 = Brown-out Reset enabled in hardware only (SBOREN is disabled)

10 = Brown-out Reset enabled in hardware only and disabled in Sleep mode (SBOREN is disabled)

01 = Brown-out Reset enabled and controlled by software (SBOREN is enabled)

00 = Brown-out Reset disabled in hardware and software

bit 0 **PWRTEN:** Power-up Timer Enable bit<sup>(2)</sup>

1 = PWRT disabled

0 = PWRT enabled

Note 1: See Section 26.1 "DC Characteristics: Supply Voltage" for specifications.

2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

| GOTO                                                | Unconditional Branch                                                                           |   |  |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------|---|--|--|

| Syntax:                                             | GOTO k                                                                                         | _ |  |  |

| Operands:                                           | $0 \leq k \leq 1048575$                                                                        |   |  |  |

| Operation:                                          | $k \rightarrow PC < 20:1 >$                                                                    |   |  |  |

| Status Affected:                                    | None                                                                                           |   |  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110 1111 k <sub>7</sub> kkk kkkk <sub>0</sub> 1111 k <sub>19</sub> kkk kkkk kkkk <sub>8</sub> |   |  |  |

| Description:                                        | GOTO allows an unconditional branch                                                            | _ |  |  |

anywhere within entire

2-Mbyte memory range. The 20-bit value 'k' is loaded into PC<20:1>. GOTO is always a two-cycle

instruction.

2 Words: Cycles: 2

Q Cycle Activity:

|   | Q1        | Q1 Q2        |           | Q4           |

|---|-----------|--------------|-----------|--------------|

|   | Decode    | Read literal | No        | Read literal |

|   |           | 'k'<7:0>,    | operation | 'k'<19:8>,   |

|   |           |              |           | Write to PC  |

|   | No        | No           | No        | No           |

| L | operation | operation    | operation | operation    |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

#### **INCF** Increment f

Syntax: INCF f {,d {,a}} Operands:  $0 \leq f \leq 255$  $d \in \left[0,1\right]$  $a \in \left[0,1\right]$

Operation: (f) + 1  $\rightarrow$  dest Status Affected: C, DC, N, OV, Z

Encoding: 0010 10da ffff ffff Description:

The contents of register 'f' are incremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 24.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details.

Words: Cycles:

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: INCF CNT, 1, 0

Before Instruction

CNT FFh

Z C ĎC

After Instruction

CNT Z C DC 00h

| SUBLW                                                            | Subtract W from Literal         |                                   |            |  |

|------------------------------------------------------------------|---------------------------------|-----------------------------------|------------|--|

| Syntax:                                                          | SUBLW                           | k                                 |            |  |

| Operands:                                                        | $0 \le k \le 25$                | $0 \leq k \leq 255$               |            |  |

| Operation:                                                       | $k - (W) \rightarrow$           | $k - (W) \rightarrow W$           |            |  |

| Status Affected:                                                 | N, OV, C,                       | DC, Z                             |            |  |

| Encoding:                                                        | 0000                            | 1000 kkl                          | kk kkkk    |  |

| Description                                                      |                                 | acted from the                    |            |  |

| Words:                                                           | 1                               |                                   |            |  |

| Cycles:                                                          | 1                               |                                   |            |  |

| Q Cycle Activity:                                                |                                 |                                   |            |  |

| Q1                                                               | Q2                              | Q3                                | Q4         |  |

| Decode                                                           | Read<br>literal 'k'             | Process<br>Data                   | Write to W |  |

| Example 1:                                                       | SUBLW (                         | )2h                               |            |  |

| Before Instruc<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 01h<br>= ?<br>on<br>= 01h     | esult is positive                 | <b>;</b>   |  |

| Example 2:                                                       | SUBLW (                         | 02h                               |            |  |

| Before Instruc<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 02h<br>= ?<br>on<br>= 00h     | esult is zero                     |            |  |

| Example 3:                                                       | SUBLW (                         | 02h                               |            |  |

| Before Instruction W C After Instruction W C Z N                 | = 03h<br>= ?<br>on<br>= FFh : ( | 2's complemel<br>esult is negativ | nt)<br>ve  |  |

| SUBWF                                                                                                                                                                                                          | Subtract                                                     | W from f                                                                 |                      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|----------------------|--|

| Syntax:                                                                                                                                                                                                        | SUBWF                                                        | SUBWF f {,d {,a}}                                                        |                      |  |

| Operands:                                                                                                                                                                                                      | 0 ≤ f ≤ 255                                                  | ;                                                                        |                      |  |

|                                                                                                                                                                                                                | $d \in [0,1]$                                                |                                                                          |                      |  |

|                                                                                                                                                                                                                | a ∈ [0,1]                                                    |                                                                          |                      |  |

| Operation:                                                                                                                                                                                                     | (f) – (W) –                                                  |                                                                          |                      |  |

| Status Affected:                                                                                                                                                                                               | N, OV, C,                                                    | N, OV, C, DC, Z                                                          |                      |  |

| Encoding:                                                                                                                                                                                                      | 0101                                                         | 0101 11da ffff ffff                                                      |                      |  |

| Description:                                                                                                                                                                                                   |                                                              | Subtract W from register 'f' (2's complement method). If 'd' is '0', the |                      |  |

|                                                                                                                                                                                                                |                                                              | ored in W. If 'd                                                         | ,                    |  |

|                                                                                                                                                                                                                |                                                              | ored back in re                                                          | egister 'f'          |  |

|                                                                                                                                                                                                                | (default).<br>If 'a' is '∩'                                  | the Access Ba                                                            | ank is               |  |

|                                                                                                                                                                                                                |                                                              | f 'a' is '1', the I                                                      |                      |  |

|                                                                                                                                                                                                                |                                                              | ne GPR bank.                                                             |                      |  |

|                                                                                                                                                                                                                |                                                              | and the extended<br>bled, this instru                                    |                      |  |

|                                                                                                                                                                                                                |                                                              | n Indexed Lite                                                           |                      |  |

|                                                                                                                                                                                                                |                                                              | g mode whene                                                             |                      |  |

|                                                                                                                                                                                                                |                                                              | n). See <b>Sectio</b> i<br>ented and Bit-                                |                      |  |

|                                                                                                                                                                                                                | Instruction                                                  | ns in Indexed                                                            |                      |  |

|                                                                                                                                                                                                                | Mode" for                                                    | details.                                                                 |                      |  |

| Words:                                                                                                                                                                                                         | 1                                                            |                                                                          |                      |  |

| Cycles:                                                                                                                                                                                                        | 1                                                            |                                                                          |                      |  |

| Q Cycle Activity:                                                                                                                                                                                              |                                                              |                                                                          |                      |  |

| Q1                                                                                                                                                                                                             | Q2                                                           | Q3                                                                       | Q4                   |  |

| Decode                                                                                                                                                                                                         | Read register 'f'                                            | Process<br>Data                                                          | Write to destination |  |

| Example 1:                                                                                                                                                                                                     | SUBWF                                                        | REG, 1, 0                                                                |                      |  |

| Before Instruct<br>REG                                                                                                                                                                                         |                                                              |                                                                          |                      |  |

| W                                                                                                                                                                                                              | - 3                                                          |                                                                          |                      |  |

| С                                                                                                                                                                                                              | = 2                                                          |                                                                          |                      |  |

| After Instruction                                                                                                                                                                                              | = ?                                                          |                                                                          |                      |  |

| After Instructio<br>REG                                                                                                                                                                                        | n = 1                                                        |                                                                          |                      |  |

|                                                                                                                                                                                                                | n = 1 = 2                                                    | esult is positive                                                        | 3                    |  |

| REG<br>W<br>C<br>Z                                                                                                                                                                                             | n = 1 = 2 = 1 ; re = 0                                       | esult is positive                                                        | 3                    |  |

| REG<br>W<br>C<br>Z<br>N                                                                                                                                                                                        | n = 1 = 2 = 1 ; re = 0 = 0                                   | esult is positive                                                        | •                    |  |

| REG W C Z N Example 2: Before Instruct                                                                                                                                                                         | n = 1 = 2 = 1 ; re = 0 = 0 SUBWF                             | •                                                                        | <b>)</b>             |  |

| REG<br>W<br>C<br>Z<br>N<br>Example 2:<br>Before Instruct<br>REG                                                                                                                                                | n = 1 = 2 = 1 ; re = 0 = 0                                   | •                                                                        | 3                    |  |

| REG W C Z N Example 2: Before Instruct REG W C                                                                                                                                                                 | n = 1 = 2 = 1 ; re = 0 = 0 SUBWF                             | •                                                                        | •                    |  |

| REG W C Z N Example 2: Before Instruct REG W C After Instructio                                                                                                                                                | n = 1 = 2 = 1 ; re = 0 = 0 SUBWF                             | •                                                                        | <del>)</del>         |  |

| REG W C Z N Example 2: Before Instruct REG W C After Instructio REG W C                                                                                                                                        | n = 1 = 2 = 1 ; re = 0 = 0 SUBWF  sion = 2 = 2 = ? n = 2 = 0 | REG, 0, 0                                                                | 3                    |  |

| REG W C Z N Example 2: Before Instruct REG W C After Instructio REG W C Z                                                                                                                                      | n = 1                                                        | •                                                                        | <b>;</b>             |  |

| REG W C Z N  Example 2:  Before Instruct REG W C After Instructio REG W C After Instructio                                                                                                                     | n = 1                                                        | REG, 0, 0                                                                | )                    |  |

| REG W C Z N Example 2: Before Instruct REG W C After Instructio REG W C Z N Example 3:                                                                                                                         | n = 1                                                        | REG, 0, 0                                                                | )                    |  |

| REG W C Z N  Example 2:  Before Instruct REG W C After Instructio REG W C Z N  Example 3:  Before Instruct REG                                                                                                 | n = 1                                                        | REG, 0, 0                                                                | •                    |  |

| REG W C Z N Example 2: Before Instruct REG W C After Instructio REG W C After Instructio REG W C S N Example 3: Before Instruct REG W                                                                          | n = 1                                                        | REG, 0, 0                                                                |                      |  |

| REG W C Z N  Example 2:  Before Instruct REG W C After Instructio REG W C Z N  Example 3:  Before Instruct REG W C After Instruct                                                                              | n = 1 = 2 = 1 ; re = 0 = 0                                   | REG, 0, 0 esult is zero REG, 1, 0                                        |                      |  |

| REG W C Z N Example 2: Before Instruct REG W C After Instructio REG W C After Instructio REG W C Z N Example 3: Before Instruct REG W C                                                                        | n = 1 = 2 = 1 ; re = 0 = 0                                   | REG, 0, 0                                                                |                      |  |

| REG W C Z N  Example 2:  Before Instruct REG W C After Instructio REG W C Z N  Example 3:  Before Instruct REG W C After Instruct REG W C Z After Instruct REG W C After Instruct REG W C After Instructio REG | n = 1 = 2 = 1 ; re = 0                                       | REG, 0, 0 esult is zero REG, 1, 0                                        | ·)                   |  |

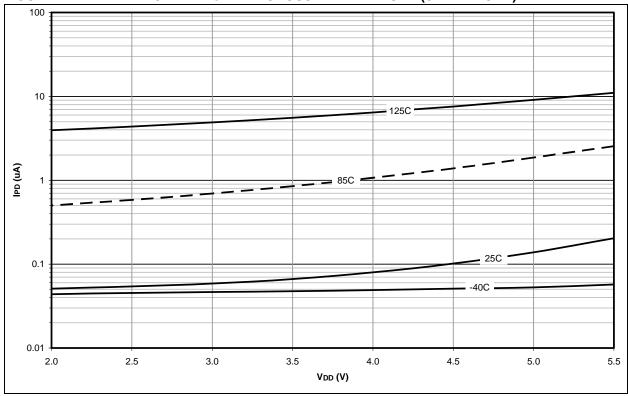

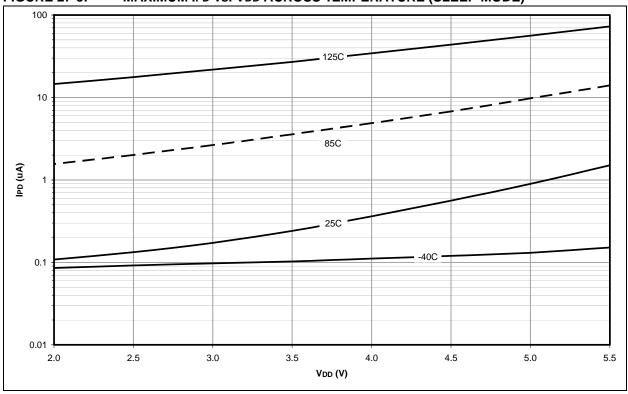

FIGURE 27-2: TYPICAL IPD vs. VDD ACROSS TEMPERATURE (SLEEP MODE)

FIGURE 27-3: MAXIMUM IPD vs. VDD ACROSS TEMPERATURE (SLEEP MODE)

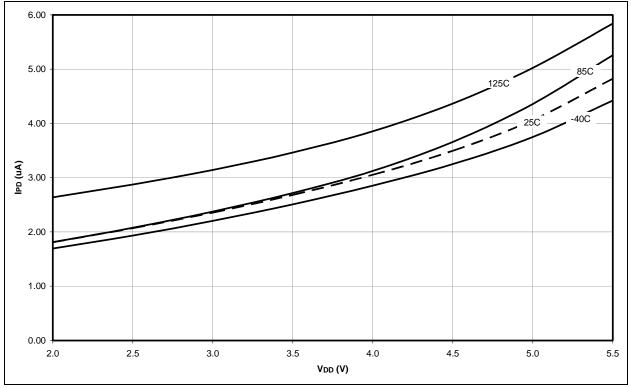

FIGURE 27-9: TYPICAL WDT CURRENT vs. VDD ACROSS TEMPERATURE (WDT DELTA CURRENT IN SLEEP MODE)

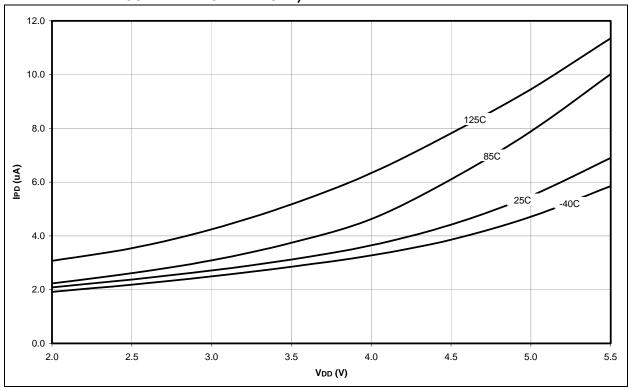

FIGURE 27-10: MAXIMUM WDT CURRENT vs. VDD ACROSS TEMPERATURE (WDT DELTA CURRENT IN SLEEP MODE)

# APPENDIX E: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the Enhanced devices (i.e., PIC18FXXX) is provided in AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442". The changes discussed, while device specific, are generally applicable to all mid-range to Enhanced device migrations.

This Application Note is available as Literature Number DS00716.

# APPENDIX F: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the Enhanced devices (i.e., PIC18FXXX) is provided in AN726, "PIC17CXXX to PIC18CXXX Migration".

This Application Note is available as Literature Number DS00726.

| C                                      |      | Interrupts                                                     |     |

|----------------------------------------|------|----------------------------------------------------------------|-----|

| C Compilers                            |      | Operation                                                      |     |

| MPLAB C18                              | 318  | Operation During Sleep                                         |     |

| MPLAB C30                              |      | Outputs                                                        |     |

| CALL                                   |      | Reference                                                      |     |

| CALLW                                  | _    | External Signal                                                |     |

| Capture (CCP Module)                   |      | Internal Signal                                                |     |

| Associated Registers                   |      | Response Time                                                  |     |

| CCP Pin Configuration                  |      | Comparator Specifications                                      |     |

| CCPRxH:CCPRxL Registers                |      | Comparator Voltage Reference                                   |     |

| Prescaler                              |      | Accuracy and Error                                             |     |

| Software Interrupt                     |      | Associated Registers                                           | 241 |

| Timer1/Timer3 Mode Selection           |      | Configuring                                                    | 239 |

| Capture (ECCP Module)                  |      | Connection Considerations                                      | 240 |

| , ,                                    |      | Effects of a Reset                                             | 240 |

| Capture/Compare/PWM (CCP)              | 139  | Operation During Sleep                                         | 240 |

|                                        | 140  | Compare (CCP Module)                                           | 142 |

| CCPRxI Register                        |      | Associated Registers                                           | 143 |